## Improvement in retention time of metal-ferroelectric-metal- insulator-semiconductor structures using MgO doped Ba 0.7 Sr 0.3 TiO 3 insulator layer

T. Y. Tseng and S. Y. Lee

Citation: Applied Physics Letters 83, 981 (2003); doi: 10.1063/1.1597412

View online: http://dx.doi.org/10.1063/1.1597412

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/83/5?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Metal-ferroelectric (BiFeO 3) -insulator (Y 2 O 3) -semiconductor capacitors and field effect transistors for nonvolatile memory applications

Appl. Phys. Lett. 94, 142905 (2009); 10.1063/1.3114403

Basic characteristics of metal-ferroelectric-insulator-semiconductor structure using a high- k PrO x insulator layer J. Appl. Phys. **93**, 4137 (2003); 10.1063/1.1558206

Mg-doped Ba 0.6 Sr 0.4 TiO 3 thin films for tunable microwave applications

Appl. Phys. Lett. 77, 289 (2000); 10.1063/1.126953

Metal/ferroelectric/insulator/semiconductor structure of Pt/SrBi 2 Ta 2 O 9 /YMnO 3 /Si using YMnO 3 as the buffer layer

Appl. Phys. Lett. 75, 722 (1999); 10.1063/1.124255

Memory window of Pt/SrBi 2 Ta 2 O 9 /CeO 2 /SiO 2 /Si structure for metal ferroelectric insulator semiconductor field effect transistor

Appl. Phys. Lett. 71, 3507 (1997); 10.1063/1.120374

APPLIED PHYSICS LETTERS VOLUME 83, NUMBER 5 4 AUGUST 2003

## Improvement in retention time of metal-ferroelectric-metalinsulator-semiconductor structures using MgO doped Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> insulator layer

T. Y. Tseng<sup>a)</sup> and S. Y. Lee

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, Republic of China

(Received 6 January 2003; accepted 31 May 2003)

We report the results of the fabrication and characterization of Pt/Bi<sub>3.35</sub>La<sub>0.85</sub>Ti<sub>3</sub>O<sub>12</sub> (BLT)/LaNiO<sub>3</sub> (LNO)/Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> (BST)/Si metal-ferroelectric-metal-insulator-semiconductor (MFMIS) structures for ferroelectric memory field effect transistor applications. The BLT films were deposited on LNO/BST/Si using the metalorganic decomposition method and annealed by rapid thermal annealing (RTA) process at 600 °C for 3 min. The ratio of remanent polarization to saturation polarization  $(P_r/P_s)$  increases with reducing area ratio,  $A_F/A_I$ . A large memory window of 3.1 V can be obtained for a small  $A_F/A_I$  ratio. By the utilization of 5 mol % MgO doped BST insulator layer, LNO bottom electrode layer for BLT, and small area ratio,  $A_F/A_I = 1/12$  in the MFMIS structure, large  $P_r/P_s$  ratio in BLT film and low leakage current and good capacitance matching of the ferroelectric and the insulator in the MFMIS structures have been achieved and, hence, long data retention time  $>10^6$  s has been obtained in this study. Experimental results demonstrate the significant progress in increase of the retention time of these structures, which make them attractive for practical ferroelectric memory field effect transistor applications. © 2003 American Institute of *Physics.* [DOI: 10.1063/1.1597412]

Recently, the ferroelectric memory field effect transistors (FeMFETs) have been attracted considerable attention for the applications to nonvolatile ferroelectric random access memories, <sup>1-3</sup> because nondestructive readout is possible and they follow the scaling rule for high density implementation. Good memory window and high switching speed have been reported by some researchers, however, at present, the best data retention time of FeMEFTs was shorter than 10<sup>5</sup> s.<sup>4</sup> Therefore, the difficulty to achieve good data retention characteristics of FeMFETs must be overcome in order to realize its practical applications.<sup>2</sup> On the basis of the results of the theoretical analysis on the electrical characteristics of FeM-FETs, the good data retention characteristics at low voltage operation can be obtained through the utilization of larger remanent polarization to saturation polarization ratio  $(P_r/P_s)$  ferroelectric film, low leakage current density of insulating layer and small  $A_F/A_I$  area ratio of the metalferroelectric-metal-insulator-semiconductor structures.<sup>5–8</sup>

In this letter, we report the electrical properties of MF-MIS structures using ferroelectric Bi<sub>3,35</sub>La<sub>0,85</sub>Ti<sub>3</sub>O<sub>12</sub> (BLT) film and 5 mol % MgO doped Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub> (BST) insulating layer. The 5 mol % MgO doped BST has been reported to have a high dielectric constant of 372 and low leakage current of  $1 \times 10^{-10}$  A/cm<sup>2</sup> at an electric field of 100 kV/cm,<sup>9</sup> which is expected to be suitably used as an insulating material for the "I" layer. Effects of area ratio,  $A_F/A_I$  on the relation capacitance versus applied voltage, memory window, and data retention time are also provided.

The Pt/BLT/LaNiO<sub>3</sub>(LNO)/BST/Si MFMIS structures

The capacitance-voltage (C-V) characteristics were measured on the MFMIS structures using a Keithley 590 CV analyzer. To measure the C-V characteristics, the voltage was applied from the accumulation to the inversion with a sweep rate of 0.1 V/s at 100 kHz and elapsed time of 30 s. The leakage current density versus voltage measurement was performed using a HP4156C semiconductor parameter analyzer. Ferroelectric hysteresis loops were measured by a Radiant Technologies 66A ferroelectric test system. The thicknesses of thin films were determined from scanning electron microscopy observation and N&K 1200 analyzer.

were fabricated in this study with p-type Si (100) as starting

substrate. Subsequent to standard Radio Corporation of America clean, SiON film was grown on silicon substrate in pure N<sub>2</sub>O gas in a furnace. After removing the sacrificial SiON layer by dipping the substrate in diluted HF solution, the 16-nm-thick 5 mol % MgO doped BST (Ba/Sr=70/30) insulator film was deposited on the earlier pretreated substrate by using rf magnetron sputtering. All insulator films were prepared at a fixed power of 100 W, substrate temperature at 450 °C and constant pressure of 20 mTorr, which was maintained by a mixture of argon and oxygen at a mixing ratio of 1:1 with a total flow of 20 sccm. The as-deposited film was annealed at 700 °C by the rapid thermal annealing (RTA) process in pure  $O_2$  ambient for 3 min. The equivalent oxide thickness of BST film is 0.56 nm. The similar steps were employed to deposit the 25-nm-thick LNO oxide electrode on insulator layer. Next, the ferroelectric BLT film with a thickness of 180 nm was formed using a metalorganic decomposition method. The BLT thin film was annealed by the RTA process at 600 °C for 3 min in oxygen ambient. The Pt top electrode was formed and patterned by the lift-off process and finally backelectrode Al was evaporated. The area ratio of MFMIS structures,  $A_I/A_F$  varies from 1 to 16.

a)Electronic mail: tseng@cc.nctu.edu.tw

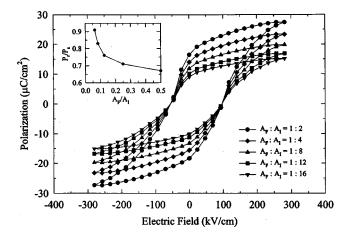

FIG. 1. P-E hysteresis loops of BLT films when the area ratio,  $A_F/A_I$  is changed from 1/2 to 1/16. The inset shows the changes of  $P_r/P_s$  with the  $A_F/A_I$  ratios.

The polarization versus electric field (P-E) hysteresis loops of BLT films were measured on Pt/BLT/LNO (MFM) structures among MFMIS frames. The voltage  $\pm 5$  V was applied to the BLT films in MFMIS structures with various area ratios,  $A_F/A_I$ . It is indicated in Fig. 1 that the  $P_r/P_s$  ratio increases from 0.67 to 0.91 with the area ratio  $A_F/A_I$  decreasing from 1/2 to 1/16.

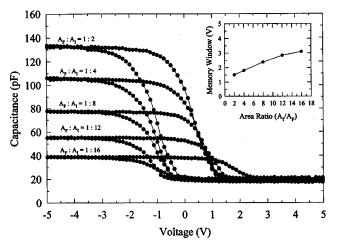

Figure 2 depicts the C-V characteristics of Pt/BLT/ LNO/BST/Si structures with various  $A_E/A_I$  ratios at the voltage sweep rang of  $\pm 5$  V. The physical reason for clockwise hysteresis loops has been given in a previous article.<sup>6</sup> In addition, the accumulation capacitance decreases when the area ratio  $A_F/A_I$  is decreased, which is attributed to decrease in total capacitance of the MFMIS structure arising from the decrease of MFM area. The theoretical memory window is about 3.1 V, because the memory window is represented by  $2V_C$  and the coercive field and thickness of BLT films were approximately 86 kV/cm and 180 nm, respectively. The memory window of Pt/BLT/LNO/BST/Si MFMIS structures increases with the decreasing area ratio  $A_F/A_I$  as shown in the inset of Fig. 2. The observed memory window is 1.5 V for  $A_F/A_I = 1:2$ , whereas it becomes 3.1 V for the  $A_F/A_I$ = 1:16.

FIG. 2. C-V characteristics of Pt/BLT/LNO/BST/Si MFMIS structures with various area ratios,  $A_F/A_I$  indicated. The inset shows the memory window as a function of area ratio.

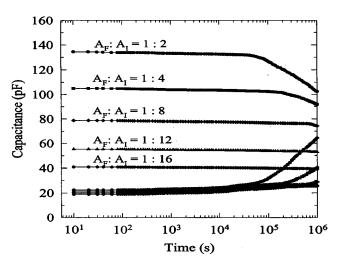

FIG. 3. Data retention time measured for MFMIS structures with various area ratios,  $A_F/A_I$  indicated.

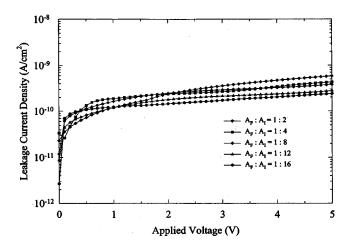

The retention characteristics of the MFMIS structures are illustrated in Fig. 3. The writing pulse applied to the MFMIS capacitors were  $\pm 4 \text{ V}$  in height and 1 s in duration. The measurement voltage was kept at 0 V. It is indicated in Fig. 3 that the retention time is more than 10<sup>5</sup> s for various area ratios,  $A_F/A_I$  and is  $10^6$  s or more (>11.6 days) for area ratio,  $A_F/A_I = 1/12$  and 1/16 which is the longest retention time of MFMIS capacitors appeared in the published literature. Figure 4 shows the leakage current density of the MFMIS structure with various area ratios,  $A_F/A_I$ , indicated. The leakage current density of the structures has a small value of near 10<sup>-10</sup> A/cm<sup>2</sup> because of high resistivity MgO doped BST used as I layer9 and nitridation treatment of silicon wafer. <sup>10</sup> For  $A_F/A_I = 1/12$  MFMIS capacitors,  $P_r$  equals  $10 \,\mu\text{C/cm}^2$  and leakage current is about  $10^{-10} \,\text{A/cm}^2$  (Fig. 4), the expected retention time for our MFMIS structure can be estimated to be 10<sup>4</sup> s for the highest possible trapping probability of  $\alpha = 1$  and  $10^8$  s for the very low trapping probability of  $\alpha = 10^{-4}$  based on a previous study. Our measured retention time,  $>10^6$  s is located between these two extreme expected values. However, an acceleration test will have to be employed to verify that is the 10 year retention time achieved. The measurement method used in this study is too tedious.

FIG. 4. Plot of leakage current density vs applied voltage for MFMIS structures with various area ratios,  $A_F/A_I$  indicated.

In comparison with the reported results, which are less than a few days of retention time for the best FeMFET, significant improvement in retention time was observed in our MFMIS structures. We attribute such improvement to four major reasons: (1) large  $P_r/P_s$  ratio in ferroelectric BLT films. The  $P_r/P_s$  ratios corresponding to  $A_F/A_I$  ratios 1/12 and 1/16 capacitors which exhibit long retention time are about 0.8 and 0.9, repectively (the inset of Fig. 1); (2) high resistivity MgO doped BST insulator layer and low leakage current MFMIS structures; (3) good interfacial properties of BST/Si due to nitridation treatment;  $^{10}$  and (4) good matching of the capacitances of MFM and MIS.

In summary, Pt/BLT (180 nm)/LNO (25 nm)/BST (16 nm)/Si MFMIS structures have been fabricated and characterized. The memory window of the MFMIS capacitors depended on the area ratio,  $A_F/A_I$ . A large memory window of 3.1 V could be obtained for  $A_F/A_I = 1/16$ . A significant improvement in data retention time, >11.6 days has been achieved for Pt/BLT/LNO/BST/Si MFMIS structures, which enables researchers to be optimistic in reaching the require-

ment of 10 year retention time for FeMFETs with potential prospects of realizing the practical applications of nonvolatile FeMFET in the future.

The work was supported by the National Science Council R.O.C. under Contract No. NSC 90-2215-E-009-100.

<sup>&</sup>lt;sup>1</sup>Y. Tarui, Tech. Dig. - Int. Electron Devices Meet. 1994, 7 (1994).

<sup>&</sup>lt;sup>2</sup>T. Y. Tseng, in Extended Abstracts of 1st International Meeting on Ferroelectric Random Access Memories, Gotemba, Japan, 19–21 Nov., 2001, pp. 62–63.

<sup>&</sup>lt;sup>3</sup>H. Ishiwara, Integr. Ferroelectr. **34**, 1451 (2001).

<sup>&</sup>lt;sup>4</sup>S. M. Yoon and H. Ishiwara, IEEE Trans. Electron Devices **48**, 2002 (2001).

<sup>&</sup>lt;sup>5</sup>E. Tokumitsu, G. Fujii, and H. Ishiwara, Jpn. J. Appl. Phys., Part 1 39, 2125 (2000).

<sup>&</sup>lt;sup>6</sup>H. T. Lue, C. J. Wu, and T. Y. Tseng, IEEE Trans. Electron Devices **49**, 1790 (2002).

<sup>&</sup>lt;sup>7</sup>H. T. Lue, C. J. Wu, and T. Y. Tseng, IEEE Trans. Ultrason. Ferroelectr. Freq. Control **50**, 5 (2003).

<sup>&</sup>lt;sup>8</sup>T. P. Ma and J. P. Han, IEEE Electron Device Lett. 23, 386 (2002).

<sup>&</sup>lt;sup>9</sup>S. Y. Lee and T. Y. Tseng, Appl. Phys. Lett. **80**, 1797 (2002).

<sup>&</sup>lt;sup>10</sup>C. Y. Liu, H. T. Lue, and T. Y. Tseng, Appl. Phys. Lett. 81, 4416 (2002).