# A Study of Parasitic Resistance Effects in Thin-Channel Polycrystalline Silicon TFTs With Tungsten-Clad Source/Drain

Hsiao-Wen Zan, Ting-Chang Chang, Po-Sheng Shih, Du-Zen Peng, Po-Yi Kuo, Tiao-Yuan Huang, *Fellow, IEEE*, Chun-Yen Chang, *Fellow, IEEE*, and Po-Tsun Liu

Abstract—With selectively-deposited tungsten film grown on source/drain regions, the parasitic source/drain resistance of thin-channel polycrystalline silicon (poly-Si) thin film transistors can be greatly reduced, leading to the improvement of device driving ability. After extracting the parasitic resistance from characteristics of devices with different channel length, the influences of parasitic resistance on device performances were discussed. A physically-based equation containing the parasitic resistance effects was derived to explain the behavior of linear transconductance under high gate voltage. Good agreements were found between calculated and measured data for both the thin-channel devices with or without tungsten-clad source/drain structure.

Index Terms—Parasitic resistance, poly-Si TFT, S/D resistance, selective tungsten, thin channel.

### I. INTRODUCTION

It has been reported that improved device performance such as high driving ability and small leakage current can be obtained by reducing the channel thickness of poly-Si TFTs [1]. However, shrinking the thickness of channel layer also enlarge the parasitic source/drain resistance, leading to a degraded driving ability. Similar problems occurred in thin-film silicon-on-insulators (SOIs) have been solved by using self-aligned silicide (SALICIDE) or selective tungsten chemical vapor deposition (SWCVD) technologies to reduce S/D resistance [2], [3]. For thin-channel poly-Si TFTs, however, most studies focus on fabricating various raised-S/D structures [4], [5]. The capability of using SALICIDE or SWCVD process on thin-channel poly-Si TFTs has never been verified. Moreover, when most papers address the improvement of device driving ability [4], [5], the parasitic resistance effects

Manuscript received April 14, 2003; revised May 19, 2003. This work was supported by the National Science Council of Taiwan, R.O.C., under Contracts NSC 91-2215-E110-019 and NSC 91-2112-M100-008. The review of this letter was arranged by Editor J. Sin.

H.-W. Zan is with the Institute of Electro-Optical Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

T.-C. Chang is with the Department of Physics and the Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung 80424, Taiwan, R.O.C (e-mail: tcchang@mail.phys.nsysu.edu.tw).

P.-S. Shih, D.-Z. Peng, P.-Y. Kuo, T.-Y. Huang, and C.-Y. Chang are with the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

P.-T. Liu is with the National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LED.2003.815160

still lack for discussion. In this letter, thin-channel poly-Si TFTs with tungsten-clad S/D (W-TFTs) are demonstrated using SWCVD process, which has smaller silicon consumption than SALICIDE technologies [3], [6]. The parasitic resistance influences are studied by extracting parasitic resistance from device characteristics. The degradation of linear transconductance caused by parasitic resistance is also explained by a physical derivation.

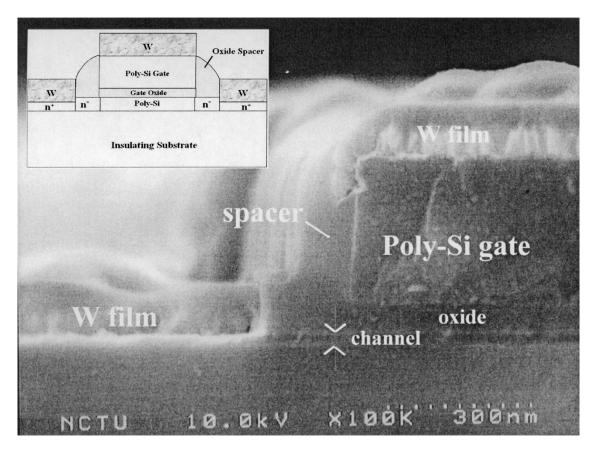

# II. EXPERIMENTAL

Proposed W-TFTs are prepared by the following process steps with a structure shown in the inset of Fig. 1. First, a 30 nm amorphous silicon layer was deposited by low-pressure chemical vapor deposition (LPCVD) at 550 °C on oxidized silicon wafers. After active region patterning, a 60 nm tetraethoxysilane (TEOS) oxide layer and subsequently a 300 nm a-Si layer were deposited by LPCVD. The a-Si layer was then recrystallized by solid phase crystallization (SPC) at 600 °C for 24 h. After defining gate electrode, n<sup>-</sup> lightly-doped drain (LDD) implant was performed using phosphorus ions at a dose of  $3 \times 10^{13}$  cm<sup>-2</sup>. A 200 nm oxide sidewall spacer abutting the gate was formed by conformal deposition of a TEOS oxide layer and subsequent reactive ion etching. Phosphorus ions at a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> were implanted to form the n<sup>+</sup> S/D region, then activated by rapid thermal annealing (RTA) at 750 °C for 20 sec. After removing the remaining oxide on source/drain regions by diluted HF, wafers were loaded into SWCVD system (ULVAC ERA-1000) to selectively deposit W film on exposed gate, source and drain regions with WF<sub>6</sub>/SiH<sub>4</sub> gas flow rate as 20/6 and process temperature of 300 °C. Conventional devices without W film deposition were also fabricated on the same wafer to serve as controls. A 500 nm Al film is deposited and defined to be metal pads. To reduce trap density and improve interface quality, wafers were also immured in an NH3 plasma generated by plasma enhanced CVD (PECVD) at 300 °C for 1 h [7]. The cross sectional SEM image of the proposed W-TFTs is shown in Fig. 1. It is observed that the thickness of the W film is about 120 nm and the silicon consumption in S/D region is less than 20 nm (not fully-consumed), ensuring good contact resistance in ultrathin channel devices [6].

Fig. 1. Schematic cross sectional view (in the inset) and the SEM image of the proposed W-TFTs.

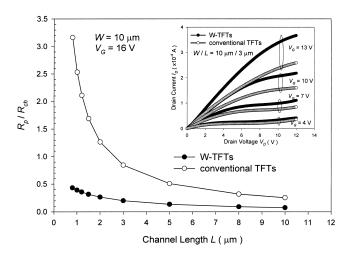

Fig. 2. Parasitic resistance over channel resistance as a function of channel length. Black circles represent data from W-TFTs, while white circles stand for data from conventional TFTs. A comparison of output characteristics for thin-channel W-TFTs and conventional TFTs is shown in the inset with nominal channel width and length of  $10~\mu m$  and  $3~\mu m$ .

# III. RESULTS AND DISCUSSIONS

The comparison of typical output characteristics of thin-channel W-TFTs and conventional ones are shown in the inset of Fig. 2. Obviously W-TFTs exhibit larger ON current than conventional ones. According to [8], the parasitic resistance  $R_p$  of devices can be extracted by plotting the channel width normalized ON resistance  $R_{on}W$  against the channel length L. With different gate bias, the relationship between

$R_{on}W$  and L can be expressed by several straight lines that extend to merge at a characteristics length  $l_0$  representing the accumulation channel in LDD (and S/D) area and have a residual value of a gate-voltage independent parasitic resistance  $R_pW$  [8]. The ON resistance is therefore expressed as

$$R_{on} = \frac{\partial V_D}{\partial I_D} = R_p + R_{ch} = R_p + \frac{L - l_0}{WC_{ox}\mu_n \left(V_G - V_{TH}\right)} \tag{1}$$

where  $R_{ch}$  represents the channel resistance,  $C_{ox}$  is the gate oxide capacitance per unit area,  $\mu_n$  is the intrinsic carrier mobility without the parasitic resistance effects,  $V_{TH}$  is the device threshold voltage, and  $L - l_0$  is defined as the effective channel length. Compared to the extracted  $R_p$  (13.2 k $\Omega$ ) of conventional thin-channel devices, W-TFTs are found to exhibit smaller  $R_p$ (3.5 k $\Omega$ ). Though  $R_p$  consists of S/D resistance and the parasitic resistance in LDD regions in our experiment, the latter one is the same by using identical LDD formation process. Accordingly, the improvement of  $R_p$  in W-TFTs is mostly contributed by reducing the S/D resistance. The influence of  $R_p$  is further revealed by plotting  $(R_p/R_{ch})$  against channel length in Fig. 2(b). When channel length scaled down,  $(R_p/R_{ch})$  keeps rising because of the reduced channel resistance. However, for conventional TFTs, the  $(R_p/R_{ch})$  increases much more drastically than that of W-TFTs. Moreover, the  $R_p$  of conventional devices starts to dominate device performance when channel length is less than 2  $\mu$ m.

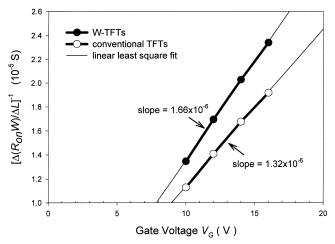

When plotting the reciprocal of the slope,  $[\Delta(R_{on}W)/\Delta L]^{-1}$  versus gate voltage  $V_G$  as given in Fig. 3, linear relationships are found for both W-TFTs and conventional ones [8]. The slope of the curves, representing

Fig. 3. Channel sheet conductance as a function of gate voltage. The solid line represents the linear least square fit of data while its slope contains the carrier mobility independent of channel length and parasitic resistance effects.

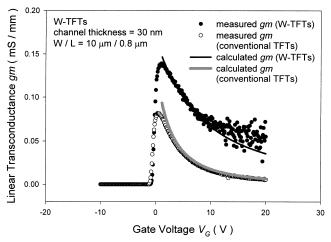

Fig. 4. Comparison between calculated and measured linear region transconductances. The nominal channel width and length are 10  $\mu$ m and 0.8  $\mu$ m, respectively.

the intrinsic carrier mobility, has no dependence on the gate voltage. This implies that the grain boundary barrier height, which dominates carrier transport in poly-Si film, have negligible variation with the gate voltage in linear region [9]. As a result, the intrinsic mobility  $\mu_n$  of W-TFTs is 14.4 cm<sup>2</sup>/Vs while that of conventional TFTs is 11.5 cm<sup>2</sup>/Vs. The linear region transconductance can be derived by

$$I_D = V_D (R_p + R_{ch})^{-1}$$

$$gm \equiv \frac{\partial I_D}{\partial V_G} = AV_D \left(\frac{R_{ch}}{R_p + R_{ch}}\right) 2$$

$$= AV_D \left[AR_p (V_G - V_{TH}) + 1\right]^{-2}$$

(3)

where  $A \equiv W \mu_n C_{ox}/L - l_0$ . With  $R_p$  and  $l_0$  obtained previously, gm calculated by eqn (3) is compared with measured data

in Fig. 4. A good agreement is found, verifying the fact that the linear region gm is dominated by parasitic resistance effect especially in short channel devices. Larger  $R_p$  value gives rise to smaller gm maximum value and severer gm degradation under high gate voltages.

# IV. CONCLUSION

Thin-channel poly-Si TFTs with reduced parasitic resistance are fabricated by capping tungsten film on S/D regions. The parasitic resistance can be reduced to 3.8 times smaller than that of control samples. W-TFTs therefore exhibit less pronounced parasitic resistance effects. By extracting the intrinsic carrier mobility, the gate voltage is found to have no influence on carrier transport in linear region. The degradation of linear region transconductance can be explained well by including the parasitic resistance effect into device current–voltage characteristics.

# ACKNOWLEDGMENT

The authors would like to thank C. H. Jan and J. L. Hsu for their assistance.

#### REFERENCES

- M. Miyasaka, T. Komatsu, W. Itoh, A. Yamaguchi, and H. Ohshima, "Effects of semiconductor thickness on poly-crystalline silicon thin film transistors," *Jpn. J. Appl. Phys.*, vol. 35, pp. 923–929, Feb. 1996

- [2] Y. Yamaguchi, T. Nishimura, Y. Akasaka, and K. Fuhibayashi, "Self-alinged silicide technology for ultra-thin SIMOX MOSFET's," *IEEE Trans. Electron Devices*, vol. 39, pp. 1179–1183, May 1992.

- [3] M. Takahashi, T. Ohno, Y. Sakakibara, and K. Takayama, "Fully depleted 20-nm SOI CMOSFETs with W-clad gate/source/drian layers," *IEEE Trans. Electron Devices*, vol. 48, pp. 1380–1385, July 2001

- [4] D. Z. Peng, T. C. Chang, P. S. Shih, H. W. Zan, T. Y. Huang, C. Y. Chang, and P. T. Liu, "Polycrystalline silicon thin-film transistor with self-aligned SiGe raised source/drain," *Appl. Phys. Lett.*, vol. 81, pp. 4763–4765, Dec. 2002.

- [5] S. Zhang, C. Zhu, K. O. Sin, and P. K. T. Mok, "A novel ultrathin elevated channel low-temperature poly-SI TFT," *IEEE Electron Device Lett.*, vol. 20, pp. 569–571, Nov. 1999.

- [6] M. Takahashi and K. Takayama, "Si consumption in selective chemical vapor deposition of tungsten using SiH<sub>4</sub> reduction of WF<sub>6</sub>," J. Electrochem. Soc., vol. 148, no. 4, pp. G229–G231, 2001.

- [7] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation on N-channel polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, pp. 64–68, Jan. 1997.

- [8] S. Luan and G. W. Neuduck, "An experimental study of the source/drain parasitic resistance effects in amorphous silicon thin film transistors," J. Appl. Phys., vol. 72, pp. 766–772, July 1992.

- [9] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin-film transistors," *J. Appl. Phys.*, vol. 53, no. 2, pp. 1193–1202, Feb. 1982