## Formation of interfacial layer during reactive sputtering of hafnium oxide

Bing-Yue Tsui and Hsiu-Wei Chang

Citation: Journal of Applied Physics **93**, 10119 (2003); doi: 10.1063/1.1574594 View online: http://dx.doi.org/10.1063/1.1574594 View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/93/12?ver=pdfcov Published by the AIP Publishing

### Articles you may be interested in

Film and interface layer properties of ultraviolet-ozone oxidized hafnia and zirconia gate dielectrics on silicon substrates Appl. Phys. Lett. **85**, 4699 (2004); 10.1063/1.1814799

Minimization of germanium penetration, nanocrystal formation, charge storage, and retention in a trilayer memory structure with silicon nitride/hafnium dioxide stack as the tunnel dielectric Appl. Phys. Lett. **84**, 4385 (2004); 10.1063/1.1757022

Epitaxial growth of metastable -TaN layers on MgO(001) using low-energy, high-flux ion irradiation during ultrahigh vacuum reactive magnetron sputtering J. Vac. Sci. Technol. A **20**, 2007 (2002); 10.1116/1.1513639

Interfacial reaction between chemically vapor-deposited HfO 2 thin films and a HF-cleaned Si substrate during film growth and postannealing Appl. Phys. Lett. **80**, 2368 (2002); 10.1063/1.1466534

Physical and electrical characterization of Hafnium oxide and Hafnium silicate sputtered films J. Appl. Phys. **90**, 6466 (2001); 10.1063/1.1417991

# AIP Re-register for Table of Content Alerts

## Formation of interfacial layer during reactive sputtering of hafnium oxide

Bing-Yue Tsui<sup>a)</sup> and Hsiu-Wei Chang

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, Republic of China

(Received 20 September 2002; accepted 25 March 2003)

Hafnium oxide is one of the most promising high dielectric constant materials to replace silicon dioxide as the gate dielectric. To take the advantages of high dielectric constant of HfO<sub>2</sub> thoroughly, the relatively low dielectric constant interfacial layer must be controlled carefully. In this work, the formation of an interfacial SiO<sub>2</sub> layer at the  $HfO_2/Si$  interface was studied comprehensively. It is observed that during reactive sputtering deposition of the HfO<sub>2</sub> layer, a very thick interfacial SiO<sub>2</sub> layer, thicker than 3 nm, would be grown. O-radical signals, instead of O<sub>2</sub>-radicl signals, are detected in the sputtering chamber. An O-radical enhanced oxidation model is proposed to explain such an unusual thick  $SiO_2$  layer. The adoption of a two-step deposition method, the thickness of interfacial  $SiO_2$  layer can be reduced only if the bottom Hf layer is thicker than 5 nm. However, the reduction of effective oxide thickness would be limited. Reoxidation of Hf film sounds a better choice. A 1.0-1.5-nm-thick interfacial SiO<sub>2</sub> layer is still observed. This implies that the traced oxygen in the sputtering chamber plays a critical role on the formation of the interfacial layer. It is thus concluded that reactive sputtering is not a suitable method to prepare a  $HfO_2$  layer with a negligible interfacial SiO<sub>2</sub> layer. Reoxidation of Hf film is a better choice, but the oxygen content in the sputtering chamber must be well controlled. © 2003 American Institute of Physics. [DOI: 10.1063/1.1574594]

#### INTRODUCTION

Silicon dioxide (SiO<sub>2</sub>) have been used as the gate dielectric of complementary metal-oxide-semiconductor devices for several decades because of its superior properties such as low interface state density, large energy band gap (8.9 eV), low leakage current, and good thermal stability for the Si substrate and poly-Si gate. As device dimensions scale down, the thickness of SiO<sub>2</sub> must be reduced to keep sufficient current driving capability. But when the thickness of SiO<sub>2</sub> was below 3.5 nm, direct tunneling current increases 100 times for every 0.4–0.5 nm decrease of thickness.<sup>1</sup> This high gate leakage current would increase standby power consumption and induce loss of inversion layer changes. According to the 2001 ITRS roadmap, the effective oxide thickness (EOT) (a number which converts thickness of dielectric thickness into thickness of SiO<sub>2</sub>) will reach 1.8 nm and the maximum gate current should be lower than 2 mA/cm<sup>2</sup> for low power application in 2005.<sup>2</sup> The simulated leakage current of 1.8 nm SiO<sub>2</sub> was about 1 A/cm<sup>2</sup> and could not meet the specified gate leakage current.

In order to reduce gate current caused by direct tunneling, the physically thickness of dielectric must increase such that the EOT can scale down continuously. Gate dielectrics with dielectric constant (K) higher than SiO<sub>2</sub> must be developed. Oxynitride (SiON), with K in the range of 5–7, has been extensively studied and was found to exhibit more controllable oxidation rate, lower interface state generation, improved resistance against dopant diffusion, higher dielectric intensity, lower stress induced leakage current, and lower charge trapping characteristics.<sup>3–5</sup> It has been thought as an alternative dielectric for the next generation. But it is unclear if oxynitride will meet future leakage current target because its dielectric constant is not high enough. Several alternative high dielectric constant (high-k) materials with dielectric constant higher than SiON have been studied to overcome the challenge of gate dielectric scale down.

The most commonly reported high-k materials are HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and La<sub>2</sub>O<sub>3</sub> etc.<sup>6-12</sup> Among these candidates, HfO2 attracted much more attention form recent researches. The reported dielectric constant of HfO<sub>2</sub> is about  $25-30.^{6,7}$  This magnitude of the K value is higher than that of  $Si_3Ni_4$  (~7) and  $Al_2O_3$  (8–11.5).<sup>6,7</sup> At the same time, it is not too high to induce severe focused ion beam lithography effect.<sup>13</sup> The energy band gap of HfO<sub>2</sub> is about 5.68 eV, which is higher than that of the other high-K materials.<sup>14</sup> Band alignment determines the barrier height for electron and hole tunneling from gate or Si substrate. The calculated band offsets of HfO<sub>2</sub> for electron and hole is 1.5 and 3.4 eV, respectively.<sup>14</sup> This band alignment is acceptable and better than other high-K materials such as Ta<sub>2</sub>O<sub>5</sub>.<sup>14</sup> The free energy of reaction with Si is about 47.6 Kcal/mol at 727 °C, which is also higher than that of TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>. Therefore, HfO<sub>2</sub> is a more stable material on the Si substrate as compared to TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>.<sup>15</sup> Among the elements in the IVA group of the periodic table (Ti, Zr, Hf), Hf has the highest heat of formation (271 kcal/mol).<sup>16</sup> Unlike other silicides, the silicide of Hf can be easily oxidized.<sup>17</sup> That means that Hf is easy to be oxidized to form HfO<sub>2</sub> and the oxide of Hf is usually stable on the Si substrate. Unlike ZrO<sub>2</sub> HfO<sub>2</sub> shows a good thermodynamic stability with poly-Si. It had been re-

0021-8979/2003/93(12)/10119/6/\$20.00

10119

[This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to ] IP 140.113.38.11 On: Thu. 01 May 2014 05:31:14

<sup>&</sup>lt;sup>a)</sup>Electronic mail: bytsui@mail.nctu.edu.tw

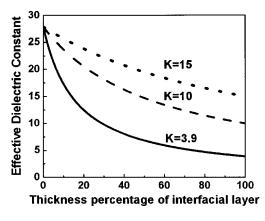

FIG. 1. Effective dielectric constant of  $HfO_2$ /interfacial layer stack structure vs the thickness of interfacial layer with the dielectric constant of interfacial layer as parameter. The dielectric constant of  $HfO_2$  is assumed to be 27.

ported that  $HfO_2$  would not react with poly-Si at temperatures as high as 1000 °C.<sup>18</sup>

Several deposition techniques have been employed to prepare HfO<sub>2</sub> film. They are physical vapor deposition (PVD),<sup>19,20</sup> chemical vapor deposition,<sup>21,22</sup> atomic layer deposition,<sup>23,24</sup> and jet vapor deposition.<sup>25,26</sup> Among these deposition techniques, PVD has advantages of simple process, high purity, and low cost-of-ownership. However, an unusually thick interfacial layer (IL) was observed in some literatures.<sup>27</sup> Figure 1 shows the calculated impact of interfacial layer on the effective *k* value of the HfO<sub>2</sub>/IL stack assuming the *k* value of HfO<sub>2</sub> is 27. A 10% SiO<sub>2</sub>-like interfacial layer results in a more than 30% degradation of the effective *k* value. To take the advantages of high *K* value of HfO<sub>2</sub> thoroughly, the interfacial layer must be reduced as possible.

In this article, we focused on the formation of interfacial layer using the PVD method. Various deposition schemes were employed to form  $HfO_2$  film. A detailed experimental procedure is described in the next section. Experimental results are presented and discussed in Sec. III. The formation mechanism of an interfacial layer and the guidelines for minimizing the interfacial layer are proposed last.

#### **EXPERIMENTAL PROCEDURE**

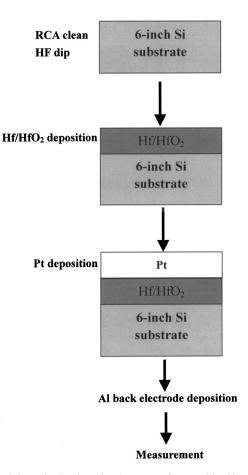

Simple metal-insulator-silicon structures were fabricated to study the EOT and interfacial layer at the HfO2/Si interface. The main process flow is briefly listed in Fig. 2. The starting material is 6 in. (100)-oriented *p*-type wafer. After a standard Radio Corporation of American clean, wafers were immersed in dilute HF solution to remove chemical oxide. Wafers were then loaded into the chamber of a reactively dc sputtering system. During film deposition, the substrate temperature was held at 100 °C. Either HfO<sub>2</sub> or Hf film was deposited by sputtering from a Hf target. The base pressure of the sputtering chamber before deposition was pumped down to  $2 \times 10^{-8}$  Torr and the pressure during deposition was kept at  $2 \times 10^{-3}$  Torr. When Hf was deposited, the gas and flow rate are Ar and 120 sccm, respectively. For HfO<sub>2</sub> deposition, the gas mixture and flow rate are Ar/O<sub>2</sub> and 30/10 sccm, respectively. The deposition power was kept

FIG. 2. Schematic drawing of main process flow used in this work.

at 100 W. The deposition rate of  $HfO_2$  and Hf is different for different power and gas ratio. For the deposition condition used in this work, the deposition rate of  $HfO_2$  and Hf is about 0.6 and 9.6 nm/min, respectively. The thickness ratio of the  $HfO_2/Hf$  stack was split into two categories. One is fixing the bottom Hf thickness at 1 nm and varying the top  $HfO_2$  thickness from 3 to 9 nm. The other is fixing the top  $HfO_2$  thickness at 7 nm and varying the bottom Hf thickness from 0 to 5 nm. The deposited film structures and sample ID are listed in Table I.

Postdeposition annealing (PDA) was performed in a rapid thermal annealing system at 600 °C for 30 s in N<sub>2</sub> ambient. Since oxygen can penetrate through both Hf and HfO<sub>2</sub> films the deposited Hf layer was converted into HfO<sub>2</sub> during PDA by reacting with residual oxygen in annealing ambient.<sup>16,28–30</sup> Platinum is used as gate electrode due to its inert property. Pt was deposited in an electron beam evaporation system through a shadow mask after PDA. The area of the capacitor is  $3.63 \times 10^{-3}$  cm<sup>2</sup>. Then a backside metallization process completed the sample fabrication. A metal–insulator–metal (MIM) sample was also fabricated to iden-

TABLE I. Sample ID and film structures used in this work.

| Sample ID             | H70 | H71 | H73 | H75 | H31 | H51 | H71 | H91 | H03 |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| HfO <sub>2</sub> (nm) | 7   | 7   | 7   | 7   | 3   | 5   | 7   | 9   | 0   |

| Hf (nm)               | 0   | 1   | 3   | 5   | 1   | 1   | 1   | 1   | 3   |

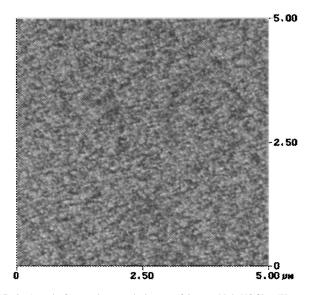

FIG. 3. Atomic force microscopic image of 2-mm-thick Hf film. The rootmean-square roughness is only 0.253 nm.

tify the actual dielectric constant of the deposited  $HfO_2$  layer. TiN is used as gate electrode of the MIM sample.

The thickness of deposited film was measured with an N&K analyzer. The surface roughness was measured with an atomic force microscope (AFM). For electrical analysis, a high frequency capacitance-voltage (HFCV) characteristic was measured at 100 kHz with a precision impedance meter of model Agilent 4284A. The effective dielectric constant is then calculated from the measured capacitance at accumulation mode and optically measured dielectric thickness. For material analysis, transmission electron microscopy (TEM) was used to determine the exact thickness and identify the interface situation between the HfO2 and Si substrate. The dielectric constant of HfO2 can be calculated from the MIM sample. Then, the dielectric constant of the interfacial layer can be determined according to the actual thickness of each layer and the dielectric constant of HfO<sub>2</sub> from the MIM sample. The composition of the interfacial layer was further identified with energy dispersive microscopy (EDS) in a TEM system.

#### **RESULT AND DISCUSSION**

The uniformity, defined as the range of thickness divided by 2 times of the average thickness, of as-deposited film thickness measured with an N&K analyzer is between 4% and 5% for both Hf and HfO<sub>2</sub> films at all thicknesses. Figure 3 shows that the surface roughness of the 2-nm-thick Hf film measured by AFM is 0.253 nm, which is very close to that of the original Si surface and is much smaller than the thickness of deposited film. The continuity of films was further characterized with plane-view scanning electron microscopy inspection, no pin holes and agglomeration phenomenon were observed. All of these results confirm the homogeneity of the deposited films.

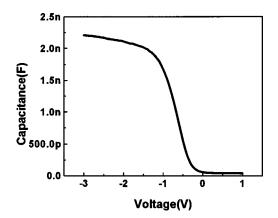

Figure 4 shows the HFCV curve of sample H73. The curve looks normal but the calculated effective K value is only 8.5, which is much lower than the typical K value of

FIG. 4. High frequency capacitance–voltage curve of sample H73. The curve looks normal but the calculated effective K value is only 8.5.

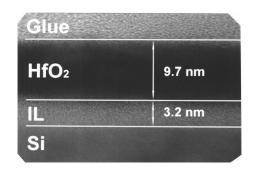

HfO<sub>2</sub> film. To check if the deposited film is normal, the TiN/Hf/HfO2/Hf/TiN structure was prepared. The thickness of the dielectric is 12.5 nm from the cross-sectional TEM inspection. The exact K value of HfO<sub>2</sub> film was calculated to be 27.9 and this value is consistent with the reported K value of HfO<sub>2</sub>, 20–30. To understand why the effective k value of sample H73 is so low, high-resolution TEM was employed to inspect the actual sample structure. Figure 5 shows the crosssectional TEM micrograph of sample H73. Because of the poor adhesion between Pt and HfO<sub>2</sub>, the Pt layer peeled-off during sample preparation. A thick interfacial layer of 3.2 nm thick between HfO<sub>2</sub> and Si substrate is clearly observed. This observation is consistent with that reported previously.<sup>27</sup> Because HfO<sub>2</sub> was deposited immediately after the HF-dip step, there should not be such an unusual thick native oxide on the Si surface. In fact, the native oxide thickness measured on the Si wafer just after the HF dip process by the N&K analyzer is less than 0.3 nm.

The interfacial layer may be either silicon dioxide of Hf-silicate. To clarify what material it is, the *K* value of the interfacial layer was estimated using the thickness of interfacial layer and the thickness of the HfO<sub>2</sub> layer measured from Fig. 5, and the dielectric constant of HfO<sub>2</sub> is assumed to be 27.9. The estimated *K* value of the interfacial layer is 3.8, which indicates that the interfacial layer is SiO<sub>2</sub>-liked material. The composition of the interfacial layer was analyzed with EDS. The signal intensity of Hf within the HfO<sub>2</sub> layer is much stronger than that within interfacial layer, while the

FIG. 5. Cross-sectional TEM micrograph of sample H73. A thick interfacial layer of 3.2 nm thick between the HfO<sub>2</sub> and Si substrate is clearly observed.

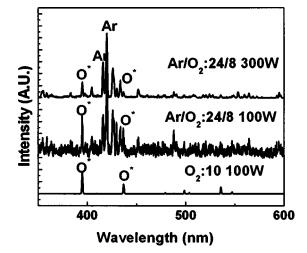

FIG. 6. Optical-emission spectrums of various gas mixtures in the sputtering chamber. Strong O-radical signals are detected in all cases.

signal intensity of oxygen keeps similar. The result confirms that the interfacial layer is SiO<sub>2</sub>-like material but not Hf–silicate.

Since the sample shown in Fig. 5 did not experience PDA, the thick interfacial oxide must be grown during the  $HfO_2$  deposition period. It should be noted that the PDA process used in this work only produces a SiO<sub>2</sub> layer thinner than 0.5 nm on bare Si. Even if the sample experienced PDA, the 3.2-nm-thick SiO<sub>2</sub>-liked IL can not be attributed to the PDA process.

Up to now, a fact that can be sure is that the thick oxide layer is formed during the reactive sputter process. Why reactive sputter introduces such a thick oxide layer? The temperature during sputtering is only 100 °C and the content of oxygen is much lower than that in typical oxidation furnace. The partial pressure of oxygen during sputtering is kept at 0.5 mTorr and the deposition time is shorter than 15 min. So it is impossible that this thick SiO<sub>2</sub> layer comes from the oxidation of the Si substrate by reacting with the oxygen molecule under such a low thermal budget and short period of time.

In order to investigate the origin of interfacial SiO<sub>2</sub>, optical emission spectroscopy (OES) was employed to detect the chemical state in sputter chamber during film deposition. Figure 6 shows the OES spectrums for various gas conditions. Only the O radical instead of the O2 radical is detected in the sputtering chamber, while in a typical O<sub>2</sub> plasma system, the  $O_2$  radical is the main radical detected.<sup>28</sup> Based on the observation, an O-radical enhanced oxidation model is proposed to explain the thick interfacial oxide layer. The injected oxygen molecules are excited into ions and radicals. The oxygen related species in the plasma system may include O ion, O<sub>2</sub> ion, O radical, O<sub>2</sub> radical, etc. O<sub>2</sub> radicals may collide with the other particles and decompose into O radicals and/or O ions. Some O radicals and O2 radicals diffuse randomly to the Si surface and form an interfacial oxide layer at the initial deposition stage. Ions are accelerated toward target and after bombarding the target, all of the O<sub>2</sub> ions decompose into O ions or O radicals. Some reflected O radicals move toward wafers with high energy. Because the

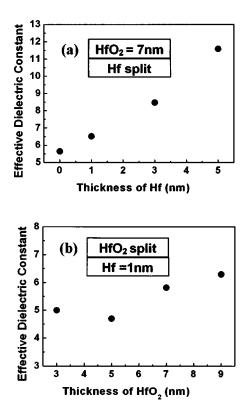

FIG. 7. Effective dielectric constant as a function of the thickness of (a) bottom Hf layer and (b) upper  $HfO_2$  layer.

O radical has a small radius and is highly reactive, it penetrate through the  $HfO_2/Hf$  stack rapidly and during the penetration, it not only oxidized the bottom Hf layer but also reacts with the Si substrate to form SiO<sub>2</sub>. Therefore, a very thick SiO<sub>2</sub> layer is formed during the reactive sputtering process. The oxidation due to the other O-contained species cannot be ruled out totally. Since O radical has the highest activity and the intensity of O radical is much higher than the other species, it is believed that O-radicals play a major role.

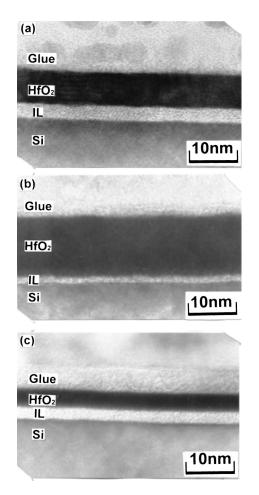

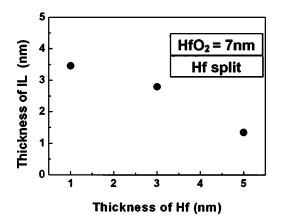

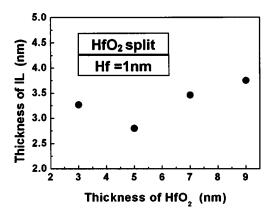

Based on the mechanism of the formation of a thick interfacial SiO<sub>2</sub>, a series of HfO<sub>2</sub>/Hf stack structures are examined to reveal the efficiency of the bottom Hf layer on the reduction of interfacial SiO<sub>2</sub>. Figures 7(a) and 7(b) show the effective K value as a function of thickness of bottom Hf layer and of thickness of upper HfO<sub>2</sub> layer, respectively. For the same thickness of top HfO<sub>2</sub> layer, a thicker Hf layer results in a higher effective K value. On the other hand, for the same thickness of the bottom Hf layer, a thicker HfO<sub>2</sub> layer results in lower effective K value. Because the final thickness of the dielectric is different for different samples, the improvement of the effective K value may be due to the reduction of the interfacial oxide layer or simply due to the decrease of the thickness percentage of the interfacial oxide layer. Figures 8(a), 8(b), and 8(c) show the cross-sectional TEM micrographs of samples with a HfO<sub>2</sub>/Hf stack of 7 nm/1 nm (sample H71), 7 nm/5 nm (sample H75), and 3 nm/1 nm (sample H31), respectively. The interfacial layer thickness depends on the HfO2/Hf stack structure. The correlation between the interfacial layer thickness and the bottom Hf thickness with the same upper HfO<sub>2</sub> thickness is shown in Fig. 9. By increasing the bottom Hf thickness to 5

FIG. 8. Cross-sectional TEM micrographs of samples (a) H71, (b) H75, and (c) H31.

nm, the thickness of the interfacial oxide layer can be reduced to 1.3 nm, which is the same as that observed in the sample with only a Hf layer (H03). This phenomenon implies that a 5-nm-thick Hf is necessary to block the diffusion of O radicals during the reactive sputtering of HfO<sub>2</sub>. The origin of the 1–1.5-mn-thick interfacial oxide layer is postulated to the surviving oxygen in the chamber or the traced oxygen impurity in Ar gas.

FIG. 9. Interfacial  $SiO_2$  layer thickness as a function of bottom Hf thickness with the same upper HfO<sub>2</sub> thickness.

FIG. 10. Interfaical SiO<sub>2</sub> layer thickness as a function of upper  $HfO_2$  thickness with the same bottom Hf thickness.

Correlation between the interfacial layer thickness and the upper  $HfO_2$  thickness is shown in Fig. 10. Similar interfacial SiO<sub>2</sub> thickness of about 3–4 nm was observed. This result indicates that the growth of the interfacial oxide layer occurs at the early stage of  $HfO_2$  deposition. With the increase of  $HfO_2$  thickness, oxidation is blocked.

#### CONCLUSION

In this work, the formation of the interfacial  $SiO_2$  layer at the HfO<sub>2</sub>/Si interface was studied comprehensively. It is observed that using the physical vapor deposition technique, it is difficult to totally eliminate the formation of the interfacial SiO<sub>2</sub> layer. During reactive sputtering deposition of the HfO<sub>2</sub> layer, an interfacial SiO<sub>2</sub> layer thicker than 3 nm would be grown. Such an unusual thick SiO<sub>2</sub> layer is formed due to the enhanced oxidation of O radicals generated in the sputtering chamber. Adoption of a two-step deposition method, the thickness of interfacial SiO<sub>2</sub> layer can be reduced only if the bottom Hf layer is thicker than 5 nm. However, the reduction of the effective oxide thickness would be limited. Reoxidation of the Hf film sounds like a better choice. A 1.0–1.5-nm-thick interfacial SiO<sub>2</sub> layer is still observed. This implies that the traced oxygen in the sputtering chamber plays a critical role in the formation of the interfacial layer. To conclude, reactive sputtering is not a good method to prepare a HfO<sub>2</sub> layer with a negligible interfacial  $SiO_2$  layer. Reoxidation of the Hf film is a better choice, but the oxygen content in the sputtering chamber must be well controlled.

#### ACKNOWLEDGMENTS

This work was supported by the National Science Council, R.O.C., under the Contract No. NSC-90-2215E-009-064. Samples were processed in National Nano Device Laboratories, R.O.C.

- <sup>1</sup>B. Yu, H. Wang, C. Riccobene, Q. Xiang, M. R. Lin, Symp. on VLSI Tech. Dig. 2000, p. 90.

- <sup>2</sup> *The International Technology Roadmap for Semiconductors* (Semiconductor Industry Association, Sematech, Austin, 2001).

- <sup>3</sup>K. A. Ellis and R. A. Buhrman, Appl. Phys. Lett. 74, 967 (1999).

- <sup>4</sup>K. A. Ellis and R. A. Buhrman, J. Electrochem. Soc. 145, 2068 (1998).

[This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to ] IP:

- <sup>5</sup>H. Yang and G. Lucovsky, Tech. Dig. Int. Electron Devices Meet. **1999**, 245 (1999).

- <sup>6</sup>C. A. Billmann et al., Mater. Res. Soc. Symp. Proc. 567, 409 (1999).

- <sup>7</sup>R. D. Shannon, J. Appl. Phys. **73**, 348 (1993).

- <sup>8</sup>H. F. Luan, S. J. Lee, C. H. Lee, S. C. Song, Y. L. Mao, Y. Senzaki, D. Roberts, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. **1999**, 141 (1999).

- <sup>9</sup>D. Park, Y.-C. King, Q. Lu, T.-J. King, C. Hu, A. Kalnitsky, S.-P. Tay, and C.-C. Cheng, IEEE Electron Device Lett. **19**, 441 (1998).

- <sup>10</sup>Z. J. Luo, Xin Guo, T. P. Ma, and T. Tamagawa, Appl. Phys. Lett. **79**, 2803 (2001).

- <sup>11</sup> A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, Symp. VLSI Tech. Dig. 1999, p. 135.

- <sup>12</sup>Y. H. Wu, M. Y. Yang, A. Chin, W. J. Chen, and C. M. Kwei, IEEE Electron Device Lett. **21**, 341 (2000).

- <sup>13</sup>B. Cheng et al., IEEE Electron Device Lett. 46, 1537 (1999).

- <sup>14</sup>J. Robertson, MRS Bull. 27, 217 (2002).

- <sup>15</sup>H. F. Luan, S. J. Lee, S. C. Song, Y. L. Mao, Y. Senzaki, D. Roverts, and D. L. Kwong, Tech. Dig. - Int. Electron Devices Meet. **1999**, 141 (1999).

- <sup>16</sup>B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, Tech. Dig. - Int. Electron Devices Meet. **1999**, 133 (1999).

- <sup>17</sup>S. P. Muraka and C. C. Chang, Appl. Phys. Lett. **37**, 639 (1980).

- <sup>18</sup>Y. Kim et al., Tech. Dig. Int. Electron Devices Meet. 2001, 455 (2001).

- <sup>19</sup>L. Kang, Y. Jon, K. Onishi, B. H. Lee, W. J. Qi, R. Nieh, S. Gopalan, and J. C. Lee, Symp. VLSI Tech. Dig., 2000, p. 44.

- <sup>20</sup> H. J. Cho, C. S. Kang, K. Onishi, S. Gopalan, R. Nieh, R. Choi, E. Dharmarajan, and J. C. Lee, Tech. Dig. Int. Electron Devices Meet. **2001**, 655 (2001).

- <sup>21</sup>S. J. Lee, H. F. Luan, W. P. Bai, C. H. Lee, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. **2000**, 31 (2000).

- <sup>22</sup>C. Hobbs *et al.*, Tech. Dig. Int. Electron Devices Meet. **2001**, 651 (2001).

- <sup>23</sup> E. P. Gusev *et al.*, AVS Topical Conf. on Atomic Layer Deposition, May 14, 2001.

- <sup>24</sup> M. Ritala and M. Leskela, in *Handbook of Thin Film Materials*, edited by H. S. Nalwa (Academic, New York, 2001), Vol. 1, Chap. 2.

- <sup>25</sup> W. Zhu, T. P. Ma, T. Tamagawa, Y. Di, J. Kim, R. Carruthers, M. Gibson, and T. Furukawa, Tech. Dig. - Int. Electron Devices Meet. **2001**, 463 (2001).

- <sup>26</sup>Z. J. Luo, T. P. Ma, E. Cartier, M. Copel, T. Tamagawa, and B. Halpern, Symp. VLSI Tech. Dig. 2001, p. 135.

- <sup>27</sup> A. Callegari, E. Cartier, M. Gribelyuk, H. F. Okorn-Schmidt, and T. Zabel, J. Appl. Phys. **90**, 6466 (2001).

- <sup>28</sup> B. H. Lee, L. Kang, R. Nieh, W. J. Qi, and J. C. Lee, Appl. Phys. Lett. **76**, 1926 (2000).

- <sup>29</sup>C. S. Kang, H.-J. Cho, K. Onishi, R. Chio, R. Nief, S. Goplan, S. Krishnan, and Jack C. Lee, Symp. VLSI Tech. Dig., 2002, p. 146.

- <sup>30</sup>T. K. Kang (private communication).