# A Novel Germanium Doping Method for Fabrication of High-Performance P-Channel Poly- $Si_{1-x}Ge_x$ TFT By Excimer Laser Crystallization

Ting-Kuo Chang, Fang-Tsun Chu, Ching-Wei Lin, Chang-Ho Tseng, and Huang-Chung Cheng

Abstract—In this letter, a novel process for fabricating p-channel poly-Si $_{1-x}$ Ge $_x$  thin-film transistors (TFTs) with high-hole mobility was demonstrated. Germanium (Ge) atoms were incorporated into poly-Si by excimer laser irradiation of a-Si $_{1-x}$ Ge $_x$ /poly-Si double layer. For small size TFTs, especially when channel width/length (W/L) was less than 2  $\mu$ m/2  $\mu$ m, the hole mobility of poly-Si $_{1-x}$ Ge $_x$  TFTs was superior to that of poly-Si TFTs. It was inferred that the degree of mobility enhancement by Ge incorporation was beyond that of mobility degradation by defect trap generation when TFT size was shrunk to 2  $\mu$ m/2  $\mu$ m. The poly-Si $_{0.91}$ Ge $_{0.09}$  TFT exhibited a high-hole mobility of 112 cm²/V-s, while the hole mobility of the poly-Si counterpart was 73 cm²/V-s.

Index Terms—Excimer laser annealing, Ge doping, poly-Si  $_{1-x}{\rm Ge}_x$  thin-film transistor (TFT).

### I. INTRODUCTION

OW-TEMPERATURE poly-crystalline silicon (LTPS) thin-film transistors (TFTs) have been widely studied because of their potential applications in high-performance displays, such as AMLCDs and AMOLEDs [1], [2]. Active matrix displays with integrated circuits on a single-glass substrate can be implemented by high-mobility LTPS TFTs [3]. To achieve high mobility for high-speed operation, excimer laser crystallization (ELC) has been widely used to fabricate LTPS TFTs [4], [5]. Even though the mobility of ELC poly-Si TFT can meet the requirements for many circuit applications, further enhancement of mobility is necessary for high-level system integration. Essentially, germanium (Ge) incorporated in silicon (Si) (i.e.,  $Si_{1-x}Ge_x$ ) cannot only lower the process thermal budget but also promotes the carrier mobility. Hence,  $Si_{1-x}Ge_x$  seems to be a potential material for the active layer of a TFT [6]-[8]. According to the results reported by Tsai et al., poly- $Si_{1-x}Ge_x$  TFTs have been found to have higher mobility than similarly processed poly-Si TFTs [8]. However, most of the poly- $Si_{1-x}Ge_x$  TFTs were fabricated by using conventional solid-phase crystallization [9], [10]. Only a few studies have been conducted for the ELC poly- $Si_{1-x}Ge_x$  TFT [11].

In this letter, we describe a novel laser process for producing p-channel high-mobility poly- $Si_{1-x}Ge_x$  TFTs. Ge atoms were incorporated into poly-Si by laser irradiation of the a- $Si_{1-x}Ge_x$

Manuscript received November 25, 2002; revised January 13, 2003. The review of this letter was arranged by Editor J. Sin.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TCSI.2003.811423

/poly-Si double layer. The grain size of the active layer was almost unaltered after Ge doping by excimer laser irradiation. We also investigate the effects of Ge atomic concentration and device dimension on the performance of the poly-Si<sub>1-x</sub>Ge $_x$  TFTs.

## II. DEVICE FABRICATION

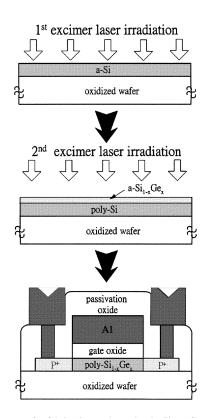

Fig. 1 illustrates the key processes for fabrication of the poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. At first, a-Si with a 500-Å thickness was deposited on oxidized Si wafers by LPCVD at 550 °C. Then, the a-Si was crystallized by a krypton fluorine (KrF) excimer laser irradiation at room temperature with optimal laser conditions, i.e., a shot density of 100 shots per area (99% overlapped) and energy density of 280 mJ/cm<sup>2</sup>. To obtain poly- $Si_{1-x}Ge_x$ , 100-Å-thick a- $Si_{1-x}Ge_x$  with 23% and 33% Ge atomic concentration were deposited on the ELC poly-Si by LPCVD at 450 °C, respectively. The a-Si<sub>1-x</sub>Ge<sub>x</sub> was then subjected to the second excimer laser irradiation with a shot density of 10 shots per area (90% overlapped). The second laser energy density was 240 mJ/cm<sup>2</sup>, which was controlled in the partially melting region of poly-Si thin film. The Ge atoms were diffused naturally into the underneath poly-Si during the laser irradiation. The RBS analysis revealed that the Ge atomic concentrations in the eventual poly- $Si_{1-x}Ge_x$ were 5% and 9%, respectively. In addition, according to the AES analysis results, the atomic concentration of Ge atom was a little higher at the film surface than in the bulk of the poly- $Si_{1-x}Ge_x$  thin film after the second laser irradiation. After defining the active layer, a 1000-Å-thick TEOS gate oxide and 3000-Å-thick aluminum (Al) were deposited by PECVD and thermal evaporation, respectively. RIE was then carried out to form the gate electrode. A self-aligned  $B^+$  implantation with a dosage of  $5 \times 10^{15}$  cm<sup>-2</sup> was performed to form source and drain regions. Dopant activation was carried out by excimer laser irradiation with 95% overlap at room temperature after depositing a 3000-Å-thick oxide as a passivation layer. Finally, contact opening and metallization were performed to complete the fabrication of the poly- $Si_{1-x}Ge_x$  TFTs.

### III. RESULTS AND DISCUSSION

The key process for fabricating the proposed poly- $Si_{1-x}Ge_x$  TFTs is to dope Ge into poly-Si without degrading the grain structure. During the second laser irradiation, the Ge would diffuse into the underneath poly-Si layer due to the high-diffusion coefficient of Ge in melting silicon and the Ge concentration gradient. When the second laser irradiation was performed, laser energy density was carefully controlled so that the poly-Si

Fig. 1. Key process for fabricating p-channel poly- $Si_{1-x}Ge_x$  TFTs.

was partially melted. These grains could vertically regrow from the unmelted poly-Si. As a result, the grain size of poly-Si<sub>1-x</sub>Ge<sub>x</sub> was almost identical to that of poly-Si after the Ge doping process [12]. The grain sizes of the poly-Si and poly-Si<sub>1-x</sub>Ge<sub>x</sub> inspected by a scanning electron microscope (SEM) were both about 5000 Å. Thus, the direct-laser crystallization of a-Si<sub>1-x</sub>Ge<sub>x</sub>, resulting in small grain size poly-Si<sub>1-x</sub>Ge<sub>x</sub> accompanied by serious Ge segregation due to the different melting points between Si and Ge, can also be avoided.

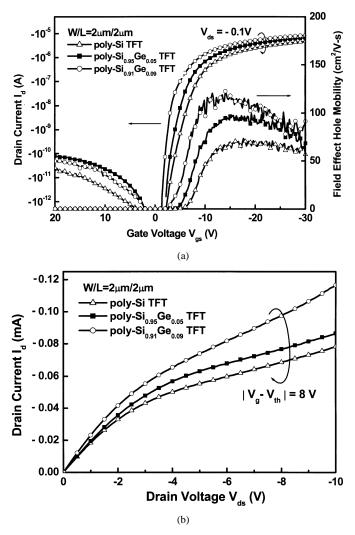

Fig. 2(a) shows the transfer characteristics of poly-Si and poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. Several important electrical characteristics are summarized in Table I. The hole mobility of poly- $Si_{1-x}Ge_x$  TFTs is higher than that of poly-Si TFTs. The higher hole mobility of poly- $Si_{1-x}Ge_x$  TFTs might be attributed to the incorporation of Ge atoms [8]. However, the leakage current of poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs was larger than that of poly-Si TFTs. The leakage current of poly-Si TFTs is related to the trap-assisted tunneling of energetic carriers [13]. Therefore, the high leakage current should result from the narrower bandgap of poly- $Si_{1-x}Ge_x$  and slight defect generation by Ge doping. Fig. 2(b) shows the output characteristics of poly-Si and poly- $Si_{1-x}Ge_x$  TFTs. In order to avoid the threshold voltage difference, the applied gate driving voltage was keeping at a constant value of  $|V_g - V_{\rm th}| = 8$  V. The output current increases with the Ge concentration, which is an evidence of mobility enhancement by Ge doping.

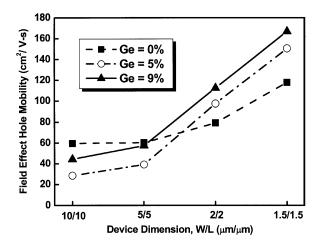

Fig. 3 shows the mobility variation with different device dimensions and Ge concentrations. Twenty TFTs were measured and the mobilities were averaged for each device dimension. The poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs exhibited degraded hole mobility when W/L was above 5  $\mu$ m/5  $\mu$ m. As the device dimension

Fig. 2. I-V curves of poly-Si TFT and poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. (a) Typical transfer characteristics. (b) Output characteristics.

# TABLE I SUMMARY OF ELECTRICAL CHARACTERISTICS OF POLY-SI AND POLY-Si\_1\_x Ge\_x TFTS WITH $W/L=2~\mu \text{m}/2~\mu \text{m}$ . The Threshold Voltage Was Defined at $I_d=-(W/L)\times 10^{-8}$ A and $V_{\text{cls}}=-0.1~\text{V}$ . The Maximum Field Effect Mobility Was Extracted From the Transformation of the Threshold Processing Type 1000 and 1

Transconductance in the Linear Region at  $V_d=0.1~{

m V}.$  The  $I_{

m on}/I_{

m off}$  Current ratio was Defined at  $V_d=-5~{

m V}$

|                                           | Poly-Si             | Poly-Si <sub>0.95</sub> Ge <sub>0.05</sub> | Poly-Si <sub>0.91</sub> Ge <sub>0.09</sub> |

|-------------------------------------------|---------------------|--------------------------------------------|--------------------------------------------|

| Threshold Voltage (V)                     | -5.2                | -4.25                                      | -2.5                                       |

| Subthreshold Swing (mV/dec)               | 867                 | 633                                        | 461                                        |

| Field Effect Mobility<br>(cm²/V-s)        | 73                  | 99                                         | 112                                        |

| Maximum I <sub>on</sub> /I <sub>off</sub> | 4.4x10 <sup>7</sup> | 2.6x10 <sup>7</sup>                        | 4.5x10 <sup>7</sup>                        |

was reduced to  $W/L=2~\mu m/2~\mu m$ , the poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs showed higher hole mobility in comparison with the poly-Si TFTs. It was inferred that the degree of mobility enhancement by Ge incorporation was beyond that of mobility degradation by defect trap generation when TFT size was reduced to  $2~\mu m/2~\mu m$ . After the second laser irradiation, a portion of Ge atoms would segregate to grain boundaries due to the lower melting point of Ge compared to Si. The segregated Ge atoms

Fig. 3. Field effect mobility variation for different device dimensions and Ge atomic concentrations.

resulted in a higher trap state density in grain boundaries, which acted as potential barriers during carrier transport. Therefore, the device characteristics were degraded, even though the hole mobility was enhanced by Ge atom incorporation. However, when the device dimension was shrunk, carriers suffered from less defect scattering at grain boundaries in the channel region. Consequently, the effect of mobility enhancement by Ge incorporation became dominant. Therefore, the poly-Si $_{1-x}$ Ge $_x$ TFT exhibited higher mobility than the poly-Si TFT only for small-dimension devices.

# IV. CONCLUSIONS

The poly- $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  TFTs with high-hole mobility were successfully fabricated using a novel laser doping process. During the Ge doping process, no deterioration was found in the original grain size of the poly-Si thin film. The poly- $\mathrm{Si}_{0.95}\mathrm{Ge}_{0.05}$  and poly- $\mathrm{Si}_{0.91}\mathrm{Ge}_{0.09}$  TFTs both exhibited higher mobilities than the poly-Si TFTs as the device dimension was reduced. The proposed new process is attractive for future small-dimension TFTs.

### REFERENCES

- [1] S. D. Brotherton, J. R. Ayres, M. J. Edwards, C. A. Fisher, C. Glaister, J. P. Gowers, D. J. McCulloch, and M. Trainor, "Laser crystallized poly-Si TFT's for AMLCD's," *Thin Solid Films*, vol. 338, pp. 188–195, 1999.

- [2] M. Kimura, I. Yudasaka, S. Kanbe, H. Kobayashi, H. Kiguchi, S. Seki, S. Miyashita, T. Shimoda, T. Ozawa, K. Kitawada, T. Nakazawa, W. Miyazawa, and H. Ohshima, "Low-temperature polysilicon thin-film transistor driving with integrated driver for high-resolution light emitting polymer display," *IEEE Trans. Electron Devices*, vol. 46, pp. 2282–2288, Dec. 1999.

- [3] T. Nishibe, "Low-temperature poly-Si TFT by excimer laser annealing," in *Proc. Mat. Res. Soc. Symp.*, vol. 685E, 2001, pp. D6.1.1–D6.1.5.

- [4] H. Kuriyama, S. Kiyama, S. Noguchi, T. Kuwahara, S. Ishida, T. Nohda, K. Sano, H. Iwata, H. Kawata, M. Osumi, S. Tsuda, S. Nakano, and Y. Kuwano, "Enlargement of poly-Si film grain size by excimer laser annealing and its application to high-performance poly-Si thin film transistor," *Jpn. J. Appl. Phys.*, vol. 30, pp. 3700–3703, 1991.

- [5] A. Kohno, T. Sameshima, N. Sano, M. Sekiya, and M. Hara, "High performance poly-Si TFTs fabricated using pulsed laser annealing and remote plasma CVD with low temperature processing," *IEEE Trans. Electron Devices*, vol. 42, pp. 251–257, Feb. 1995.

- [6] T. J. King, K. C. Saraswat, and J. R. Pfiester, "PMOS transistors in LPCVD polycrystalline silicon-germanium films," *IEEE Electron Device Lett.*, vol. 12, pp. 584–586, Nov. 1991.

- [7] J. B. Rem, M. C. V. de Leuw, J. Holleman, and J. F. Verweij, "Furnace and rapid thermal crystallization of amorphous Ge<sub>x</sub>Si<sub>1-x</sub> and Si for thin film transistors," *Thin Solid Films*, vol. 296, pp. 152–156, 1997.

- [8] A. J. Tang, J. A. Tsai, and R. Reif, "A novel poly-silicon-capped poly-silicon-germanium thin film transistor," in *IEDM Tech. Dig.*, 1995, pp. 513–516.

- [9] T. J. King and K. C. Saraswat, "Polycrystalline silicon-germaninum thin-film transistors," *IEEE Trans. Electron Devices*, vol. 41, pp. 1581–1591, Sept. 1994.

- [10] S. Jurichich, T. J. King, K. C. Saraswat, and J. Mehlhaff, "Low thermal budget polycrystalline silicon-germanium thin-film transistors fabricated by rapid thermal annealing," *Jpn. J. Appl. Phy.*, vol. 33, p. L1139, 1994.

- [11] S. M. Cho, J. A. Ahn, and O. Kim, "Fabrication of laser-annealed poly-TFT by forming a Si<sub>1-x</sub>Ge<sub>x</sub> thermal barrier," *IEEE Electron Device Lett.*, vol. 22, pp. 121–123, Mar. 2001.

- [12] H. J. Kim and J. S. Im, "Multiple pulse irradiation effects in excimer laser-induced crystallization of amorphous si films," in *Proc. Mat. Res.* Soc. Symp., vol. 321, 1994, pp. 665–670.

- [13] K. R. Olasupo and M. K. Hatalis, "Leakage current mechanism in submicro polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 46, pp. 1218–1223, June 1999.