# A SPICE-Compatible Model for Nanoscale MOSFET Capacitor Simulation Under the Inversion Condition

Ting-wei Tang, Fellow, IEEE, and Yiming Li, Member, IEEE

**SPICE-compatible** charge nanoscale MOSFETs is proposed. Based on the solution of Schrödinger-Poisson (S-P) equations, the developed compact charge model is optimized with respect to: 1) the position of the charge concentration peak; 2) the maximum of the charge concentration; 3) the total inversion charge sheet density; and 4) the average inversion charge depth, respectively. This model can predict inversion layer electron density for various oxide thicknesses and applied voltages. Compared to the S-P results, our model prediction is within 5% of accuracy. Application of this charge quantization model to the C-V measurement produces an excellent agreement. This compact model has continuous derivatives and is therefore amenable to a device simulator. It can also be easily incorporated into circuit simulator for modeling ultrathin oxide MOSFET *C*–*V* characteristics.

Index Terms—C-V curve, compact charge model, device and circuit simulation, MOSFETs, quantum correction, Schrödinger—Poisson.

# I. INTRODUCTION

S THE feature size of MOS devices shrinks for higher density and performance, the thickness of silicon oxide also scales down. In aggressively scaled MOSFETs, the thickness of oxide in a MOS capacitor can be as thin as 0.8 nm [1] prevented only by the leakage tunneling current. For the oxide thickness ( $T_{\rm ox}$ ) of  $1\sim3$  nm and the applied gate voltage ( $V_G$ ) of  $0.5\sim1.5$  V, the displacement of the inversion carrier density away from the Si–SiO<sub>2</sub> interface due to the quantization effect cannot be neglected [2]. Thus, any accurate calculation of the inversion-layer capacitance must take this quantization effect into consideration.

The most accurate way of incorporating the quantum effect in the inversion layer is to solve the coupled Schrödinger-Poisson (S-P) equations subject to an appropriate boundary condition at the Si-SiO<sub>2</sub> interface [3]. This can be done without difficulties in solving the S-P equations in one dimension, but the S-P approach is not amenable to a realistic device simulator such as a simple compact model used in the SPICE. Other approaches such as the density gradient method [3], [4] and the effective

Manuscript received June 8, 2002; revised October 10, 2002. This work was supported in part by the National Science Foundation under Grant ECS-0120128, the National Science Council of Taiwan under Contract NSC 91–2112-M-317–001, and the 2002 Research Fellowship Award of the Pan Wen-Yuan Foundation in Taiwan.

T.-W. Tang is with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst, MA 01003 USA (e-mail: ttang@ecs.umass.edu)

Y. Li is with the National Nano Device Laboratories, Hsinchu 300, Taiwan. He is also with the Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymli@faculty.nctu.edu.tw).

Digital Object Identifier 10.1109/TNANO.2002.807389

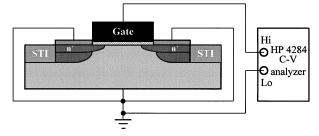

Fig. 1. Cross-section view of the nanoscale MOSFET and C-V curves measurement configuration.

potential method [5], [6] also suffer from the same disadvantage—computationally it is still excessive and physically the method is not very transparent.

In this paper, we have successfully developed a SPICE-compatible model feasible for nanoscale MOSFET capacitor simulation. The model is a generalization of an analytical model proposed by Hänsch  $et\ al.$  many years ago [7]. The solution of S-P equations is utilized to construct the model, where four optimization constraints: 1) the position of the charge concentration peak; 2) the maximum of the charge concentration; 3) the total inversion charge sheet density; and 4) the average inversion charge depth are used as criteria for the model parameter extraction. The model parameters are expressed as a function of  $T_{\rm ox}$  and  $V_G$  for the purpose of simulating nanoscale MOSFET capacitances. For other applications, they can be also expressed in terms of the surface electric field and the oxide thickness.

## II. MODEL CONSTRUCTION AND RESULT

First, a poly-oxide-silicon system as shown in Fig. 1 is simulated using the drift-diffusion (D-D) approximation [8], [9]. The D-D equations are solved self-consistently with the S-P equations. The S-P equations are assumed to have no wave penetration at the Si–SiO $_2$  interface [10]. The S-P equations are discretized by the finite difference method (the so-called box method). After the discretization, the corresponding matrix eigenvalue problem and the system of nonlinear algebraic equations are solved iteratively to obtain a self-consistent solution. More than 16 subbands are used in the Schrödinger equation solver. The chosen  $T_{\rm ox}$  varies from 1 to 3 nm and the applied  $V_G$  ranges from 0.2 to 2 V. The calculated inversion-layer charge densities are then cast into the form

$$n_{\text{QM}} = n_{\text{CL}} a_0 \left[ 1 - \exp\left( -a_1 \left( \frac{x}{\lambda_{\text{th}}} \right)^2 + a_2 \left( \frac{x}{\lambda_{\text{th}}} \right)^4 - a_3 \left( \frac{x}{\lambda_{\text{th}}} \right)^6 \right) \right]$$

(1)

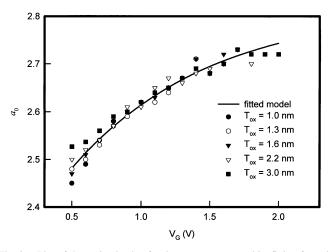

Fig. 2. Plot of the optimal value for the parameter  $a_0$  and its fitting formula for various  $T_{\rm ox}$  and different  $V_G$ .

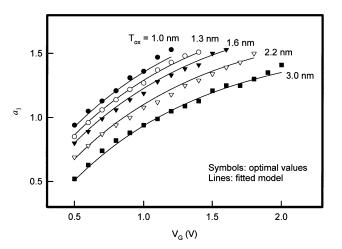

Fig. 3. Plot of the optimal value for the parameter  $a_1$  and its fitting formula for various  $T_{\rm ox}$  and different  $V_G$ .

where  $n_{\rm CL}$  is the classical electron density solved from the Poisson equation and  $\lambda_{\rm th}=(\hbar/2m^*k_BT)^{1/2}$  is the thermal wavelength. Using a generic algorithm, the four model parameters  $a_0$ ,  $a_1$ ,  $a_2$ , and  $a_3$  are optimized to best fit the self-consistent S-P solution for all  $T_{\rm ox}$ 's and  $V_G$ 's. The fitting accuracy of these parameters is based on the optimization with respect to the aforementioned four constraints. The average inversion charge depth is defined as

$$\langle x \rangle = \frac{\int_0^\infty x n(x) dx}{\int_0^\infty n(x) dx}.$$

(2)

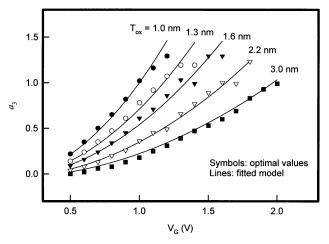

The results of these parameters fittings are shown in Figs. 2–4. As seen in Fig. 2, the plots of  $a_0$ 's versus  $V_G$  are almost independent of  $T_{\rm ox}$ . Fig. 3 shows that the dependence of  $a_1$ 's on  $V_G$  for different  $T_{\rm ox}$  is similar; all have a decreasing slope. Note that  $a_1$  increases as  $T_{\rm ox}$  is decreased. Not shown are plots of  $a_2$ 's which are for all practical purpose nearly zero. Shown in Fig. 4 are plots of  $a_3$ 's versus  $V_G$ , all having an increasing slope opposite to the shape of  $a_1$ 's. Also noticed is that all  $a_3$ 's converge to zero at a very low  $V_G$ , implying that  $a_3$  is only associated with a higher-order quantum correction.

Fig. 4. Plot of the optimal value for the parameter  $a_3$  and its fitting formula for various  $T_{\rm ox}$  and different  $V_G$ .

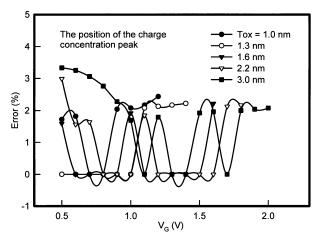

Fig. 5. Error plots of the position of the charge concentration peak versus  $V_G$  for various  $T_{\rm ox}$ .

After optimization, these parameters are empirically fitted as a function of  $V_G$  and  $T_{\rm ox}$  as follows:

$$a_0 = 2.82 - 0.555 \exp(-V_G)$$

(3)

$$a_1 = 2.22 - 1.79 \exp(-V_G) - 0.21T_{\text{ox}}$$

(4)

$$a_3 = -0.00467 + 1.048 \frac{V_G^2}{T_{\text{ox}}^{1.23}}$$

(5)

where  $V_G$  is in volts and  $T_{\rm ox}$  is in nanometers. The model parameters given in (3)–(5) are based on a p-type substrate with  $N_A=10^{17}~{\rm cm}^{-3}$ . For other substrate dopings,  $V_G$  should be adjusted by an amount equal to a shift in the threshold voltage due to the change in  $N_A$ . However, this adjustment is usually very small (< 0.13 V). The accuracy of the model inversion-layer charge density given by (1), (3) – (5) compared to the S-P solution is very good. In terms of the four criteria mentioned above, the accuracy is within 5%.

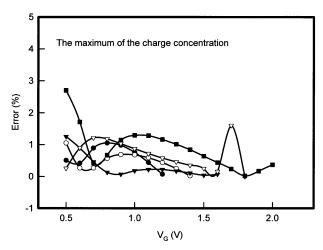

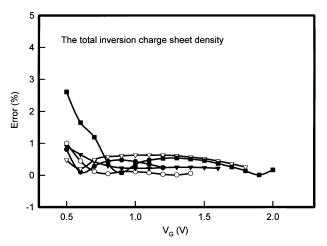

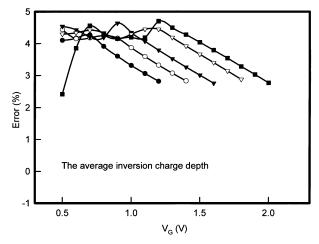

Shown in Figs. 5–8 are, respectively, errors between the fitted a's formula and the S-P solution against  $V_G$  for each optimization criterion. In Figs. 5 and 6, it is shown that the error of the position of the charge concentration peak is less than 3.5% and the error of the maximum of the charge concentration is less than 3%, respectively. Fig. 7 shows that the error of the total inversion charge sheet density between our model and the S-P equation is

Fig. 6. Error plots of the maximum of the charge concentration versus  $V_G$  for various  $T_{\rm ox}$ .

Fig. 7. Error plots of the total inversion charge sheet density versus  $V_G$  for various  $T_{\rm ox}$ .

less than 3%. Fig. 8 shows that the error of the average inversion charge depth is within 2%–5%. For the doping concentration  $N_A$  varying from  $10^{16}~\rm cm^{-3}$  to  $10^{18}~\rm cm^{-3}$ , the four errors versus  $V_G$  are also estimated with the same fitted a's formula. We have found that the variation of errors are all within 6% and this maximum error of the average inversion charge depth occurred at  $N_A = 10^{16}~\rm cm^{-3}$ ,  $T_{\rm ox} = 3.0~\rm nm$ , and  $V_G = 0.5~\rm V$ . For a MOSFET with the Gaussian and low–high doping profiles, we have also found that the error trend is similar to that of uniform doping and that the largest error fluctuation (6.7% for Gaussian doping profile) occurs under low doping level ( $N_A = 10^{16}~\rm cm^{-3}$ ), thicker oxide thickness ( $T_{\rm ox} = 3.0~\rm nm$ ), and low gate bias ( $V_G = 0.5~\rm V$ ) conditions.

Finally, for other applications such as a two-dimensional (2-D) simulation, it is more conventient to express the coefficients:  $a_0$ ,  $a_1$ , and  $a_3$  in terms of the surface electric field  $E_s$  and the oxide thickness  $T_{\rm ox}$

$$a_0 = 2.11 + 1.3 \times 10^{-6} E_s^{2/3} + 0.085 T_{\text{ox}}$$

(6)

$$a_1 = -0.96 + 4.2 \times 10^{-3} E_s^{1/3} \tag{7}$$

$$a_3 = 2.13 \times 10^{-8} \left( E_s^{1/2} - 6500 \right)^2$$

(8)

where the  $T_{\rm ox}$  is in nm and the  $E_s$  in kV/cm is self-consistently computed with the D-D model.

Fig. 8. Error plots of the average inversion charge depth versus  $V_G$  for various  $T_{\mathrm{ox}}$ .

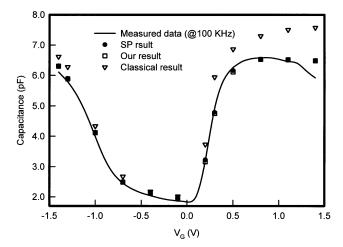

Fig. 9. Comparison of the simulated and measured *C–V* curves for the proposed SPICE-compatible model and the S-P model.

# III. APPLICATION TO PREDICTION OF C-V CHARACTERISTICS

As an application, we have applied our compact quantum correction model for the inversion charge to the calculation of  $C\textsc-V$  curves. A  $20\times20~\mu\text{m}^2$  N-MOSFET with  $T_{\rm OX}=1.6$  nm is fabricated and is measured for the  $C\textsc-V$  curve. The developed model is used to analyze the  $C\textsc-V$  data of the MOSFET sample at a frequency of 100~kHz as shown in Fig. 1. The total capacitance consists of three components in series connection, the poly-gate capacitance ( $C_{\rm poly}$ ), the gate-oxide capacitance ( $C_{\rm OX}=\epsilon_{\rm ox}/T_{\rm ox}$ , where  $\epsilon_{\rm ox}$  is oxide dielectric constant), and the surface capacitance ( $C_{\rm surf}$ ). The total capacitance C is thus given by [11], [12]

$$C = \left(\frac{1}{C_{\text{poly}}} + \frac{1}{C_{\text{ox}}} + \frac{1}{C_{\text{surf}}}\right)^{-1}.$$

(9)

The surface capacitance  $C_{\rm surf}=\partial Q_{\rm surf}/\partial \phi_s$ , where  $\phi_s$  is the surface potential, is computed by the Poisson equation. The surface charge  $Q_{\rm surf}$  consists of the inversion and depletion charge, and the computed  $n_{\rm QM}$  from (1) is integrated over the entire inversion layer to obtain the inversion charge sheet density. For the sample with 1.6-nm oxide thickness, the doping profile of the device is simulated and calibrated in our  $C\!-\!V$  curve calculation. The experimentally measured data is shown together with the classical and S-P results in Fig. 9. Our result almost coincides

with that of the S-P model as should be. The agreement with the experimental data is excellent except for  $V_G \geq 1.0$  V. This is expected as we have assumed zero penetration of the wavefunction into the oxide in our S-P equation solver. The deviation of the calculated result from the measured data indicates that there is a substantial tunneling through the oxide taking place at  $V_G \geq 1.0$  V.

### IV. CONCLUSION

Based on the S-P solutions, we have developed a compact model for correcting the classical inversion-layer charge distribution which agrees with the S-P solution within 5%. By inputting the classical charge density from the series expansion solution of Poisson's equation [13], [14] or the D-D-based simulator, together with the device oxide thickness and gate voltage, the proposed inversion-layer charge correction model calculates nanoscale MOSFET inversion charge explicitly, taking into consideration of the quantum effect. The application of this SPICE compatible model to the C-V measurement produces an excellent agreement. This inversion-layer charge correction model has continuous derivatives and therefore is amenable to a device simulator. It can also be easily incorporated into circuit simulator for modeling ultrathin oxide MOSFET *C*–*V* characteristics without impact on the computational time and data storage. We are currently extending this model to include leakage tunneling currents at high gate voltages.

### ACKNOWLEDGMENT

The author would like to thank the referees and the Associate Editor for valuable comments and suggestions.

# REFERENCES

- S. Song, H. Kim, J. Y. Yoo, J. H. Yi, W. S. Kim, N. I. Lee, K. Fujihara, H.-K. Kang, and J. T. Moon, "On the gate oxide scaling of high performance CMOS transistors," *IEDM. Tech. Dig.*, pp. 03-02.1-03-02-4, 2001

- [2] F. Stern and W. E. Howard, "Properties of semiconductor surface inversion layers in the electric quantum limit," *Phys. Rev.*, vol. 163, pp. 816–835, 1967.

- [3] M. G. Ancona, Z. Yu, W.-C. Lee, and R. W. Dutton, "Simulation of quantum confinement effects in ultra-thin-oxide MOS structures," *IEEE Trans. Computer-Aided Design*, vol. 11, pp. 1–17, May 1998.

- [4] M. G. Ancona, Z. Yu, R. W. Dutton, P. J. Vande Voorde, M. Cao, and D. Vook, "Density-gradient analysis of MOS tunneling," *IEEE Trans. Electron Devices*, vol. 47, pp. 2310–2319, Dec. 2000.

- [5] S. M. Ramey and D. K. Ferry, "Modeling of quantum effects in ultrasmall FD-SOI MOSFET's with effective potentials and three-dimensional Monte Carlo," *Physica B*, vol. 314, no. 1-4, pp. 350–353, Mar. 2002.

- [6] D. K. Ferry, "Simulation at the start of the new millennium: Crossing the quantum-classical threshold," *VLSI Design*, vol. 13, no. 1-4, pp. 155–161, 2001.

- [7] W. Hänsch, T. Vogelsang, R. Kircher, and M. Orlowski, "Carrier transport near the Si/SiO interface of a MOSFET," *Solid-State Electron.*, vol. 32, pp. 839–849, 1989.

- [8] X. Wang, "Quantum Correction to the Charge Density Distribution in Inversion Layers," M.S. thesis, Univ. Massachusetts, Amherst, 2001.

- [9] X. Wang and T.-W. Tang, "Comparison of three quantum correction models for the charge density in MOS inversion layers," J. Comput. Electron., submitted for publication.

- [10] S.-H. Lo, D. A. Buchanan, and Y. Taur, "Modeling and characherization of quantization, polysilicon depletion, and direct tunneling effects in MOSFET's with ultrathin oxides," *IBM J. Res. Dev.*, pp. 327–337, 1999

- [11] F. Stern, "Quantum properties of surface space-charge layers," CRC Crit. Rev. I, Solid State Sci., pp. 499–514, 1974.

- [12] K. Chen, G. Zhang, J. Duster, C. Hu, J. Huang, Z. Liu, and P. K. Ko, "MOSFET inversion layer capacitance model based on Fermi-Dirac statistics for wide temperature range," *Solid-State Electron.*, vol. 41, p. 507, 1997

- [13] T. N. Nguyen, "Small-geometry mos transistor: Physics and modeling of surface- and buried-channel MOSFET's," Ph.D. dissertation, Stanford Univ., Stanford, CA, 1984.

- [14] J. C. S. Woo, K. W. Terrill, and P. K. Vasudev, "Two-dimensional analytical modeling of very thin SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 37, pp. 1999–2006, Sept. 1990.

**Ting-wei Tang** (SM'70–F'99) received the B.S. degree in electrical engineering from the National Taiwan University, Taiwan, R.O.C. in 1957 and the M.Sc. and Ph.D degrees in engineering from Brown University, Providence, RI, in 1961 and 1964, respectively.

From 1964 to 1968, he was an Assistant Professor of Aerospace Engineering at the University of Connecticut, Storrs. In 1968, he joined the Electrical and Computer Engineering Department, University of Massachusetts, Amherst, as an Associate Pro-

fessor and was promoted to Professor in 1974. He was a Visiting Professor at Oxford University, Oxford, U.K., in 1975 and a Visiting Samsung Professor of Electronics Engineering at Seoul National University, Seoul, Korea, in the fall of 1990. During 1999–2000, he was a Research Chair at the National Center for High-Performance Computing, Hsinchu, Taiwan, R.O.C. His current research interest is in semiconductor device physics and numerical modeling of semiconductor devices. He teaches a graduate-level course in which students gain hands-on experience in developing an elementary device simulation software. He has published more than 100 journal articles and conference papers.

Dr. Tang served on the IEEE Admission and Advancement Committee (1974–1977), the Technical Program Committee of IEEE BCTM (1995–1998), and the Scientific Advisory Committee of ISSDT (1994–1995). He received an Outstanding Senior Faculty Award and an Outstanding Teaching Award from the College of Engineering, University of Massachusetts, in 1989 and 1991, respectively, and the Chancellor's Medal from the University of Massachusetts in 2000. He was a keynote speaker at the 1993 Symposium on Semiconductors Modeling and Simulation in Taipei, Taiwan, R.O.C. the 1995 Fourth International Seminar on Simulation of Devices and Technologies at Kruger National Park, South Africa, and the 1999 Semiconductor Technology CAD Workshop and Exhibition in Hsinchu, Taiwan, R.O.C.

Yiming Li (M'02) received the B.S. degrees in applied mathematics and electronics engineering, the M.S. degree in applied mathematics, and the Ph.D. degree in electronics, all from National Chiao Tung University, Taiwan, R.O.C. in 1996, 1998, and 2001, respectively.

In 2001, he joined the National Nano Device Laboratories (NDL) as an Associate Researcher and the Microelectronics and Information Systems Research Center, National Chiao Tung University (NCTU), as an Assistant Professor, where he has been engaged in

the research and development of modeling and simulation of nanodevices and VLSI circuits. He was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst, in the fall of 2002. He is in charge of the nanodevice TCAD Laboratory and the Parallel and Scientific Computing Laboratory at NDL and NCTU. His current research areas include semiconductor nanostructures physics, modeling, and device simulation, VLSI circuit simulation, computational biology, and advanced numerical techniques and scientific computation. He has authored or coauthored over 90 researcher papers in international books, journals, and conferences.

Dr. Li is a member of Phi Tau Phi. He received a Research Fellowship Award from the Pan Wen-Yuan Foundation, Taiwan, R.O.C. in 2002. Dr. Li is a member of the Institute of Electronic, Information and Communication Engineers, the American Physical Society, the Society for Industrial and Applied Mathematics, and WSEAS.