# Effect of CF<sub>4</sub> Plasma Pretreatment on Low Temperature Oxides

Tzu Yun Chang, Hsiao Wei Chen, Tan Fu Lei, Member, IEEE, and Tien Sheng Chao

Abstract—This study describes a novel technique for forming low temperature oxides ( $<350\,^{\circ}$ C) using a replacement metal gate process. Low temperature oxides were generated by N<sub>2</sub>O plasma in a PECVD system with pretreatment in CF<sub>4</sub>. Fabricated oxides demonstrate excellent current–voltage (I-V) characteristics, such as low leakage current, high breakdown charge and good reliability. Experimental results indicate that CF<sub>4</sub> plasma treatment can significantly improve the mobility and resistance against hot carrier stress of MOSFETs. With excellent electrical properties, this technique is suitable for fabrication low temperature devices.

Index Terms—Low temperature oxides, mobility and hot carrier stress,  $N_2$  O/CF $_4$  plasma, Qbd, replacement metal gate, TDDB.

#### I. INTRODUCTION

S SEMICONDUCTOR devices are being scaled down, A increasing the speed of devices by reducing the parasitic resistances of gate/source/drain is becoming more important. Polysilicon processes with dopant activation retain a large gate parasitic resistance. The use of metal gates is a possible solution to reduce gate resistance in future generations of MOSFETs [1]–[4]. However, conventional high-temperature processes, such as thermally growing oxides will be incompatible with the desired device structure. For example, the metal replacement gate process [5]-[7] involves annealing the source/drain implant before the gate insulator is formed. Thermal oxides grown subsequently by high temperature processes deviate from the existing doping profiles. Based on fabrication procedure, gate oxides formed at low temperature conditions are very important for replacement gate applications. PECVD offers the advantages of depositing an oxide at a very low temperature. Depositing oxides directly on device substrates can eliminate the thermal process and the segregation or redistribution of the dopant. Moreover, some studies have revealed that oxynitrides formed by N<sub>2</sub>O show good electrical properties [8]. Combining the two concepts, oxidation in N<sub>2</sub>O plasma by PECVD provides a simple way to form low temperature oxides. Nevertheless, the interfacial properties of nitrides oxides are the outstanding issue [9], [10]. Fluorinated oxides with high resistance against ionized radiation and hot carriers have been reported [11], [12].

Manuscript received June 10, 2002; revised September 6, 2002 This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 90-2215-E-009-095. The review of this paper was arranged by Editor C.-Y. Lu.

Digital Object Identifier 10.1109/TED.2002.807451

TABLE I SPLIT CONDITIONS OF GATE DIELECTRICS FORMATION OF LT-OXIDES WITH METAL GATE

|                               | CF.                               | Oxide formation by N <sub>2</sub> O plasma |                                                                              |

|-------------------------------|-----------------------------------|--------------------------------------------|------------------------------------------------------------------------------|

|                               | CF₄ pre-treatment                 | Time interval                              | Chamber environment                                                          |

| <u>CF<sub>4</sub>+25sec</u>   | CF <sub>4</sub> flow rate: 20sccm | 25 sec                                     |                                                                              |

| CF <sub>4</sub> +90sec        | Time: 30sec<br>RF power: 5W       | 90 sec                                     | N <sub>2</sub> O flow rate:20sccm<br>RF power : 50W<br>Ar flow rate : 50sccm |

| <u>CF<sub>4</sub>+180se</u> c |                                   | 180 sec                                    |                                                                              |

| 25sec                         |                                   | 25 sec                                     | Substrate heating: 300℃                                                      |

| 90sec                         | None                              | 90 sec                                     | Chamber pressure: 500m T                                                     |

| 180sec                        |                                   | 180 sec                                    |                                                                              |

Furthermore, plasma treatment has been recently used as a simple way to improve device characteristics in the IC industry. Our recent study described a simple fabrication process to grow low temperature fluorinated oxides, formed by  $N_2O$  plasma with further  $CF_4$  plasma pretreatment [13]. This study investigates the electrical and physical characteristics of MOSFETs with this fluorinated oxide using  $CF_4$  plasma pretreatment.

# II. EXPERIMENTS

MOS capacitors and MOSFETs with a TiN metal gate were fabricated on a 6-in (100) p-type silicon wafer with a resistivity of 5–10  $\Omega$ -cm. Replacement metal gate processes were applied to fabricate the devices. After the Source/Drain was formed and the dummy gate was removed, gate dielectrics were grown by N2O plasma in a PECVD system at 300 °C. Before the gate dielectric was formed, some samples were treated in CF4 plasma in the same chamber. Table I lists the split conditions to form the gate dielectric. Thermal oxides were grown in O2 ambient at 900 °C to serve as control samples. After the gate dielectric was formed, a 4-layer metal gate electrode (TiN/Al–Si–Cu/Ti/TiN) was deposited. All process temperatures after the dummy gate was removed were lower than 400 °C.

The current–voltage (I-V) characteristics were measured using an HP 4156A to determine the electrical properties and reliability of the gate dielectric. Capacitance–voltage (C-V) curves were measured by HP4284A and the equivalent oxide thickness (EOT) of gate dielectrics was extracted. The physical properties of gate dielectric films were investigated using an

T. Y. Chang, H. W. Chen, and T. F. Lei are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. (e-mail: tflei@cc.nctu.edu.tw)

T. S. Chao is with the Department of Electrophysics, National Chaio Tung University Hsinchu, Taiwan. He is also with the National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C.

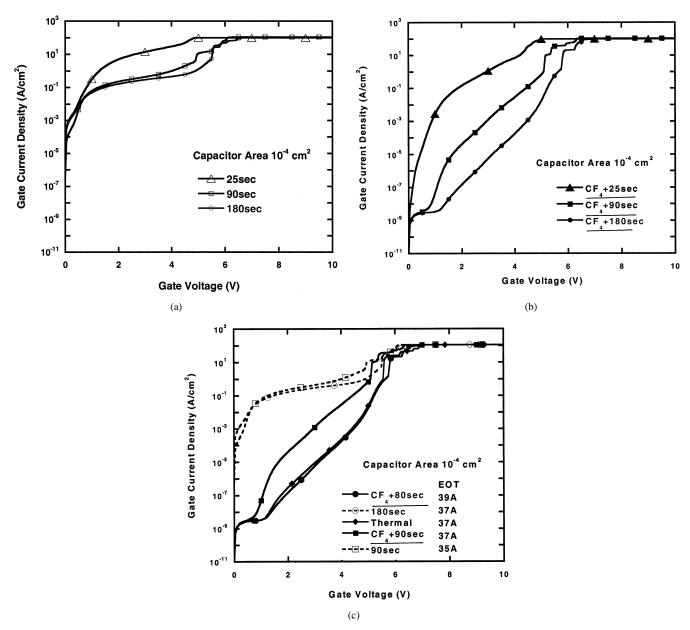

Fig. 1. (a) J-V characteristics of LT oxide films with different plasma duration. (b) J-V characteristics of LT oxide films with CF<sub>4</sub> pretreatment with different plasma duration. (c) J-V characteristics of LT oxides with/without CF<sub>4</sub> treatment and thermal oxides.

ESCA (electronic spectroscope for chemical analysis), and an AFM (atomic force microscope). The ESCA technique is highly surface specific due to the short range of the photoelectrons that are excited from the solid. The energy of the photoelectrons leaving the sample is determined using a CHA (Concentric Hemispherical Analyzer) and this gives a spectrum with a series of photoelectron peaks. The binding energy of the peaks is characteristic of each element. The peak areas can be used (with appropriate sensitivity factors) to determine the composition of the materials surface.

### III. RESULTS AND DISCUSSION

## A. Characteristics of Low Temperature Oxide With TiN Gate

Fig. 1(a) and (b) show J-V characteristics of low temperature oxides (LT oxides) with and without  $CF_4$  treatment. LT oxides

were formed using N<sub>2</sub>O plasma in 25, 90, and 180 s. As-deposited samples have a large leakage current due to damage caused by plasma and samples with longer process times have a lower leakage current as the equivalent oxide thickness (EOT) increases. The rate of deposition by N2O plasma saturated at 90 s. Notably, excess N2O plasma will increase the density of the low-temperature oxide and only slightly increases the EOT. Thus, the additional CF<sub>4</sub> pretreatment restores the LT oxides and yields a better I-V curve, perhaps due to the formation of strong Si-F bonds' replacing weak bonds such as Si-H and Si-OH. Fig. 1(c) plots the J-V characteristics of LT oxides with/without CF<sub>4</sub> treatment and thermal oxides. The numbers represent the duration of N<sub>2</sub>O plasma treatment. According to our results, as-deposited or "90 sec" samples, have the largest leakage current among these samples due to plasma damage. However, the sample pre-treated with CF<sub>4</sub> exhibits a significant reduction in leakage that is comparable to that of thermal

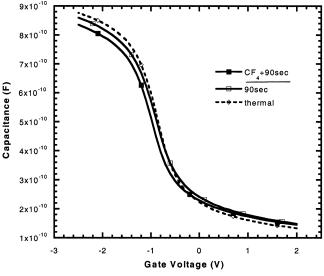

Fig. 2.  $C\!-\!V$  characteristics of thermal oxide and LT oxides with/without CF<sub>4</sub> pre-treatment.

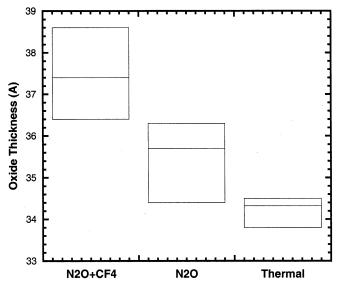

Fig. 3. EOT for each sample.

oxide. This improvement appears to follow from the formation of strong Si–F bonds. Although a longer plasma time typically causes significant damage to the film, according to the results obtained, the sample pre-treated with CF<sub>4</sub> performs excellently almost as well as thermal oxides. With CF<sub>4</sub> treatment, a longer N<sub>2</sub>O plasma time is preferred over a shorter one. Therefore, the low-temperature oxide formed by N<sub>2</sub>O plasma (for 180-sec) with CF<sub>4</sub> pretreatment could effectively improve the I-V characteristics similar to thermal oxides.

Fig. 2 plots the high-frequency C–V characteristics of thermal oxide and LT oxides with/without  $CF_4$  pre-treatment. The frequency of CV measurement was 100 KHz. The LT oxide curve is similar to that of thermal oxide, but the capacitance of the LT oxide is slightly lower than that of thermal oxide. A negligible  $V_{FB}$  shift implies that nearly no fixed charge or traps exist in the LT oxide. Moreover, additional  $CF_4$  treatment causes a  $V_{FB}$  shift due to the incorporation of fixed charges in oxide regimes. Restated, fluorine incorporated into

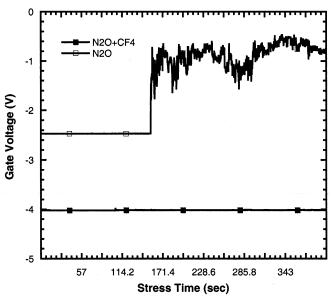

Fig. 4. Stress time versus gate voltage of LT oxides with/without CF<sub>4</sub>.

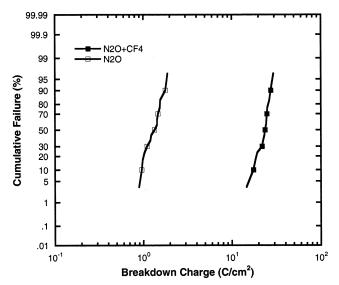

Fig. 5. Charge to breakdown (Qbd) distribution.

oxide regimes enhances the generation of oxide fixed charges. Fig. 3 plots the EOT of each sample. Fifty samples were tested for each condition. The EOTs were extracted in accumulation mode. CF<sub>4</sub> pre-treatment did not greatly increase the electrical thickness of the dielectric film. The thickness variation of LT oxides with/without CF<sub>4</sub> pre-treatment exceeds that of thermal oxide, resulting in PECVD dielectric film that is less uniform than thermal oxide film.

Maintaining a constant current stress enables the integrity of the gate insulator to be determined. Fig. 4 plots stress time versus gate voltage for LT oxides with/without  $CF_4$ . The applied current density is  $10 \text{ mA/cm}^2$ . The  $CF_4$ -treated sample exhibits negligible voltage variation. But LT oxides without  $CF_4$  pre-treatment exhibit breakdown phenomena after approximately 170 s. The time to breakdown is one order of magnitude smaller than  $CF_4$ -treated; we did not include time to breakdown of  $CF_4$ -treated sample in Fig. 4. The  $CF_4$  pre-treated film is better than the other film, implying that the

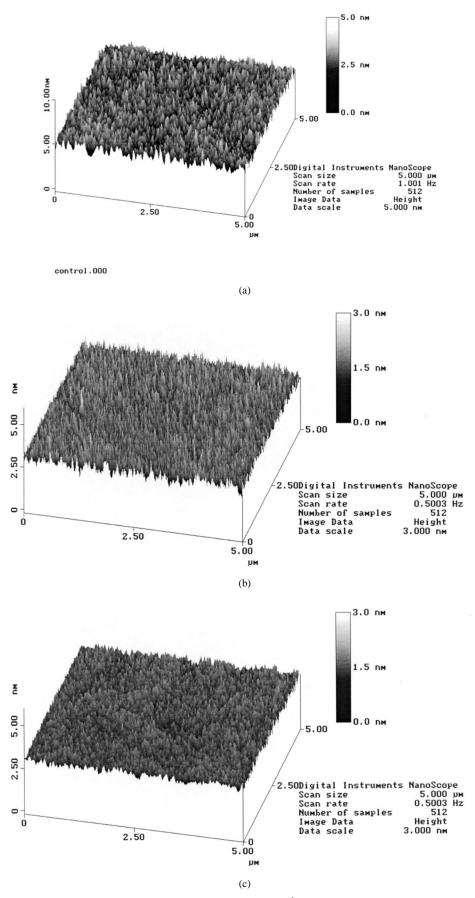

Fig. 6. (a) AFM image of the sample after standard cleaning with RMS roughness of 3.4  $\mathring{A}$ . (b) AFM image of the sample using  $N_2O$  90 s formation without CF<sub>4</sub> treatment with RMS roughness of 1.8  $\mathring{A}$ . (c) AFM image of the sample using  $N_2O$  90 s formation with CF<sub>4</sub> treatment with RMS roughness of 1.3  $\mathring{A}$ .

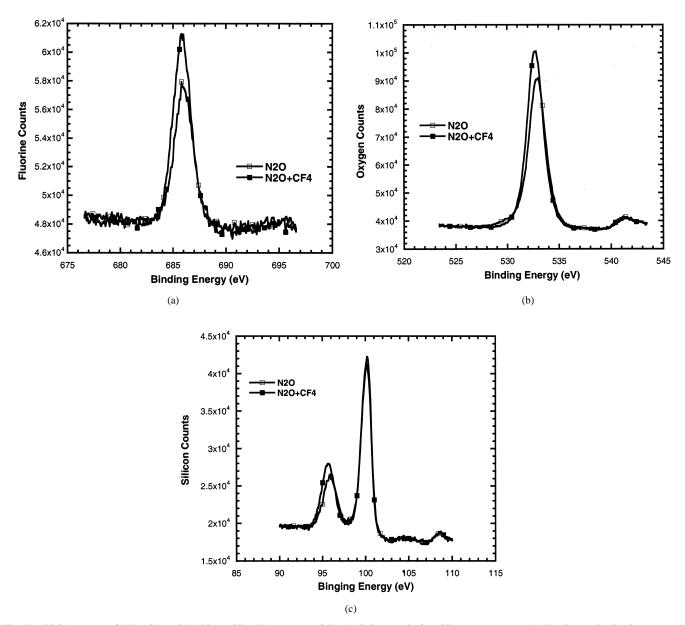

Fig. 7. ESCA spectra of LT oxides with/without  $CF_4$ . The amount of F and O increased after  $CF_4$  pre-treatment. (a) Fluorine peak. (b) Oxygen peak. (c) Silicon peak.

formation of Si–F bonds can reduce the number of interface traps between Si and the oxide interface, and improve the reliability of the LT oxides. Breakdown charge is one specification of the quality of a gate insulator. Breakdown charge is defined as constant stress current density multiplied by the time to breakdown. Fig. 5 exhibits that charge to breakdown (Qbd) distribution of LT oxides with/without  $CF_4$ . The breakdown charge can be increased by a single order of magnitude by additional  $CF_4$  pre-treatment. Restated,  $CF_4$  pre-treatment can effectively increase the incorporation of fluorine into oxide regimes and improve the integrity of the LTO.

Nevertheless,  $CF_4$  plasma is one kind of etching processes. The atomic force microscope (AFM) was used to measure the surface morphology of all samples and thus determine the effect of  $CF_4$  on the silicon surface. Fig. 6(a) presents the AFM image of the sample after standard cleaning, (b) is the sample using  $N_2O$  90 s formation without  $CF_4$ , and (c) is the sample using

$N_2O$  90 s formation with  $CF_4$ . The RMS roughness of (a), (b), and (c) are 3.4 Å, 1.8 Å, and 1.3 Å, respectively. These values show that  $CF_4$  pre-treatment smooths the silicon surface morphology, without further damaging it. Consequently, low power  $CF_4$  plasma treatment does not cause etching during LT oxides formation.

Electron Spectroscopy for Chemical Analysis (ESCA) was applied to samples with/without CF<sub>4</sub> treatment to identify the incorporation of fluorine during CF<sub>4</sub> treatment. Fig. 7(a)–(c) present the intensities associated with fluorine, oxygen and silicon, respectively. Further CF<sub>4</sub> pretreatment not only increases the incorporation of fluorine but also increases the number of Si–O bonds. Moreover, the Si peak is shifted in Fig. 7(c) due to the incorporation of fluorine. Restated, CF<sub>4</sub> treatment can improve low temperature LT oxide by replacing dangling bonds with stronger Si–F or Si–O bonds. Table II is the quantify table of LT oxides with/without CF<sub>4</sub> treatment. Additional CF<sub>4</sub> pre-

| Atom % | N <sub>2</sub> O oxide without CF <sub>4</sub> | N <sub>2</sub> O oxide with CF <sub>4</sub> |

|--------|------------------------------------------------|---------------------------------------------|

| F 1s   | 4.166                                          | 5.933                                       |

| O 1s   | 32.689                                         | 37.963                                      |

| N 1s   | 1.265                                          | < 1%                                        |

| C 1s   | 15.692                                         | 11.342                                      |

| Si 2p  | 46.188                                         | 44.762                                      |

TABLE II QUANTIFICATION TABLE OF LT OXIDES WITH/WITHOUT  ${\rm CF_4}$

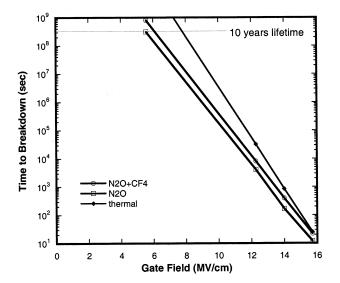

Fig. 8. TDDB plot of LT oxides with/without CF<sub>4</sub> treatment.

treatment reduces the amount of nitrogen and carbon, demonstrating that the improvement in I-V characteristics was due to the replacement of Si-C and Si-H with stronger Si-F bonds.

Time-dependent dielectric breakdown (TDDB) is one characteristics used in determining the lifetime of a device. Three different high fields are applied to measure the time to breakdown (pad area =  $3 \times 10^{-4}$  cm<sup>2</sup>); the operating field for a lifetime of 10 years can be determined by extrapolation [14]. According to our results (Fig. 8), the operating field of the LT oxide is 5.5 MV/cm for a lifetime of ten years. Moreover, the CF<sub>4</sub>-treated sample has an increased operation field of 6.2 MV/cm, confirming that the proposed method of CF<sub>4</sub> treatment can improve the integrity of LT oxides. However, the reliability of thermal oxides exceeds that of CF<sub>4</sub>-treated low temperature oxides. The low temperature process (<350 °C) can not anneal defects or traps during plasma fabrication and degrades the reliability of the oxide. However, low temperature oxides with CF<sub>4</sub> treatment are highly promising for low temperature applications.

# B. Electrical Characteristics of MOSFETs

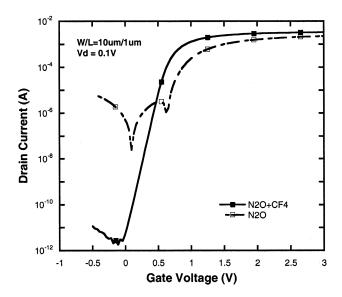

The exact effect of the proposed CF<sub>4</sub> pre-treatment method on the performance of devices is described when NMOSFETs are fabricated by the replacement gate process. Fig. 9 shows the  $V_g$ – $I_d$  characteristics of 10  $\mu$ m/1  $\mu$ m NMOSFETs using LT oxides with/without CF<sub>4</sub> pre-treatment. Samples without CF<sub>4</sub> treatment have inferior characteristics because of a large gate

Fig. 9.  $V_q$ – $I_d$  characteristics of LT oxides with/without CF<sub>4</sub> pre-treatment.

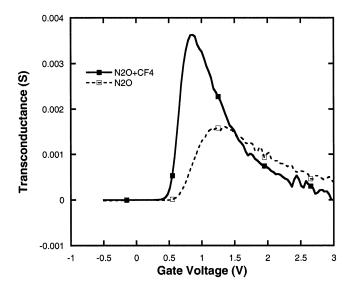

Fig. 10. Transconductance  $(G_m)$  of LT oxides with/without  $\operatorname{CF}_4$  pre-treatment.

current, and the  $I_d$  distortion is also caused by gate leakage. For samples that had undergone CF<sub>4</sub> pretreatment, a 70% improvement in drain current is observed. Restated, CF4 pretreatment can effectively improve device performance. Fig. 10 shows the transconductance  $(G_m)$  of LT oxides with/without CF<sub>4</sub> pretreatment. The maximum  $G_m$  value of a sample with CF<sub>4</sub> is 3.5 mS, and its  $V_{th}$  (threshold voltage) is 0.8V. A sample without CF<sub>4</sub> has a lower  $G_m$  value of 1.6 ms, and its  $V_{th}$  is shifted to 1.25 V. We posit that additional CF<sub>4</sub> pre-treatment can reduce the number of interface states and maintain higher mobility. A higher  $G_m$  is associated with an electrically superior Si/SiO<sub>2</sub> interface. Fluorine incorporation increases the number of Si–F bonds and efficiently suppresses the surface scattering effect. Moreover, the difference in the threshold voltage is related to the plasma-induced charge generation, as confirmed by Fig. 2.

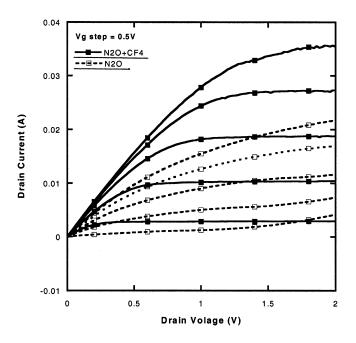

Fig. 11 plots the  $V_d$ - $I_d$  characteristics of samples with/without CF<sub>4</sub> pre-treatment. The gate voltage step is

Fig. 11.  $V_d$ - $I_d$  characteristics of LT oxides with/without CF<sub>4</sub> pre-treatment.

Fig. 12.  $G_m$  degradation of LT oxides with/without CF<sub>4</sub> after 100 s stress.

$0.5~\rm V$  and the W/L dimensions of the measured MOSFETs are 10/1. No saturation region of N2O samples is observed to be caused by increasing the gate leakage current. Additional CF<sub>4</sub> pre-treatment can further improve the carrier mobility and drivability. Not only can the surface scattering effect be suppressed, but also the surface morphology can be improved. Restated, CF<sub>4</sub> pretreatment can increase interface quality and reduce the roughness of the surface.

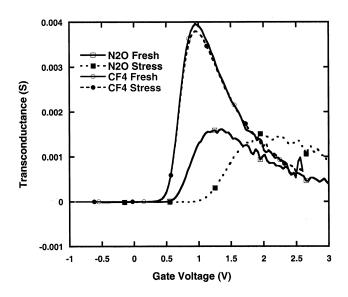

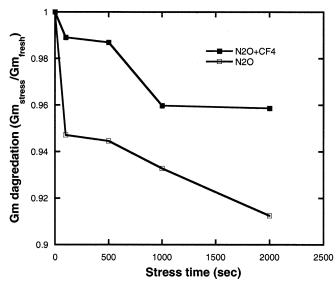

Hot carrier lifetime is an important issue in device operation, especially when the device is stressed under drain avalanche hot carrier (DAHC) conditions. Fig. 12 illustrates the  $G_m$  degradation after DAHC stressing ( $V_d=3$  V,  $V_g=1.5$  V) LT oxides with/without CF $_4$  treatment for 100 s. The degradation of both these samples is minor, but the N $_2$ O sample exhibits a  $V_{th}$  shift after stress. Given the poor interface quality (even bulk) of LT

Fig. 13. Time dependence of  $G_m$  degradation after DAHC (drain avalanche hot carrier) stress.

oxides, many hot carriers destroy the film's structure and introduce traps.  $CF_4$  pre-treatment increases the incorporation of fluorine and effectively increases resistance against hot carrier stress. Fig. 13 plots the time-dependence of  $G_m$  degradation after DAHC stress of  $N_2O$  oxide with/without  $CF_4$  pre-treatment. Under fixed hot carrier stress conditions,  $CF_4$  treatment reduces the hot carrier effect, yielding stronger Si–F bonds that increase the ability of the oxide to resist hot carrier stress.

#### IV. CONCLUSIONS

Results in this study demonstrate that additional  $\operatorname{CF}_4$  treatment improves the  $I{-}V$  characteristics of the low temperature oxide, which performs similar to the thermal oxide.  $\operatorname{CF}_4$  pretreatment improves gate oxide integrity (GOI) and the reliability of LTO, because Si–F bonds replace dangling bonds between the oxide/Si interface, and fluorine can enhance re-oxidation to make strengthen the oxide. LTO with  $\operatorname{CF}_4$  treatment has excellent leakage, breakdown,  $\operatorname{Q}bd$ , TDDB, and SILC properties, as well as MOSFET characteristics.

## REFERENCES

- [1] T. Ohmi, "Trend of future silicon technology," *Jpn. J. Appl. Phys.*, vol. 33, p. 6747, 1994.

- [2] K. Ino, T. Ushiki, K. Kawai, I. Ohshima, T. Shinohara, and T. Ohmi, "Highly-reliability, low-resistivity bcc-Ta gate MOS technology using low-damage Xe-plasma sputtering and Si-encapsulated silicidation process," in VLSI Tech. Dig., 1999, pp. 186–184.

- [3] D. H. Lee, S. H. Joo, G. H. Lee, J. Moon, T. E. Shim, and J. G. Lee, "Characteristics of CMOSFETs with sputter-deposited W/TiN stack gate," in VLSI Tech. Dig., 1995, p. 119.

- [4] H. Yang et al., "A comparison of TiN processes for CVD W/TiN gate electrode on 3 nm gate oxide," in IEDM Tech. Dig., 1997, pp. 459–462.

- [5] A. Chatterjee et al., "CMOS metal replacement gate transistors using tantalum pentoxide gate insulator," in *IEDM Tech. Dig.*, 1998, pp. 777–780.

- [6] J. M. Hergenrother *et al.*, "The vertical replacement-gate (VRG) MOSFET: A 50-nm vertical MOSFET with lithography-independent gate length," in *IEDM Tech. Dig.*, 1999, pp. 75–78.

- [7] C. P. Chang et al., "SALVO process for Sub-50 nm low-Vt replacement gate CMOS with KrF lithography," in *IEDM Tech. Dig.*, 2000, pp. 53–56.

- [8] H. R. Soleimani, B. S. Doyle, and A. Philipossian, "Formation of ultrathin nitrided SiO<sub>2</sub> oxides by direct nitrogen implantation into silicon," *J. Electrochem. Soc.*, vol. 142, no. 8, p. 132, 1995.

- [9] A. Kamgar et al., "Reduced electron mobility due to nitrogen implant prior to the gate oxide growth," *IEEE Electron Device Lett.*, vol. 21, May 2000.

- [10] A. Kamgar et al., "Impact of nitrogen implant prior to the gate oxide growth on transient enhanced diffusion," in *IEDM Tech. Dig.*, 1997, p. 695.

- [11] G. O. Lo et al., "Thin fluorinated gate dielectrics grown by rapid thermal processing in O<sub>2</sub> with diluted NF<sub>3</sub>," *IEEE Trans. Electron Devices*, vol. 35, p. 148, 1992.

- [12] T. K. Nguyan et al., "Effects of fluorine implants on induced charge components in gate oxides under constant current Fowler–Nordhiem stress," IEEE Trans. Electron Device, vol. 44, p. 1432, 1997.

- [13] T. Y. Chang et al., "Improvement of low temperature gate dielectric formed in N<sub>2</sub>O plasma by an additional CF<sub>4</sub> pretreatment process," IEEE Electron Device Lett., to be published.

- [14] J. McPherson, V. Reddy, K. Banerjee, and L. Huy, "Comparison of E and 1/E TDDB models for SiO/sub 2/under long-term/low-field test conditions," in *IEDM Tech. Dig.*, 1998, pp. 171–174.

**Hsiao Wei Chen** was born in Hualien, Taiwan, R.O.C., on September 12, 1978. She received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2000 and 2002, respectively.

Tan Fu Lei (M'98) was born in Keelung, Taiwan, R.O.C., on September 17, 1944. He received the B.S. degree in electrical engineering from National Cheng Kung University, Tainan, Taiwan, in 1967 and the M.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1970 and 1979, respectively.

From 1970 to 1972, he was with the Fine Products Microelectronics Corporation, Taiwan, as an Engineer working on the fabrication of small-signal transistors. From 1980 to 1982, he was the Plant Manager

of Photronic Corporation, Taiwan. In 1983, he joined the faculty at NCTU as an Associate Professor in the Department of Electronics Engineering and the Institute of Electronics. During 1984 to 1986, he was the Director of the Semi-conductor Research Center. During 1991 to 1998, he also was the deputy director of the National Nano Device Laboratory. Presently he is a Professor in the Department of Electronics Engineering and the Institute of Electronics. His research interests are semiconductor devices and VLSI technologies.

**Tzu Yun Chang** was born in Hsinchu, Taiwan, R.O.C., on September 27, 1975. He received the B.S. degree in electrical engineering from National Chiao Tung University (NCTU), Hsinchu, in 1997.

He is currently pursuing the Ph.D. degree at NCTU. His latest research is in the field of gate insulators for nano MOSFET device applications.

**Tien Sheng Chao** was born in Penghu, Taiwan, R.O.C., in 1963. He received the Ph.D. degrees in electronics engineering from National Chiao-Tung University (NCTU), Hsinchu, Taiwan, R.O.C. in 1992.

He joined the National Nano Device Laboratories (NDL), Hsinchu, as an Associate Researcher in July 1992 and became a Researcher in 1996. He was engaged in developing the thin dielectrics preparations and cleaning processes. He joined the faculty at NCTU as an Associate Professor in the Department

of Electrophysics in August 2001.