ELSEVIER

Contents lists available at ScienceDirect

## Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Impacts of a buffer layer and hydrogen-annealed wafers on the performance of strained-channel nMOSFETs with SiN-capping layer

Tzu-I Tsai<sup>a</sup>, Horng-Chih Lin<sup>a,b</sup>, Yao-Jen Lee<sup>b,\*</sup>, King-Sheng Chen<sup>b</sup>, Jeff Wang<sup>d</sup>, Fu-Kuo Hsueh<sup>b</sup>, Tien-Sheng Chao<sup>c</sup>, Tiao-Yuan Huang<sup>a</sup>

- <sup>a</sup> Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

- <sup>b</sup> National Nano Device Laboratories, Hsinchu, Taiwan

- <sup>c</sup> Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan

- <sup>d</sup> Department of Nanotechnology Engineering, University of Waterloo, Waterloo, Canada

#### ARTICLE INFO

Article history: Received 15 May 2008 Accepted 7 June 2008 Available online 23 August 2008

Review of this manuscript was arranged by A. Iliadis, C. Richter, and A. Zaslavsky

Keywords: Strained-Si CESL Si<sub>3</sub>N<sub>4</sub> capping Hydrogen-annealed wafer

#### ABSTRACT

In this study, the effects of  $Si_3N_4$  layer capping and TEOS buffer layer inserted prior to the  $Si_3N_4$  deposition on the NMOS device characteristics as well as correlated hot-electron degradations were investigated. The devices were built on two kinds of the substrates, namely, Cz and hydrogen-annealed (Hi) wafers. More importantly, we found that hydrogen species is the primary culprit for aggravated reliabilities in strained devices. By exerting the accelerated stress test, we could study the hot-electron degradation thoroughly in terms of threshold voltage shift ( $\Delta V_{TH}$ ), transconductance degradation ( $\Delta Gm$ ) and so on. The TEOS buffer layer could effectively block the diffusion of hydrogen species from the  $Si_3N_4$  capping layer into the channel and the  $Si/SiO_2$  interface during the  $Si_3N_4$  deposition as well as subsequent thermal cycles.

© 2008 Elsevier Ltd. All rights reserved.

#### 1. Introduction

With CMOS scaling into the nanometer regime, strained channel engineering has been adopted as one of the most effective remedies and thoroughly explored for the much needed performance enhancement such as boosting the drive current of the scaled devices [1–3]. With regard to carrier mobility enhancement, introducing strain in the channel region can enhance the carrier mobility [4]. What the researchers could accomplish is by either applying highly bi-axial tensile strain to the channel region with a SiGe virtual substrate [1], or by uni-axially straining the channel with strain boosters [1–3]. Recent studies have shown that the uni-axial strained channel from a contact etch-stop silicon nitride layer increases the current drivability [5]. Such scheme is attractive and practical because it can be easily implemented using VLSI processing. The local strained channel (LSC) technique is proposed to provide tensile strained channel in nMOSFETs [6].

As long as the knowledge base concerning the mobility enhancement of Si strained channel has been established, it is appropriate now for us to concentrate our attention to its relating issue such as reliability. Among the most critical reliability issues, device degradation induced by hot-electrons is the most representative one in deep sub-micro nMOSFETs [7]. The physical mechanisms and characteristics of hot-electrons degradation have been extensively examined [8]. Furthermore, by exerting the accelerated stress test, we could study the hot-electron degradation thoroughly in terms of threshold voltage shift ( $\Delta V_{\rm TH}$ ), drain current degradation ( $\Delta I_{DS}$ ), subthreshold swing degradation ( $\Delta S.S$ ), and transconductance degradation ( $\Delta$ Gm) and so on. According to the aforementioned contents, local tensile strain technology with the Si<sub>3</sub>N<sub>4</sub> capping layer has been viewed as one of the most effective methods to boost the drive current in scaled nMOSFET devices. the device reliability associated with the strained device owing to the strain, and excess hydrogen and nitrogen incorporation from the deposited Si<sub>3</sub>N<sub>4</sub> layer is an imminent concern. In line with this, the incorporation of a thin TEOS buffer layer to improve the reliability performance has been proposed [9].

In addition, hydrogen-annealed wafers (Hi-wafer) have been reported having reduced oxygen defects in Czochralski (CZ) wafers [10–11], with improved micro roughness and less defect on the surface after high temperature hydrogen anneal. The following sections describe in detail the behaviors of nMOSFETs device with local strained channel technique using SiN-capping layer on Hi- or Cz-wafers as well as the related reliability.

<sup>\*</sup> Corresponding author. E-mail address: yjlee@ndl.org.tw (Yao-Jen Lee).

#### 2. Device concept

#### 2.1. Strained-Si technology

Strained-Si technology improves the drive current of CMOS through altering the energy band structures of the surface channel [12–14]. There is a branch of strained-Si technology: bi-axial strain and uni-axial strain. The bi-axial tensile strained channel achieved by growing a Si channel layer on a relaxed SiGe substrate could improve the drive currents of both nMOSFETs and pMOSFETs when the incorporated Ge content is more than 20% of the relaxed SiGe substrate [15–16]. It is worthy to note that the thickness of the top strained-Si layer has to be thinner than a critical thickness that depends on the Ge content of the underlying relaxed SiGe substrate to avoid the generation of abundant amount of dislocations due to lattice mismatch [17]. Aplenty dislocations of the virtual SiGe substrate may become an obstacle to practical applications.

In contrast, the uni-axial strained channel technology has been proposed to avoid the shortcomings of bi-axial strained channel. Uni-axial strain can be set up by modifying contact-etch-stop-layer (CESL) deposition [18–19], silicidation [20], source/drain material [21], shallow trench isolation (STI) [22], packing process [23], and so on. Moreover, uni-axial strain can be arbitrarily exerted in any direction correlative with the carrier transportation; hence the performance of both NMOS and PMOS devices can be enhanced by respectively applying the tensile and compressive strains. Mobility,  $\mu$ , for carriers in semiconductors is formulated as

$$\mu = \frac{q\tau}{m^*} \tag{1}$$

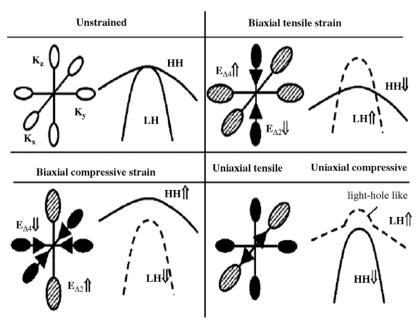

where  $1/\tau$  is the overall scattering rate and  $m^*$  is the conductivity effective mass. From the above mobility formula, we could set about mobility enhancement of strained-Si devices by reducing either the conductivity effective mass or the scattering rate. The conduction band of unstrained bulk Si is consisted of six degenerate valleys ( $\Delta 6$ ) with the same energy [24] (as shown in Fig. 1). Under the effect of bi-axial tensile strain, the sixfold degenerate conduction band is split up into a fourfold ( $\Delta 4$ ) in-plane and a twofold ( $\Delta 2$ ) out-of-plane degenerate valleys in the energy band diagram [25]. The energy difference ( $\Delta E$ ) between  $\Delta 2$  and  $\Delta 4$  sub-bands deter-

mines the total population of electrons in each sub-band. As a result, the larger  $\Delta E$ , the more the percentage of total electron population would occupy the  $\Delta 2$  valleys. Since the  $\Delta 2$  valleys have a smaller effective mass as compared with that of the  $\Delta 4$  valleys, the electron mobility enhancement could be accomplished as more electrons occupy the  $\Delta 2$  valleys. In addition, suppression of intervalley phonon scattering can effectively reduce the electron scattering rate  $(1/\tau)$  [25–26], which in turn may also enhance the mobility. From the effort of Leitz et al. [27], we know that uni-axially and compressively strained pMOSFETs may have lighter in-plane effective mass through full-band Monte Carlo simulation [24], thus hole mobility is enhanced. However, for the case of bi-axial tensile strain. the reduction of the inter-valley scattering is the only plausible approach to the hole mobility enhancement by about 25-30% of germanium concentration necessary for introducing more than 1 G Pa stress [27].

#### 2.2. Hi-wafer technology

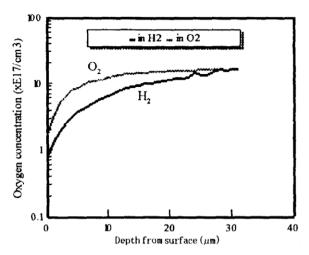

A raw Czochralski-grown (CZ) silicon wafer includes supersaturated oxygen atoms and nuclei for oxygen precipitation, which are introduced during crystal growth. For ultra large scale integrated (ULSI) devices, CZ silicon wafers ought to be free of defects in the device active layer and adequate oxygen precipitates in the bulk region to enable intrinsic gettering for metallic contamination. However, inadequate oxygen contents would induce many micro-defects during later heat treatments for ULSI fabrication. The micro-defects, which are induced near surface region, lead to various harmful defects such as OISF (Oxidation induced Stacking Fault), pattern edge dislocations, gate oxide breakdown failures and so on. For the purpose of improving the surface quality and preventing the harmful defect generation, both oxygen and nuclei ought to be completely removed from the surface region. There is an approach to produce oxygen-less Si wafer by virtue of a high temperature anneal in hydrogen ambient so as to efficiently eject the oxygen atoms from the surface region [10–11]. The hydrogen anneal was carried out at 1200 °C for 1 h by using a hot wall type vertical furnace. Wafers which received such treatment are dubbed "Hi-wafer". Fig. 2 shows the oxygen out diffusion profile after annealing in hydrogen or oxygen ambient. The oxygen contents

Fig. 1. Simple schematic of conduction and valence band bending with strain [24].

Fig. 2. Schematic diagram of the oxygen depth profile after hydrogen anneal at  $1200\,^{\circ}\text{C}$  for  $1\,h\,|11|$ .

in the surface region of Hi-wafer are obviously smaller than that of a wafer annealed in oxygen ambient. Thus the generation of oxygen-induced defects near the surface region could be significantly reduced in Hi-wafers, making such wafers a good choice for improving the wafer yield.

#### 3. Experimental results

#### 3.1. Device fabrication

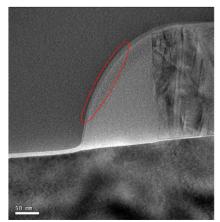

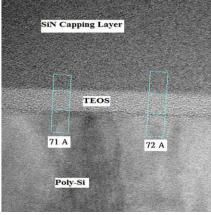

All device fabrications were carried out at National Nano Device Laboratories, nMOSFETs were fabricated on 6-in Hi- and Cz-wafers with resistivity of 15–25  $\Omega$  cm. The hydrogen anneal was carried out at 1200 °C for 1 h. The p-type well was formed first by BF<sub>2</sub><sup>+</sup> implantation at 70 keV and  $1.2 \times 10^{13}$  cm<sup>-2</sup>. Next, a standard local oxidation of silicon (LOCOS) process with channel stop implant (by BF<sub>2</sub><sup>+</sup> implantation at 120 keV and  $4 \times 10^{13}$  cm<sup>-2</sup>) was used for device isolation. Threshold voltage adjustment and anti-punch through implantation steps were done by implanting 40 keV BF<sub>2</sub><sup>+</sup> and 35 keV B+, respectively. Gate dielectric thickness about 2.5 nm was grown in an N<sub>2</sub>O ambient. Then, 200 nm un-doped poly-Si was deposited. Shallow S/D extensions were formed by implanting As (10 keV,  $1 \times 10^{15}$  cm<sup>-2</sup>). After a 200 nm TEOS spacer formation, S/D regions were formed by As+ implantation at 30 keV and  $5 \times 10^{15} \, \text{cm}^{-2}$ . Then the substrate electrode patterning was performed through lithography and etching processes, followed by the formation of the substrate contact regions by  $BF_2^+$  implantation at 40 keV and  $5\times 10^{15}\, {\rm cm}^{-2}$ . Rapid thermal anneal (RTA) was subsequently carried out in a nitrogen ambient at  $1000\,^{\circ}{\rm C}$  for  $10\,{\rm s}$  to activate dopants in the gate, S/D, and substrate regions. A 300 nm LPCVD  ${\rm Si}_3{\rm N}_4$  was next deposited (denoted as  ${\rm SiN/Cz}$  and  ${\rm SiN/Hi}$ ), while some wafers were deliberately skipped of the  ${\rm Si}_3{\rm N}_4$  deposition step to serve as the controls (denoted as  ${\rm Cz-control}$  and Hi). In addition, the effect of intrinsic stress inside the  ${\rm Si}_3{\rm N}_4$  layer with 300 nm thickness was remarkable [31]. For some  ${\rm Si}_3{\rm N}_4$ -capped nMOSFETs on either Hi- or CZ-wafers, a thin LPCVD-TEOS buffer layer (about 7 nm, denoted as  ${\rm SiN/buffer/Cz}$  and  ${\rm SiN/buffer/Hi}$ ) was capped prior to the  ${\rm Si}_3{\rm N}_4$  deposition, as shown in Fig. 3. Finally, a four-level metallization was carried out in PVD system for contact.

#### 3.2. Electrical characterization and related reliability

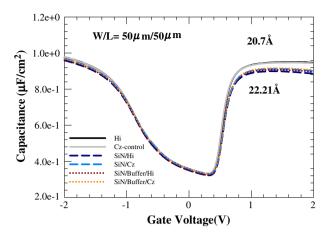

All measurements in the following section were evaluated by an HP4156A precision semiconductor parameter analyzer and an HP4284 LCR meter, respectively. Temperature-regulated hot chucks were used to set the measurement temperature at 25 °C. Fig. 4 shows the capacitance–voltage (C–V) characteristics of devices. In Fig. 4, we could distinctly observe that the poly-depletion effect becomes obvious in the splits with  $\rm Si_3N_4$  capping layer depositions, irrespective of the use of Cz or Hi-wafers.

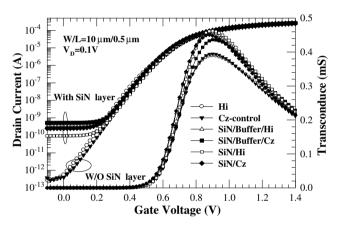

This phenomenon is attributed to the additional thermal budget associated with the nitride deposition step by 780 °C LPCVD. It is known that the solid solubility of dopants is temperature-dependent and the thermal conditions mentioned above tend to lower the activated carrier concentration in the poly-Si gates [28]. In addition, the poly-silicon depletion can be avoided when PECVD is used for the nitride deposition owing to the short deposition time of PECVD for the activated carrier concentration in the poly-Si gates being less influenced. Fig. 5 shows the drain current  $(I_D)$ and transconductance (Gm) versus  $V_G$  for nMOSFETs with W/ $L = 10 \mu m/0.5 \mu m$  from different splits. Higher subthreshold slope (S.S.) and leakage current, about 2 orders larger, are found for the splits with Si<sub>2</sub>N<sub>4</sub> capping layer due to contact etched damages. A significant increase of Gm was found for the splits with Si<sub>3</sub>N<sub>4</sub> capping layer owing to the tensile stress in the channel, which increases the electron mobility in the channel.

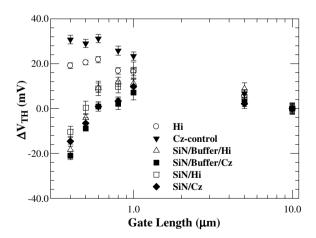

Fig. 6 shows the distribution of the threshold voltage ( $V_{\rm TH}$ ),  $V_{\rm TH}$  (L)– $V_{\rm TH}$  (10  $\mu$ m), versus the gate length. Among the splits, the control splits depict a pronounced reverse-short-channel-effect (RSCE). This is probably due to boron segregation at the implant-damaged regions located near the edge of the channel. The phenomenon, however, is not observed in the Si<sub>3</sub>N<sub>4</sub> capping splits. It

Fig. 3. TEM pictures for TEOS buffer layer. The thickness is about 7 nm.

**Fig. 4.** Capacitance–voltage(C–V) characteristics of nMOSFETs processed with TEOS buffer layer and  $Si_3N_4$  capping layer on both Cz and Hi-wafers.  $W/L = 50 \mu m/50 \mu m$ .

**Fig. 5.** Drain current and Gm (measured at  $V_{\rm D}$  = 0.1 V) versus  $V_{\rm G}$  for nMOSFETs with W/L = 10  $\mu$ m/0.5  $\mu$ m.

Fig. 6.  $V_{TH}$  distribution,  $V_{TH}$  (L)– $V_{TH}$  (10  $\mu m$ ), versus gate length.

is noted that RSCE would be suppressed by boron redistribution as the thermal budget increases and bandgap narrowing effect caused by channel stress [29].

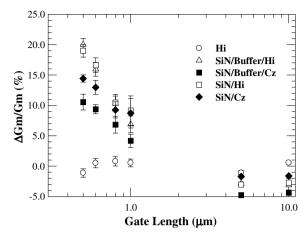

Fig. 7 shows the percentage increase of transconductance (Gm) for all splits as a function of channel length. The Gm is linearly related to channel mobility. When the channel length is scaled to less

Fig. 7. Percentage increase of Gm for all splits as a function of channel length.

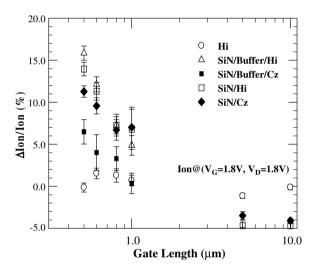

Fig. 8. Percentage increase of on-current for all splits as a function of channel length.

than 1  $\mu$ m, Gm increases sharply owing to the unique feature mentioned above. Specifically, Gm increases by 20% for nMOSFETs with  $W/L = 10 \ \mu$ m/0.5  $\mu$ m. In addition, the channel strain was scarcely influenced as the thickness of the TEOS buffer layer was lower than 20 nm [9]. Fig. 8 shows the percentage increase of the on-current with respect to the Cz-control ( $V_G = 1.8 \ V$ ,  $V_D = 1.8 \ V$ ) for all splits as a function of channel length. The trend of on-current enhancement is the same as the Gm enhancement.

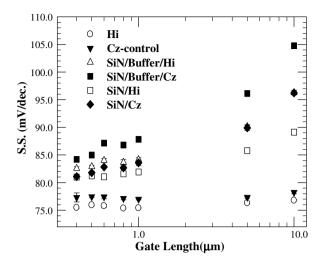

Fig. 9 shows the distribution of the S.S. versus the gate length. For the splits of Cz-controls and Hi, S.S. is independent of gate length. Hi split depicts lower S.S. than Cz-controls because of the better surface quality after high temperature hydrogen anneal. However, the splits with  $\mathrm{Si}_3\mathrm{N}_4$  capping layer depict higher S.S., especially for long channel devices. The root cause for such phenomenon is not clear yet at this stage. Increase in EOT due to poly-depletion effect may play a role. It is noted that the TEOS buffer layer could effectively block hydrogen molecules diffusion from  $\mathrm{Si}_3\mathrm{N}_4$  capping layer deposition. As a consequence, the S.S. increases due to less effective interface passivation.

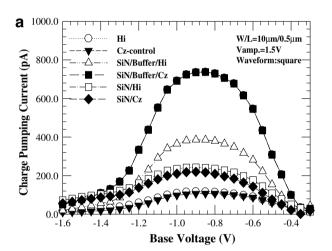

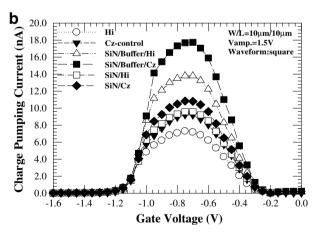

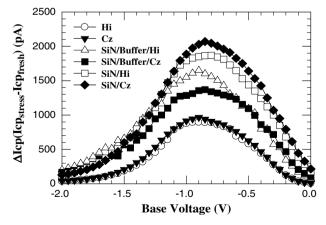

Fig. 10 shows charge pumping current ( $I_{\rm cp}$ ) versus base voltage. The device size is  $W/L=10~\mu{\rm m}/0.5~\mu{\rm m}$  for (a),  $W/L=10~\mu{\rm m}/10~\mu{\rm m}$  for (b), the pulse amplitude is 1.5 V, and the square waveform is used for  $I_{\rm cp}$  extraction. The splits of SiN/Cz and SiN/Hi depict slightly higher  $I_{\rm cp}$  compared with the splits of Hi and Cz-control.

Fig. 9. Subthreshold slope versus gate length.

**Fig. 10.** Charge pumping current ( $I_{cp}$ ) versus base voltage. The device size is  $W/L=10~\mu\text{m}/0.5~\mu\text{m}$  for (a),  $W/L=10~\mu\text{m}/10~\mu\text{m}$  for (b), the pulse amplitude is 1.5 V, and the square waveform is used for  $I_{cp}$  extraction.

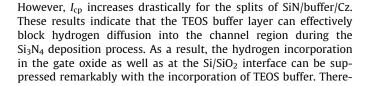

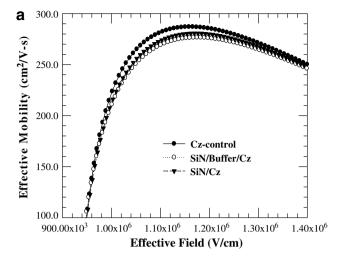

Fig. 11. Comparisons of effective mobility for devices with W/L = 50  $\mu$ m/50  $\mu$ m. (a) Cz group; and (b) Hi group.

**Fig. 12.** On-current ( $V_G$  = 1.8 V,  $V_D$  = 1.8 V) versus off-current ( $V_G$  = 0 V,  $V_D$ =1.8 V) with W/L = 10  $\mu$ m/0.4  $\mu$ m.

fore, the interface states from the Si<sub>3</sub>N<sub>4</sub> capping layer are not repaired due to the mechanism of TEOS blocking hydrogen diffusion.

Therefore, the percentage increase of Gm for the SiN/buffer/Cz split is lower than that for the SiN/Cz split owing to the large amount of un-repaired interface traps, compared with the Cz-controls. In addition, it is noted that  $I_{\rm cp}$  of SiN/buffer/Hi split only

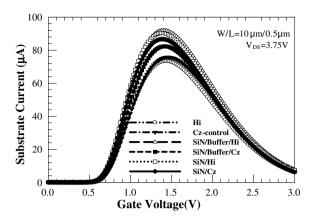

**Fig. 13.** Substrate current versus gate voltage. The device size is  $W/L = 10 \ \mu m/0.5 \ um$ .

**Fig. 14.**  $\Delta V_{\rm TH}$  after hot-electron stressing performed at  $V_{\rm DS}$  = 3.75 V and  $V_{\rm GS}$  at the peak substrate current. The device size is W/L = 10  $\mu$ m/0.5  $\mu$ m.

slightly increases over the SiN/Hi split. Therefore, the effect of hydrogen diffusion or blocking is not a serious concern for the SiN/buffer/Hi split. Besides, the larger  $I_{\rm cp}$  of long length with Si<sub>3</sub>N<sub>4</sub> capping layer than that of short length was a direct evidence to explain the S.S. increases for long channel devices due to less hydrogen species diffusion at long channel devices.

Fig. 11 compares the effective mobility for devices with  $W/L = 50 \,\mu\text{m}/50 \,\mu\text{m}$ . For Cz group, as shown in Fig. 7a, degraded behaviors are observed for the splits with  $\text{Si}_3\text{N}_4$  capping. However, for Hi group, as shown in Fig. 7b, it is very interesting to note that the buffer layer prevents the mobility degradation from the  $\text{Si}_3\text{N}_4$  capping.

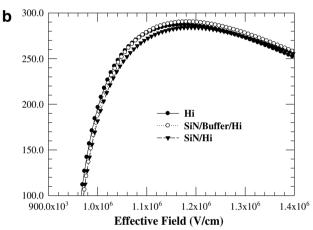

Fig. 12 shows the distribution of the on-current ( $V_G$  = 1.8 V,  $V_D$  = 1.8 V) versus off-current ( $V_G$  = 0 V,  $V_D$  = 1.8 V) with W/L = 10  $\mu$ m/0.4  $\mu$ m. Lower off-current is found for the splits on the Hi-wafers, owing to its better surface quality.

Fig. 13 shows substrate current ( $I_{\rm sub}$ ) versus gate voltage for all splits ( $V_{\rm DS}$  = 3.75 V) for devices with W/L = 10 µm/0.5 µm. The Si<sub>3</sub>N<sub>4</sub>-capped splits exhibit larger  $I_{\rm sub}$  than the control splits for both Cz and Hi-wafers owing to the enhancement of the ionization rate caused by the channel strain [30]. In addition, among the SiN-capped splits, the SiN/buffer/Hi split exhibits the largest  $I_{\rm sub}$  owing to its largest transconductance.

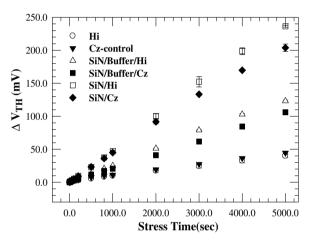

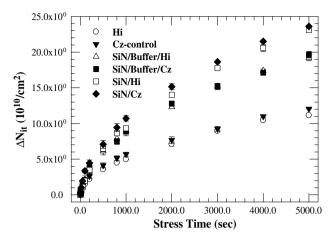

Figs. 14 and 15 show the threshold voltage shift ( $\Delta V_{TH}$ ) and the interface state density increase as a function of stress time for all splits after hot-electron (HC) stressing at  $V_{DS}$  = 3.75 V and  $V_{GS}$  at the peak substrate current, and the device size is W/L = 10  $\mu$ m/0.5  $\mu$ m. The SiN-capping splits for both Cz and Hi-wafers exhibit

**Fig. 15.** Interface trap density generation measured after hot-electron stressing performed at  $V_{DS}$  = 3.75 V and  $V_{GS}$  at the peak substrate current. The device size is W/L = 10  $\mu$ m/0.5  $\mu$ m.

**Fig. 16.** Transconductance degradation after hot-electron stressing performed at  $V_{\rm DS}$  = 3.75 V and  $V_{\rm GS}$  at the peak substrate current. The device size is W/L = 10  $\mu$ m/0.5  $\mu$ m.

**Fig. 17.** Increase in charge pumping current after hot-electron stressing performed at  $V_{\rm DS}$  = 3.75 V and  $V_{\rm GS}$  at the peak substrate current. The device size is W/L = 10  $\mu$ m/0.5  $\mu$ m.

the worst HC degeneration, while the improvement of the HC degradation by using the TEOS buffer layers is obviously seen. However, the threshold voltage shift of the SiN/Hi split is worse than that of the SiN/Cz split, similar to the case of the buffer-layer splits,

owing to the fact that the fresh maximum Gm values of both the SiN/Hi split and the SiN/buffer/Hi split are larger than those of the SiN/Cz and SiN/buffer/Cz splits.

It is important to note that, although the  $I_{\rm sub}$  is high for the SiN/buffer samples, significant improvement in HC resistance than that without the buffer is observed. Since the HC tends to break the Si-H bonds during the stressing, and much severe degradation will occur with higher Si-H density. The use of TEOS buffer layer can effectively block the diffusion of hydrogen species into the channel region, therefore less HC degradation in terms of  $V_{\rm TH}$  shift and interface-state generation is achieved.

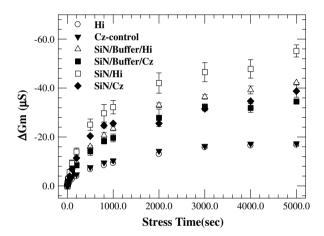

Fig. 16 shows the transconductance degradation as a function of stress time for all splits after receiving hot-electron (HC) stressing at  $V_{\rm DS}$  = 3.75 V and  $V_{\rm GS}$  at the peak substrate current. The device size is W/L = 10  $\mu$ m/0.5  $\mu$ m. The SiN/Hi split shows the worst Gm degradation among all splits owing to the strain enhancement effects and extra hydrogen incorporation mentioned above.

Fig. 17 shows the increase in charge pumping current after 5000 s of hot-carrier stress for devices with  $W/L=10~\mu m/0.5~\mu m$ . The effect of TEOS buffer layer is observed in terms of lower  $\triangle I_{\rm cp}$ . After stressing, the SiN/buffer/Hi split possesses higher  $\triangle I_{\rm cp}$  than the SiN/buffer/Cz split, although in principle the former split should have a better interface quality. Higher  $I_{\rm sub}$  and higher population of generated HC are postulated as the plausible origin for this observation.

#### 4. Conclusions

We have performed a detailed investigation of the LSC channel technique induced by SiN-capping layer with or without buffer layer. Device characteristics including Gm, S.S.,  $I_{\rm Cp}$ , and reliability were studied on devices fabricated with Hi and Cz starting wafers. The Gm and current drivability can indeed be enhanced by capping the Si<sub>3</sub>N<sub>4</sub> layer. We found that the splits with Hi-wafers depict lower S.S. than the splits with Cz-wafers. However, with the incorporation of TEOS buffer layer,  $I_{\rm Cp}$  increases and Gm is degraded for SiN/buffer/Cz splits, contrary to the results of the SiN/buffer/Hi splits. The hot-electron degradation is adversely affected when the Si<sub>3</sub>N<sub>4</sub> capping layer is deposited over the gate, regardless of the types of wafers. When a TEOS buffer layer is inserted prior to the Si<sub>3</sub>N<sub>4</sub> deposition, although still worse than the control ones, significant improvement in hot-carrier resistance over those without the buffer layer is achieved.

### References

- Hoyt JL, Nayfeh HM, Eguchi S, Aberg I, Xia G, Drake T, et al. Strained silicon MOSFET technology. IEDM Tech Dig 2002:23–6.

- [2] Ghani T, Armstrong M, Auth C, Bost M, Charvat P, Glass G, et al. A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors. IEDM Tech Dig 2003:978–80.

- [3] Pidin S, Mori T, Inoue K, Fukuta S, Itoh N, Mutoh E, et al. A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films. IEDM Tech Dig 2004:213–6.

- [4] Welser J, Hoyt JL, Gibbons JF. Electron mobility enhancement in strained-Si Ntype metal-oxide-semiconductor field-effect transistors. IEEE Electron Dev Lett 1994;15:100–2.

- [5] Chen Chien-Hao, Lee TL, Hou TH, Chen CL, Chen CC, Hsu JW, et al. Stress memorization technique (SMT) by selectively strained-nitride capping for sub-65 nm high-performance strained-Si device application. VLSI Tech Dig 2004:56-7.

- [6] Ota K, Sugihara K, Sayama H, Uchida T, Oda H, Eimori T, et al. Novel locally strained channel technique for high performance 55 nm CMOS. IEDM Tech Dig 2002:27–30.

- [7] Momose HS, Nakamura S, Ohguro T, Yoshitomi T, Morifuji E, Morimoto T, et al. A study of hot-carrier degradation in N- and P-MOSFETs with ultra-thin gate oxides in the direct-tunneling regime. IEDM Tech Dig 1997:453–6.

- [8] Heremans P, Bellens R, Groeseneken G, Maes H. Consistent model for the hotcarrier degradation in N-channel and P-channel MOSFETs. IEEE Trans Electron Dev 1988(35):2194–209.

- [9] Lu Ching-Sen, Lin Horng-Chih, Lee Yao-Jen, Huang Tiao-Yuan. Improved hot carrier reliability in strained-channel NMOSFETs with TEOS buffer layer. IRPS 2007:670.

- [10] Izunome Koji, Shirai Hiroshi, Kashima Kazuhiko, Yoshikawa Jun, Hojo Akimichi. Oxygen precipitation in Czochralski-grown silicon wafers during hydrogen annealing. Appl Phys Lett 1996(68):49–50.

- [11] Matsushita Y, Samata S, Miyashita M, Kubota H. Improvement of thin oxide quality by hydrogen annealed wafer. IEDM Tech Dig 1994:321–4.

- [12] Takagi S, Mizuno T, Tezuka T, Sugiyama N, Numata T, Usuda K, et al. Channel structure design fabrication and carrier transport properties of strained-Si/SiGe-on-insulator (strained-SOI) MOSFETS. IEDM Tech Dig 2003:57-60.

- [13] Thompson SE, Armstrong M, Auth C, Cea S, Chau R, Glass G, et al. A logic nanotechnology featuring strained-silicon. IEEE Trans Electron Dev 2004:191–3.

- [14] Zhao W, He J, Belford RE, Wernersson L, Seabaugh A. Partially depleted SOI MOSFETs under uniaxial tensile strain. IEEE Trans Electron Dev 2004:317–23.

- [15] Hoyt JL, Nayfeh HM, Eguchi S, Aberg I, Xia G, Drake T, et al. Strained silicon MOSFET technology. IEDM Tech Dig 2002:23–6.

- [16] Lee BH, Mocuta A, Bedell S, Chen H, Sadana D, Rim K, et al. Performance enhancement on sub-70 nm strained silicon SOI MOSFETs on ultra-thin thermally mixed strained silicon/SiGe on insulator (TM-SGOI) substrate with raised S/D. IEDM Tech Dig 2002:946–8.

- [17] Mizuno T, Sugiyama N, Tezuka T, Numata T, Maeda T, Takagi S. Design for scaled thin film strained-SOI CMOS devices with higher carrier mobility. IEDM Tech Dig 2002:31–4.

- [18] Ito S, Namba H, Yamaguchi K, Hirata T, Ando K, Koyama S, et al. Mechanical stress effect of etch-stop nitride and its impact on deep submicron transistor design. IEDM Tech Dig 2000:247–50.

- [19] Shimizu A, Hachimine K, Ohki N, Ohta H, Koguchi M, Nonaka Y, et al. Local mechanical-stress control (LMC): a new technique for CMOS-performance enhancement. IEDM Tech Dig 2001:433–6.

- [20] Steegen A, Stucchi M, Lauwers A, Maex K. Silicide induced pattern density and orientation dependent transconductance in MOS transistors. IEDM Tech Dig 1999:497–500.

- [21] Ghani T, Armstrong M, Auth C, Bost M, Charvat P, Glass G, et al. A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors. IEDM Tech Dig 2003:978–80.

- [22] Scott G, Lutze J, Rubin M, Nouri F, Manley M. NMOS drive current reduction caused by transistor layout and trench isolation induced stress. IEDM Tech Dig 1999:827–30.

- [23] Maikap S, Liao MH, Yuan F, Lee MH, Huang C, Chang ST, et al. Package-strainenhanced device and circuit performance. IEDM Tech Dig 2004:233–6.

- [24] Lin HN, Lu CY, Lin HC, Huang TY. Material process and device characteristics analyses of CMOS with local and global strained silicon channel (I). Nano Commun 2005(12):44-9.

- [25] Welser J, Hoyt JL, Takagi S, Gibbons JF. Strain dependence of the performance enhancement in strained-Si N-MOSFETs. IEDM Tech Dig 1994:373–6.

- [26] Thompson SE, Sun G, Wu K, Kim J, Nishida T. Key differences for processinduced uniaxial vs. substrate-induced biaxial stressed Si and Ge channel MOSFETs. IEDM Tech Dig 2004:221–4.

- [27] Leitz CW, Currie MT, Lee ML, Cheng Z-Y, Antoniadis DA, Fitzgerald EA. Hole mobility enhancements and alloy scattering-limited mobility in tensile strained Si/SiGe surface channel metal-oxide-semiconductor field-effect transistors. J Appl phys 2002(92):3745-51.

- [28] Sze SM. Physics of semiconductor devices, 2nd ed.; 1985 [p. 69].

- [29] Lu Chia-Yu, Lu Ching-Sen, Hsieh Yu-Lin, Lee Yao-Jen, Lin Horng-Chih, Huang Tiao-Yuan. Impacts of LP-SiN capping layer and lateral diffusion of interface trap on hot carrier stress of NMOSFETs. SSDM 2006:528.

- [30] Sano N, Tomizawa M, Yoshii A. Temperature dependence of hot carrier effects in short-channel Si-MOSFETs. IEEE Trans Electron Dev 1995(42):2211–6.

- [31] Lu Chia-Yu, Lin Horng-Chih, Lee Yao-Jen, Shie Yu-Lin, Chao Chih-Cheng. Impacts of LP-SiN capping layer on the device characteristics and hot carrier degradation of NMOSFETs. IEEE Trans Electron Dev Mater Reliab 2007;7:175–80.