## Bi 3.25 La 0.75 Ti 3 O 12 thin films on ultrathin Al 2 O 3 buffered Si for ferroelectric memory application

San-Yuan Chen, Chia-Liang Sun, Shi-Bai Chen, and Albert Chin

Citation: Applied Physics Letters 80, 3168 (2002); doi: 10.1063/1.1471937

View online: http://dx.doi.org/10.1063/1.1471937

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/80/17?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Characteristics of Pt/Bi 3.25 La 0.75 Ti 3 O 12 / ZrO 2 / Si structures using ZrO 2 as buffer layers for ferroelectric-gate field-effect transistors

J. Vac. Sci. Technol. A 22, 1739 (2004); 10.1116/1.1759352

Physical characteristics and electrical properties of Sr 0.8 Bi 2+x Ta 2 O 9 films on Al 2 O 3 / Si annealed at high temperature

J. Appl. Phys. 94, 6735 (2003); 10.1063/1.1621716

Effect of annealing temperature on physical and electrical properties of Bi 3.25 La 0.75 Ti 3 O 12 thin films on Al 2 O 3 -buffered Si

Appl. Phys. Lett. 80, 1984 (2002); 10.1063/1.1459115

Fatigue-free samarium-modified bismuth titanate ( Bi 4x Sm x Ti 3 O 12 ) film capacitors having large spontaneous polarizations

Appl. Phys. Lett. 79, 3137 (2001); 10.1063/1.1415353

Bi 3.25 La 0.75 Ti 3 O 12 thin films prepared on Si (100) by metalorganic decomposition method Appl. Phys. Lett. **78**, 1733 (2001); 10.1063/1.1355012

APPLIED PHYSICS LETTERS VOLUME 80, NUMBER 17 29 APRIL 2002

## Bi<sub>3.25</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> thin films on ultrathin Al<sub>2</sub>O<sub>3</sub> buffered Si for ferroelectric memory application

San-Yuan Chena) and Chia-Liang Sun

Department of Materials Science and Engineering, National Chiao Tung University, 300 Hsinchu, Taiwan, Republic of China

## Shi-Bai Chen and Albert Chin

Department of Electronics Engineering, National Chiao Tung University, 300 Hsinchu, Taiwan, Republic of China

(Received 4 June 2001; accepted for publication 20 February 2002)

We have investigated the physical and electrical properties of Bi<sub>3.25</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> (BLT) thin films on Pt/Ti/SiO2/Si and on Al2O3(6 nm)/Si, which are used for one-transistor-one-capacitor and one-transistor ferroelectric memory, respectively. The BLT thin films on both substrates show good capacitance-voltage characteristics and the same threshold voltage shift of 1.6 V at applied ±10 V bias. However, the leakage current of BLT on  $Al_2O_3/Si$  at -100 kV/cm is two orders of magnitude lower than that on Pt. The comparable memory characteristics and much reduced leakage current of BLT on Al<sub>2</sub>O<sub>3</sub>/Si are the strong advantages as compared with BLT on Pt because it is directly related to switching energy and device scaling down. © 2002 American Institute of Physics.

[DOI: 10.1063/1.1471937]

Ferroelectric random access memory (FRAM) has attracted much attention recently because of better speed performance than Flash memory and smaller size than static RAM. The current cell structure of FRAM is one transistor and one capacitor (1T-1C) type where the data are memorized in the metal/ferroelectric/metal (MFM) capacitor.<sup>2-6</sup> To utilize the full advantage of FRAM, one transistor (1T) ferroelectric metal-oxide-semiconductor field effect transistor (FeMOSFET)-type memory is desirable because of the same small 1T cell structure as Flash memory. Further, the ferroelectric effect induced voltage can be amplified by the transistor in 1T MOSFET cell that gives higher sensitivity than 1T-1C cell. Unfortunately, the progress of 1T FeMOSFET memory is obstructed by the strong interface reaction between most ferroelectric materials and Si that greatly degrades the device characteristics.<sup>7,8</sup> Recently, we have developed 1T FeMOSFET memory using Al<sub>2</sub>O<sub>3</sub><sup>9,10</sup> as both gate dielectric for MOSFET and interface reaction barrier between ferroelectric Pb(Zr,Ti)O3 (PZT) and Si. Good transistor and memory characteristics are obtained simultaneously because of good gate dielectric integrity and interface property of Al<sub>2</sub>O<sub>3</sub>. 9,10 In this letter, we have investigated the stacked gate dielectric of Bi<sub>3.25</sub>La<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> (BLT)/Al<sub>2</sub>O<sub>3</sub> on Si because BLT is another promising ferroelectric material with excellent nonfatigue behavior on Pt electrode. 11

Four-inch, p-type (100) Si wafers with  $\sim 10 \Omega$  cm resistivity were used in this study. For the MFM structure, a 150nm-thick Pt was first deposited on SiO<sub>2</sub>(200 nm)/Si as the bottom electrode. For the FeMOS structure, a 6-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric was first formed on Si and the detailed formation procedure was reported previously.<sup>9,10</sup> Then BLT was deposited on both Pt/Ti/SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Si by chemical solution deposition using spin coating at 4000 rpm for 30 s.5,6 For the chemical solution synthesis, bismuth acetate, lanthanum acetate hydrate, and titanium n-butoxide were used as precursors and dissolved in the solvents composed of acetic acid, 2-methoxythanol, and glycerol in sequence. Excess 10% Bi precursor was added to compensate for the Bi loss during annealing. After each coating, the wet films were pyrolyzed for several minutes and the formed multilayer films were annealed at 650 °C for 1 h. Au was used as upper electrode for both capacitor structures and Al bottom electrode was used for FeMOS capacitor at the bake side of Si substrates. The total thickness of BLT is about 420 nm as measured by cross-sectional scanning electron microscopy (SEM) images and the capacitor area is  $9 \times 10^{-4}$  cm<sup>2</sup>. The phase and surface microstructure of BLT films were observed by x-ray diffraction (XRD) and SEM. Transmission electron microscopy (TEM) was used to investigate the interface characteristics of BLT film grown on Al<sub>2</sub>O<sub>3</sub>/Si. The electrical properties were characterized by capacitance-voltage (C-V) and current density-voltage (J-V) by using Hewlett Packard 4284 and 4155B, respectively.

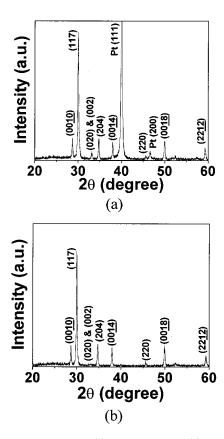

Figures 1(a) and 1(b) show the XRD patterns of BLT thin films deposited on Pt/Ti/SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Si, respectively. As shown in Fig. 1(a), BLT on Pt is polycrystalline without preferred orientation, 12 even though the bottom Pt has preferred (111) orientation. In the case of BLT deposited on amorphous Al<sub>2</sub>O<sub>3</sub> shown in Fig. 1(b), the structure is also polycrystalline and the XRD pattern is almost the same as that on Pt. Thus, high quality ferroelectric BLT can be formed on both polycrystalline Pt and amorphous Al<sub>2</sub>O<sub>3</sub>.

a)Electronic mail: sychen@cc.nctu.edu.tw

FIG. 1. XRD patterns of BLT on (a)  $Pt/Ti/SiO_2/Si$  and (b)  $Al_2O_3(6 \text{ nm})/Si$ .

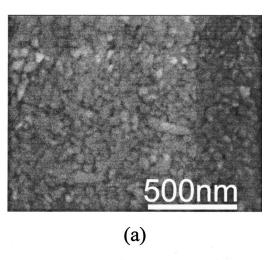

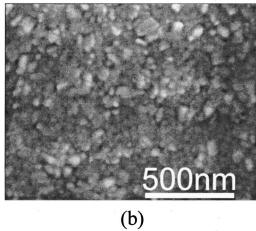

We have also examined the microstructures of BLT thin films deposited on Pt/Ti/SiO $_2$ /Si and Al $_2$ O $_3$ /Si by SEM, and the images are shown in Figs. 2(a) and 2(b), respectively. The grain sizes of BLT on Pt/Ti/SiO $_2$ /Si and Al $_2$ O $_3$ /Si are almost the same, about 50 nm, even though the structure of Pt substrate is polycrystalline that is quite different from amorphous Al $_2$ O $_3$ . The near same grain size of BLT on Pt/Ti/SiO $_2$ /Si or Al $_2$ O $_3$ /Si observed by SEM is consistent with the XRD analysis shown in Fig. 1, which suggests that BLT on both substrates may have close material quality.

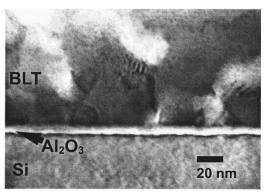

Figure 3 shows the cross-sectional TEM picture of the BLT/Al<sub>2</sub>O<sub>3</sub>/Si structure and reveals only a slight interface layer on the top of Al<sub>2</sub>O<sub>3</sub>. One possible reason may be due to the fact that the atoms in BLT diffuse to Al<sub>2</sub>O<sub>3</sub> gate dielectric. This result is in sharp contrast to the obvious thick intermediate amorphous layer reported by Choi *et al.*, <sup>13</sup> which may be due to the difference in substrate temperature between pulsed ablation deposition and chemical solution deposition. Without the appearance of thick amorphous layer, the ferroelectric BLT film could directly come in contact with the buffer layer this indicates the better interface between them since the memory performance of capacitors may be improved.

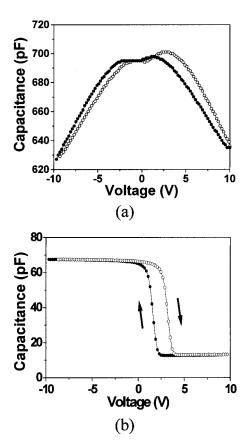

We have further studied the memory properties using high frequency (1 MHz) C-V measurement, and Figs. 4(a) and 4(b) show the C-V characteristics of BLT on Pt/Ti/SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Si, respectively. As shown in Fig. 4(a) the C-V characteristics of BLT on Pt have the typical butterfly pattern, which is similar to that of other ferroelectric materials. After  $\pm 10$  V applied voltages, a peak voltage difference of 1.6 V is obtained that is due to the polarization effect of BLT. For BLT on Al<sub>2</sub>O<sub>3</sub>/Si, the hysteresis C-V

FIG. 2. SEM images of BLT on (a) Pt/Ti/SiO $_2$ /Si and (b)  $Al_2O_3(6\ nm)/Si.$

curves shown in Fig. 4(b) are related to the ferroelectric properties of BLT because Al<sub>2</sub>O<sub>3</sub> gate dielectric has negligible hysteresis. 9,10 The decrease of capacitance value at positive gate bias in the FeMOS structure is due to the small series capacitance in Si depletion region. The phenomenon is different from that in the MFM structure because of the negligible depletion width in metal. A threshold voltage shift of 1.6 V is measured for BLT on Al<sub>2</sub>O<sub>3</sub>/Si that is the same as that in MFM capacitor. The same voltage shift suggests that the electric memory property of BLT on Al<sub>2</sub>O<sub>3</sub>/Si is at least the same or even better than that on Pt because of the additional voltage drop in Al<sub>2</sub>O<sub>3</sub> gate dielectric and reduced electric field in BLT.

ect to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: FIG. 3. Cross-sectional TEM image of BLT on Al<sub>2</sub>O<sub>3</sub>(6 nm)/Si. 1 May 2014 06:22:28

FIG. 4. C-V characteristics of BLT on (a) Pt/Ti/SiO $_2$ /Si and (b) Al $_2$ O $_3$ (6 nm)/Si.

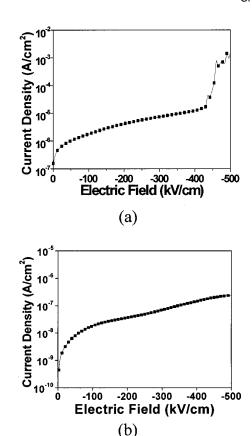

We have also investigated the capacitor leakage current because it is one of the most important properties for a memory capacitor. Figures 5(a) and 5(b) show J-V characteristics of BLT on Pt/Ti/SiO<sub>2</sub>/Si and on Al<sub>2</sub>O<sub>3</sub>/Si, respectively. The leakage current density of BLT on Pt is 1.8  $\times 10^{-6}$  A/cm<sup>2</sup> at -100 kV/cm that is comparable to that of (118)-oriented Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>, 15 and the high dielectric breakdown field of -450 kV/cm is also comparable to that of (001)-oriented  $Bi_4Ti_3O_{12}$ . These results indicate the good quality of BLT on Pt. 15 On the other hand, the leakage current density of BLT on Al<sub>2</sub>O<sub>3</sub>/Si at -100 kV/cm is 1.8  $\times 10^{-8}$  A/cm<sup>2</sup> that is almost two orders of magnitude lower than BLT on Pt. This low leakage current is comparable with that of vanadium-doped  ${\rm Bi_4Ti_3O_{12}}^{16}$  and smaller than our previous data of PZT/Al<sub>2</sub>O<sub>3</sub>/Si FeMOS. <sup>16-17</sup> In addition, no dielectric breakdown up to -500 kV/cm also implies that BLT on Al<sub>2</sub>O<sub>3</sub>/Si has better dielectric integrity than that on Pt/Ti/SiO<sub>2</sub>/Si. This smaller leakage current and the larger breakdown field may be due to the additional large energy barrier of  ${\rm Al_2O_3}$  dielectric  $^{9,10}$  and no intermediate phase in the interface. The much reduced leakage current of BLT on Al<sub>2</sub>O<sub>3</sub>/Si is the strong advantage as compared with BLT on Pt because it is directly related to the applied switching energy and technology scaling down.

In conclusion, BLT films on Pt/Ti/SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Si substrates were investigated in this work. Both MFM and FeMOS capacitors show good C-V characteristics and have the same threshold voltage shift of 1.6 V at  $\pm 10$  V applied voltages. The leakage current density of BLT FeMOS capacitors is about  $1.8\times 10^{-8}$  A/cm<sup>2</sup> at -100 kV/cm that is two

FIG. 5. J-V characteristics of BLT on (a) Pt/Ti/SiO $_2$ /Si and (b) Al $_2$ O $_3$ (6 nm)/Si.

orders of magnitude lower than that of MFM capacitors. The excellent memory characteristics and very low leakage current of BLT on  ${\rm Al_2O_3/Si}$  are the merits for 1T ferroelectric memory as compared with 1T-1C cell.

This work has been supported by the National Science Council Contract Nos. NSC90-2215-E-009-061 and NSC89-2215-E-009-100 of Taiwan.

<sup>1</sup> J. F. Scott, Phys. World **8**, 46 (1995).

<sup>&</sup>lt;sup>2</sup> W. Wu, K. H. Wong, C. L. Mak, C. L. Choy, and Y. Z. Zhang, J. Appl. Phys. 88, 2068 (2000).

<sup>&</sup>lt;sup>3</sup>D. Bao, N. Mizutani, X. Yi, and L. Zhang, Appl. Phys. Lett. 77, 1041 (2000).

<sup>&</sup>lt;sup>4</sup>S. H. Kim, D. J. Kim, J. P. Maria, A. I. Kingon, S. K. Streiffer, J. Kim, O. Auciello, and A. R. Krauss, Appl. Phys. Lett. 76, 496 (2000).

<sup>&</sup>lt;sup>5</sup>S. Y. Chen and V. C. Lee, J. Appl. Phys. **87**, 8024 (2000).

<sup>&</sup>lt;sup>6</sup>S. Y. Chen and V. C. Lee, J. Appl. Phys. **87**, 3050 (2000).

<sup>&</sup>lt;sup>7</sup>K. Sugibuchi, Y. Kurogi, and N. Endo, J. Appl. Phys. **46**, 2877 (1975).

<sup>&</sup>lt;sup>8</sup> Y. Shichi, S. Tanimoto, T. Goto, K. Kuroiwa, and Y. Tarui, Jpn. J. Appl. Phys., Part 1 33, 5172 (1994).

<sup>&</sup>lt;sup>9</sup> A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, Symposium on Very Large Scale Integrated Technology, Honolulu, HI, 2000, p. 16.

<sup>&</sup>lt;sup>10</sup> A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, Symposium on Very Large Scale Integrated Technology, Kyoto, Japan, 1999, p. 135.

<sup>&</sup>lt;sup>11</sup> B. H. Park, B. S. Kang, S. D. Du, T. W. Noh, J. Lee, and W. Jo, Nature (London) **401**, 682 (1999).

<sup>&</sup>lt;sup>12</sup> Y. Hou, X. H. Wu, H. Wang, M. Wang, and S. X. Shang, Appl. Phys. Lett. 78, 1733 (2001).

<sup>&</sup>lt;sup>13</sup>T. Choi, Y. S. Kim, C. W. Yang, and J. Lee, Appl. Phys. Lett. **79**, 1516 (2001)

<sup>&</sup>lt;sup>14</sup>M. Sedlar and M. Sayer, J. Appl. Phys. **80**, 372 (1996).

<sup>&</sup>lt;sup>15</sup>T. Watanabe, H. Funakubo, and K. Saito, J. Mater. Res. **16**, 303 (2001).

<sup>&</sup>lt;sup>16</sup>Y. Noguchi and M. Miyayama, Appl. Phys. Lett. **78**, 1903 (2001).

<sup>&</sup>lt;sup>17</sup> A. Chin, M. Y. Yang, C. L. Sun, and S. Y. Chen, IEEE Electron Device Lett. 22, 336 (2001).