Thin Solid Films 398-399 (2001) 544-548

# Integration of MOCVD titanium nitride with collimated titanium and ion metal plasma titanium for 0.18-µm logic process

J.K. Lana, Y.L. Wangb,c,\*, K.Y. Lod, C.P. Liue, C.W. Liub,c, J.K. Wangb, Y.L. Chengb, C.G. Chaua

<sup>a</sup>Department of Material Science and Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan, ROC

<sup>b</sup>Taiwan Semiconductor Manufacturing Co., Ltd, Hsinchu, Taiwan, ROC

<sup>c</sup>Department of Electrical Engineering, National Chi-Nan University, Nan-Tou, Taiwan, ROC

<sup>d</sup>Department of Applied Physics, National Chiayi University, Chiayi, Taiwan, ROC

<sup>c</sup>Department of Material Science Engineering, National Cheng Kung University, Tanani, Taiwan, ROC

#### **Abstract**

Both collimated titanium (CO-Ti) and ion metal plasma titanium (IMP-Ti) have been widely used for plug liner layers. The focused ion beam (FIB) images of these films show that the IMP-Ti surface is granular and the CO-Ti surface is amorphous. It is concluded that the lower reflectivity and resistivity of IMP-Ti films are caused by the fact that IMP-Ti has a larger grain than that of the CO-Ti films. We define a grain size factor (GF) and find that the activation energy of grain growth of IMP-Ti film is 3.8 times larger than that of CO-Ti film. The electric measurement of vias resistance shows that IMP-Ti plug liner gives 13.6% higher via resistance and broader distribution than that of the CO-Ti plug liner. From the experimental data, we can conclude that there are three factors that make the IMP Ti plug liner process have higher vias resistance. These three factors are IMP-Ti resistivity, IMP-Ti thickness and CVD TiN thickness. © 2001 Elsevier Science B.V. All rights reserved.

Keywords: Ion metal plasma (IMP) titanium; Collimated titanium; Vias resistance

#### 1. Introduction

After contact and/or via hole definition, titanium (Ti) followed by titanium nitride (TiN) is often used as an adhesion promoter and a barrier layer for tungsten (W) plug integration of contact/via in modern ULSI technology [1–3]. Because of the high reaction activity of Ti with other elements, Ti serves as a getter for interfacial impurities and effectively reduces metal oxides, therefore, promoting a good ohmic contact between the vias of the adjacent metal levels. Ti and TiN films have traditionally been processed by physical vapor deposition (PVD) [1,3], but when circuit dimensions continue to shrink, the high aspect ratio of metal schemes gives limited applications for the PVD Ti and TiN [3,5]. For TiN films, the metalorganic chemical vapor deposition

E-mail address: ylwang@tsmc.com.tw (Y.L. Wang).

(MOCVD) [2–6] process can meet the aspect ratio requirement due to the conformal nature of the CVD process. In-situ plasma treatment was found to stabilize the MOCVD TiN films [2,3,7].

However, it is expected that the applicability of MOCVD for Ti liner deposition is problematic since titanium has great affinity for oxygen and nitrogen [8]. Beyond the 0.25-μm generation, there is increasing interest in developing acceptably conformal PVD based Ti liners. The collimated (CO-Ti) and ion metal plasma (IMP-Ti) Ti process has been reported and widely used [9–13] for liner metal deposition to improve the poor bottom coverage of PVD liners. To further investigate these promising PVD processes, this paper presents a comparison of CO-Ti and IMP-Ti based on their resistivity, reflectivity and morphologies. The performance of the IMP-Ti and CO-Ti liner process with the 0.18 μm test vehicle is also investigated.

<sup>\*</sup> Corresponding author. Tel.: 886-3-5781688 ext.: 4230; fax: +886-3-5790298.

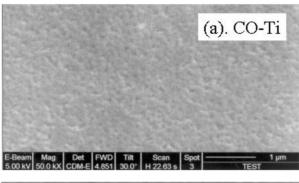

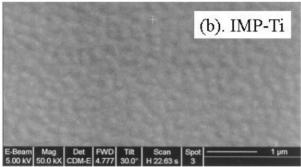

Fig. 1. FIB images of (a) CO-Ti (260 nm) (b) IMP-Ti (260 nm).

## 2. Experimental

The experiments were carried out on 8-inch wafers. For blanket wafers with oxide film, the CO-Ti films are deposited on a heated substrate in an AMAT PVD chamber. The heated substrate temperature was  $100^{\circ}$ C. The deposition of IMP-Ti films was performed on a heated substrate in an AMAT PVD IMP chamber. The heated substrate temperature is  $200^{\circ}$ C. Both the chamber base pressure for CO-Ti and IMP-Ti process are  $< 1 \times 10^{-7}$  torr.

After, via hole definition for patterned wafers with 0.18 µm test vehicles, the tungsten (W) plug process including 30 nm CO-Ti or 20 nm IMP-Ti, 10 nm CVD TiN and 300 nm W was performed. MOCVD TiN films were thermally deposited on a heated substrate in AMAT's MOCVD TiN TxZ chamber using tetrakisdimethyl-amino-titanium (TDMAT) as the reactant. The sequential thermal deposition was followed by an insitu nitrogen (N<sub>2</sub>) plasma densification step, which allows control of the film's resistivity. The 10-nm thick MOCVD TiN was formed by two cycles of deposition and treatment. W was deposited by an AMAT Centura WCVD system. The deposition temperature for W was 430°C. The deposition pressure of W was 80 torr. Tencor RS-35, a four-point probe tool, was used to measure the resistance. The film thickness was measured by SEM, Hitachi 4500. The film morphologies were imaged by the focused ion beam (FIB) process, FEI xP, with 5 kV e-beam. The film reflectivity is measured by NANOS-

PEC, 8000X. The TEM cross-section was analyzed with a Philips Jeol 2010

### 3. Results and discussion

## 3.1. For blanket wafers

The FIB images of the surface of the 260-nm CO-Ti and 260-nm IMP-Ti films on the blanket wafers are shown in Fig. 1. Fig. 1a shows that the resulting CO-Ti film has an amorphous surface. For IMP-Ti, process conditions shape the crystallography of the film with the granular surface (Fig. 1b). The difference in images of these films is related to the following different process conditions. (1) The deposition rate is different. Based on the experimental conditions, the deposition rate of CO-Ti is 47 nm/min. For IMP-Ti process, the deposition rate is 96 nm/min. The IMP-Ti process is twice as fast as the CO-Ti process. (2) The process pressure is different. PVD process is very contamination sensitive. The chamber base pressure before process is controlled at  $< 1 \times 10^{-7}$  torr for both CO-Ti and IMP-Ti processes. But these two different processes have different process pressures. For CO-Ti process, the process pressure is 1.0 mtorr in the experimental conditions. For IMP-Ti process, the deposition pressure of IMP-Ti is 22.0 mtorr. (3) The deposition temperature of IMP-Ti process is 200°C, which is larger than that of CO-Ti (100°C) and provides more thermal energy for grain growth. Fig. 2 shows the EDX profiles of CO-Ti and IMP-Ti films with oxide as an underlayer. The EDX analysis is identical for both processes and no signal shift of Ti, O and Si is observed.

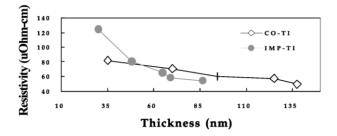

Fig. 3 shows the correlation between film resistivity and thickness for IMP-Ti and CO-Ti films. For thicker films (>260 nm), IMP-Ti and CO-Ti have nearly the same resistivity. For thinner films (<260 nm), IMP-Ti and CO-Ti films have a large differences in the resistiv-

Fig. 2. The EDX analysis of CO-Ti and IMP-Ti.

Fig. 3. The correlation between film resistivity and thickness for IMP-Ti. CO-Ti.

ity. For example, when the Ti thickness is  $\sim 260$  nm, the resistivity of IMP-Ti is 44.5 ( $\mu\Omega$  cm) and the resistivity of CO-Ti is 44.4 ( $\mu\Omega$  cm). The resistivity difference between IMP-Ti and CO-Ti is only 0.1%. When the Ti thickness is  $\sim 90$  nm, the resistivity of IMP-Ti is 54.3 ( $\mu\Omega$  cm) and the resistivity of CO-Ti is 59.8 ( $\mu\Omega$  cm). The resistivity difference between IMP-Ti and CO-Ti is  $\sim 10\%$ . When the Ti thickness is ~30 nm, the resistivity of IMP-Ti is 123.9 ( $\mu\Omega$  cm) and the resistivity of CO-Ti is 82.3 ( $\mu\Omega$  cm). The resistivity difference between IMP-Ti and CO-Ti is  $\sim$  33%. There is a crossover between these two curves. For Ti films with thickness < 50 nm, the resistivities of CO-Ti are less than those of IMP-Ti. However, when the Ti thickness is >50 nm, the resistivities of IMP-Ti are less than those of CO-Ti. The resistivities and film thicknesses are summarized in Table 1.

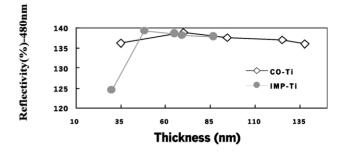

Fig. 4 shows the correlation between film reflectivity and thickness for IMP-Ti and CO-Ti films. The reference material for reflectivity measurement is silicon. The reflectivity measurement is carried out with a wavelength of 480 nm. For film thicknesses >50 nm, both IMP-Ti and CO-Ti films show that their reflectivity decreases with increases in film thickness. When the films are <50 nm, they show lower reflectivity. The reason of this lower reflectivity is that thin metal film will become semi-transparent. When the film thickness is >50 nm, the reflectivity of IMP-Ti is less than that of CO-Ti. This is consistent with the resistivity data. The lower reflectivity and the resistivity of IMP-Ti film can be attributed to their larger grain size.

Table 1 Resistivities<sup>a,b</sup> and film thicknesses<sup>c</sup>

| Thickness (nm) | ρ <sub>CO-Ti*</sub> | $\rho_{\mathrm{IMP-Ti}}$ | $\rho_{\mathrm{CO-Ti}}\!\!-\!\!\rho_{\mathrm{IMP-Ti}}/\rho_{\mathrm{IMP-Ti}}$ |

|----------------|---------------------|--------------------------|-------------------------------------------------------------------------------|

| 260            | 44.47               | 44.53                    | -0.1%                                                                         |

| 90             | 59.88               | 54.27                    | 10.3%                                                                         |

| 30             | 82.25               | 123.93                   | -33.6%                                                                        |

<sup>\*</sup>ρ: resistivity

Fig. 4. Reflectivity (480 nm) vs. film thickness for CO-Ti and IMP-Ti

The film resistivity is related to structural imperfection [14]. A larger grain size gives lower grain boundary density and lower structural imperfection. Thus, the resistivity of metal films is related to their grain size. The larger the grain size is, the smaller the resistivity will be. We define a grain size factor (GF) which is proportional to the reverse of resistivity  $(\rho)$ , i.e:

# $GF \propto 1/\rho$

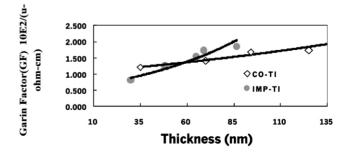

For IMP-Ti and CO-Ti films, the correlations between film thickness and GF are shown in Fig. 5. By using exponential curve fitting, the mathematical equations for the GF are shown below.

$$GF_{IMP-Ti} = 0.565*EXP[0.0015 W]$$

for IMP-Ti

$$GF_{CO-Ti} = 1.0372*EXP[0.0005 W]$$

for CO-Ti

where W is film thickness (nm).

We assume that the grain size and film thickness meet Arrhenius equation, i.e:

$$GF = C*EXP[Ea/RT]$$

where C is a process related constant, Ea is the activation energy for grain growth, R is the gas constant and T is the process temperature. The activation energy of grain growth can be easily calculated according to above equations. For IMP-Ti process, its Ea is 5.90 J/mol. For CO-Ti deposition, its Ea is 1.55 J/mol. The activation energy of grain growth for IMP-Ti is 3.8 times larger than that of CO-Ti. This explains why the IMP-

Fig. 5. The grain size factor vs. thickness for CO-Ti and IMP-Ti.

$<sup>^{</sup>a}$  The measured resistivity of 11 nm CVD TiN is 250  $\mu\Omega\text{-cm}.$

$<sup>^{\</sup>text{b}}$  The measured resistivity of 300 nm W is 11.9  $\mu\Omega\text{-cm}.$

<sup>&</sup>lt;sup>c</sup> Film thickness is measured by SEM.

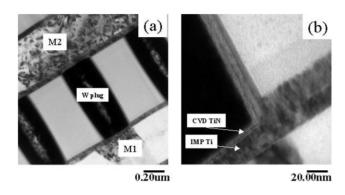

Fig. 6. The TEM pictures of IMP-Ti process (a) cross-section, (b) the via bottom.

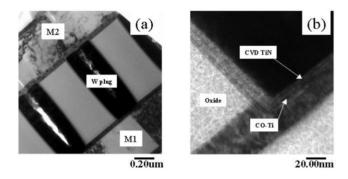

Fig. 7. The TEM pictures of CO-Ti process. (a) Cross-section, (b) the via bottom.

Ti process needs higher deposition temperatures than that of the CO-Ti process.

# 3.2. For patterned wafers

Fig. 6 is the TEM cross-section pictures for IMP-Ti process. Fig. 6a shows that the tested via structure for

Fig. 8. The via resistance for different Ti processes.

IMP-Ti process has an aspect ratio of 3:1. Fig. 6b shows that the thickness of IMP-Ti liner is 7.3 nm. The via bottom step coverage of IMP-Ti liner is 36%. The thickness of CVD TiN above IMP-Ti is 6.7 nm. The via bottom step coverage of CVD TiN in IMP-Ti process is 61%. Fig. 7 is the TEM cross-section pictures for CO-Ti process. Fig. 7a shows that the tested via structure for CO-Ti process has the same aspect ratio (3:1) with IMP-Ti. Fig. 7b shows that the thickness of CO-Ti liner is 4.7 nm. The via bottom step coverage of CO-Ti liner is 16%. The thickness of CVD TiN above CO-Ti is 4.6 nm. The via bottom step coverage of CVD TiN in CO-Ti process is 42%. The via bottom step coverage of IMP-Ti process is 1.6 times better than that of CO-Ti process. The via bottom step coverage of CVD TiN has 19% difference between IMP-Ti and CO-Ti process. The above TEM data are summarized in Table 2.

Fig. 8 shows the via resistance for IMP-Ti and CO-Ti liner processes. It shows that the IMP-Ti process gives a via resistance 13.6% higher than that of CO-Ti process. For the via plug process, the components that contribute to the via resistance are tungsten (W), CVD TiN and Ti, i.e.

vias resistance=Ti resistance+TiN resistance +W resistance.

| Table 2                                        |  |

|------------------------------------------------|--|

| The TEM thickness for IMP-Ti and CO-Ti process |  |

| Process/<br>parameters | Aspect ratio | Ti thickness (nm) | Ti step<br>coverage <sup>a</sup> | CVD TiN<br>(nm) <sup>b</sup> | CVD TiN step<br>Coverage <sup>c</sup> |

|------------------------|--------------|-------------------|----------------------------------|------------------------------|---------------------------------------|

| IMP-Ti                 | 3            | 7.3               | 36%                              | 6.7                          | 61%                                   |

| CO-Ti                  | 3            | 4.7               | 16%                              | 4.6                          | 42%                                   |

<sup>&</sup>lt;sup>a</sup> via bottom step coverage for Ti.

Table 3

The vias resistance of different liner Ti process

| Vias resistance                               | Measured vias resistance $(R/R_{CO-Ti})$ | Calculated vias resistance $(R/R_{\mathrm{CO-Ti}})$ |

|-----------------------------------------------|------------------------------------------|-----------------------------------------------------|

| $R/R_{\text{co-Ti}}$                          | 1                                        | 1                                                   |

| $R/R_{	ext{CO-Ti}} \ R/R_{	ext{IMP-Ti}}$      | 1.136                                    | 1.128                                               |

| Difference $(R_{IMP-Ti}-R_{CO-Ti}/R_{CO-Ti})$ | 13.60%                                   | 12.80%                                              |

<sup>&</sup>lt;sup>b</sup> CVD TiN thickness above Ti at the viz bottom.

<sup>&</sup>lt;sup>c</sup> via bottom step coverage for CVD TiN.

These three films are in serial connection when we study the via resistance. The vias resistances by measurement and calculation are summarized in Table 3. The calculated via resistance difference is 12.8%. This is close to the measured 13.6% difference. We can conclude that there are three factors that make the IMP-Ti processes higher via resistances. These three factors are IMP-Ti resistivity, IMP-Ti thickness and CVD TiN thickness. In the 12.8% of calculated via resistance difference, the percentage caused by Ti resistance difference is 7.9%, which is the combination of the Ti thickness and the resistivity difference. The percentage caused CVD TiN thickness difference is only 4.8%. Therefore, the dominant factor is Ti liner that effects the via resistance. It includes Ti thickness, resitivity and IMP-Ti or CO-Ti.

### 4. Conclusion

In this study, CO-Ti and IMP-Ti are combined with MOCVD titanium nitride (CVD TiN) for the via plug barrier process in the 0.18 µm scheme. The morphology of IMP-Ti and CO-Ti analyzed by FIB shows that IMP-Ti surface is granular and CO-Ti is amorphous. The TEM cross-section pictures shows that the via bottom step coverage of IMP-Ti is 36%. For CO-Ti, the via bottom step coverage is 16%. The resistivities of IMP-Ti and CO-Ti films will change with the film thickness for thicknesses < 200 nm. For example, when the IMP-Ti and CO-Ti thickness is ~260 nm, the resistivity difference between IMP-Ti and CO-Ti is only 0.1%. When the thickness is  $\sim 90$  nm, the resistivity difference between IMP-Ti and CO-Ti is ~10%. When the thickness is ~30 nm, the resistivity difference between IMP-Ti and CO-Ti is  $\sim 33\%$ . When the thickness is < 50nm, the resistivity of CO-Ti is less than that of IMP-Ti. However, when the film thickness is >50 nm, the resistivity of IMP-Ti is less than that of CO-Ti. The reflectivities of IMP-Ti and CO-Ti films also show the same result. The lower reflectivities and resistivities of IMP-Ti films are attributed to their larger grain size because the resistivities of metal films are related to their grain size. The larger the grain size the smaller is the resistivity. We define a grain size factor (GF) and find that the activation energy of grain growth for IMP-Ti process is 3.8 times larger than that for CO-Ti process.

The electrical measurement of vias resistance shows that IMP-Ti process gives 13.6% higher vias resistance than that of CO-Ti process. For the via plug process, the components that contribute to the vias resistance are tungsten (W), CVD TiN and Ti. These three films are in serial connection. From the TEM thickness data and the resistivities data, the vias resistance difference between IMP-Ti and CO-Ti processes can be calculated. The calculated vias resistance difference is 12.8%. This is close to the measured difference 13.6%. We can

conclude that there are three factors that make the IMP Ti process higher vias resistance. These three factors are IMP-Ti resistivity, IMP-Ti thickness and CVD TiN thickness. In the calculated 12.8% difference of vias resistance, the percentage caused by Ti resistance difference is 7.9%, which is the combination of Ti thickness and its resistivity difference. The calculated vias resistance difference caused by CVD TiN is only 4.8%. For the impact on vias resistance, Ti liner is 1.6 times heavier than that of CVD TiN. Therefore, for 0.18  $\mu m$  process, the dominant factor that will impact the vias resistance is the Ti film, which includes its thickness, resitivity, IMP-Ti, or CO-Ti.

#### References

- [1] S.K. Ghandhi, VLSI Fabrication Principles Silicon and Gallium Arsenide, 2nd Edn., John Wiley, 1994, p. 545.

- [2] A. Hausmann, G. Weidner, G. Ritter, Advanced Metallization and Interconnect Systems for ULSI Applications in 1997, Conference Proceedings ULSI XIII, Materials Research Society, 1998, pp. 111–115.

- [3] A. Paranjpe, M. Islamraja, J. Vac. Sci. Technol. B 13 (5) (1995) 2105–2114.

- [4] Y.P. Chen, G.A. Dixit, J.P. Lu, J.D. Luttmer, R.H. Havemann, Advanced Metallization and Interconnect Systems for ULSI Applications in 1997, Conference Proceedings ULSI XIII, Materials Research Society, 1998, pp. 57–62.

- [5] H.S. Choe, M. Danek, Proceeding of International Interconnect Technology Conference (IITC), IEEE, 1999, pp. 62–64.

- [6] T. Itoh, T.J. Konno, R. Sinclair, I.J.M.M. Raaijmakers, B.E. Robertrs, Mat. Res. Soc. Symp. Proc. 337 (1994) 735–740.

- [7] A. Jain, C. Simpson, T. Saaranen, R. Venkatraman, M. Herrick, M. Angyal, R. Bajai, C. Dang, S. Das, D. Denning, J. Farkas, D. Watts, C. Capasso, J. Gelatos, R. Islam, B. Smith, T. Sparks, P. Crabtree, S. Filipiak, C. King, B. Fiordalice, H. Kawasaki, J. Klein, S. Venkatesan, E. Weitzman, Advanced Metallization and Interconnect Systems for ULSI Applications in 1997, Conference Proceedings ULSI XIII, Materials Research Society, 1998, pp. 41–47.

- [8] A. Ludviksson, T.T. Kodas, M.J. Hampden-Smith, Advanced Metallization and Interconnect Systems for ULSI Applications in 1997, Conference Proceedings ULSI XIII, Materials Research Society, 1998, pp. 149–155.

- [9] K. Macak, V. Kouznetsov, J. Schneider, U. Helmersson, I. Petrov, J. Vac. Sci. Technol. A 18 (4) (2000) 1533–1537, July / Aug

- [10] E. Klawuhn, G.C. D'Couto, K.A. Ashtiani, P. Rymer, M.A. Biberger, K.B. Levy, J. Vac. Sci. Technol. A 18 (4) (2000) 1546–1549, Jul/Aug.

- [11] B.Y. Yoo, Y.H. Park, H.D. Lee, J.H. Kim, H.K. Kang, M.Y. Lee, H.G. Wang, K.S. Lee, J.V. Gogh, C.H. Chu, S. Lai, B. McClintock, S. Edelstein, F. Chen, Proceeding of International Interconnect Technology Conference (IITC), 1998, pp. 262–264.

- [12] Y. Tanaka, G. Yao, J.V. Gogh, B. Herner, J.Y. Zhang, H.G. Wang, L. Buckley, P. Chakravarthy, A. Mak, S. Ghanayem, Solid-State and Integrated Circuit Technology, Proceedings of the 1998 5th International Conference, 1998, pp. 207–210.

- [13] G.A. Dixit, W.Y. Hsu, A.J. Konecni, S. Krishnan, J.D. Luttmer, R.H. Havemann, J. Forster, G.D. Yao, M. Narasimhan, Z. Xu, S. Ramaswami, F.S. Chen, J. Nulman, International Electron Devices Meeting (IEDM), IEEE, 1996, pp. 357–360.

- [14] J. Wulff, Struct. Properties Mater. 4 (1971) 82.