# Cu Contamination Effect in Oxynitride Gate Dielectrics

Y. H. Lin, F. M. Pan, Y. C. Liao, Y. C. Chen, I. J. Hsieh, and Albert Chin

<sup>a</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan

We have studied the effect of Cu contamination in oxynitride gate dielectrics. Compared to thermal  $SiO_2$  with a physical thickness of 3-5 nm, the oxynitride shows a much improved Cu contamination resistance. Furthermore, the Cu contamination resistance increases with increasing nitrogen content. The mechanism of improved gate dielectric resistance to Cu is due to the strong diffusion barrier properties of oxynitride as observed by secondary ion mass spectroscopy.

© 2001 The Electrochemical Society. [DOI: 10.1149/1.1407834] All rights reserved.

Manuscript submitted April 16, 2001; revised manuscript received June 20, 2001. Available electronically September 28, 2001.

Copper interconnect technology has been widely implemented in very-large-scale-integration (VLSI) processes because it can reduce the back-end resistance-capacitance delay as required for advanced high speed complementary-metal-oxide-semiconductor (CMOS) circuits. However, Cu contamination is an important concern because Cu related front-end gate dielectric degradation has been reported <sup>1-7</sup> and an appropriate Cu barrier metal must be applied to reduce the Cu out-diffusion. Previously, almost all the Cu contamination studies were focused on its effect on SiO<sub>2</sub> gate dielectrics. Presently, however, high-*k* gate dielectrics are necessary for further scaling down the VLSI technology. <sup>8-13</sup> Therefore, the study of Cu contamination in high-*k* dielectric is important for future process integration considerations.

In this paper, we present our studies of the Cu contamination effect in oxynitride gate dielectrics with different N contents. An oxynitride gate dielectric is known to be one of the best candidates used for sub-0.1 µm technology because of its superior boron penetration resistance<sup>14</sup> in combination with its high-*k* properties. In contrast to the increased trap-assisted leakage current<sup>6</sup> or reduced effective barrier<sup>7</sup> in thermal SiO<sub>2</sub> after Cu contamination, we have found negligible electric characteristic degradation in oxynitride gate dielectrics. According to secondary ion mass spectroscopy (SIMS) measurements, the much-improved Cu contamination resistance is due to the largely reduced Cu diffusion through oxynitride. The much better Cu contamination resistance may be an additional merit for high-*k* oxynitride gate dielectrics.

## **Experimental**

4 in. p-type Si(100) wafers with 1-10  $\Omega$  cm resistivity were used in this study. The oxynitride prepared by oxidizing silicon nitride is similar to the process published in the literature. <sup>10</sup> After the standard RCA clean and 300 nm field oxide patterning, the oxynitride was formed by depositing a 3 nm chemical vapor deposition (CVD) SiN from dichlorosilane and ammonia at 750°C, and subsequently, oxidizing at 900°C for 30-70 min. To avoid a reduction of the effective k, a native oxide was eliminated by HF vapor passivation  $^{12-13}$  and in situ desorption inside the low-pressure CVD (LPCVD) system. The additional oxidation after SiN deposition is to reduce the dielectric and interface traps within the SiN, although the effective k value is also reduced. Different oxidation times are used to form oxynitride film of different N contents. The thickness and refractive index of the oxynitrides were measured by ellipsometry, and the dielectric constant k was measured by the voltage-capacitance (C-V) method. Then a 300 nm poly-Si layer was deposited on the oxynitride and n<sup>+</sup> doped by POCl<sub>3</sub>. Finally, MOS capacitors of 100 × 100 μm were fabricated after Al metallization and sintering. The Cu contamination was performed by immersing the Si wafers into a diluted Cu(NO<sub>3</sub>)<sub>2</sub> solution of 10 ppb and 10 ppm. The contaminated MOS capacitor was further annealed at 400°C for 1 h in a nitrogen gas ambient. More details on the Cu contamination process can be found in our previous publications.<sup>6,7</sup> Standard current-voltage (I-V) and C-V measurements were used to investigate the electrical property changes caused by the Cu contamination. The oxygen and nitrogen content in the oxynitride gate dielectric was measured by X-ray photoelectron spectroscopy (XPS).

## **Results and Discussion**

Table I summarizes the dielectric properties of the studied oxynitride dielectrics. The oxynitride thickness after oxidizing for 30, 50, and 70 min are 3.6, 4.4, and 4.7 nm, and the nitrogen content in the oxynitrides are 23, 16, and 14%, respectively. The k values of 4.7, 4.5, and 4.4 are obtained for the 3.6, 4.4, and 4.7 nm oxynitride capacitors, respectively, which give respective an equivalent oxide thickness (EOT) of 3.0, 3.8, and 4.2 nm for the three oxynitride dielectrics. The typical interface trap density from C-V measurement increases from  $3 \times 10^{10}$  to  $1 \times 10^{11}$  eV $^{-1}$ /cm $^2$  for an increasing N content from 14 to 23%, indicating a reasonable interface quality for the oxynitride gate dielectrics.

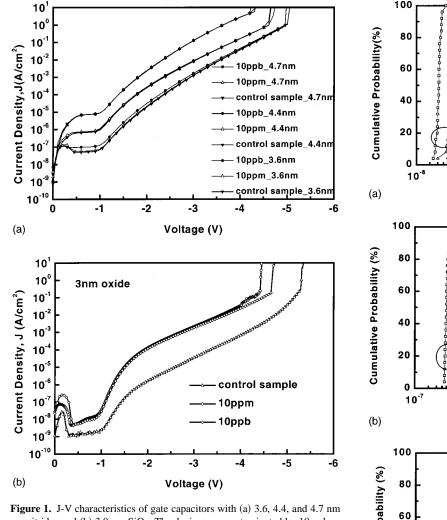

Based on the good dielectric properties of high-k oxynitrides, we have further studied the Cu contamination effect. Figure 1a shows current density-voltage characteristics of different EOT oxynitrides before and after the contamination. For comparison purpose, we also show in Fig. 1b the Cu contamination effect on a 3 nm SiO<sub>2</sub> gate dielectric. As shown in Fig. 1a, a Fowler-Nordheim tunneling current is observed for all three oxynitrides demonstrating good dielectric properties due to a reduced trap density after oxidation. The Cu-contaminated 4.7 nm oxynitride shows a slightly higher pretunneling current, which is due to trap-assisted tunneling as reported previously.<sup>6</sup> In contrast, negligible changes in the pretunneling current<sup>6</sup> and the Fowler-Nordheim tunneling current<sup>7</sup> are observed for the thinnest 3.6 nm oxynitrides. The much-improved Cu contamination resistance as compared with thermal SiO<sub>2</sub> with a physical thickness of 3.0 nm shown in Fig. 1b is believed to be due to the high nitrogen content in the oxynitrides.

Table I. Important dielectric properties of oxynitrides formed by oxidizing a CVD deposited SiN.

| Oxidation time          | 30 min | 50 min | 70 min |

|-------------------------|--------|--------|--------|

| Refractive index        | 1.65   | 1.6    | 1.58   |

| Physical thickness (nm) | 3.6    | 4.4    | 4.7    |

| EOT (nm)                | 3.0    | 3.8    | 4.2    |

| k from C-V              | 4.72   | 4.46   | 4.41   |

| N% from XPS             | 23%    | 16%    | 14%    |

<sup>&</sup>lt;sup>b</sup>National Nano-Device Laboratory, Hsinchu, Taiwan

<sup>&</sup>lt;sup>c</sup>Department of Electric Engineering, Chung Hua University, Hsinchu, Taiwan

**Figure 1.** J-V characteristics of gate capacitors with (a) 3.6, 4.4, and 4.7 nm oxynitrides and (b) 3.0 nm SiO<sub>2</sub>. The devices are contaminated by 10 ppb or 10 ppm Cu.

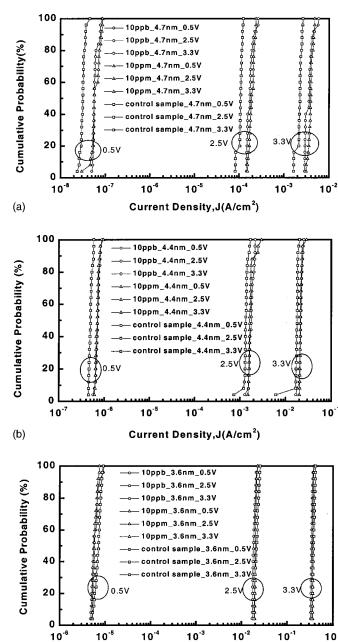

The cumulative leakage current distributions of the respective 3.6, 4.4, and 4.7 nm oxynitrides are shown in Fig. 2a, b, and c. For the thickest 4.7 nm oxynitride with the lowest nitrogen content, the Cu contamination increases the leakage current and the contamination effect saturates for a Cu concentration above 10 ppb. This saturation effect is believed to be due to the limited Cu solubility in the dielectric during the annealing at  $400^{\circ}$ C for 1 h. Although a similar Cu saturation contamination effect is also observed in the thinner 4.4 nm oxynitride, the leakage current increase is reduced. However, the current increase is negligible for the thinnest 3.6 nm oxynitride with the highest nitrogen content of 23%, which is in sharp contrast to the much larger leakage current for the 3.0 nm thermal SiO<sub>2</sub> shown in Fig. 1b. The reduced Cu contamination effect with increasing nitrogen content suggests that nitrogen strengthens the resistance against Cu contamination coming from the wafer front side.

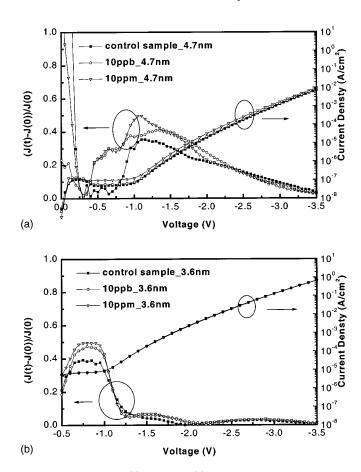

One advantage of incorporating nitrogen into the oxide is the improved reliability. We have also studied the stress-induced leakage current (SILC) effect in these oxynitrides. Figures 3a and b show the stress effect on [J(t)-J(0)]/J(0) for 14 and 23% nitrogen content, respectively. The stress for both samples is performed at a constant electric field of  $\sim 6.3\,$  kV/cm for 200 s, which gives a total charge injection of 7 and 70 C/cm² for the oxynitrides with 14 and 23% nitrogen content, respectively.

Under the same stress condition, the control oxynitrides in both cases show the smallest current increase and the Cu contamination increases the SILC effect. The saturated [J(t)-J(0)]/J(0) for increas-

**Figure 2.** The cumulative current distribution of (a) 4.7 nm, (b) 4.4 nm, and (c) 3.6 nm oxynitrides contaminated by 10 ppb and 10 ppm Cu.

Current Density, J (A/cm²)

ing Cu concentration is consistent with the saturated current increase in the J-V characteristics shown in the right axis, and attributed to the saturated Cu solubility at 400°C. However, a much-reduced SILC effect is observed for the oxynitrides with 23% nitrogen as compared with our previous work in  $\mathrm{SiO}_2.^7$  Because the increased SILC effect in the Cu contaminated oxynitride is due to the increased bulk and interface traps, the small SILC effect in the oxynitrides with 23% nitrogen demonstrates both the excellent Cu diffusion barrier property and the strong Si-N bonding in this sample. The improved SILC effect is important for the reliability of oxynitride gate dielectrics used for sub-0.1  $\mu m$  technologies.

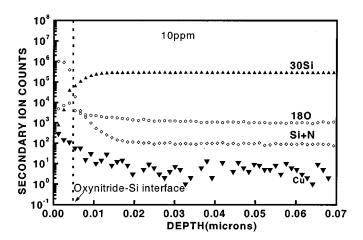

To study the much-improved Cu contamination resistance, we have used SIMS to measure the Cu concentration within the oxynitride. Figure 4 shows the SIMS profile of the 4.7 nm oxynitride after Cu contamination. In contrast to the Cu penetration through SiO<sub>2</sub>

(c)

**Figure 3.** SILC effect of (a) 4.7 nm and (b) 3.6 nm oxynitrides contaminated by 10 ppb and 10 ppm Cu.

**Figure 4.** SIMS profile for the 4.7 nm oxynitride contaminated by 10 ppm Cu from the front side of the wafer.

reported previously, <sup>7</sup> the Cu concentration is very small within the oxynitride and decreases rapidly inside the Si substrate. Therefore, the presence of nitrogen inside the Si oxide layer behaves as a diffusion barrier for Cu. This is also confirmed by the increased Cu contamination resistance for increasing nitrogen content. A similar strong resistance to boron penetration is also observed for oxynitrides used for sub-micrometer p-type MOS field effect transistors. <sup>14</sup>

### Conclusions

Gate dielectric degradation by Cu contamination is greatly reduced in oxynitrides as compared with thermal  $\mathrm{SiO}_2$ , and the Cu contamination resistance increases with increasing nitrogen content. Improved gate dielectric resistance to adverse Cu contamination is attributed to the strong diffusion barrier property of the oxynitride as observed by SIMS.

## Acknowledgments

Technical support from National Nano Device Lab is greatly appreciated. We would also like to thank Professor Cor Claeys for correcting our language. This work has been supported by NSC89-2215-E-317-006 and NSC90-2721-2317-200.

National Chiao Tung University assisted in meeting the publication costs of this paper.

#### References

- B. Vermeire, L. Lee, and H. G. Parks, IEEE Trans. Semicond. Manuf., 11, 232 (1998).

- P. Motte, J. Torres, J. Palleau, F. Tardif, and H. Bernard, Solid-State Electron., 43, 1015 (1999).

- 3. D. A. Ramappa and W. B. Henley, J. Electrochem. Soc., 146, 2258 (1999).

- A. Correia, D. Ballutaud, and J. L. Naurice, Jpn. J. Appl. Phys., Part 1, 33, 1217 (1994).

- T. Gravier, F. Braud, J. Torres, J. Palleau, A. Chantre, and J. Kirtsch, *Microelectron. Eng.*, 33, 211 (1997).

- Y. H. Lin, Y. H. Wu, A. Chin, and F. M. Pan, J. Electrochem. Soc., 147, 4305 (2000).

- Y. H. Lin, Y. C. Chen, K. T. Chan, F. M. Pan, I. J. Hsieh, and A. Chin, J. Electrochem. Soc., 148, F73 (2001).

- 8. C. T. Liu, Y. Ma, E. Becerro, S. Nakahara, D. J. Eaglesham, and S. J. Hillenius, *IEEE Electron Device Lett.*, **18**, 105 (1997).

- 9. X. Wang, M. Khare, and T. P. Ma, Symp. on VLSI Tech., p. 226 (June 1996).

- 10. T. Yamamoto, T. Ogura, and T. Mogami, Symp. on VLSI Tech., p. 45 (June 1997).

- H. F. Luan, S. J. Lee, C. H. Lee, S. C. Song, Y. L. Mao, Y. Senzaki, D. Roberts, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet., 1999, 141.

- A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, Symp. on VLSI Tech., p. 135 (1999).

- A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, Symp. on VLSI Tech., p. 16 (2000).

- H.-H. Tseng, D. L. O'Meara, P. J. Tobin, V. S. Wang, X. Guo, R. Hegde, I. Y. Yang, P. Gilbert, R. Cotton, and L. Hebert, Tech. Dig. Int. Electron Devices Meet., 1998, 703

- A. Chin, W. J. Chen, T. Chang, R. H. Kao, B. C. Lin, C. Tsai, and J. C.-M. Huang, IEEE Electron Device Lett., 18, 417 (1997).