# High Quality Interpoly Dielectrics Deposited on the Nitrided-Polysilicon for Nonvolatile Memory Devices

Wen Luh Yang, Tien Sheng Chao, Chun-Ming Cheng, Tung Ming Pan, and Tan Fu Lei, Member, IEEE

Abstract—High quality interpoly dielectrics have been fabricated by using  $NH_3$  and  $N_2O$  nitridation on polysilicon and deposition of tetra-ethyl-ortho-silicate (TEOS) oxide with  $N_2O$  annealing. The surface roughness of polysilicon is improved and the value of weak bonds is reduced due to nitrogen incorporation at the interface, which improves the integrity of interpoly dielectrics. The improvements include a higher barrier height, breakdown strength, and charge-to-breakdown, and a lower leakage current and charge trapping rate than counterparts. It is found that this method can simutaneously improve both charge-to-breakdown (up to  $20\ C/cm^2$ ) and electric breakdown field (up to  $17\ MV/cm$ ).

Index Terms—Barrier height, charge-to-breakdown, dielectric, electric breakdown field, interpoly, nonvolatile memories, polysilicon.

### I. INTRODUCTION

■ HERMALLY grown or deposited oxides on n<sup>+</sup> polysilicon have been used as the inter-dielectric for nonvolatile memories such as erasable-programmable read-only memory (EPROM), electrical-erasable programmable memory (EEPROM), and flash memories. In order to obtain good data retention and endurance characteristics, inter-dielectrics with a low conductivity (low leakage current) and a high electric breakdown field  $(E_{\rm bd})$  have been topics of research for a long time [1]-[3]. Because thermal oxidation of polysilicon leads to a rough polysilicon surface, thermally grown polyoxides exhibit a lower dielectric strength and a higher leakage current than those of oxide grown on single crystal silicon [4]–[12]. Recently, in contrast to thermal oxides, deposited dielectric layers have been investigated as a very promising alternative, since these dielectric layers are deposited on the polysilicon layer without silicon consumption. Consequently, the surface of polysilicon for a deposited polyoxide structure is found to be smoother than oxidizing counterpart. Low-temperature oxides (LTO) with an annealing in a rapid thermal processing (RTP) system or oxides deposited in a low-pressure chemical-vapor-deposition (LPCVD) system

Manuscript received October 30, 2000; revised January 23, 2001. This work was supported in part by Feng Chia University, Taichung, Taiwan, R.O.C., under Contract FCU-RD-88-01, and the National Science Council, R.O.C., under Contract NSC 89-2215-E-035-013. The review of this paper was arranged by Editor D. Verret.

W. L. Yang and C.-M. Cheng are with the Institute and Department of Electrical Engineering, Feng Chia University, Taichung, Taiwan, R.O.C.

T. S. Chao is with the National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C., and also with the Department of Engineering and System Science, National Tsing Hua University, Hsinchu, Taiwan, R.O.C.

T. M. Pan and T. F. Lei are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(01)05316-3.

have been used, but resultant electrical properties of LTO are not good enough for EEPROM applications even with additional postdeposition treatments [13]–[15]. In contrast to LTO, dielectrics deposited at a high temperature, like tetra-ethyl-ortho-silicate (TEOS), exhibit an improved performance [16]–[18]. In addition, high-temperature oxides (HTO) with the postdeposition treatment in a rapid thermal annealing (RTA) system are proposed to improve electrical properties, which can achieve effects of densification, reoxidation, and nitridation [19]–[21]. Furthermore, Klootwijk *et al.* [19] found that the oxide deposited with an additional N<sub>2</sub>O-annealing is an attractive alternative for conventional polyoxide, which results in an improved endurance of EEPROM devices by a factor of ten.

The underlying polysilicon layer also plays a dominant role in the dielectric strength. Lei et al. [22], [23] found that the strength of deposited dielectric depends on the roughness of polysilicon. Using chemical-mechanical polishing (CMP) on polysilicon, the dielectric integrity is significantly improved due to the smooth interface of the polysilicon, but charge-to-breakdown  $(Q_{bd})$  values are not improved simutaneously [23]. The method using both CMP and CVD oxide yields a high breakdown field  $(E_{\mathrm{bd}})$  and low electron-trapping rate. Recent reports show that the reliability of MOS and polyoxide capacitors can be improved by introducing proper amounts of nitrogen or fluorine [1], [24], [25]. It is also reported that the  $N_2O$ -grown and N2O-annealing polyoxides have better electrical performances than O<sub>2</sub>-grown polyoxides, which contributes to the nitrogen incorporation at the polyoxide/polysilicon interface [21], [26]–[29]. However, this treatment moderately improves the dielectric strength only.

In this paper, polyoxides are fabricated by utilizing a NH<sub>3</sub>-nitridation and RTA N<sub>2</sub>O-annealing on polysilicon to incorporate nitrogen at the surface of polysilicon. TEOS-oxides are then deposited on this nitrided polysilicon and followed with or without a densification in an N<sub>2</sub>O ambient. It is found that this method can simutaneously improve both  $Q_{\rm bd}$  and  $E_{\rm bd}$ .

# II. EXPERIMENTS

The n<sup>+</sup>-polysilicon/polyoxide/n<sup>+</sup>-polysilicon capacitors were fabricated on the p-type (100) silicon wafers. First, silicon wafers were thermally oxidized at 1000°C to form a 100-nm-thick isolation oxide. Then a 300-nm polysilicon layer (poly-1) was deposited in a LPCVD system using SiH<sub>4</sub> gas at 620 °C and subsequently doped with POCl<sub>3</sub> at 900 °C for 30 min, resulting in a sheet resistance of 30~40  $\Omega$ / $\square$ . After the *p*-glass was stripped off, the samples were then annealed

in NH<sub>3</sub> ambient at 800 °C for 2 h followed with or without a N<sub>2</sub>O-RTA annealing at 800 °C for 20 s. After that, a TEOS oxide with thickness to 100 Å was deposited in a LPCVD system at 650 °C, followed by a RTA at 900 °C for 30 s in the N<sub>2</sub> or N<sub>2</sub>O ambient for densification of oxides to a final 90 Å. Then a second polysilicon layer (poly-2) of 300-nm was deposited by a LPCVD system at 620 °C and doped to a sheet resistance of 30~40  $\Omega/\Box$  with the same POCl<sub>3</sub> process as poly-1. After definition of the poly-2, all samples were covered with a 100-nm oxide as a passivation layer. Contact holes were opened and aluminum was deposited and patterned to form the final capacitor structures. Finally, all devices were sintered at 400 °C for 30-min in a N<sub>2</sub> ambient.

Atomic force microscope (AFM) was used to characterize the surface morphology of polysilicon films with or without nitridation. Polyoxide thickness was determined by the high-frequency capacitance-voltage measurements with Keithley 590 and 595. The electrical properties, effective electron barrier height, electron trapping characteristics, and charge-to-breakdown were measured by a HP-4145B semiconductor parameter analyzer.

### III. RESULTS AND DISCUSSION

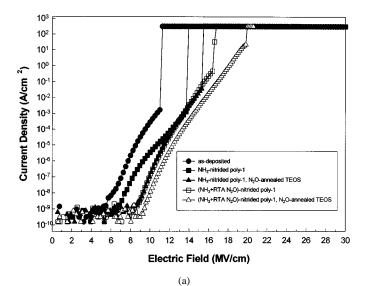

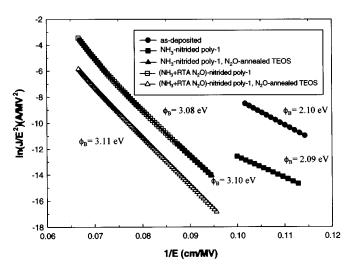

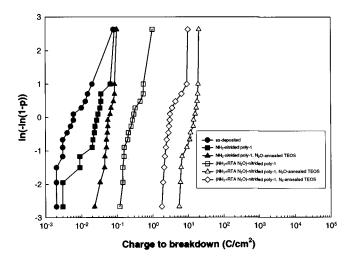

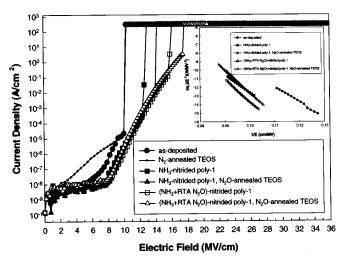

Impacts of nitridation on poly-1 and densification of TEOS in N<sub>2</sub>O are evaluated by the measurement of current-voltage (I-V) and breakdown field. In this measurement, the poly-2 is positively biased. (i.e., electrons are injected from the dielectric/poly-1 interface). Fig. 1(a) shows curves of current density versus electrical field, and Fig. 1(b) depicts the Weibull distributions of breakdown field for 75 capacitors corresponding to Fig. 1(a). The electrical field  $(E_{ox})$  is defined as  $V_g/T_{ox}$ , where  $V_g$  is the applied gate voltage, and  $T_{

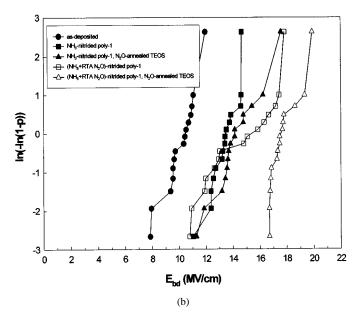

m ox}$  is the effective dielectric thickness as determined by the (capacitance-voltage (C-V)measurement. It is found that samples with nitridation of poly-1 have higher breakdown fields  $(E_{bd})$  than control samples (as deposited). They exhibit a lower leakage current and start conducting at higher voltages than control samples. It is also noted in Fig. 1 that samples with the RTA N<sub>2</sub>O-treatment on poly-1 exhibit an improved  $E_{\rm bd}$  and reduced leakage current. Since the NH<sub>3</sub>-nitridation will introduce hydrogen into the polysilicon, leading to unstable Si-H bonds. The NH<sub>3</sub>-nitridation of poly-1 only moderately improves the dielectric strength. With an additional RTA N<sub>2</sub>O-treatment, the unstable Si-H bonds will be annealed out, resulting in the better electrical characteristics with respect to the NH<sub>3</sub>-treated samples, as shown in Fig. 1. Secondary ion mass spectroscopy (SIMS) measurements of two samples fabricated with and without nitridation of poly-1 are shown in Fig. 2. The profiles of Si+N within the dielectric film are significantly increased by the nitridation treatment. In comparison with the control sample, a relatively high peak of Si+N profile within the dielectric film was observed for the (NH<sub>3</sub>+RTA N<sub>2</sub>O)-nitrided sample. It has been well recognized that the quality improvement of dielectrics by nitridation is thought to be the replacement of strained Si-O bonds or dangling bonds by Si-N bonds, leading to a relaxation of the interface stress [19], [25], [32]. In addition, annealing of dielectric in  $N_2O$  ambient has been used to achieve an oxidation

Fig. 1. (a) Typical J-E characteristics of interpoly dielectric layers with or without  $NH_3$  and RTA  $N_2O$  nitridation of poly-1 and  $N_2O$  densification of TEOS under positive applied voltages, i.e., electrons are being injected from the bottom electrode. (b) Typical Weibull distribution of the electrical breakdown field for the as-deposited, deposited on the nitrided-poly-1, and postdeposition annealing interdielectrics.

of the bulk nonstoichiometric  $SiO_2$ , a nitridation at the  $Si\text{-}SiO_2$  interface and a densification of the dielectric [19]. Hence, a very high  $E_{\rm bd}$  up to 17 MV/cm (average of 50%) was achieved for the sample by using the (NH<sub>3</sub>+RTA N<sub>2</sub>O)-nitridation of poly-1 and the N<sub>2</sub>O-densification of TEOS.

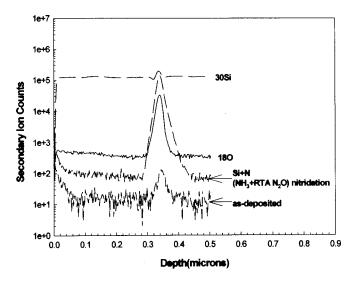

Plotting the J-E characteristics in the form of a Fowler-Nordheim (F-N) plot  $(J/E^2)$  versus 1/E) [30], [31], straight lines were obtained for all samples as shown in Fig. 3, indicating that F–N tunneling is the major conducting mechanism. The transport of F-N tunneling has the form  $J = C_1 E^2 \exp(-\phi_B/E)$ , where E is the field, and  $C_1$  and  $\phi_B$  are constants in terms of effective mass and barrier height. Indeed, the barrier height increased upon nitridation of poly-1, and N<sub>2</sub>O densification of TEOS. In all fabrication conditions, samples with (NH<sub>3</sub>+RTA N<sub>2</sub>O) nitridation of poly-1 and N<sub>2</sub>O-densification of TEOS has

Fig. 2. SIMS profile of two samples fabricated with (NH $_3+$ RTA N $_2$ O ) and without nitridation of poly-1.

Fig. 3. J-E characteristics in the form of a Fowler-Nordheim plot  $(J/E^2)$  versus 1/E for all dielectric layers. According to the F-N model, from the corresponding slopes of these lines the barrier heights foe the electron were obtained.

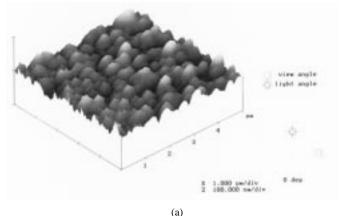

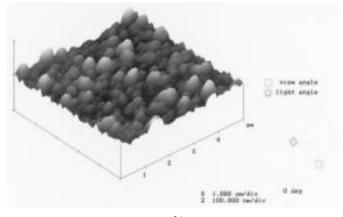

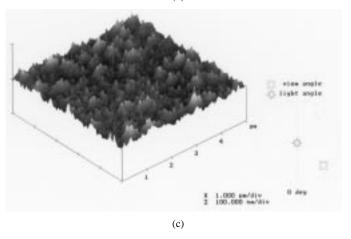

the highest effective electron barrier height. Fig. 4 displays the surface images of the poly-1 film with or without nitridation of poly-1 and  $N_2O$ -densification of TEOS by the atomic force microscope (AFM) measurement. The surface morphology of the poly-1 without/with the nitridation, and RTA  $N_2O$ -densification of TEOS are shown in Fig. 4(a)–(c). Root mean square (RMS) roughness for these three samples are 97.8, 85.6, and 71.8 Å, respectively. This implies NH<sub>3</sub> and RTA  $N_2O$ -nitridation results in a smooth surface. The dielectrics deposited on the (NH<sub>3</sub>+RTA  $N_2O$ )-nitrided poly-1 and  $N_2O$ - densification of TEOS exhibit the smoothest interface and hence result in the higher breakdown field.

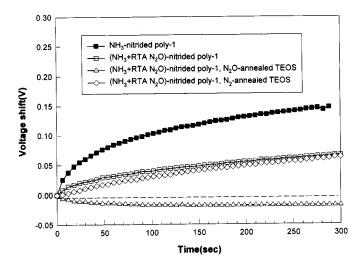

Fig. 5 shows shift of gate-voltage under the constant current stressing at 100  $\mu A/cm^2$  for all capacitors. It reveals that the additional RTA  $N_2O$ -nitridation of poly-1 has a smaller voltage shift than the  $NH_3$  nitrided-only sample. This implies that samples with the additional RTA  $N_2O$ -nitridation of poly-1

Fig. 4. Surface images of the polysilicon film by AFM measurement. (a) As-deposited, (b)  $NH_3$ -nitrided poly-1, and (c)  $NH_3$  and RTA  $N_2O$ -nitrided poly-1 with additional  $N_2O$  densification of TEOS.

yield a better immunity to the trapping of charges. Relatively, the rougher dielectric/poly-1 interface leads to a smaller conduction area and a higher local current density, subsequently causing a higher trapping rate of charge [23]. For the sample of (NH<sub>3</sub>+RTA N<sub>2</sub>O)-nitrided poly-1 and N<sub>2</sub>O-densification of TEOS, a small initial hole trapping is found, after that, no significant trapping is observed. This is due to the highest nitrogen incorporation among these samples.

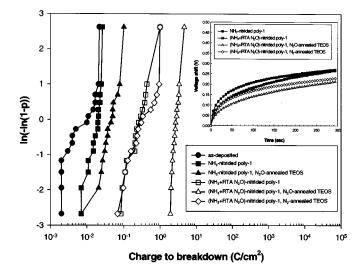

Regarding the reliability of polyoxide in nonvolatile memories, charge-to-breakdown  $(Q_{\rm bd})$  is also a critical parameter of interest. Dielectrics with large value of  $Q_{\rm bd}$  are needed to guaranty long read/write cycles. In the conventional polyoxide fab-

Fig. 5. Charge trapping characteristics, i.e., curves of gate voltage shifts versus stress time under positive top bias with a constant current stressing at  $100 \,\mu\text{A/cm}^2$ .

Fig. 6. Typical Weibull plots of the charge-to-breakdown for the as-deposited, nitrided-poly-1, and postdeposition annealed interdielectric layers under positive stress.

rication,  $Q_{\rm bd}$  values are very small (in the range of 0.01 °C/cm<sup>2</sup> to 0.1 °C/cm<sup>2</sup>) due to surface roughness and nonuniform polyoxide thickness. In Fig. 6, the Weibull distributions of charge-tobreakdown of 90-capacitor ( $100 \times 100 \,\mu\text{m}^2$ ) are shown for positive bias at top-gate. In the measurement, a constant current of 1 mA/cm<sup>2</sup> was used to stress the control and NH<sub>3</sub>-nitrided samples (solid symbols) and a constant current of 100 mA/cm<sup>2</sup> was stressed for the RTA N<sub>2</sub>O-nitrided samples (empty symbols). It is seen that the NH<sub>3</sub>-nitridation of poly-1 improves dielectric layer slightly, while the additional RTA N<sub>2</sub>O-nitridation of poly-1 increases  $Q_{\rm bd}$  significantly. It can be seen in Fig. 6 that the improvement of  $Q_{\rm bd}$  is about from 0.01 C/cm<sup>2</sup> to 0.1 C/cm<sup>2</sup> by using NH<sub>3</sub>-nitridation only. This may be due to the incorporation of hydrogen atoms at the dielectric/poly-1 interface. But if the poly-1 was nitrided with the additional RTA  $N_2O$ ,  $Q_{bd}$  increases significantly. In addition to the improvement on roughness of poly-1 as discussed in Fig. 4, the improved integrity is also due to the incorporation of nitrogen atoms, which reduce

Fig. 7. Typical J-E characteristics of interpoly dielectric layers with or without NH<sub>3</sub> and RTA N<sub>2</sub>O nitridation of poly-1 and N<sub>2</sub>O densification of TEOS under negative applied voltages, i.e., electrons are being injected from the top electrode. The inset is a Fowler-Nordheim plot  $(J/E^2$  versus 1/E) under negative top bias.

the weak Si-O (Si-H) bonds and relax the interface stress [19], [25]. Again, it is seen that a densification of TEOS by  $N_2O$  (or  $N_2$ ) annealing can further improve the dielectric integrity. It is found that  $Q_{\rm bd}$  up to  $20\,{\rm C/cm^2}$  can be obtained as the poly-1 was nitrided by the NH<sub>3</sub> and RTA  $N_2O$ -annealing and the TEOS annealed with  $N_2O$  postdeposition.

So far, only the electron injection from the bottom electrode has been considered. For the negative top electrode bias, i.e., electron injection from the top electrode, it had been shown that dielectrics with an additional N2O postannealing conducted a higher current than the as-deposited oxides [19], which is in contrast to positive top bias. This polarity preference was also observed for interdielectric layers directly grown from N<sub>2</sub>O [25]. Fig. 7 shows the J-E characteristics for the samples under negative bias at top-gate. Although the postdeposition annealing results in the polarity asymmetry, it is found that samples with nitridation of poly-1 still exhibit a better performance than the as-deposited samples. As compared to Fig. 1, the leakage currents of negative bias are one order of magnitude higher than those obtained from the positive bias. This is mainly ascribed to the nitrogen incorporated at the interdielectric/poly-1 interface. The inset in Fig. 7 depicts the F-N plots for electron injection from the top gate. Although the barrier height for the electron tunneling from poly-2 to the SiO<sub>2</sub> is not strongly related to the nitridation of poly-1 and the densification of TEOS, it is found that the barrier height is slightly improved with nitridation and N<sub>2</sub>O densification of TEOS as shown in Fig. 7. The Weibull distributions of  $Q_{\rm bd}$  under the negative bias are shown in Fig. 8. It is noted that the improvements of  $Q_{\rm bd}$  using nitridation of poly-1 and densification of TEOS are similar to the positive top gate bias. The inset of Fig. 8 shows the charge trapping characteristics under constant current stressing at 100 ( $\mu$ A/cm<sup>2</sup> for the negative bias at top-gate. The shift of gate-voltage increases with time. The additional RTA N<sub>2</sub>O-nitridation of poly-1 has a smaller voltage shift than the NH<sub>3</sub>-nitrided capacitor. This finding also implies that the additional RTA N2O-nitridation of

Fig. 8. Typical Weibull plots of the charge-to-breakdown for the as-deposited, nitrided-poly-1, and postdeposition annealed interdielectric layers under positive stress. The inset is the charge trapping characteristics under negative top bias.

poly-1 yields a better immunity to electron trapping, no matter what directions of electrons are injected. Furthermore, as TEOS was annealed in N<sub>2</sub>O ambient, the sample exhibits a better performance of charge trapping characteristic, which results in a higher charge-to-breakdown as seen in Fig. 8. However, as compared to Fig. 5, the electron trapping rates of capacitors under the negative bias at top gate are higher than those obtained from the positive bias counterpart. This is due to the different position of trapped charges in the N<sub>2</sub>O-annealed oxide under different gate bias, which is similar to the physical model proposed in [4].

# IV. CONCLUSION

In this study, an  $NH_3$  with RTA  $N_2O$  process to incorporate nitrogen at dielectric/polysilicon interface has demonstrated to improve integrity of polyoxides. Polyoxides deposited on this nitrided polysilicon with the additional  $N_2O$ -densification exhibit a lower leakage current, higher electric breakdown field, higher electron barrier height, lower electron trapping rate, and much higher charge-to-breakdown than the as-deposited polyoxides. SIMS results show the incorporation of nitrogen at the polyoxide/poly-1 interface, which improves electrical properties in return. Polyoxides formed by this method can achieve a high breakdown field up to 17 MV/cm and charge-to-breakdown more than 20 °C/cm². This process appears to be a very attractive alternative for conventional polyoxides.

### ACKNOWLEDGMENT

The authors would like to thank National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C., for technical support, and the Semiconductor Research Center and Instrument Center, National Chiao-Tung University, Hsinchu, for sample preparation and analyses.

### REFERENCES

- H. N. Chern, C. L. Lee, and T. F. Lei, "Improvement of polysilicon oxide characteristics by fluorine incorporation," *IEEE Electron Device Lett.*, vol. 5, pp. 181–182, May 1994.

- [2] C. Cobianu, O. Popa, and D. Dascalu, "On the electrical conduction in the inter-polysilicon dielectric layers," *IEEE Electron Device Lett.*, vol. 14, pp. 213–215, 1993.

- [3] T. Ono, T. Mori, T. Ajioka, and T. Takayashiki, "Studies of thin poly-Si oxides for E and E<sup>2</sup>PROM," in IEDM Tech. Dig., pp. 380–383, 1985.

- [4] C. S. Lai, T. F. Lei, and C. L. Lee, "The characteristics of polysilicon oxide grown in pure N<sub>2</sub>O," *IEEE Trans. Electron Devices*, vol. 43, pp. 326–331, Feb. 1996.

- [5] M. C. Jun, Y. S. Kim, and M. K. Han, "Polycrystalling silicon oxidation method improving surface roughness at the oxide/polycrystalline silicon interface," *Appl. Phys. Lett.*, vol. 66, no. 17, pp. 2206–2208, 1995.

- [6] L. Faraone, "Thermal SiO<sub>2</sub> films on n<sup>+</sup> polycrystalline silicon: Electrical conduction and breakdown," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 1785–1786, 1986.

- [7] L. Faraone, R. D. Vibronek, and J. T. Mcginn, "Characterization of thermally oxidized n<sup>+</sup> polycrystalline silicon," *IEEE Trans. Electron Devices*, vol. ED-32, pp. 577–584, 1985.

- [8] L. Faraone and G. Harbeke, "Surface roughness and electrical conduction of oxide/polysilicon interfaces," *J. Electrochem. Soc.*, vol. 133, no. 7, pp. 1410–1413, 1986.

- [9] R. B. Marcus, T. T. Tseng, and P. Lin, "Polysilicon/SiO<sub>2</sub> interface microtexture and dielectric breakdown," *J. Electrochem. Soc.*, vol. 129, no. 6, pp. 1282–1285, 1982.

- [10] R. M. Anderson and D. R. Kerr, "Evidence of surface asperity mechanism of conductivity in oxide grown on polycrystalline silicon," *J. Appl. Phys.*, vol. 48, no. 11, pp. 4843–4847, 1977.

- [11] J. C. Lee and C. Hu, "Polarity asymmetry of oxides grown on polycrystalline silicon," *IEEE Trans. Electron Devices*, vol. 35, pp. 1063–1067, July 1988.

- [12] S. L. Wu, C. Y. Chen, T. Y. Lin, C. L. Lee, T. F. Lei, and M. S. Liang, "Investigation of the polarity asymmetry on the electrical characteristics of thins polyoxides grown on N<sup>+</sup> polysilicon," *IEEE Trans. Electron Devices*, vol. 44, pp. 153–159, Jan. 1997.

- [13] C. Cobianu, "Silane oxidation in a low pressure chemical vapor deposition system in the temperature range 100–450°C," *Thin Solid Films*, vol. 226, pp. 1–2, 1993.

- [14] S. Ang and S. Wilson, "Rapid thermal annealed low pressure chemical vapor deposited SiO<sub>2</sub> as gate dielectric in Si MOSFET's," *J. Electrochem. Soc.*, vol. 134, no. 5, pp. 1254–1259, 1987.

- [15] V. R. Rao, I. Eisele, R. M. Patrikas, D. K. Sharma, and T. Grabolla, "High-field stressing of LPCVD gate oxides," *IEEE Electron Device Lett.*, vol. 18, pp. 84–86, Feb. 1997.

- [16] C. H. Kao, C. S. Lai, and C. L. Lee, "The TEOS CVD oxide deposited on phosphorus in situ doped polysilicon with rapid thermal annealing," *IEEE Trans. Electron Devices*, vol. 44, pp. 526–528, Mar. 1997.

- [17] C. Cobianu, O. Popa, and D. Dascalu, "Electrical properties of interlevel deposited oxides related to polysilicon preparation," *J. Phys.*, vol. 3, pp. 467–473, 1993.

- [18] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley, 1981.

- [19] J. H. Klootwijk, H. van Kranenburg, P. H. Woerlee, and H. Wallinga, "Deposited inter-polysilicon dielectrics for nonvolatile memories," *IEEE Trans. Electron Devices*, vol. 46, pp. 1435–1445, July 1999.

- [20] J. H. Klootwijk, H. van Kranenburg, M. H. H. Weusthof, P. H. Worelee, and H. Wallinga, "RTP annealings for high-quality LPCVD inter-polysilicon dielectric layers," *Microelectron Reliab.*, vol. 38, no. 2, pp. 277–280, 1998.

- [21] J. H. Klootwijk, M. H. H. Weusthof, H. van Kranenburg, P. H. Worelee, and H. Wallinga, "Improvements of deposited inter-polysilicon dielectric characteristics with RTP N<sub>2</sub>O anneal," *IEEE Electron Device Lett.*, vol. 17, pp. 358–359, 1996.

- [22] T. F. Lei, J. Y. Cheng, S. Y. Shiau, T. S. Chao, and C. S. Lai, "Improvement of polysilicon oxide by growing on polished polysilicon film," IEEE Electron Device Lett., vol. 18, pp. 270–271, 1997.

- [23] —, "Characterization of polysilicon oxides thermally grown and deposited on the polished polysilicon films," *IEEE Trans. Electron Devices*, vol. 45, pp. 912–917, Apr. 1998.

- [24] P. Chowdhury, A. I. Chou, K. Kumar, C. Lin, and J. C. Lee, "Improvement of ultrathin gate oxide and oxynitride integrity using fluorine implantation technique," *Appl. Phys. Lett.*, vol. 70, pp. 37–39, 1997.

- [25] W. L. Yang, M. S. Shieh, Y. M. Cheng, T. S. Chao, D.-G. Liu, and T. F. Lei, "Improvement of polysilicon oxide integrity using NF<sub>3</sub>-annealing," *Jpn. J. Appl. Phys.*, vol. 39, no. 6B, pp. L562–L563, 2000.

- [26] C. S. Lai, T. F. Lei, and C. L. Lee, "The electrical characteristics of polysilicon oxide grown in pure N<sub>2</sub>O," *IEEE Electron Device Lett.*, vol. 15, pp. 385–386, 1995.

- [27] T. Y. Huang, F. C. Jong, T. S. Chao, H. C. Lin, L. Y. Leu, K. Young, C. H. Lin, and Y. Chiu, "Improving radiation hardness of EEPROM/flash cell by N<sub>2</sub>O annealing," *IEEE Electron Device Lett.*, vol. 19, pp. 256–258, July 1998.

- [28] N. I. Lee, J. W. Lee, H. S. Kim, and C. H. Han, "High-performance EEPROM's using N- and P-channel polysilicon thin-film transistors with electron cyclotron resonance N<sub>2</sub>O-plasma oxide," *IEEE Electron Device Lett.*, vol. 20, pp. 15–17, Jan. 1999.

- [29] K. C. Huang, Y. K. Fang, D. N. Yaung, C. S. Wang, and M. S. Liang, "Improved programming performance of EEPROM/flash cell using post-poly-Si gate N<sub>2</sub>O annealing," *Electron. Lett.*, vol. 35, no. 13, pp. 1112–1114, 1999.

- [30] M. Lenzlinger and E. H. Snom, "Fowler-Nordheim tunneling into thermally grown SiO<sub>2</sub>," J. Appl. Phys., vol. 40, no. 1, pp. 278–283, 1969.

- [31] H. J. Mattausch, H. Baumgärtner, R. Allinger, M. Kerber, and H. Braun, "Electrical/thermal properties of nonplanar polyoxides and the consequent effects for EEPROM cell operation," *IEEE Trans. Electron Devices*, vol. 47, pp. 1251–1257, June 2000.

- [32] Y. Harada, K. Eriguchi, M. Niwa, T. Watanabe, and I. Ohdomari, "Impacts of strained SiO<sub>2</sub> on TDDB lifetime projection," in 2000 Symp. VLSI Technology, Honolulu, HI, 2000, pp. 216–217.

**Tien Sheng Chao** was born in Penghu, Taiwan, R.O.C., in 1963. He received the Ph.D. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1992.

He joined the National Nano Device Laboratories (NDL), as an Associate Researcher in July 1992, and became a Researcher in 1996. He was engaged in developing the thin dielectrics preparations, cleaning processes, and CMOS devices fabrication.

Chung-Ming Cheng was born in Pinton, Taiwan, R.O.C., on December 6, 1975. He received the B.S. and M.S. degrees in electrical engineering from Feng Chia University, Taichung, Taiwan, R.O.C., in 1997 and 1999, respectively. He is currently serving in the Chinese Army.

**Tung Ming Pan** was born in Taipei, Taiwan, 1970. He received the B.S. degree from the Department of Electronics Engineering, National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1997, and the Ph.D. degree from the Institute of Electronics, NCTU, in March 2001.

He is currently a Principal Engineer, LOGIC Development Department, Technology and Process Development Division (TD), United Microelectronics Corporation (UMC). His current research areas focus on the development novel one-step cleaning solutions

for pregate oxide cleaning technology and novel cleaning solutions for poly-Si film postchemical mechanical polishing. Applications of his research include the ultrathin oxynitride films and high-k gate dielectric materials for ultralarge scale integrated devices

Wen Luh Yang was born in Taichung, Taiwan, R.O.C., on May 5, 1961. He received the B.S. degree from the Department of Electrophysics, National-Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1983, and the M.S. and Ph.D. degrees in electronics from NCTU, in 1987 and 1992, respectively.

In 1993, he joined the Faculty of Feng Chia University, Taichung, where he is now an Associate Professor with the Institute and Department of Electrical Engineering. He is interested in fabrication process

in deep submicronmeter VLSIs, thin-gate dielectrics, ultra shallow junctions, metal silicides, and multilevel interconnections. He is currently developing the CMP technologies, interpoly dielectrics, and Cu metallization processing. Since 1999, he has been Editor of the *Journal of Vacuum Science Technology*, Vacuum Science Technology Society, Taiwan, and a Patent Examiner of the Intellectual Property Office, Ministry of Economic Affairs, Taiwan, R.O.C.

**Tan Fu Lei** (M'98) was born in Keelung, Taiwan, R.O.C., in 1944. He received the B. S. degree in electrical engineering from National Cheng Hung University, Tainan, Taiwan, in 1967, and the M. S. and Ph. D degrees in electronics engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1970 and 1979, respectively.

From 1970 to 1972, he was with the Fine Products Microelectronics Corporation, Taiwan, as an engineer working on the fabrication of small-signal transistors. From 1980 to 1982, he was the Plant

Manager of Photronic Corporation, Taiwan. In 1983, he joined the Faculty at NCTU as an Associate Professor in the Department of Electronics Engineering and the Institute of Electronics. From 1984 to 1986, he was the Director of the Semiconductor Researcher Center. From 1991 to 1998, he was also the Deputy Director of the National Nano Device Laboratory. Presently, he is a Professor of the Department of Electronic Engineering and the Institute of Electronics. His research interests are in semiconductor devices and VLSI.