# Extraction of Eleven Model Parameters for Consistent Reproduction of Lateral Bipolar Snapback High-Current I-V Characteristics in NMOS Devices

Ming-Jer Chen, Senior Member, IEEE, Hun-Shung Lee, Member, IEEE, and Shuenn-Tarng Chen

Abstract—A series of literature models originally devoted to the second breakdown trigger current  $I_{t2}$  in a grounded-gate nMOS transistor can further find promising potential in handling high-current I-V due to lateral bipolar snapback. This is achieved primarily by building significant linkage between bipolar current-gain  $\beta$ -related parameters: 1) the collector-to-base junction voltage dependencies  $A_1$  and  $A_2$  of the medium-level injection  $\beta$  roll-off factor; 2) the high-level  $\beta$  roll-off factor  $A_3$ ; and 3) the collector-to-base junction voltage dependencies  $A_4$  and  $A_5$  of the collector corner current at the onset of high-level  $\beta$ roll-off. The new parameters  $A_1$  to  $A_5$  enable a consistent I-Vsolution along with other existing six model parameters such as the substrate resistance  $R_{

m sub}$  and its conductivity modulation factor  $A_r$ , the impact ionization coefficients  $K_1$  and  $K_2$ , and the emitter series resistance  $R_e$  and collector series resistance  $R_c$ . Parameter extraction except Rc is thoroughly performed using only the parametric analyzer, and opposed to the traditional procedure, impact ionization coefficients and current gains are all assessed without entering the snapback regime. Remarkably, not only excellent agreements are gotten, but also bipolar snapback I-Vmeasured under the current pulsing condition can be separated into two distinct parts: medium- and high-level injection region. This is quite effective under  $R_e = R_c$ . Series resistance, although having very low value, is not to be absent under the high-level injection conditions. Experimental evidences from test structures with different epitaxial layer thicknesses strongly confirm the validity of the assumptions such as  $R_e = R_c$ . In light of the epitaxial layer thickness dependencies of the model parameters, the epitaxial layer thickness effect is addressed as well.

Index Terms—Bipolar, electrostatic discharge (ESD), MOS, second breakdown, snapback.

## I. INTRODUCTION

THE grounded-gate nMOS transistor is one of the widely utilized input/output (I/O) devices [1] since it can be snapped back into the lateral bipolar high-current conduction state in an electrostatic discharge (ESD) event. In case of ESD Human-Body-Mode, the current discharging waveform

Manuscript received August 29, 2000; revised November 20, 2000. This work was supported by the National Science Council under Contract 89-2215-009-049. The review of this paper was arranged by Editor J. N. Hollenhorst.

M.-J. Chen is with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

H.-S. Lee was with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. He is now with CSIST, Lung-Tan 325, Taiwan, R.O.C.

S.-T. Chen was with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. He is now with Avant!, Taipei 100, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(01)03250-6.

can adequately be approximated by a pulse with width in the order of several hundreds of nanoseconds [2]; and under such current pulsing or transmission-line-pulsing (TLP) condition, the measured lateral bipolar snapback high-current I-V characteristics can provide information about ESD transient energy the device is carrying away [2]. This is valid until the second breakdown trigger current  $I_{t2}$  is encountered. Thus, characterization and modeling of high-current I-V due to lateral bipolar snapback is essential. There exist a series of models in the literature originally devoted to  $I_{t2}$ :

- 1) a substrate current model [3], [4], with the substrate resistance  $R_{\rm sub}$  and the conductivity modulation factor  $A_r$  as parameters;

- an avalanche generation model [3]–[5] with the impact ionization coefficients K<sub>1</sub> and K<sub>2</sub> as parameters for the multiplication factor M;

- 3) a lateral bipolar high-level injection current-gain  $\beta$  model [4], [6], with the roll-off factor  $A_o$  as the primary parameter.  $R_{\rm sub}$ , M, and  $\beta$ , all extracted from a single nMOS transistor in terms of dc drain current versus drain voltage curve containing a snapback regime [3], [7], were shown to be well related to  $I_{t2}$  [4], [7].

This indicates the potential of a wafer-level process monitor [4], [7] in tracing ESD robustness capability to process tuning or device redesign, greatly reducing the load of the destructive characterization equipment like current pulse generator, high-voltage generator, switcher, and oscilloscope. Despite these striking achievements, the models themselves indeed fail to stand up in producing I-V of interest due to the lacking in the linkage between parameters.

The goal of the work is to highlight another promising potential of the aforementioned models in handling lateral bipolar snapback high-current I-V. This is achieved by recovering the linkage between parameters. First of all,  $A_o$  is replaced by five ones: the collector-to-base junction voltage dependencies  $A_1$  and  $A_2$  of the bipolar medium-level injection  $\beta$  roll-off factor, the high-level  $\beta$  roll-off factor  $A_3$ , the collector-to-base junction voltage dependencies  $A_4$  and  $A_5$  of the collector corner current at the onset of high-level  $\beta$  roll-off. The new parameters  $A_1$  to  $A_5$  enable a consistent solution of I-V characteristic along with other existing six model parameters such as  $R_{\rm sub}$ ,  $A_r$ ,  $K_1$ ,  $K_2$ , and the series resistance [8]–[11]  $R_e$  in emitter and  $R_c$  in collector. Parameter extraction except  $R_c$  is thoroughly performed using only the parametric analyzer, and opposed to the traditional procedure [3], [7], impact ionization coefficients

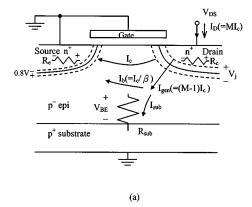

Fig. 1. (a) Schematic cross section of a grounded-gate nMOS transistor. The distinct current components and paths after snapback takes place are denoted. The potential drops are labeled as well. (b) Experimental I-V characteristic curve illustrating the avalanche voltage  $V_{t1}$ , the snapback voltage  $V_{sp}$ , the second breakdown triggering voltage  $V_{t2}$  and current  $I_{t2}$ , and the second breakdown regime.

and current gains are all assessed without entering the snapback regime. Moreover, traditionally applying an external forward bias was reported to be weak in measuring real  $\beta$  [5], [12]; however, in this paper, we alternatively characterize  $\beta$  as a function of the drain-to-substrate junction voltage and reasonably extract the impact ionization induced generation current in a consistent manner. As a result, remarkably excellent agreements are gotten while comparing lateral bipolar snapback I-V measured under the current pulsing condition. Series resistance, although having very low value, is not to be absent under the high-level injection conditions. Experimental evidences from test structures with different epitaxial layer thicknesses furnish strong supports to the assumptions behind the models. The epitaxial layer thickness effect is also addressed in light of the epitaxial layer thickness dependencies of the model parameters.

### II. MODEL CITATION

Fig. 1 schematically shows the cross-sectional view of a grounded-gate nMOS device. Also attached is the experimental I-V characteristic curve including second breakdown regime, as explained in later sections. For device initially in off-state, increasing drain voltage to approach the avalanche voltage  $V_{t1}$

can produce a significant substrate current  $I_{\mathrm{sub}}$  via avalanche generation, which in turn develops a potential drop across the substrate resistance  $R_{\mathrm{sub}}$ . As the substrate potential drop forward biasing the substrate-to-source junction rises to a certain criterion  $V_{BE}$ , the parasitic lateral bipolar turns on, and the drain voltage has to be lowered to around the snapback voltage  $V_{sp}$  such as to sustain the subsequent drain current. Then, the device enters into the so-called self-biased mode, that is, as depicted in Fig. 1(a), the bipolar electron current  $I_c$  collected at the edge of the substrate-to-drain junction is amplified by a multiplication factor M to constitute the drain electron current  $I_D(=MI_c)$ , and the substrate hole current  $I_{\mathrm{sub}}(=(M-1)I_c-I_c/\beta)$  and the base hole current  $I_b(=I_c/\beta)$  both are provided by the generated hole current  $I_{\mathrm{gen}}(=(M-1)I_c)$ . Such relation mathematically leads to [4]

$$M = \frac{(\beta + 1)}{\beta \left(1 - \frac{I_{\text{sub}}}{I_D}\right)}.$$

(1)

There exists a compact model relating the drain-to-substrate junction voltage  $V_i$  to M [4]

$$V_j = \frac{K_2}{\ln\left(\frac{K_1}{1 - \frac{1}{M}}\right)}.$$

(2)

$I_{\mathrm{sub}}$  can readily be calculated using a substrate current model [3], [4], but with parameter redefined for including  $R_e$ :  $I_{\mathrm{sub}} = A_r I_D + V_{BE}/R_{\mathrm{sub}}$  where  $V_{BE} = 0.8V + (1+1/\beta)R_e I_D/M$ . As a result,  $I_{\mathrm{sub}} = (A_r + (\beta + 1)R_e/\beta MR_{\mathrm{sub}})I_D + 0.8V/R_{\mathrm{sub}}$ . The parasitic lateral bipolar current-gain  $\beta$  roll-off was usually approximated by a simple form  $\beta = A_o/I_C$  [4], [6]; as demonstrated later, however, such formulation is far away from the reality due to lacking of the linkage to junction voltage, making a consistent I-V solution improbable. To further cover the medium- and high-level regimes, a set of five parameters instead of single  $A_o$  is subsequently introduced. As a result of parameter expansion,  $V_j$  can be consistently solved from (1) and (2). Thus, summing all known or calculated potential drops from drain to substrate terminal for given  $I_D$  creates a model for the lateral bipolar snapback I-V under investigation

$$V_{DS} = I_D R_c + V_i + V_{BE}. (3)$$

### III. CHARACTERIZATIONS AND PARAMETER EXTRACTION

The nMOS test transistors were formed on a p-type epitaxial layer on p+ substrate. The gate oxide was grown to a thickness of 70 Å. Phosphorous (6.0  $\times$   $10^{12}$  cm $^{-2}$ , 30 KeV) and then Arsenic (4.0  $\times$   $10^{13}$  cm $^{-2}$ , 45 KeV) were implanted to form the low-doped source/drain, followed by Arsenic implant (4.4  $\times$   $10^{15}$  cm $^{-2}$ , 40 KeV) for the highly doped n+ source/drain. Three different epitaxial layer thicknesses of 2, 4, and 5  $\mu \rm m$  were presented. The corresponding thickness values were measured after the processing by a spreading resistance probe. The gate width to length ratio selected in this work was 20  $\mu \rm m/0.3~\mu m$  for the threefold goals:

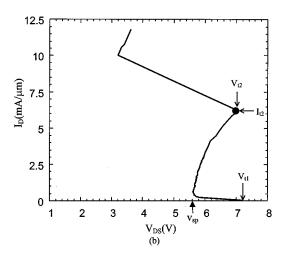

Fig. 2. Scatter plot between measured substrate current and drain current. A straight line fitting data points for  $I_D > 4\,$  mA is drawn. The inset depicts the test configuration.

- wafer-level parameter extraction using a parametric analyzer;

- 2) wafer-level measurement of bipolar snapback I-V curve down to off-state using the same parametric analyzer with the equipment limit of 100 mA;

- 3) wafer-level measurement of bipolar snapback high-current I-V curve and extension up to second breakdown regime using a current pulse generator with the equipment limit of 1 A. Unless stated otherwise, the  $4-\mu$ m thick epitaxial layer structure is first concentrated.

The parametric analyzer Keithley 236 was used to perform characterizations and parameter extraction on the same sample. First of all, the biasing condition for  $R_{\rm sub}$  and  $A_r$  was tying source, gate, and substrate to ground. The drain current and substrate current were measured against drain voltage, and their correlation is plotted in Fig. 2. It can be seen that almost all data points for 4 mA  $< I_D <$  30 mA fall exactly on a straight line. The slope and intercept of that line represent  $A_r$  and 0.8 V/ $R_{\rm sub}$ , respectively. Note that within the current range illustrated in Fig. 2,  $A_r \gg (\beta+1)R_e/\beta MR_{\rm sub}$ , as evaluated using the quantities later. To extract  $K_1$  and  $K_2$ , the test device was biased in above threshold and the measured drain current versus drain voltage for different gate voltages is depicted in Fig. 3(a). The multiplication factor M in the avalanche region can be characterized by [5], [11]

$$M = \frac{1}{1 - K_1 \exp\left(\frac{-K_2}{V_{DS} - V_{DS,SAT}}\right)} \tag{4}$$

where  $V_{DS,SAT}$  is the drain saturation voltage at the pinchoff point. The  $V_{DS,SAT}$  value can be readily gotten by transforming the I-V curves (0 <  $V_{DS}$  < 1.5 V in Fig. 3(a), for instance) free of avalanche generation to another function G according to [13]–[15]

$$G = g_{DS} \frac{\partial}{\partial V_{DS}} \left( \frac{1}{g_{DS}} \right) \tag{5}$$

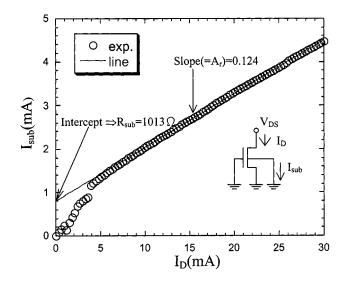

Fig. 3. (a) Measured nMOS transistor output I-V characteristics for gate voltages over threshold voltage. (b) Transformed G versus  $V_{DS}$  for different  $V_{GS}$ . The inset depicts the extracted  $V_{DS,SAT}$  versus gate voltage. (c) Extracted (1-1/M) versus  $1/(V_{DS}-V_{DS,SAT})$  along with a straight line for determination of  $K_1$  and  $K_2$ .

where  $g_{DS} = \partial I_{DS}/\partial V_{DS}$  is the conductance of the device. The resulting G versus  $V_{DS}$  is depicted in Fig. 3(b), where a peak G takes place at  $V_{DS,SAT}$ . The extracted  $V_{DS,SAT}$  versus  $V_{GS}$  is plotted in the inset of Fig. 3(b), suggesting a linear relationship between the two. Then the I-V part in the avalanche

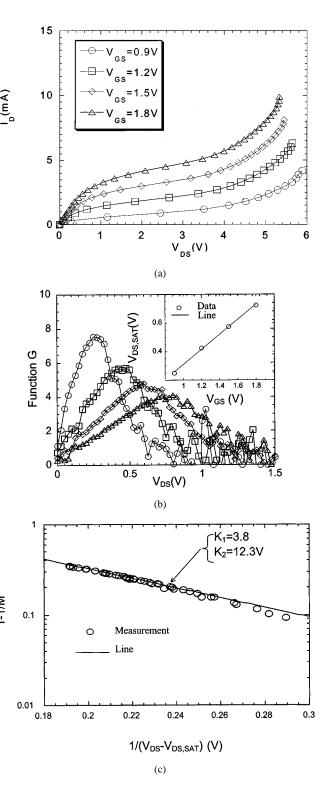

Fig. 4. Set-up of extracting the emitter series resistance as well as the measurement results.

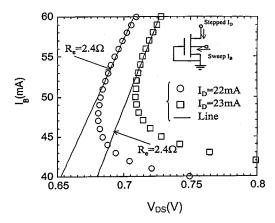

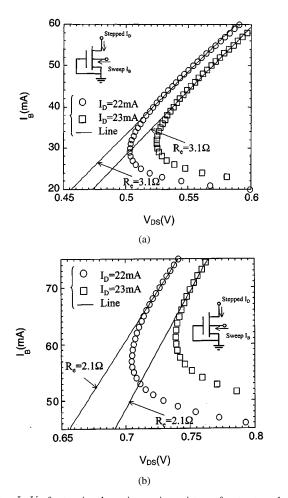

regimes (not entering the snapback) in Fig. 3(a) were transformed to (1 - 1/M) in log scale versus  $1/(V_{DS} - V_{DS,SAT})$ in Fig. 3(c), from which a straight line is drawn along with extracted  $K_1$  and  $K_2$ . The technique of extracting the emitter resistance  $R_e$  is well defined in a bipolar transistor [6]: sweeping  $I_B$  for fixed  $I_D$  while monitoring  $V_{DS}$ , as shown in the inset of Fig. 4. The devices burn out if  $I_B$  exceeds about 70 mA. The measurement results for  $I_B < 60$  mA are shown in Fig. 4, where the inverse of the slope near the knee of  $I_B$  versus  $V_D$  is around 2.4  $\Omega$ . In spite of distinct bias modes in two junctions, to facilitate the analysis we made first order approximation of  $R_c = R_e$  based on the symmetry of the n<sup>+</sup> diffusion regions. This also implies that the series resistance involved is located in certain part of diffusion regions where injection is insignificant. Strong experimental evidences supporting this assumption is presented later.

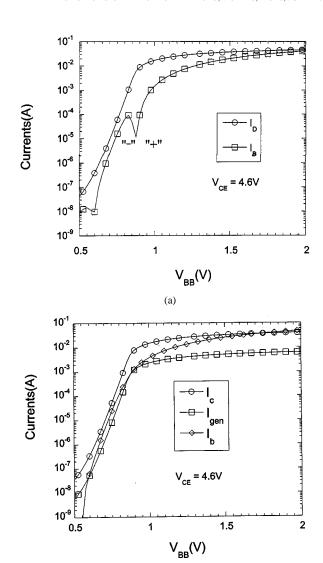

The biasing condition for bipolar current-gains is that, with grounded source and gate, an external forward bias  $V_{BB}$  was applied to the substrate while a reverse bias of  $\mathcal{V}_{CE}$  was connected to the drain. Fig. 5(a) shows the measured drain terminal current  $I_D$  and bulk terminal current  $I_B$  versus  $V_{BB}$  at  $V_{CE} = 4.6$  V. It can be seen that a bulk current reversal phenomenon like that in [16] (e.g., the avalanche generation bulk component exceeds the traditional base current component for recombination in the base and injection into the emitter) occurs for  $V_{BB} < 0.9 \text{ V}$ . Both  $I_D$  and  $I_B$  can be transformed to  $I_c$  and  $I_b$ , respectively, according to the formula:  $I_D = I_c M$ ;  $I_{gen} = (M-1)I_c$ ; and  $|I_B| = I_{\text{gen}} - I_b$  for  $V_{BB} < 0.9 \text{ V}$  and  $I_B = I_b - I_{\text{gen}}$ for  $V_{BB}\,>\,0.9$  V. The resulting current components are depicted in Fig. 5(b) for clarification. Fig. 6 displays the resultant current gains versus collector current with  $V_{CE}$  as a parameter. First of all, the traditional  $\beta_1 = A_o/I_c$  is found to dominate the medium-level current regime as fitted in Fig. 6(a). The extracted  $A_o$  versus  $V_i$  is given in Fig. 7(a), where a fitting line of  $A_o = A_1(V_j - A_2)$  is drawn. One plausible explanation for such  $V_i$  dependencies is that, due to Early effect, an increase in  $V_j$  narrows the base width and thus increases current gain. Note that  $V_j$  was transferred from  $V_{CE}$  using the potential drop relation  $V_{CE} = V_j + 0.8V + (I_E R_e + I_D R_c)$ , and again to simplify the analysis, the average value of  $I_E R_e + I_D R_c$  was roughly 0.2 V for the current range of interest in Fig. 5, namely,

Fig. 5. (a) Measured drain terminal current and bulk terminal current and (b) the extracted collector current, base current, and generation current, all versus external forward bias  $V_{BB}$  at  $V_{CE}=4.6~{\rm V}$ .

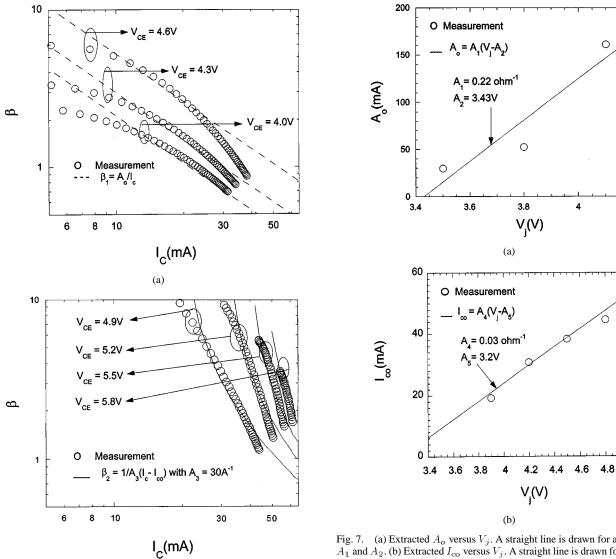

10 to 70 mA. Returning back to Fig. 6(a), one can see that 1) as  $V_{CE}$  increases, the deviation of  $\beta_1$  is more pronounced in the high-level injection regime and 2) for  $V_{CE} > 4.9$  V, current gain seems to shift toward the direction of increasing collector current as characterized by an increase in the collector corner current  $I_{co}$  at the onset of  $\beta$  roll-off [10]. Thus, we adopt the other form as cited in [10] for the high-level current gain  $\beta_2$

$$\beta_2 = 1/A_3(I_c - I_{co}).$$

(6)

The fitting lines of (6) are drawn in Fig. 6(b), yielding  $A_3=30$   ${\rm A}^{-1}$ ; and the extracted  $I_{\rm co}$  is plotted in Fig. 7(b) versus  $V_j$ . Similarly,  $I_{\rm co}$  can be empirically related to  $V_j$  through  $I_{\rm co}=A_4(V_j-A_5)$

# IV. CURRENT PULSING I-V MEASUREMENT AND REPRODUCTION

Equipment HP8114A with the upper limit of 1 A generated out a 400-ns wide current pulse to force entering the drain of

4.2

Fig. 6. Extracted current gains versus collector current for (a)  $V_{CE}$  of 4.0 to 4.6 V and (b)  $V_{CE}$  of 4.9 to 5.8 V. The fitting lines are shown for extraction of  $A_o$ ,  $A_3$ , and  $I_{co}$ .

(b)

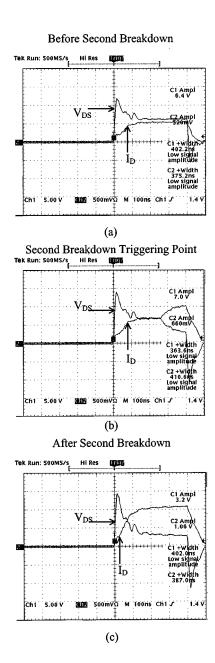

the sample with gate grounded. A digital oscilloscope Tek744A recorded the transient waveforms of the drain current (via a CT-1 current probe) and drain voltage. Fig. 8(a)–(c) displays the measured waveforms for three increasing pulse heights corresponding, respectively, to the self-biased point, the second breakdown trigger point, and the second breakdown quasi-stable point. It can be observed that initially the device experiences the dynamic process starting from off-state through the avalanche point to the negative resistance regime, and eventually it enters the steady state in the remaining pulse width. In particular, in Fig. 8(b), a sudden drop in  $V_{DS}$  accompanying a rise in  $I_D$  during the subsequent decay is noticeable, evidencing the second breakdown trigger point. The corresponding steady-state I-V is plotted in Fig. 1(b). It is worth noticing that between the second breakdown trigger point and the snapback point, there exists a critical point separating the I-V into two distinct parts. The product of the second breakdown trigger voltage  $V_{t2}$  and  $I_{t2}$ herein is 45 mW/um, quite close to those reported with the same

Fig. 7. (a) Extracted  $A_o$  versus  $V_j$ . A straight line is drawn for assessment of  $A_1$  and  $A_2$ . (b) Extracted  $I_{\infty}$  versus  $V_j$ . A straight line is drawn for assessment of  $A_4$  and  $A_5$ .

pulse width [4]. Additional equipment Keithley 236 with a maximum allowable current limit of 100 mA was also used to characterize the other samples (different locations on the same wafer) and the resulting I-V down to off-state is together plotted in Fig. 1(b) for comparison. It can be seen that both have consistent overlap. This rather confirms the validity of the present current pulsing measurement technique. It is also noteworthy that since Keithley 236 has a much longer pulse width during the measurement, a catastrophic failure is easily produced in samples for currents exceeding only around 70 mA.

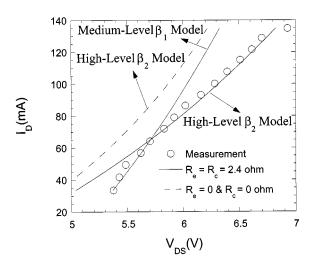

Substituting extracted parameters into the models, two I-Vcurves were created for medium-level  $\beta_1$  and high-level  $\beta_2$ , as shown in Fig. 9 along with experimental I-V. Strikingly, excellent reproductions are obtained. This is rigorously achieved without adjusting any parameters. Obviously, the mentioned separation of experimental I-V in Fig. 1(b) into two distinct parts can be adequately attributed to the two different operating regions, namely, the medium-level injection region and the high-level injection region. This suggests that an adequate tradeoff can be made between medium- and high-level current

Fig. 8. Measured waveforms of drain current and drain voltage corresponding to current pulse heights of (a) 100 mA; (b) 130 mA; and (c) 210 mA.

regimes:  $1/\beta = 1/\beta_1 + 1/\beta_2$ . Also plotted in Fig. 9 is an extra calculation in high-level injection for  $R_e = 0$  and  $R_c = 0$ . Surprisingly, ignoring series resistance indeed produces a serious deviation of the real I-V curve. Thus, series resistance, although very low value as that in our study, is not to be absent under the high-level injection conditions, confirming the role of  $R_e$  and/or  $R_c$  reported elsewhere [8]–[11].

In the presence of excellent reproduction demonstrated above, however, some issues associated with the eleven-parameters-based models must be addressed. First, the reproduction is apparently effective under  $R_e=R_c$ . Second, the gate width is utilized for calculation, indicating the current distribution uniformity along the gate width or peripheral direction. The final problem rises in nature: the parameters extracted and measured in dc parametric analyzer could be suitable for

Fig. 9. Experimental I-V characteristics and calculated results for two current-gain injection models.  $R_e=R_c=2.4~\Omega.$  Also plotted is the high-level injection calculation for  $R_e=0$  and  $R_c=0$ .

reproducing  $I\!-\!V$  measured via current pulsing technique. Prior to answering these problems, it must be recognized that what we are faced with is a highly challenging area where very complex, sophisticated phenomena occur in an ESD event and each may play significant roles in terms of electrical-thermal coupling, three-dimensional distributing current and potential, and current filament formation. Even self-heating may considerably participate during extracting dc parameters. With this in mind, if any noticeable deviations would occur, one could trace back deviations to certain assumption and/or could evaluate the degree of deviations produced and relate them to that assumption. Strictly speaking, only more experimental evidences can be useful in this matter. This is presented below in terms of the epitaxial layer thickness effect.

## V. EPITAXIAL LAYER THICKNESS EFFECT

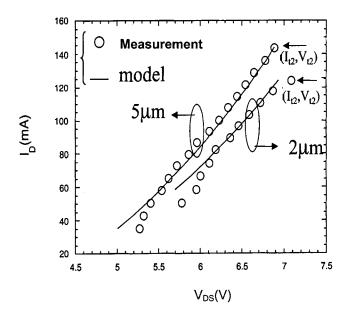

Again, following the same procedure of device characterization and parameter extraction for the other structures having epitaxial layer thicknesses of 2 and 5  $\mu$ m, comparable results do turn out, as depicted in Fig. 10. This is achieved again without any parameter adjustment. Thus, it is concluded that the assumptions behind the models are quite adequate and reasonable. Note that some serious deviations appear in the vicinity of the second breakdown trigger point, which may be attributed to current filament formation or others. Comparing both Figs. 9 and 10, one can see that I-V curve shifts toward the increasing drain voltage with decreasing epitaxial layer thickness. Now we explain such effect in terms of the epitaxial-layer-thickness dependent model parameters. Fig. 11 depicts the measured I-V of extracting  $R_e$  for epitaxial layer thicknesses of 2 and 5  $\mu$ m. Again, comparing Figs. 4 and 11, it is argued that  $R_e$  increases with decreasing epitaxial layer thickness. This tendency is arisen from out-diffusion extension from underlying p<sup>+</sup> heavily doped substrate as supported by measured doping profile, which in turn narrows the quasi-neutral diffusion region. Under the same influence, due to structure symmetry another series resistance should show the same

Fig. 10. Experimental I-V characteristics and calculated results for high-level injection current gain model.  $R_e=R_c=3.1~\Omega$  for epitaxial layer thickness of 2  $\mu$ m and  $R_e=R_c=2.1~\Omega$  for 5  $\mu$ m.

Fig. 11. I-V of extracting the emitter series resistance for structures having epitaxial layer thickness of (a)  $2\mu$ m and (b)  $5~\mu$ m.

behavior. This naturally serve as a strong evidence of  $R_e = R_c$  as employed in our work.

TABLE I

THE EXTRACTED PARAMETER VALUES FOR THREE DIFFERENT EPITAXIAL

LAYER THICKNESSES. CURRENT-GAIN PARAMETERS ONLY IN THE

HIGH-LEVEL INJECTION REGION ARE LISTED

| Epitaxial Layer<br>Thickness | R <sub>sub</sub> | A <sub>r</sub> | Kı  | K <sub>2</sub> | A <sub>3</sub>     | A <sub>4</sub>      | <b>A</b> <sub>5</sub> | Re    |

|------------------------------|------------------|----------------|-----|----------------|--------------------|---------------------|-----------------------|-------|

| 2 um                         | 987 Ω            | 0.158          | 3.8 | 12.3           | 18 A <sup>-1</sup> | $0.021~\Omega^{-1}$ | 2.70 V                | 3.1 Ω |

| 4 um                         | 1013 Ω           | 0.124          | 3.8 | 12.3           | 30 A <sup>-1</sup> | $0.030~\Omega^{-1}$ | 3.20 V                | 2.4 Ω |

| 5 um                         | 1065 Ω           | 0.103          | 3.8 | 12.3           | 40 A <sup>-1</sup> | $0.031~\Omega^{-1}$ | 3.22 V                | 2.1 Ω |

Table I lists in part the extracted parameter values for different epitaxial layer thicknesses. This table reveals some dependencies of relevance. First, impact ionization coefficients are intact, indicating that the mentioned out-diffusion does not extend significantly to the surface beneath the gate, or its range is quite limited to around the bottom n<sup>+</sup> diffusion to p-type epitaxial layer junction. Second, the substrate resistance decreases with decreasing epitaxial layer thickness, as expected. According to the models, either increasing series resistance or decreasing substrate resistance can shift the I-V toward positive drain voltage. This is because the former can increase the potential drop across the series resistance, while a bipolar current increase is accompanied with the latter to maintain the same substrate potential drop, which in turn increases the potential drop from drain to source. Relative to other parameters, an analysis simply judges out the series resistance and substrate resistance both as primary contributing factors to the above epitaxial layer thickness effect.

# VI. CONCLUSION

We have demonstrated in detail one promising potential of the well-recognized literature models in dealing with the lateral bipolar snapback high-current I-V of a grounded-gate NMOS transistor. This is achieved by building significant linkage between parameters such as to enable a consistent solution of a snapback I-V curve. Experimental evidences from structures with different epitaxial layer thicknesses give strong supports to the assumptions used. The epitaxial layer thickness effect is also addressed in light of the epitaxial layer thickness dependencies of the model parameters.

# REFERENCES

- C. Duvvury and A. Amerasekera, "ESD: A pervasive reliability concern for IC technologies," *Proc. IEEE*, vol. 81, pp. 690–702, 1993.

A. Amerasekera, L. Van Roozendaal, J. Bruines, and F. Kuper, "Char-

- [2] A. Amerasekera, L. Van Roozendaal, J. Bruines, and F. Kuper, "Characterization and modeling of second breakdown in NMOST's for the extraction of ESD-related process and design parameters," *IEEE Trans. Electron Devices*, vol. 38, pp. 2161–2168, 1991.

- [3] S. Ramaswamy, A. Amerasekera, and M. C. Chang, "A unified substrate current model for weak and strong impact ionization in sub-0.25-μm NMOS devices," in *IEDM Tech. Dig.*, 1997, pp. 885–888.

- [4] A. Amerasekera, V. Gupta, K. Vasanth, and S. Ramaswamy, "Analysis of snapback behavior on the ESD capability of sub-0.20-μm NMOS," in *Proc. IEEE IRPS*, 1999, pp. 159–166.

- [5] A. Amerasekera, S. Ramaswamy, M. C. Chang, and C. Duvvury, "Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations," *Proc. IEEE IRPS*, pp. 318–327, 1996.

- [6] I. E. Getreu, Modeling the Bipolar Transistor. Beaverton, OR: Tektronix, Inc., 1976.

- [7] V. Gupta, A. Amerasekera, S. Ramaswamy, and A. Tsao, "ESD-related process effects in mixed-voltage sub-0.5-μm technologies," in *Proc.* EOS/ESD Symp., 1998, pp. 161–169.

- [8] A. D. Stricker, D. Gloor, and W. Fichtner, "Layout optimization of an ESD-protection nMOSFET by simulation and measurement," in *Proc.* EOS/ESD Symp., 1995, pp. 205–211.

- [9] C. Russ, K. Verhaege, K. Bock, P. J. Roussel, G. Groeseneken, and H. E. Maes, "A compact model for the grounded-gate nMOS transistor behavior under CDM ESD stress," *J. Electrostatics*, vol. 42, pp. 351–381, 1998.

- [10] H. Wolf, H. Gieser, and W. Stadler, "Bipolar model extension for MOS transistors considering tate coupling effects in the HBM ESD domain," in *Proc. EOS/ESD Symp.*, 1998, pp. 271–280.

- [11] M. Mergens, W. Wilkening, S. Mettler, H. Wolf, and W. Fichtner, "Modular approach of a high current MOS compact model for circuit-level ESD simulation including transient gate coupling behavior," *Proc. IEEE IRPS*, pp. 167–178, 1999.

- [12] A. Amerasekera, V. McNeil, and M. Rodder, "Correlating drain junction scaling, salicide thickness, and lateral NPN behavior, with the ESD/EOS performance of a 0.25-μm CMOS process," in *IEDM Tech. Dig.*, 1996, pp. 893–896.

[13] W. Y. Jang, C. Y. Wu, and H. J. Wu, "A new experimental method to

- [13] W. Y. Jang, C. Y. Wu, and H. J. Wu, "A new experimental method to determine the saturation voltage of a small-geometry MOSFET," *Solid-State Electron.*, vol. 31, pp. 1421–1431, 1988.

- [14] N. D. Arora and M. S. Sharma, "MOSFET substrate current model for circuit simulation," *IEEE Trans. Electron Devices*, vol. 38, pp. 1392–1398, 1991.

- [15] S. Ramaswamy, E. Li, E. Rosenbaum, and S. M. Kang, "Circuit-level simulation of CDM-ESD and EOS in submicron MOS devices," in *Proc.* EOS/ESD Symp., 1996, pp. 316–321.

- [16] T. H. Huang and M. J. Chen, "Base current reversal phenomenon in a CMOS compatible high gain n-p-n gated lateral bipolar transistor," *IEEE Trans. Electron Devices*, vol. 42, pp. 321–327, 1995.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree (with highest honors) from the National Cheng-Kung University, Taiwan, R.O.C., in 1977, and the M.S. and Ph.D. degrees from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1979 and 1985, respectively, all in electrical engineering.

Since 1985, he has been with the Department of Electronics Engineering, NCTU, where he is currently a Professor. From 1987 to 1992, he was a Principal Consultant of TSMC, where he led a

team from NCTU and ERSO/ITRI to together build process window and design rule. In 1996 and 1997, he critically enabled the ERSO/ITRI video A/D converters and the TSMC mixed-mode CMOS processes, respectively. From 2000 to 2001, he has been a Visiting Professor in the Department of Electrical Engineering, Stanford University, Stanford, CA. His current research interests are in technology reliability physics and nanoscale silicon-based quantum devices. He has graduated six Ph.D. students and has been granted four U.S. patents and six Taiwanese patents in the above areas.

Professor Chen is a co-winner of the 1992 and 1993 Chinese Young Engineer Paper Award and a co-winner of the 1996 Acer Distinguished Ph.D. Dissertation Award. He is a member of Phi Tau Phi.

**Hun-Shung Lee** (S'95–M'01) received the B.S.E.E. degree from Feng-Chia University, Taiwan, R.O.C., in 1977, and the M.S.E.E. degree from Syracuse University, Syracuse, NY, in 1988. Since 1994, he has been a full-time doctoral student at National Chiao-Tung University, Taiwan, R.O.C.

In 1979, he joined the Failure Analysis and Reliability Evaluation Laboratory of PEBEI (Philips Corp. Kaohsiung, Taiwan) in 1979, where he was responsible for IC failure analysis and reliability test evaluation. Since 1981, he has been with the Q&R De-

partment of CSIST, Lung-Tan, Taiwan, as a Research Scientist on defense electronics. Currently, his major research field is the reliability physics of submicron CMOS devices and circuits, especially CMOS ESD and latch-up. He is now Technical Director in the EMC Lab of CSIST.

**Shuenn-Tarng Chen** received the B.S. degree in electronics engineering from National Chiao-Tung University (NCTU), Taiwan, R.O.C., in 1998 and the M.S. degree in electronics engineering from the Institute of Electronics, NCTU, in 2000.

Currently, he is with Avant!, exploring software development tools for deep submicron CMOS devices and circuits including interconnect RLC, latch-up, and ESD.