Home Search Collections Journals About Contact us My IOPscience

Discrete-Dopant-Fluctuated Threshold Voltage Roll-Off in Sub-16 nm Bulk Fin-Type Field Effect Transistors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2008 Jpn. J. Appl. Phys. 47 2580

(http://iopscience.iop.org/1347-4065/47/4S/2580)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/04/2014 at 16:55

Please note that terms and conditions apply.

©2008 The Japan Society of Applied Physics

# Discrete-Dopant-Fluctuated Threshold Voltage Roll-Off in Sub-16 nm Bulk Fin-Type Field Effect Transistors

Yiming LI\* and Chih-Hong HWANG

Department of Communication Engineering, National Chiao Tung University, 1001 Ta-Hsueh Rd., Hsinchu 300, Taiwan

(Received October 2, 2007; accepted November 22, 2007; published online April 25, 2008)

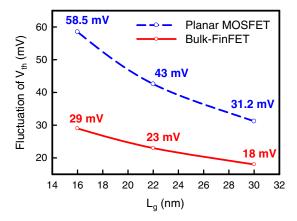

The effect of the number and position of discrete dopants on device characteristics is crucial in determining the behavior of nanoscale semiconductor devices. We explore the fluctuations of threshold voltage ( $V_{th}$ ) roll-off in nanoscale bulk fin-type field effect transistors (FinFETs) by a three-dimensional (3D) statistically full-scale "atomistic" device simulation technique. The explored devices are of three different dimensions: 16, 22, and 30 nm<sup>3</sup>. Discrete dopants are statistically positioned into the 3D channel region to explore associated carrier transport characteristics, concurrently capturing "dopant concentration variation" and "dopant position fluctuation". For the device with a gate length of 16 nm, the  $V_{th}$  fluctuation of FinFETs is only half that of planar metal-oxide-semiconductor (MOS) FET. Compared with planar MOSFETs, the bulk FinEFTs can significantly suppress the fluctuation of  $V_{th}$  roll-off. The standard deviation of  $V_{th}$  is proportional to (WL)<sup>-0.25</sup>, which is better than the (WL)<sup>-0.5</sup> of planar devices. The superior immunity against fluctuation and the stable fluctuation of  $V_{th}$  roll-off indicate the bulk FinFET to be a promising device for the sub-16 nm technology era. [DOI: 10.1143/JJAP.47.2580]

KEYWORDS: threshold voltage fluctuation, random dopant, modeling and simulation, planar MOSFET, bulk FinFET, metal gate

#### 1. Introduction

Ion implantation, diffusion and thermal annealing induce significant characteristic fluctuations randomly in nanometer-scale metal-oxide-semiconductor field effect transistors (MOSFETs). Various randomness effects have recently been investigated both experimentally and theoretically. 1-20) Fluctuations of characteristics are caused not only by a variation in the average doping density (which is associated with a fluctuation in the number of dopants) but also by the particular random distribution of dopants in the channel region. Fluctuations will be very conspicuous when the variations of the spatial scale of doping and the oxide thickness become comparable to the device dimensions. 12,19,20) The International Roadmap for Semiconductors has forecasted a transition from conventional bulk devices to multiple-gate transistors as high-performance devices.<sup>21)</sup> Accordingly, nanoscale devices with vertical channel structures, such as FinFETs, are of great interest. 3,22-24) However, channel doping must be employed to alter the threshold voltage  $(V_{th})$  in today's semiconductor manufacturing processes. Consequently, characteristic fluctuation, induced by discrete dopants, continuously plays an important role in these nanoscale devices including those fascinating devices. Diverse approaches, such as small-signal analysis, <sup>10–12</sup> driftdiffusion, 13-15) and Monte Carlo simulation 16-18) have recently been reported in studies of process-variationand random-dopant-induced characteristic fluctuations. As MOSFETs shrink in size, unlike the electrostatic potential in large MOSFETs, which is controlled by a cloud of remote charges, the electrostatic potential of small MOSFETs is dominated by only a few nearby charges whose contributions are large enough to be distinct. Many approaches<sup>5,9,13)</sup> have been reported for the investigation of the dependence of device scaling on discrete-dopant-induced fluctuation. The fluctuation of  $V_{th}$  in planar MOSFETs is inversely proportional to square root of the device area.<sup>5,9,13)</sup> However, for bulk FinFET device, because of the variety of device structures, the dependence of  $V_{\rm th}$  fluctuation on the channel area of the device has not been clearly investigated by threedimensional (3D) modeling and simulation.

In this study, we thus explore the fluctuations of  $V_{\rm th}$ roll-off in nanoscale bulk FinFETs by a 3D statistically full-scale "atomistic" device simulation technique. The explored devices are of three different dimensions: 16, 22, and 30 nm<sup>3</sup>. The statistically sound 3D "atomistic" device simulation is conducted using parallel computing system.<sup>25–27)</sup> On the basis of statistically generated large-scale doping profiles, each device simulation is performed by solving a set of 3D drift-diffusion equations with quantum corrections by the density gradient method. <sup>28–31)</sup> For the gate length of 16 nm, the  $V_{\rm th}$  fluctuation of FinFETs is only half that of planar MOSFETs. Moreover, the bulk FinEFTs can significantly suppress the fluctuation of  $V_{\rm th}$  roll-off. The fluctuation of  $V_{th}$  is proportional to  $(WL)^{-0.25}$ , which is better than the  $(WL)^{-0.5}$  of planar devices, where W and L are the width and length of the channel, respectively. The superior immunity against fluctuation and the stable fluctuation of  $V_{\rm th}$  roll-off indicate the bulk FinFET to be a promising device for the sub-16 nm device era.

This article is organized as follows. In  $\S 2$ , we describe the analyzing technique. In  $\S 3$ , we discuss the results for the fluctuations of  $V_{th}$  roll-off in nanoscale bulk FinFETs. Finally, conclusions are presented.

## 2. Simulation Methodology

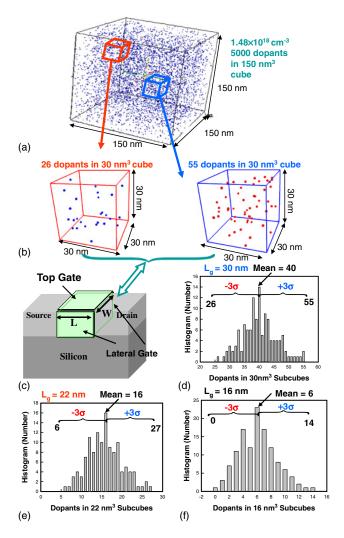

The fluctuation of  $V_{\rm th}$  is assumed to be resulted from the randomness of ion implantation. The nominal channel doping concentration of these devices is  $1.48 \times 10^{18} \, {\rm cm}^{-3}$ . They have a workfunction of  $4.4 \, {\rm eV}$  and a gate oxide thickness of  $1.2 \, {\rm nm}$ . We consider three different channel dimensions, 16, 22, and  $30 \, {\rm nm}^3$ , of the explored device. Outside the channel, the doping concentrations in the source/drain and the background are  $3 \times 10^{20}$  and  $1 \times 10^{15} \, {\rm cm}^{-3}$ , respectively. Take a device with  $30 \, {\rm nm}^3$  channel size as an example. For the channel region, to consider the effect of a random fluctuation in the number and location of discrete channel dopants,  $5000 \, {\rm dopants}$  are first generated in a large cube with  $150 \, {\rm nm}^3$ , in which the equivalent doping concentration is  $1.48 \times 10^{18} \, {\rm cm}^{-3}$ , as shown in Fig. 1(a).

<sup>\*</sup>E-mail address: ymli@mail.nctu.edu.tw

Fig. 1. (Color online) (a) Discrete dopants randomly distributed in  $150\,\mathrm{nm}^3$  cube with average concentration of  $1.48\times10^{18}\,\mathrm{cm}^{-3}$ . There will be 5000 dopants within the cube, but dopants may vary from 26 to 55 (average number is 40) within each of the 125 subcubes of  $30\,\mathrm{nm}^3$  [(b) and (d)]. The 125 sub cubes are then equivalently mapped into the channel region for dopant position/number-sensitive simulation (c). Similar statistically generated discrete-dopant distributions for 22- and 16-nm-gate length are shown in (e) and (f).

The 150 nm<sup>3</sup> cube is then partitioned into 125 subcuboids of 30 nm<sup>3</sup>. The number of dopants may vary from 26 to 55, and the average number is 40, as displayed in Figs. 1(b) and 1(d), respectively. These 125 subcubes are then equivalently mapped into the channel region of the device for the 3D discrete dopant simulation, as shown in Figs. 1(b) and 1(c). The distributions of discrete dopant fluctuated cases for 22 nm and 16 nm gate lengths can be generated by a similar approach, as show in Figs. 1(e) and 1(f). All statistically generated discrete dopants are incorporated into the largescale 3D device simulation, which is conducted using a parallel computing system.<sup>25–27)</sup> According to this analyzing scenario, only channel dopants are treated discretely. The doping concentrations remain continuous in the source/drain region because the concentration of source/drain dopants is two orders of magnitude greater than that of channel dopants. However, as a consequence, the present simulations give only qualitative results. Nevertheless, this approach allows us to focus on the study of characteristic fluctuations induced by the randomness in the number and position of

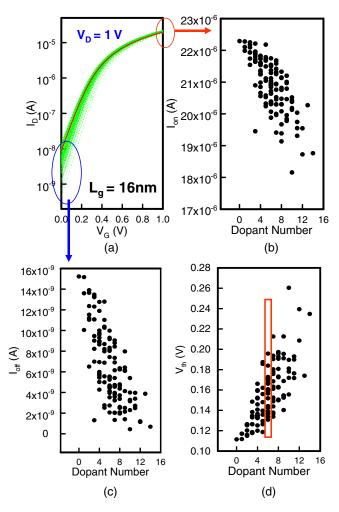

Fig. 2. (Color online) (a) The characteristics of  $I_{\rm D}$ – $V_{\rm G}$ , where the solid line indicates the continuous (i.e., the nominal) case. The fluctuations of (b) on-state current ( $I_{\rm on}$ ), (c) off-state current ( $I_{\rm off}$ ), and (c) threshold voltage ( $V_{\rm th}$ ) as a function of the number of dopants.

dopants in the channel simultaneously. The statistically sound 3D "atomistic" device simulation technique is also computationally cost-effective.

## 3. Results and Discussion

Figure 2(a) shows the large-scale statistically computed results of the drain current (ID) as a function of the gate voltage (V<sub>G</sub>) for the bulk FinFET device with gate length  $(L_g)$  of 16 nm, where the red solid line presents the nominal case (continuous doping profile:  $1.48 \times 10^{18} \, \text{cm}^{-3}$ ) and the dotted lines show the discrete dopant fluctuated cases. The spread of the  $I_D$ - $V_G$  curves indicates the magnitude of the effect of discrete dopants. The characteristics of fluctuation are further explored with respect to the on-state current  $(I_{on})$ , off-state current ( $I_{\text{off}}$ ), and  $V_{\text{th}}$ , as shown in Figs. 2(b), 2(c), and 2(d), respectively. From the random-dopant-number point of view, the equivalent channel doping concentration increases as the dopant number increases; this substantially alters the  $V_{\text{th}}$ ,  $I_{\text{on}}$ , and  $I_{\text{off}}$ . Moreover, it is observed that even for devices with the same numbers of dopants inside the channel, the effect of random dopant position induces different fluctuations of characteristics in spite of there being the same number of dopants. Furthermore, the magnitude of the spread characteristics increases as the number of dopants

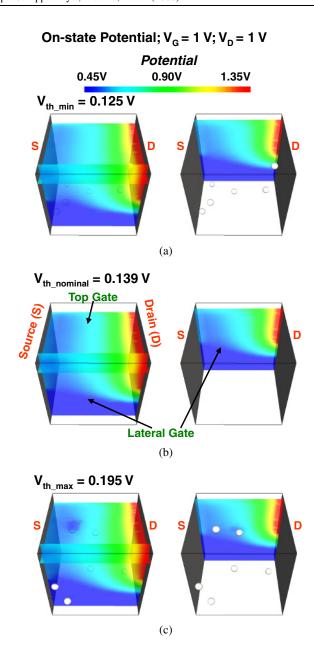

Fig. 3. (Color online) The on-state potential distributions of the 16 nm bulk FinFETs with six discrete dopants inside the channel (average concentration:  $1.48 \times 10^{18} \, \mathrm{cm}^{-3}$ ), as shown in the rectangle of Fig. 2(d), and the nominal case (continuous doping profile:  $1.48 \times 10^{18} \, \mathrm{cm}^{-3}$ ). The potential distributions are 2 nm below the top and lateral gates. The potential distributions for the device with (a) minimal threshold voltage (b) nominal threshold voltage and (c) maximal threshold voltage.

increases. To explore the random-dopant-position-induced  $V_{\rm th}$  fluctuation, the on-state potential distributions of the 16 nm bulk FinFETs with six discrete dopants inside the channel (average concentration:  $1.48 \times 10^{18} \, {\rm cm}^{-3}$ ), as shown by the rectangle in Fig. 2(d), and the nominal case (continuous doping profile:  $1.48 \times 10^{18} \, {\rm cm}^{-3}$ ) are investigated and shown in Fig. 3, where the potential distributions are 2 nm below the top and lateral gates. We note that the  $V_{\rm th}$  is determined from the current criterion that  $I_{\rm D} \geq 10^{-7} (W/L) \, {\rm A}$ . Because of the lack of discrete dopants located near the channel surface, the device with minimal  $V_{\rm th}$ , as shown in Fig. 3(a), exhibits a larger potential distribution than that in the nominal case, as shown in Fig. 3(b). On the other hand, in a device with maximal  $V_{\rm th}$ ,

Table I. Threshold voltages of the studied devices with equivalent doping concentration of  $1.48 \times 10^{18} \, \mathrm{cm}^{-3}$ .

| Technology node (nm) | Nominal V <sub>th</sub> (V) | Maximum $V_{\text{th}}$ (V) | Minimum $V_{\text{th}}$ (V) |

|----------------------|-----------------------------|-----------------------------|-----------------------------|

| 30                   | 0.226                       | 0.268                       | 0.211                       |

| 22                   | 0.192                       | 0.225                       | 0.168                       |

| 16                   | 0.139                       | 0.195                       | 0.125                       |

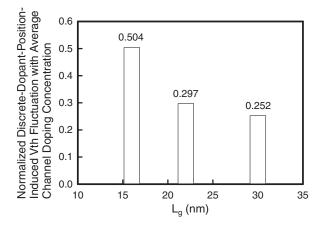

Fig. 4. For cases with  $1.48 \times 10^{18} \, \mathrm{cm}^{-3}$  average channel doping concentration, the maximum differences in threshold voltage induced by discrete-dopant-position effect for 30, 22, and 16 nm gate lengths, which are normalized by the corresponding nominal threshold voltage.

as shown in Fig. 3(c), there are four dopants located near the surface of the channel. The corresponding potential distributions near these dopants are significant decreased, which significantly changes the electron conducting path. The random dopant position induces rather different fluctuations of characteristics in spite of there being the same number of dopants. The results for the studied devices with the same doping concentration of  $1.48 \times 10^{18} \, \mathrm{cm}^{-3}$  are summarized in Table I. The maximum differences in  $V_{\rm th}$  induced by the discrete-dopant-position effect for 30, 22, and 16 nm gate lengths are then normalized with respect to their nominal  $V_{\rm th}$ , as plotted in Fig. 4. The result shows a significant increase in discrete-dopant-position-induced  $V_{\rm th}$  fluctuation in nanoscale transistors.

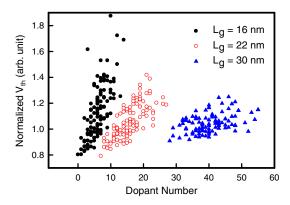

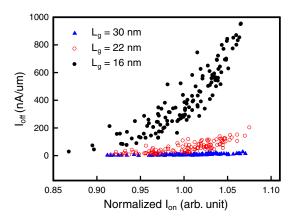

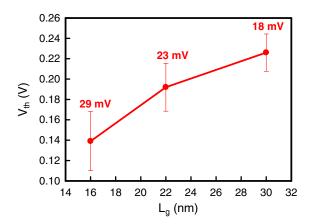

Figure 5 shows the fluctuations of  $V_{\rm th}$  for the 30-, 22-, and 16-nm-gate bulk FinFETs. All  $V_{\rm th}$ 's of the studied devices are normalized by their corresponding nominal  $V_{\rm th}$ . As bulk FinFETs shrink in size, the  $V_{\rm th}$  scales with an increasing fluctuation of  $V_{\rm th}$ . In addition to the fluctuation of  $V_{\rm th}$ , the fluctuation of current is significant. Figure 6 shows the  $I_{\rm on}$ - $I_{\rm off}$  characteristic fluctuations. For cases with similar  $I_{\rm on}$ , the maximum fluctuation of  $I_{\rm off}$  increases significantly as the gate length is scaled down. The plot of  $V_{\rm th}$  roll-off and fluctuation of  $V_{th}$  against the gate length of bulk-FinFETs is shown in Fig. 7. The  $V_{\rm th}$  fluctuation of the 22- and 16-nmgate bulk FinFETs are 1.28 and 1.61 times larger than that of the 30-nm-gate device. Fluctuation of  $V_{\rm th}$  for bulk FinFETs and planar MOSFETs are presented in Fig. 8. For the gate length of 16 nm, the  $V_{\rm th}$  fluctuation of FinFETs is only half that of planar MOSFETs. Moreover, as gate length is reduced from 30 to 16 nm, the fluctuation of  $V_{\rm th}$  is increased by 11 mV, which is better than the increase in the case of

Fig. 5. (Color online) Fluctuations of threshold voltage for the 30-, 22-, and 16-nm-gate bulk FinFETs. The threshold voltages of the studied devices are normalized by the corresponding nominal threshold voltage.

Fig. 6. (Color online) On-off state current characteristics of the 30-, 22-, and 16-nm-gate bulk FinFET devices.

Fig. 7. (Color online) Plot of threshold voltage roll-off for the 30-, 22-, and 16-nm-gate bulk FinFETs, where the bars indicate the fluctuation of threshold voltage.

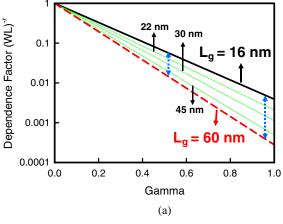

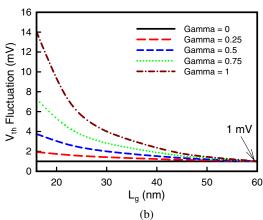

$$\sigma_{V_{\text{th}}} \approx (WL)^{-\gamma},$$

(1)

where  $\gamma$  is 0.5 for the planar MOSFETs.<sup>5,9,13)</sup> The dependence factor of threshold voltage,  $(WL)^{-\gamma}$ , is then plotted as a function of  $\gamma$ , as shown in Fig. 9(a). As  $\gamma$  decreases, the difference between 60 and 16 nm decreases. The difference

Fig. 8. (Color online) Fluctuations of threshold voltage roll-off (i.e., vs the  $L_{\rm g}$ ) of bulk FinFETs and planar MOSFETs.

Fig. 9. (Color online) Threshold voltage fluctuation as a function of device dimension. (a) Plots of dependence factor on  $\gamma$  for various device dimensions. (b) Fluctuation of threshold voltage for the 60-nm-gate device was assumed to be 1 mV.

is greater than one order for  $\gamma=1$  and less than one order for  $\gamma=0.5$ . The dependence on device dimension is eliminated at  $\gamma=0$ , which means that the  $V_{\rm th}$  fluctuation will be constant regardless of the size of the device. Assume the fluctuation of  $V_{\rm th}$  for the 60-nm-gate device to be 1 mV. Figure 9(b) shows the increase in  $V_{\rm th}$  fluctuation as the device becomes smaller. The fluctuation of  $V_{\rm th}$  decreases as  $\gamma$  decreases. According to this relationship and the aforementioned results, the  $\gamma$  factor of the bulk FinFETs on

device dimension is then fitted to be 0.25. For the device with 16 nm gate length, the fluctuation of device with  $\gamma=0.5$ , as shown in Fig. 9(b), is about two times larger than that of  $\gamma=0.25$ , which is similar to the results in Fig. 8. The bulk FinFETs shows superior immunity against fluctuation and less sensitivity to device size, which indicates the bulk FinFET to be a promising device for the sub-16 nm device era.

### 4. Conclusions

The dependence of discrete-dopants-induced threshold voltage fluctuation roll-off on the size of nanoscale bulk FinFETs has been statistically explored by a full-scale 3D atomistic simulation technique. Discrete dopants were statistically positioned into 3D channel regions, 16, 22, and 30 nm<sup>3</sup>, to explore the associated carrier transport characteristics, concurrently capturing "dopant concentration variation" and "dopant position fluctuation". The dependence of the threshold voltage fluctuation of bulk FinFETs on device dimension was empirically fitted as  $\sigma_{V_{\rm th}} \approx (WL)^{-0.25}$ , which is superior to that of planar MOSFETs,  $\sigma_{V_{th}} \approx (WL)^{-0.5}$ . The preliminary results indicate the bulk FinFETs can not only provide better immunity against discrete-dopant-induced threshold voltage fluctuations, but also show less sensitivity to device size than planar MOSFETs. The superior immunity against fluctuation and the more stable fluctuation of threshold voltage roll-off indicate the bulk FinFET to be a promising device for the sub-16 nm era.

We have noted that the study will be more interesting if we can separately calculate the dependences of  $V_{\rm th}$  fluctuation on W and L of the device. However, this statistically sound large-scale 3D simulation requires huge central processing unit time; for example, it required about 3 months to examine the three technology nodes described herein (because we had to perform 375 3D simulations in total). According to our estimation, it will take about 9 months to independently consider the effects of W and L of the device on  $V_{\rm th}$  fluctuation. We are planning to conduct such an investigation and will include discussion on the W and L dependences of  $V_{\rm th}$  fluctuation in our future work.

# Acknowledgments

This work was supported by Taiwan National Science Council (NSC) under Contract NSC-96-2221-E-009-210 and Contract NSC-96-2752-E-009-003-PAE, and by the

Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan, under a 2006–2008 grant.

- 1) R. W. Keyes: Appl. Phys. 8 (1975) 251.

- 2) H.-S. Wong and Y. Taur: IEDM Tech. Dig., 1993, p. 705.

- 3) Y. Li and C.-H. Hwang: Microelectron. Eng. 84 (2007) 2093.

- X.-H. Tang, V. K. De, and J. D. Meindl: IEEE Trans. VLSI Syst. 5 (1997) 369.

- P. A. Stolk, F. P. Widdershoven, and D. B. M. Klaassen: IEEE Trans. Electron Devices 45 (1998) 1960.

- S. Xiong and J. Bokor: IEEE Trans. Electron Devices 50 (2003) 2255.

- 7) P. Dollfus, A. Bournel, S. Galdin, S. Barraud, and P. Hesto: IEEE Trans. Electron Devices **51** (2004) 749.

- 8) S. Roy and A. Asenov: Science 309 (2005) 388.

- 9) A. Asenov, A. R. Brown, J. H. Davies, S. Kaya, and G. Slavcheva: IEEE Trans. Electron Devices **50** (2003) 1837.

- 10) Y. Li and S.-M. Yu: J. Comput. Electron. 5 (2006) 125.

- 11) P. Andrei and I. D. Mayergoyz: J. Appl. Phys. 94 (2003) 7163.

- 12) Y. Li and S.-M. Yu: Jpn. J. Appl. Phys. 45 (2006) 6860.

- 13) A. Asenov: IEEE Trans. Electron Devices 45 (1998) 2505.

- D. J. Frank, Y. Taur, M. Ieong, and H.-S. Wong: Dig. Tech. Pap. Symp. VLSI Technology, 1999, p. 169.

- A. R. Brown, A. Asenov, and J. R. Watling: IEEE Trans. Nanotechnol. 1 (2002) 195.

- C. L. Alexander, G. Roy, and A. Asenov: IEDM Tech. Dig., 2006, p. 1.

- W. J. Gross, D. Vasileska, and D. K. Ferry: IEEE Electron Device Lett. 20 (1999) 463.

- C. J. Wordelman and U. Ravaioli: IEEE Trans. Electron Devices 47 (2000) 410.

- F.-L. Yang, J.-R. Hwang, H.-M. Chen, J.-J. Shen, S.-M. Yu, Y. Li, and D. D. Tang: Dig. Tech. Pap. Symp. VLSI Technology, 2007, p. 208.

- F.-L. Yang, J.-R. Hwang, and Y. Li: Proc. IEEE Custom Integrated Circuits Conf., 2006, p. 691.

- 21) http://www.itrs.net

- Y. Li, H.-M. Chou, and J.-W. Lee: IEEE Trans. Nanotechnol. 4 (2005) 510.

- Y. Li and W.-H. Chen: Proc. IEEE Nanotechnology Conf., Vol. 2, 2006, p. 569.

- 24) E. J. Nowak, I. Aller, T. Ludwig, K. Kim, R. V. Joshi, C.-T. Chuang, K. Bernstein, and R. Puri: IEEE Circuits Devices Mag. 20 (2004) No. 1, 20.

- 25) Y. Li and S.-M. Yu: J. Comput. Appl. Math. 175 (2005) 87.

- Y. Li, H.-M. Lu, T.-W. Tang, and S. M. Sze: Math. Comput. Simulation 62 (2003) 413.

- 27) Y. Li, S. M. Sze, and T. S. Chao: Eng. Comput. 18 (2002) 124.

- 28) M. G. Ancona and H. F. Tiersten: Phys. Rev. B 35 (1987) 7959.

- S. Odanaka: IEEE Trans. Comput.-Aided Des. Integrated Circuits Syst. 23 (2004) 837.

- 30) T.-W. Tang, X. Wang, and Y. Li: J. Comput. Electron. 1 (2002) 389.

- G. Roy, A. R. Brown, A. Asenov, and S. Roy: J. Comput. Electron. 2 (2003) 323.