### Comparison of ultrathin CoTiO 3 and NiTiO 3 high-k gate dielectrics

Tung Ming Pan, Tan Fu Lei, and Tien Sheng Chao

Citation: Journal of Applied Physics 89, 3447 (2001); doi: 10.1063/1.1347405

View online: http://dx.doi.org/10.1063/1.1347405

View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/89/6?ver=pdfcov

Published by the AIP Publishing

#### Articles you may be interested in

Soft-breakdown-suppressed ultrathin atomic-layer-deposited silicon—nitride/SiO 2 stack gate dielectrics for advanced complementary metal—oxide—semiconductor technology

Appl. Phys. Lett. 79, 3488 (2001); 10.1063/1.1420586

Effective enhancement of C54 TiSi 2 phase formation with multi-thermal-shock processing at 600°C

Appl. Phys. Lett. 79, 1139 (2001); 10.1063/1.1382630

Characterization of RuO 2 electrodes on Zr silicate and ZrO 2 dielectrics

Appl. Phys. Lett. 78, 1134 (2001); 10.1063/1.1347402

X-ray photoelectron spectroscopy and time-of-flight secondary ion mass spectrometry study of the role of Ti and TiN caps on the cobalt/SiO 2 interface

J. Vac. Sci. Technol. A 17, 1244 (1999); 10.1116/1.581804

Effect of Al 3 Ti intermetallic compound on electromigration lifetime of Al alloy interconnections

J. Appl. Phys. 84, 742 (1998); 10.1063/1.368132

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

JOURNAL OF APPLIED PHYSICS VOLUME 89, NUMBER 6 15 MARCH 2001

## Comparison of ultrathin CoTiO<sub>3</sub> and NiTiO<sub>3</sub> high-k gate dielectrics

Tung Ming Pan, Tan Fu Lei, and Tien Sheng Chao<sup>a)</sup>

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University,

Hsinchu 300, Taiwan, Republic of China

(Received 23 August 2000; accepted for publication 13 December 2000)

High-k cobalt—titanium oxide (CoTiO<sub>3</sub>) and nickel—titanium oxide (NiTiO<sub>3</sub>) were formed by directly oxidizing sputtered Co/Ti and Ni/Ti film. Al/CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si and Al/NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor structures were fabricated and measured. The effective dielectric constant (k value $\cong$ 45) with buffer layer for CoTiO<sub>3</sub> is larger than that of NiTiO<sub>3</sub>. In addition, CoTiO<sub>3</sub> depicts excellent electrical properties at the same time. This metal oxide thus appears to be a very promising high-k gate dielectric for future ultralarge scale integrated devices. © 2001 American Institute of Physics. [DOI: 10.1063/1.1347405]

#### I. INTRODUCTION

To continue the scaling trend of complementary metal oxide-semiconductor (CMOS) technology, the high leakage current is inevitable due to direct tunneling when oxide thickness is less than 25 Å.1 In order to suppress the tunneling current, alternative gate dielectric with higher dielectric constant than conventional SiO<sub>2</sub> is necessary to provide a physically thicker film for the required equivalent oxide thickness  $E_{\rm OT}$ . Gate dielectric materials having high dielectric constant, low interface state density, and good thermal stability are needed for future gate dielectric applications. Ultrathin silicon nitride<sup>2</sup> and Al<sub>2</sub>O<sub>3</sub> (Ref. 3) gate dielectrics are proposed to replace the conventional oxide to meet the need for increased capacitance, while maintaining a low gate leakage. Because the dielectric constant is only two times larger than that of SiO<sub>2</sub>, the technology life span of nitride or Al<sub>2</sub>O<sub>3</sub> is expected to last no longer than two or three generations. Recently, many high-k materials such as HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, and TiO<sub>2</sub> gate dielectric films have been widely studied;<sup>4–7</sup> however, these high-k films having a slightly higher leakage current and lower-k value may not be an adequate choice for alternative gate dielectric application. Materials having too high dielectric constant such as SrTiO<sub>3</sub> or BaTiO<sub>3</sub> may cause short-channel performance degradation due to the fringing fields from the gate to source/drain regions.<sup>8</sup> Also, dielectric constant materials larger than 50 are suitable only for dynamic random access memory applications, but inadequate as the gate dielectric of metaloxide-semiconductor devices.

The formation of interfacial silicon oxide layer during the metal—oxide deposition process is a serious issue high-k gate dielectric development. An interfacial SiO<sub>2</sub> layer with a thickness over 20 Å was obtained when Ta<sub>2</sub>O<sub>5</sub> was deposited directly on silicon. This interfacial oxide layer will limit the scalability of high-k dielectrics and cause poor interface quality. Besides, thermal stability of the high-k dielectric is

another major concern, as severe degradation of the dielectric quality has been shown to occur after  $Ta_2O_5$  is subjected to processing temperature above  $800\,^{\circ}\text{C.}^{10}$  In this article, we report high-k dielectrics, i.e.,  $CoTiO_3$  and  $NiTiO_3$ , which is formed by direct oxidation of sputtering Co/Ti and Ni/Ti films. These metal—oxides were explored for their electrical property influence on oxidizing different temperature and time.

#### II. EXPERIMENT

Samples were fabricated on 6-in.-diam, p-type (100)oriented Si wafers with resistivity of 14-21  $\Omega$  cm. All the wafers were first cleaned by the standard RCA clean method. To avoid reaction between metal and silicon during the sputtering process and later high-temperature oxide step, a 10 Å Si<sub>3</sub>N<sub>4</sub> film was grown by NH<sub>3</sub> (flow rate 105 sccm, pressure 500 mTorr) nitridation of the Si substrate in a low pressure chemical vapor deposition system at 800 °C for 1 h. Afterward, all samples were immediately deposited in sequence with Ti (50 Å) and then Co (50 Å) or Ni (50 Å) film from independent targets by using the physical vapor deposition method. The direct thermal oxidation was carried out at 700, 750, or 800 °C in diluted  $O_2(N_2/O_2=2/1)$  gas as listed in Table I to form cobalt-titanium oxide and nickel-titanium oxide films. A 5000 Å Al film was deposited on the wafer by a thermal coater to serve as the gate electrode. The gate of the MOS capacitor was defined by lithography, and then Al was etched by wet etching solutions. Finally, a 5000 Å Al film was also deposited on the backside of the wafers after stripping the oxide on the backside. The x-ray diffraction (XRD) provides identify of the composition and the phase of these new metal-oxide films. The equivalent oxide thickness of CoTiO<sub>3</sub> and NiTiO<sub>3</sub> oxidized for Si<sub>3</sub>N<sub>4</sub> buffered layer structures was by high frequency capacitance-voltage (C-V) of 0.1 MHz at an operating range of -3-2 V in the strong accumulation region without considering quantum mechanical effects. The physical thickness was doubly checked by transmission electron micros-

a)Also with: National Nano Device Laboratories, and Department of Engineering and System Science, National Tsing Hua University, Hsinchu 300, Taiwan, Republic of China; electronic mail: tschao@ndl.gov.tw

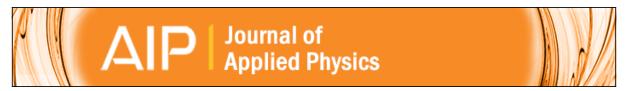

FIG. 1. XRD spectrum of  $CoTiO_3$  films oxidized at: (a) 700  $^{\circ}C$  and (b) 800  $^{\circ}C$  for various conditions.

FIG. 2. XRD spectrum of NiTiO  $_3$  films oxidized at: (a) 700  $^{\circ}{\rm C}$  and (b) 750  $^{\circ}{\rm C}$  for various conditions.

copy to obtain the *k* value. The electrical properties and reliability characteristics of the metal–oxide were measured by using the Hewlett–Packard (HP) 4156 semiconductor parameter analyzer.

TABLE I. Various oxidation conditions for CoTiO3 and NiTiO3 films.

| Condition | Oxidation and annealing time                                                                 |

|-----------|----------------------------------------------------------------------------------------------|

| A         | Oxidation for 5 min in diluted O <sub>2</sub> (N <sub>2</sub> /O <sub>2</sub> =1/1) gas      |

| В         | Oxidation for 5 min in diluted $O_2(N_2/O_2=1/1)$ gas and annealing for 5 min in $N_2$ gas   |

| C         | Oxidation for 10 min in diluted $O_2(N_2/O_2=1/1)$ gas                                       |

| D         | Oxidation for 10 min in diluted $O_2(N_2/O_2=1/1)$ gas and annealing for 10 min in $N_2$ gas |

#### III. RESULTS AND DISCUSSION

Film crystallization and degradation during the backend thermal process is a major concern for metal–oxide with high dielectric constant. The Ilmenite structure is the  $CoTiO_3$  (Ref. 11) and  $NiTiO_3$  compounds in which Co or Ni and Ti both prefer to form a structure of octahedral coordination. This structure is similar to the corundum structure of  $Al_2O_3$ , which is density and stable. Figures 1(a) and 1(b) show XRD spectra of oxidizing at various conditions for  $CoTiO_3$  samples. Samples with the  $Si_3N_4$  buffer layer and oxidized at either 700 or 800 °C reacted with oxygen and formed cobalt–titanium oxide films (named  $CoTiO_3/Si_3N_4/Si$ ). Samples oxidized at 800 °C under conditions A and B [Fig.

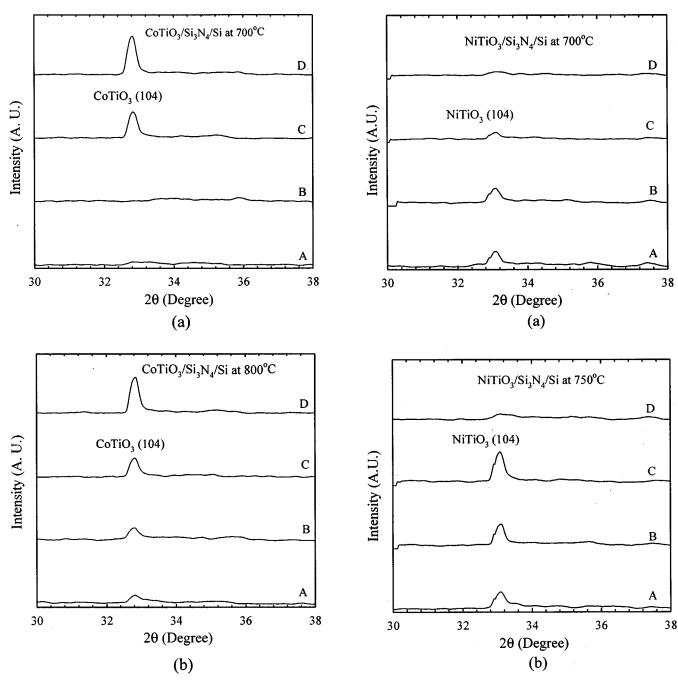

FIG. 3. C-V curves of CoTiO<sub>3</sub> films oxidized at: (a) 700 °C and (b) 800 °C for various conditions.

FIG. 4. C-V curves of NiTiO $_3$  films oxidized at: (a) 700 °C and (b) 750 °C for various conditions.

2(b)] had a stronger spectrum than those of samples oxidized at 700 °C [Fig. 2(a)]. No noticeable CoTiO<sub>3</sub> crystal peak is observed for oxidation at 700 °C and 5 min, suggesting that there was insufficient time for crystallization. The CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si oxidized at either 700 or 800 °C for condition D (oxidation for 10 min, with additional 10 min N<sub>2</sub> annealing) has a stronger spectrum than that oxidized at condition C (only oxidation for 10 min). This implies that a sample oxidized and annealed for a long time can enhance crystallization of CoTiO<sub>3</sub>. Figures 2(a) and 2(b) show the NiTiO<sub>3</sub> with the S<sub>3</sub>N<sub>4</sub> buffer layer (named NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si) for oxidation at 700 and 750 °C. Samples oxidized at 750 °C have a stronger spectrum than those oxidized at 700 °C. However, samples oxidized at 700 and 750 °C with condition

D exhibit a weak peak. This phenomenon could be explained by the fact that the ultrathin silicon nitride buffer layer was not able to retard the nickel diffusion at an elevated oxidation and annealing process.

The tendency to form an interfacial silicon oxide layer during sputtering and thermal process makes it very difficult to realize the high k that one wishes to achieve. The use of a high quality silicon nitride buffer layer solves this problem. The  $E_{\rm OT}$  of these metal oxides with  ${\rm Si_3N_4}$  buffer layers are extracted from the C-V curves of Figs. 3(a) and 3(b). Well behavior C-V characteristics were observed for the  ${\rm CoTiO_3/Si_3N_4/Si}$  capacitor even with an  $E_{\rm OT}$  of less than 20 Å. It is clear that the  ${\rm CoTiO_3/Si_3N_4/Si}$  capacitor with oxidation at 800 °C shows less distortion in the depletion region

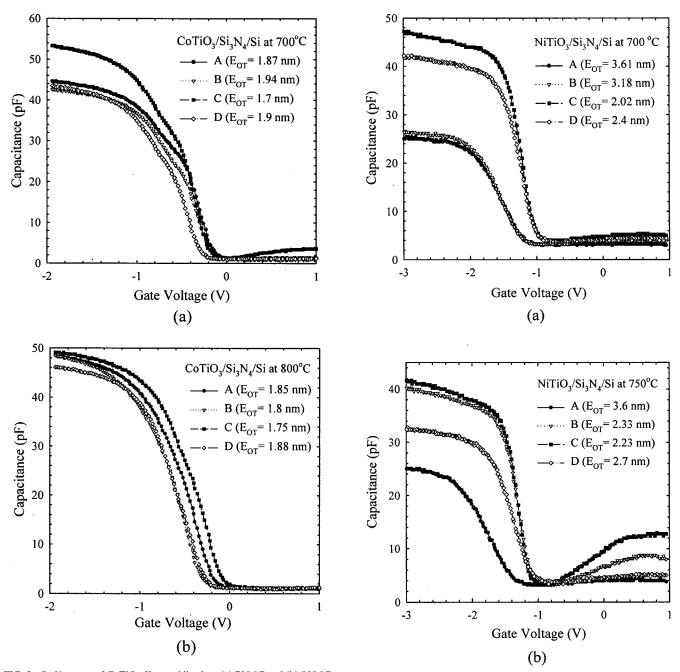

FIG. 5. The k value of  $CoTiO_3$  and  $NiTiO_3$  films oxidized at various temperatures and conditions.

than that of oxidation at 700 °C. This indicates that there could be insufficient temperature for densification and crystallization by oxidizing and annealing at 700 °C. The C-Vcurves and  $E_{OT}$  with various process conditions for the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor are shown in Figs. 4(a) and 4(b). The flatband voltage of the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor is over -1.5 V, which is a larger than that of CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si of -1 V. The result is that CoTiO<sub>3</sub> can imply a lesser amount of fixed charge than NiTiO<sub>3</sub>. In addition, as the  $E_{\rm OT}$ of the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor increases, it is suggested that nickel diffusion into the buffer layer will limit the scalability of high-k dielectrics and cause poor interface quality. The decreased capacitance value of conditions A and B oxidized at 700 °C for the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor could be due to insufficient time for crystallization at this temperature. Nevertheless, the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor oxidized at 750 °C for conditions A and D decreases capacitance value. This suggests that film crystallization has insufficient time at 750 °C and NiTiO<sub>3</sub> crystallization damages the ultrathin silicon nitride buffer layer to reduce k value.

The effective dielectric constant (*k* value) of these metal–oxides with buffer layer depends on the process conditions. The CoTiO<sub>3</sub> film including the silicon nitride buffer layer depicts a higher value than that of NiTiO<sub>3</sub> as shown in Fig. 5. On the other hand, it shows that samples oxidized at 700 °C in condition C for the CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si and NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si stacks have the highest *k* value among the four conditions. This result could be explained because metal–oxide for crystallization was insufficient by oxidizing time in conditions A and B. The metal–oxide formed crystallization in condition D seems to have damaged the ultrathin nitride buffer layer. Condition C is the optimum condition.

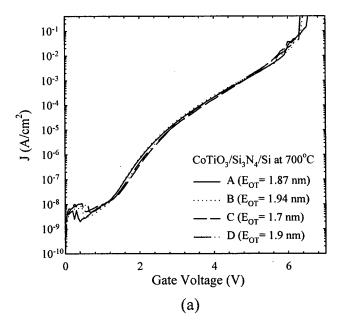

Figures 6(a) and 6(b) show the corresponding J-V characteristics of CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si samples oxidized at 700 and 800 °C, respectively. It is noted that metal—oxides oxidized at 800 °C show compatible leakage current compared to the sample oxidized at 700 °C. Since all curves are close to each

FIG. 6. J-V characteristics of CoTiO<sub>3</sub> films oxidized at: (a) 700 °C and (b) 800 °C for various conditions.

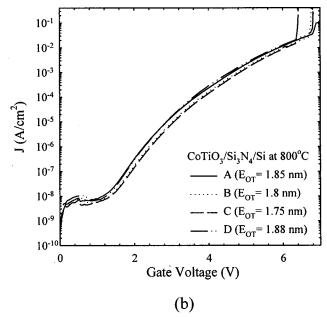

other, the gate leakage current and breakdown voltage of CoTiO<sub>3</sub> film is almost independent of those oxidized at different conditions. However, the gate leakage current and breakdown voltage of NiTiO<sub>3</sub> film depend on oxidizing at different conditions, as shown in Figs. 7(a) and 7(b). The gate leakage current density at a low field of NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si oxidized at 750 °C is lower than that oxidized at 700 °C. Thus, high temperature processes benefit from full crystallization of film.

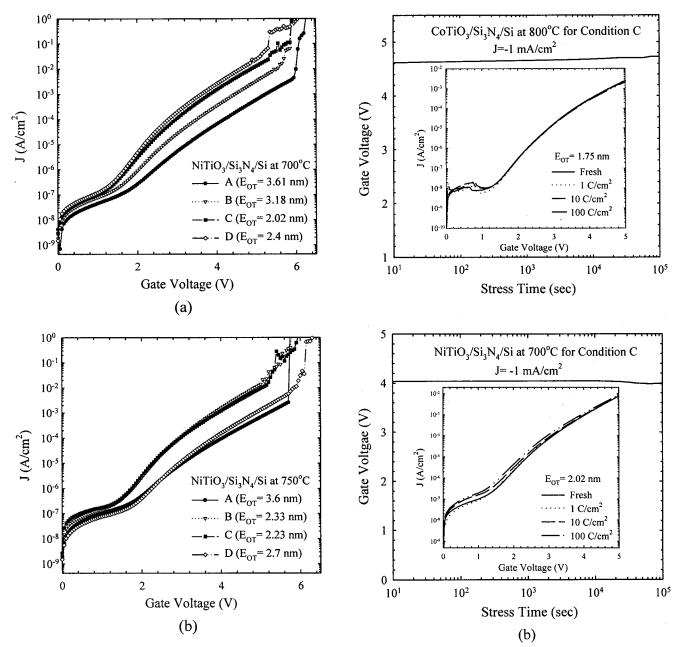

Figure 8(a) shows the result after constant current stressing at  $-1 \text{ mA/cm}^2$  for the  $\text{CoTiO}_3/\text{Si}_3\text{N}_4/\text{Si}$  stack. Time dependent dielectric breakdown measurement shows that there was no considerable charge trapping for these capacitors oxidized at 800 °C for condition C. No significant stressinduced-leakage current (SILC) was observed for these

FIG. 7. J-V characteristics of NiTiO<sub>3</sub> films oxidized at: (a) 700 °C and (b) 750 °C for various conditions.

samples even after  $10^5$  s stressing, as shown in the inset of Fig. 8(a). On the other hand, from Fig. 8(b), the time dependence of the gate voltage shows that there is no significant charge trapping for the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si stack oxidized at 700 °C in condition C. No significant increase of leakage current was formed for these samples after  $10^5$  s stressing, as shown in the inset of Fig. 8(b). However, it indicates that some traps or defects exist in the NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si structure. This phenomenon could result from nickel diffusion into the silicon interface, causing excessively fixed charge. From the above result, it is clearly seen that CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitors exhibit a less significant increase of leakage current in SILC than NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitors.

#### IV. CONCLUSION

We have reported high-k material cobalt-titanium oxide (CoTiO<sub>3</sub>) and nickel-titanium oxide (NiTiO<sub>3</sub>), which is

FIG. 8. The gate voltage during constant current stress of  $-1~\text{mA/cm}^2$ . Inset shows SILC under constant voltage stress for: (a) CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitors oxidized at 800 °C for condition C and (b) NiTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitors oxidized at 700 °C for condition C.

formed by direct oxidation of the sputtered Co/Ti and Ni/Ti film. The  $CoTiO_3/Si_3N_4/Si$  structure shows higher k value and better electrical properties, such as low gate leakage current at low voltage operation and high reliability after stressing, than the  $NiTiO_3/Si_3N_4/Si$  structure. This high-k material with  $CoTiO_3$  thus appears to be very promising for future ultralarge scale integrated devices.

#### **ACKNOWLEDGMENTS**

The authors would like to express their appreciation to the entire staff of the Semiconductor Research Center, National Chiao Tung University for their technical help. Financial support was from National Science Council Taiwan, Republic of China under Contract No. NSC89-2215-E009-306.

- <sup>1</sup>C. Hu, Tech. Dig. Int. Electron Devices Meet. **1996**, 319 (1996).

- <sup>2</sup>S. C. Song, H. F. Luan, Y. Y. Chen, M. Gardner, J. Fulford, M. Allen, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. **1998**, 373 (1998).

- <sup>3</sup> A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, *VLSI Technical Symposium Digest*, 1999, p. 135.

- <sup>4</sup>B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, Tech. Dig. Int. Electron Devices Meet. **1999**, 133 (1999).

- <sup>5</sup>W. J. Qi, R. Nieh, B. H. Lee, L. Kang, Y. Jeon, K. Onishi, T. Ngai, S. Banerjee, and J. C. Lee, Tech. Dig. Int. Electron Devices Meet. **1999**, 145 (1999).

- <sup>6</sup>H. F. Luan, S. J. Lee, S. C. Song, Y. L. Mao, Y. Senzaki, D. Roberts, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. **1999**, 141 (1999).

- <sup>7</sup> X. Guo, X. Wang, Z. Luo, T. P. Ma, and T. Tamagawa, Tech. Dig. Int. Electron Devices Meet. **1999**, 137 (1999).

- <sup>8</sup>B. Cheng, M. Cao, P. V. Voorde, W. Greene, H. Stork, Z. Yu, and J. C. S. Woo, IEEE Trans. Electron Devices 46, 261 (1999).

- <sup>9</sup>G. B. Alers, D. J. Werder, and Y. Chabal, Appl. Phys. Lett. **73**, 1517 (1998).

- <sup>10</sup>F. Chiu, J. Wang, J. Lee, and S. C. Wu, J. Appl. Phys. **81**, 6911 (1997).

- <sup>11</sup>T. M. Pan, T. F. Lei, T. S. Chao, K. L. Chang, and K. C. Hsieh, Electron. Solid-State Lett. 3, 433 (2000).

- <sup>12</sup>Y. M. Chiang, D. P. Birnie, and W. D. Kingery, *Physical Ceramics* (Wiley, New York, 1997), p. 33.