## High-k cobalt-titanium oxide dielectrics formed by oxidation of sputtered Co/Ti or Ti/Co films

Tung Ming Pan, Tan Fu Lei, and Tien Sheng Chao

Citation: Applied Physics Letters 78, 1439 (2001); doi: 10.1063/1.1352044

View online: http://dx.doi.org/10.1063/1.1352044

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/78/10?ver=pdfcov

Published by the AIP Publishing

#### Articles you may be interested in

Hybrid titanium—aluminum oxide layer as alternative high- k gate dielectric for the next generation of complementary metal—oxide—semiconductor devices

Appl. Phys. Lett. **86**, 042904 (2005); 10.1063/1.1856137

Characteristics of high-k gate dielectric formed by the oxidation of sputtered Hf/Zr/Hf thin films on the Si substrate

J. Vac. Sci. Technol. A 22, 1342 (2004); 10.1116/1.1760751

Properties of La-silicate high-K dielectric films formed by oxidation of La on silicon

J. Appl. Phys. 93, 1691 (2003); 10.1063/1.1531818

Comparison of ultrathin CoTiO 3 and NiTiO 3 high-k gate dielectrics

J. Appl. Phys. 89, 3447 (2001); 10.1063/1.1347405

Ultrathin oxide films deposited using electron cyclotron resonance sputter

J. Vac. Sci. Technol. B 17, 2222 (1999); 10.1116/1.590897

APPLIED PHYSICS LETTERS VOLUME 78, NUMBER 10 5 MARCH 2001

# High-k cobalt-titanium oxide dielectrics formed by oxidation of sputtered Co/Ti or Ti/Co films

### Tung Ming Pan and Tan Fu Lei

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, Republic of China

### Tien Sheng Chao<sup>a)</sup>

National Nano Device Laboratories, and Department of Engineering and System Science, National Tsing Hua University, Hsinchu 300, Taiwan, Republic of China

(Received 14 August 2000; accepted for publication 4 January 2001)

High-k cobalt—titanium oxide (CoTiO<sub>3</sub>) film was formed by directly oxidizing sputtered Co/Ti or Ti/Co films. Al/CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si capacitor structures were fabricated and measured. Excellent electrical properties with an effective dielectric constant (i.e., k value) as high as 40 have been achieved for a CoTiO<sub>3</sub> gate dielectric with a buffer layer. The metal—oxide thus appears to be a very promising high-k gate dielectric for future ultralarge scale integrated devices. © 2001 American Institute of Physics. [DOI: 10.1063/1.1352044]

As conventional SiO<sub>2</sub> gate dielectric scales down to less than 20 Å, a high leakage current is inevitable due to the occurrence of direct tunneling. To solve this problem, high-k (>3.9 of oxide) dielectric materials that allow a physically thicker film for the required equivalent oxide thickness  $(E_{OT})$  are proposed to replace the conventional SiO<sub>2</sub>. Thus, gate dielectric materials having high dielectric constant, low interface state density and good thermal stability appear to be promising for future gate dielectric application. Recently,  $Si_3N_4$  (k=7),  $Al_2O_3$  (k=9),  $Ta_2O_5$  (k=25), and  $TiO_2$  (k =40) gate dielectric films have been widely studied.<sup>2-5</sup> However, these high-k films still exhibit undesirable high leakage current. The formation of an interfacial silicon oxide layer during the metal-oxide deposition process is a serious issue in high-k gate dielectric development. An interfacial SiO<sub>2</sub> layer with a thickness over 20 Å was obtained when Ta<sub>2</sub>O<sub>5</sub> was deposited directly on silicon. This interfacial oxide layer seriously limits the scalability of high-k dielectrics and causes poor interface quality. <sup>6</sup> Besides, thermal stability of the high-k dielectric material is another major concern. Severe degradation of the dielectric quality has been shown to occur after Ta<sub>2</sub>O<sub>5</sub> is subjected to processing temperature above 800 °C.7 In this letter, we reported a cobalt-titanium oxide (CoTiO<sub>3</sub>) film as an alternative gate dielectric. This CoTiO<sub>3</sub> film is formed by direct oxidation of Co/Ti or Ti/Co films. From our results, the dielectric constant can reach as high as 40, while depicting excellent electrical properties.

Samples were fabricated on *p*-type (100)-oriented Si wafers with resistivity of 14–21  $\Omega$  cm. All wafers were first cleaned by a standard Radio Corporation of America clean. To avoid reaction between metal and silicon during the sputtering process and later high-temperature oxidation step, a 10 Å Si<sub>3</sub>N<sub>4</sub> film was first grown by NH<sub>3</sub> nitridation of the Si substrate in low-pressure chemical vapor deposition system at 800 °C for 1 h. Afterwards, samples were immediately deposited in sequence first with a 50 Å Ti and then a 50 Å Co (Co/Ti), or first a 50 Å Co and then 50 Å Ti (Ti/Co) film

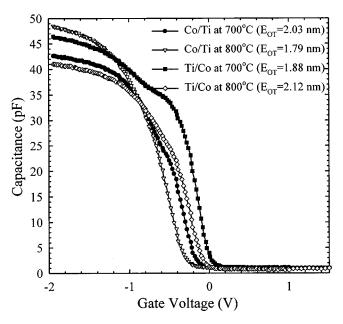

from independent targets by using a physical vapor deposition method. Direct thermal oxidation was carried out at 700 or 800 °C in diluted  $O_2$  ( $N_2/O_2=2/1$ ) gas for 5 min and annealed in N<sub>2</sub> ambient for 5 min to form CoTiO<sub>3</sub> films. A 5000 Å Al film was deposited on the wafer by a thermal coater to serve as the gate electrode. The gate of the metaloxide-semiconductor (MOS) capacitor was defined by lithography, and then the Al was etched by a wet etching solution. Finally, a 5000 Å Al film was also deposited on the back side of the wafers after stripping the oxide on the back side. X-ray diffraction (XRD) was used to identify the composition and the phase of these new metal-oxide films. The gate dielectrics of MOS capacitors with an area of 2.5  $\times 10^{-5}$  cm<sup>2</sup> were measured. The  $E_{\rm OT}$  (17.9–21.2 Å) of CoTiO<sub>3</sub> with a Si<sub>3</sub>N<sub>4</sub> buffered layer structure was obtained by high frequency capacitance-voltage (C-V) of 0.1 MHz at an operating range of -2-2 V in a strong accumulation

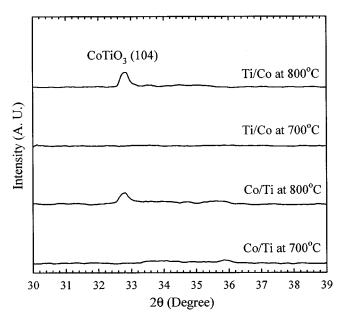

FIG. 1. XRD spectra of  $\text{CoTiO}_3$  films with various stack structures and temperatures.

a)Electronic mail: tschao@ndl.gov.tw

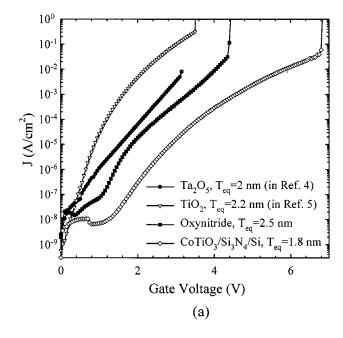

FIG. 2. J-V characteristics of (a) different gate dielectric material films with various equivalent oxide thicknesses and (b) CoTiO3 films with various stack structures and temperatures.

region without considering quantum mechanical effects. The physical thickness (~200 Å) was doubly checked by transmission electron microscopy to obtain the k value. The k value (36.8-43.6) is calculated by timing 3.9 to the physical thickness and dividing it by the  $E_{\rm OT}$ . The electrical properties and reliability characteristics of the metal oxide were measured by using an Hewlett-Packard 4156 semiconductor parameter analyzer.

Film crystallization and degradation during a back-end thermal process is a major concern for high-dielectricconstant metal-oxide materials. Figure 1 shows the resultant XRD spectra. From the results, Co/Ti and Ti/Co samples oxidized at either 700 or 800 °C are found to react with oxygen and form CoTiO<sub>3</sub> films as shown in Fig. 1. The sample oxidized at 800 °C has a stronger spectrum than that

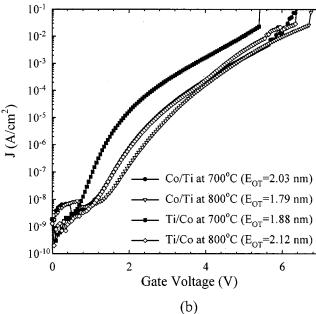

FIG. 3. High-frequency C-V curves of Co/Ti and Ti/Co films with 700 and 800 °C oxidation.

crystal peak is observed for oxidation at 700 °C, suggesting insufficient time for crystallization, as shown in Fig. 1. Figure 2(a) shows current density-voltage (J-V) curves for different gate dielectric films. With a thinner  $E_{\rm OT}$  of 1.8 nm, the CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si sample shows a lower leakage at low field and a higher breakdown voltage than those of Ta<sub>2</sub>O<sub>5</sub>  $(E_{\text{OT}} = 2.0 \text{ nm}, \text{ in Ref. 4}), \text{TiO}_2 (E_{\text{OT}} = 2.2 \text{ nm}, \text{ in Ref. 5}), \text{ or}$ oxynitride ( $E_{OT}$ = 2.5 nm). Figure 2(b) shows J-V curves of CoTiO<sub>3</sub> capacitors. Co/Ti and Ti/Co capacitors oxidized at 700 and 800 °C were compared. It is found that the Co/Ti capacitor oxidized at 800 °C demonstrates the highest breakdown voltage among all samples. In addition, the metal oxide oxidized at 800 °C exhibits a lower leakage current than that oxidized at 700 °C, implying that samples oxidized at 800 °C may exhibit CoTiO<sub>3</sub> crystallization.

The formation of an interfacial silicon oxide layer during sputtering and thermal processing makes it very difficult to

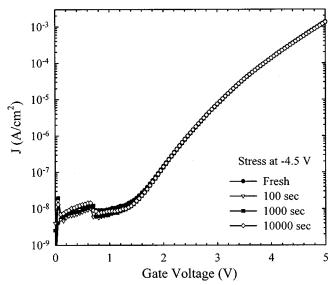

FIG. 4. SILC for Co/Ti capacitors with 800 °C oxidation.

of the sample oxidized at 700 °C. No noticeable CoTiO<sub>2</sub>

realize a high-k value. An effective method to solve this problem is to use a high quality silicon nitride buffer layer. Figure 3 shows the high frequency (C-V) curves for Co/Ti and Ti/Co capacitors oxidized at 700 and 800 °C. It is found that the Co/Ti stack capacitor exhibits a higher capacitance (k value) than the Ti/Co stack capacitors. Figure 4 shows the result after constant voltage stress at -4.5 V for Co/Ti stack capacitors. No significant stress induced leakage current (SILC) was observed for these four samples even after  $10^4$  s stressing.

In summary, we have demonstrated a high-k CoTiO<sub>3</sub> which is formed by direct oxidation of the sputtered Co/Ti and Ti/Co film. The CoTiO<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/Si stack by sputtering Co/Ti film oxidation shows higher k value and better electrical properties, such as low gate leakage current at low voltage operation, and high reliability after stressing. This high-k material with CoTiO<sub>3</sub> thus appears to be very promising for future ultralarge scale integrated devices.

The authors would like to express their appreciation to all the staff of the Semiconductor Research Center, National Chiao Tung University for their technique help. Financial support was from National Science Council Taiwan, Republic of China under Contract No. NSC89-2215-E009-306.

- <sup>1</sup> International Technology for Semiconductor Roadmap (Semiconductor Industry Association, San Jose, 1999).

- <sup>2</sup>S. C. Song, H. F. Luan, Y. Y. Chen, M. Gardner, J. Fulford, M. Allen, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. 373 (1998).

- <sup>3</sup> Albert Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, VLSI Tech. Symp. Dig. 135 (1999).

- <sup>4</sup>H. F. Luan, B. Z. Wu, L. G. Kang, B. Y. Kim, R. Vrtis, D. Roberts, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. 609 (1998).

- <sup>5</sup>Xin Guo, T. P. Ma, T. Tamagawa, and B. L. Halpern, Tech. Dig. Int. Electron Devices Meet. 377 (1998).

- <sup>6</sup>G. B. Alers, D. J. Werder, and Y. Chabal, Appl. Phys. Lett. **73**, 1517 (1998).

- <sup>7</sup>F. Chiu, J. Wang, J. Lee, and S. C. Wu, J. Appl. Phys. **81**, 6911 (1997).

- <sup>8</sup>T. M. Pan, T. F. Lei, T. S. Chao, K. L. Chang, and K. C. Hsieh, Electron. Solid-State Lett. 3, 433 (2000).