Home Search Collections Journals About Contact us My IOPscience

Analysis of Temperature Effects on High-Frequency Characteristics of RF Lateral-Diffused Metal–Oxide–Semiconductor Transistors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2008 Jpn. J. Appl. Phys. 47 2650

(http://iopscience.iop.org/1347-4065/47/4S/2650)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/04/2014 at 16:54

Please note that terms and conditions apply.

©2008 The Japan Society of Applied Physics

# Analysis of Temperature Effects on High-Frequency Characteristics of RF Lateral-Diffused Metal-Oxide-Semiconductor Transistors

Hsin-Hui Hu, Kun-Ming Chen<sup>1</sup>, Guo-Wei Huang<sup>1</sup>, Alex Chien<sup>2</sup>, Eric Cheng<sup>2</sup>, Yu-Chi Yang<sup>2</sup>, and Chun-Yen Chang

Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

(Received October 1, 2007; accepted November 16, 2007; published online April 25, 2008)

In this work, the effects of temperature on the DC and RF characteristics of lateral-diffused metal—oxide—semiconductor (LDMOS) transistors were studied. Devices with different layout structures were fabricated using a 40 V LDMOS process. The temperature coefficients of the threshold voltage and channel mobility are negative and their values are similar for devices with fishbone and ring structures. In addition, we found that both the cutoff frequency ( $f_T$ ) and the maximum oscillation frequency ( $f_{max}$ ) decrease with increasing temperature. The variations of  $f_T$  with different temperatures are not only affected by the change in transconductance but also affected by the drain resistance. Finally, the temperature behaviors of S-parameters were measured, and the ring structure showed less  $S_{22}$  variation with different temperatures than the fishbone structure. We extracted the model parameters of the devices to explain this observation. [DOI: 10.1143/JJAP.47.2650]

KEYWORDS: cutoff frequency, layout structure, LDMOS, maximum oscillation frequency, S-parameters, temperature

#### 1. Introduction

Lateral-diffused metal-oxide-semiconductor (LDMOS) transistor technology has played a predominant role in wireless base-station applications for frequencies ranging from 450 MHz to 2.7 GHz owing to its advantages in performance, cost, reliability, and power capability. 1) For high-power applications, temperature is an important issue. The cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{\text{max}})$  are critical figures of merit for evaluating the performance of RF transistors. For conventional MOS transistors in RF applications, the temperature effect was investigated by studying the temperature dependence of  $f_T$ , which is proportional to the transconductance.<sup>2)</sup> With an increase in temperature, the  $f_T$  and  $f_{max}$  have been shown to decrease. According to its structure, the parasitic drain resistance of the LDMOS becomes more important than that of the conventional MOS field-effect transistor (MOSFET) for the present drift region. However, in most of the studies, the effect of the parasitic resistance was not considered when analyzing the temperature effect on the device characteristics.<sup>2–4)</sup> By de-embedding the effect of the parasitic source and drain resistors from the measured S-parameters, the temperature dependence of the intrinsic  $f_T$  can be analyzed. Several researchers have investigated the effects of temperature on the reliability and dc performances of LDMOS transistors.<sup>5–7)</sup> However, the temperature effects on the highfrequency characteristics of LDMOS have seldom been addressed.

In this work, the DC and high-frequency characteristics of LDMOS transistors with different layout structures were studied at various temperatures. From the DC characteristics, we found that fishbone and ring structures have similar variations in threshold voltage and channel mobility for different temperatures. However, the measured S-parameters of the two structures show different temperature behaviors. Electrical parameters have been extracted to describe the temperature behavior of the transistors. In addition, the variations of  $f_{\rm T}$  and  $f_{\rm max}$  with different temperatures were also investigated. The LDMOS transistors with different

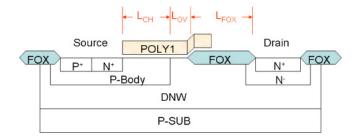

Fig. 1. (Color online) Schematic cross section of an LDMOS transistor.

layout structures have different drain resistances.<sup>8)</sup> In order to eliminate the effect of drain resistance, the intrinsic  $f_{\rm T}$  was extracted from the de-embedded S-parameters. The results of extrinsic and intrinsic  $f_{\rm T}$  variations with temperature are compared.

## 2. Experiments

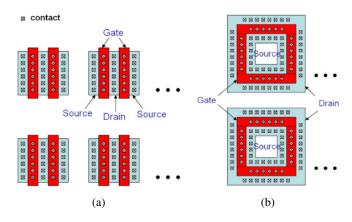

The RF LDMOS transistors used in this study were fabricated using a 40 V LDMOS process. The schematic cross section of the device is shown in Fig. 1. The drain region was extended under the field oxide (FOX) and consisted of a lightly doped N-well drift region and an Nregion with higher doping doses for on-resistance control. The source region and the p-body were tied together to eliminate extra surface bond wires to reduce the source inductance and improve the RF performance in a power amplifier configuration.<sup>9)</sup> The gate oxide thickness was 135 Å and the mask channel length ( $L_{CH}$ ) was 0.5  $\mu$ m. The drift length ( $L_{\text{Drift}} = L_{\text{OV}} + L_{\text{FOX}}$ ) was fixed at 3.6  $\mu$ m in this investigation. The LDMOS transistors were designed with two types of layout structures, as shown in Fig. 2. In the "fishbone" structure, all the gate fingers are divided into several subcells, in each of which 6 gate fingers are grouped together with a finger width  $(L_F)$  of  $10 \,\mu\text{m}$ . To achieve a lower on-resistance and a more compact device, we adopted a "ring" structure in the layout design. All the rings were arranged as a  $3 \times 3$  array in one device. In each ring, the source region was surrounded by the drain region, while the

<sup>&</sup>lt;sup>1</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>2</sup>United Microelectronics Corporation, Hsinchu 300, Taiwan

Fig. 2. (Color online) LDMOS layout structures: (a) fishbone and (b) ring.

gate was located between the source and the drain. The width of each gate ring, which is defined at the center of the channel region, was  $4 \times 10\,\mu\text{m}$ . To compare the performances of the fishbone and ring structures fairly, both structures had the same total channel width ( $W=360\,\mu\text{m}$ ). Additionally, the contact placement in the ring structure corresponded to that in the fishbone structure. Because the effective width of the drift region in the ring structure is larger than that in the fishbone structure, the ring structure has a lower drain resistance.

The DC characterization of the test devices was performed using an HP4156 semiconductor parameter analyzer. To characterize the high-frequency performance, the *S*-parameters were measured on-wafer from 0.1 to 10 GHz for different temperatures using an HP8510 network analyzer and then de-embedded by subtracting the OPEN dummy. Different control biases were applied from an HP4142B source measure unit.

#### 3. Results and Discussion

## 3.1 DC characteristics

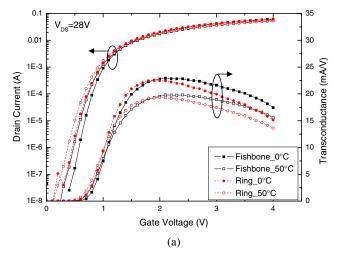

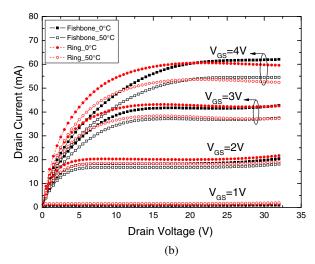

The DC characteristics of the LDMOS transistor with different layout structures at 0 and 50 °C are compared in Fig. 3. At low gate voltages ( $V_{GS} < 1 \text{ V}$ ), the transconductance  $(g_m)$  and drain current at 50 °C are higher those that at 0°C owing to the decrease in the threshold voltage. At high gate voltages, because the channel mobility decreases with increasing temperature, the  $g_{\rm m}$  and drain current at 50 °C become lower than that at 0 °C. In low- and medium-bias regions, the ring structure showed a higher drain current and  $g_m$  than the fishbone structure. For a high drain bias ( $V_{DS} = 28 \text{ V}$ ), the drain current and extrinsic  $g_{\rm m}$ had zero-temperature-coefficient biases near  $V_{GS} = 1.3 \,\mathrm{V}$ and  $V_{\rm GS}=1\,\rm V$ , respectively. The zero-temperature-coefficient bias point results from the negative temperature coefficients of both the effective mobility and threshold voltage.6)

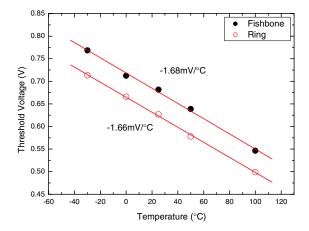

Figure 4 shows the threshold voltage plotted against temperature. The threshold voltage variations are -1.66 and  $-1.68 \, \text{mV}/^{\circ}\text{C}$  for the fishbone and ring structures, respectively. The values in the literature vary from -1 to  $-4 \, \text{mV}/\text{K}$  with the most frequently noted value of  $-2 \, \text{mV}/\text{K}$  for the conventional complementary MOS (CMOS). For the LDMOS transistors, the threshold voltage variation in our

Fig. 3. (Color online) (a) Subthreshold and (b) output characteristics of LDMOS transistors with different layout structures at 0 and  $50\,^{\circ}$ C.

Fig. 4. (Color online) Threshold voltage variation with temperature for different layout structures.

study is smaller than the proposed values of  $-5.2\,\text{mV}/^\circ\text{C}$ ,  $^{6)}$   $-3.2\,\text{mV/K}$ ,  $^{11)}$  and  $-2.8\,\text{mV}/^\circ\text{C}$ . This results from the lighter doping in the double-diffused channel.

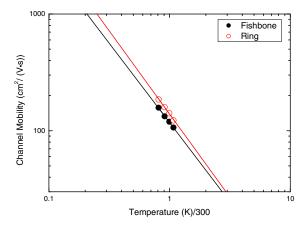

The extracted channel mobility for different temperatures is shown in Fig. 5. The LDMOS channel mobility was deducted from the first-order one-dimensional model in the

Fig. 5. (Color online) Temperature dependence of channel mobility for different layout structures.

linear mode.<sup>6)</sup> This method is applicable for low drain voltages. The temperature dependence of the channel mobility can be modeled as  $\mu = \mu_0 \times (T/T_0)^{-m}$ , where m = -1.35 for the fishbone structure and -1.36 for the ring structure. For intermediate inversion layer concentrations  $[N=(0.5-5)\times 10^{12}\,\mathrm{cm}^{-3}]$  at room temperature, the phonon-scattering-limited channel mobility has been observed to be dependent on N and T ( $\mu_{\rm ph} \propto T^{-n}N^{-1/\gamma}$ ), where  $\gamma = 3-6$  and  $n=1-1.5.^{13}$ ) Therefore, the mobility in our devices is dominated by the phonon scattering.

# 3.2 Cutoff frequency and maximum oscillation frequency

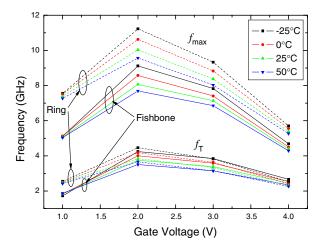

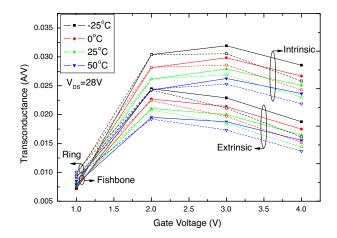

The cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{\text{max}})$  versus the gate voltage for the LDMOS transistors at various temperatures are shown in Fig. 6. We calculated the maximum stable gain/maximum available gain (MSG/MAG) and short-circuit current gain  $(h_{21})$  from the S-parameters. The  $f_{\rm T}$  and  $f_{\rm max}$  were determined to be the frequencies at which the current gain was 0 dB and the MAG was 0 dB, respectively. As shown in Fig. 6, the ring structure has better high-frequency performance than the fishbone structure owing to a lower drain resistance.<sup>8)</sup> In addition, both  $f_T$  and  $f_{max}$  decrease with increasing temperature for the two structures. The degradations of  $f_T$  and  $f_{max}$  are attributed to the lower  $g_{\rm m}$ , as shown in Fig. 7. The variations in  $f_T$  and intrinsic  $g_m$  are 17 and 20%, respectively at  $V_{\rm GS} = 2 \, \rm V$ , as temperature changes from -25 to  $50 \, ^{\circ} \rm C$ . Because the temperature dependence of  $f_{\text{max}}$  is also affected by the drain resistance  $(R_d)$  and drain-substrate junction capacitance  $(C_{idb})$ , the variation in  $f_{max}$  is approximately 15%. It should be noted that the  $f_T$  and  $g_m$  have zerotemperature-coefficient bias points near  $V_{GS} = 1 \text{ V}$ . In Fig. 7, at a higher gate voltage, both the intrinsic and extrinsic  $g_{\rm m}$  values of the ring structure are lower than those of the fishbone structure owing to the self-heating effect. Owing to the series resistance, the intrinsic  $g_{\rm m}$  for the two

Fig. 6. (Color online) Cutoff frequency and maximum oscillation frequency versus gate voltage at various temperatures.

Fig. 7. (Color online) Extrinsic and intrinsic transconductances versus gate voltage at various temperatures for different layout structures.

structures was higher than the extrinsic  $g_{\rm m}$ . The variation in both the intrinsic and extrinsic  $g_{\rm m}$  values are approximately 20% at  $V_{\rm GS}=2\,{\rm V}$  as temperature changes from -25 to 50 °C. However, the variation changes to 17% for the fishbone structure and 15% for the ring structure at a high gate voltage ( $V_{\rm GS}=4\,{\rm V}$ ). The higher gate voltage leads to severe surface scattering and lowers the effective mobility. As the gate voltage increases, the effect of surface scattering is more prominent resulting in smaller changes in  $g_{\rm m}$  and also in  $f_{\rm T}$  and  $f_{\rm max}$  with temperature.

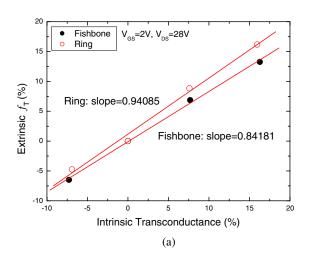

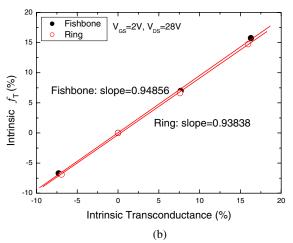

Figure 8 shows the variations in extrinsic and intrinsic  $f_{\rm T}$  values versus the variation in intrinsic  $g_{\rm m}$  at  $V_{\rm GS}=2\,{\rm V}$  when temperature changes from 25 °C. The usual approximate relation of extrinsic  $f_{\rm T}$  and intrinsic  $g_{\rm m}$  can be expressed as follows:  $^{14)}$

$$f_{\rm T} = \frac{g'_{\rm m0}}{2\pi \sqrt{(C'_{\rm gs} + C_{\rm gd})^2 \left(1 + \frac{r_{\rm d}}{R'_{\rm ds} \parallel R'_{\rm sub}}\right)^2 - (g'_{\rm m0}C'_{\rm gs}R'_{\rm gs} - C_{\rm gd})^2}},$$

(1)

where  $g'_{m0} = g_{m0}/(1 + g_{m0}R_s)$ . The extrinsic  $f_T$  in eq. (1) was extrapolated assuming a  $-20\,\mathrm{dB/decade}$  roll-off for the short-circuit current gain  $|h_{21}|$ .  $R_{gs}$  refers to the channel resistance and leads to an additional term related to the  $g_m$  in the denominator. The sign of this term in the denominator is negative, making the slope of the extrinsic  $f_T$  variation versus the intrinsic  $g_m$  variation larger than 1. This is contradictory to our measured results in Fig. 8(a). Moreover, in eq. (1), the small-signal equivalent circuit can be viewed as a dual-feedback circuit in which  $R_s$  is the local series—

series feedback element and  $C_{\rm gd}$  is the local shunt–shunt feedback element. <sup>14)</sup> Even though  $R_{\rm s}$  makes the extrinsic  $g_{\rm m}$  smaller than the intrinsic  $g_{\rm m}$  by a factor of  $1/(1+g_{\rm m}R_{\rm s})$ , it also decreases  $C_{\rm gs}$  and  $C_{\rm gd}$  by the same factor and thus should not affect  $f_{\rm T}$ .

In LDMOS, however, the effect of drain parasitic resistance is also important, which is ignored in eq. (1). Tasker and Hughes reported a more rigorous derivation for the short-circuit current gain of a FET that takes source and drain resistance into account:<sup>15)</sup>

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi \{ (C_{\rm gs} + C_{\rm gd}) \cdot [1 + (R_{\rm S} + R_{\rm d})/R_{\rm ds}] + C_{\rm gd} \cdot g_{\rm m} \cdot (R_{\rm S} + R_{\rm d}) \}},$$

(2)

According to eq. (2), the sign of the term related to the  $g_{\rm m}$  in the denominator is positive, making the slope of the  $f_{\rm T}$  variation versus the intrinsic  $g_{\rm m}$  variation smaller than 1. In Fig. 8(a), the extrinsic  $f_{\rm T}$  includes the effects of source and drain resistances and the values of the curve slope are smaller than 1. This might be attributed to the effect of  $(R_{\rm S}+R_{\rm d})$  being more prominent than the effect of  $R_{\rm gs}$ . Furthermore, the fishbone and ring structures we studied here have difference drain resistances, resulting in the distinct values of the curve slopes in Fig. 8(a). To eliminate

Fig. 8. (Color online) (a) Extrinsic  $f_T$  and (b) intrinsic  $f_T$  variations versus intrinsic transconductance variation when temperature changes from 25 °C.

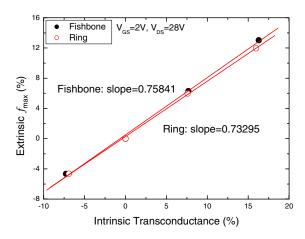

Fig. 9. (Color online) Extrinsic  $f_{\rm max}$  variation versus intrinsic transconductance variation when temperature changes from 25 °C.

the effect of parasitic resistance, the intrinsic  $f_{\rm T}$  was extrapolated after de-embedding the effect of the parasitic resistors from the measured S-parameters. As shown in Fig. 8(b), the curve slopes of the intrinsic  $f_{\rm T}$  variation versus the intrinsic  $g_{\rm m}$  variation for the fishbone and ring structures are quite similar (0.95 for fishbone and 0.94 for ring) and approach 1.

Figure 9 shows the variation in the extrinsic  $f_{\rm max}$  versus the variation in the intrinsic  $g_{\rm m}$  at  $V_{\rm GS}=2\,{\rm V}$  when temperature changes from 25 °C. The approximate relation of the extrinsic  $f_{\rm max}$  and intrinsic  $g_{\rm m}$  can be expressed as follows: <sup>16</sup>

$$f_{\rm max} \sim \frac{f_{\rm T}}{\sqrt{4g_{\rm DS}R_{\rm g} + 8\pi f_{\rm T}C_{\rm gd}(R_{\rm g} + \alpha R_{\rm d})}},$$

(3)

The intrinsic  $g_{\rm m}$  dependence of  $f_{\rm max}$  comes about through the  $f_{\rm T}$  we mentioned above. The positive relation of  $f_{\rm T}$  in the denominator results in a lower value for the curve slope in Fig. 9 than that in Fig. 8(a). In addition, the parasitic drain resistance in the denominator indicates that the  $R_{\rm d}$  has a larger effect on  $f_{\rm max}$ . Therefore, the ring structure, which has a lower drain parasitic resistance, shows more improvement on  $f_{\rm max}$  than  $f_{\rm T}$ .

#### 3.3 S-parameters characteristics

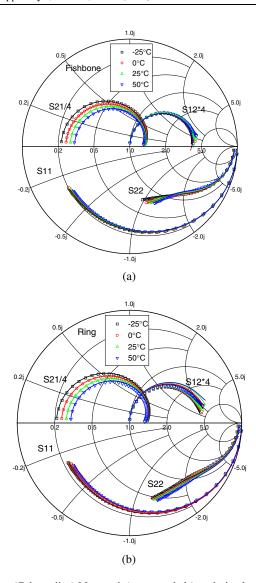

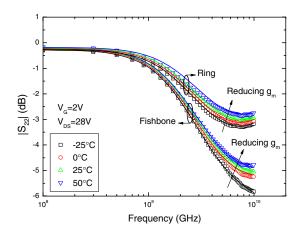

Figure 10 shows the measured and simulated S-parameters of the fishbone and ring structures at various temper-

Fig. 10. (Color online) Measured (open symbols) and simulated (solid line) *S*-parameters of transistors with (a) fishbone and (b) ring structures from 0.1 to 10 GHz.

atures. The transistors were measured at  $V_{\rm GS}=2\,\rm V$  and a drain voltage  $(V_{\rm DS})$  of 28 V for the maximum value of  $f_{\rm T}$ . In order to demonstrate the temperature dependence of the S-parameters, the model parameters of the small-signal equivalent circuit of the LDMOS transistors were extracted. The simulated results are also shown in Fig. 10. As illustrated in Fig. 10, the deviation of  $S_{11}$  with temperature is not marked. This suggests that the input impedance is affected by temperature slightly. Because the  $g_{\rm m}$  decreases with increasing temperature, both  $S_{21}$  and  $S_{22}$  change significantly. At low frequencies,  $S_{21}$  can be approximated by  $^{17}$

$$S_{21} = -2 \cdot g_{\mathrm{m}}' \cdot R_{\mathrm{L}} \cdot \frac{Z_{\mathrm{O}}}{Z_{\mathrm{O}} + R_{\mathrm{d}}},\tag{4}$$

where  $Z_{\rm O}=50\,\Omega$  and  $R_{\rm L}=R_{\rm DS}\parallel(R_{\rm d}+Z_{\rm O})$ . It is proportional to  $g_{\rm m}$ . However, at low frequencies,  $S_{12}=2sC'_{\rm gd}\cdot Z_{\rm O}$  is only related to the gate-to-drain capacitance  $(C_{\rm gd})$ . Therefore,  $S_{21}$  changed significantly owing to the decrease in  $g_{\rm m}$ , and  $S_{12}$  showed minor changes owing to the slight variation in  $C_{\rm gd}$  with increasing temperature. It is interesting that the temperature-induced variation in  $S_{22}$  in the ring

Fig. 11. (Color online) Measured (open symbols) and simulated (solid line)  $|S_{22}|$  of transistors for different layout structures from 0.1 to 10 GHz

structure is lower than that in the fishbone structure. Figure 11 shows the measured and simulated results of  $|S_{22}|$  for the fishbone and ring structures. The extracted  $R_{\rm d}$  and  $C_{\rm jdb}$  of the ring structure are  $7.8\,\Omega$  and  $149\,{\rm fF}$ , respectively, which are lower than those of the fishbone structure (the extracted  $R_{\rm d}$  and  $C_{\rm jdb}$  are  $18\,\Omega$  and  $244\,{\rm fF}$ , respectively). This is a possible reason for the lower  $S_{22}$  variation in the ring structure with different temperatures.

#### 4. Conclusions

The effects of temperature on the DC and high-frequency characteristics of RF LDMOS transistors were investigated in this study. The transconductance, threshold voltage, and channel mobility decrease with increasing temperature. The decrease in transconductance degrades the  $f_T$  and  $f_{max}$ at high temperatures. Owing to the higher drain resistance in the LDMOS transistors, the  $f_T$  is also affected by drain resistance. After de-embedding the effect of drain resistance, the temperature-induced  $f_T$  variation is almost proportional to the  $g_m$  variation. In addition, we found that the temperature dependence of  $f_{\text{max}}$  is also affected by the drain resistance and drain-substrate junction capacitance. Finally, we discussed the measured S-parameters at various temperatures. Because the LDMOS transistors with the ring structure have a lower drain resistance and a lower drain-substrate junction capacitance, the variation in  $S_{22}$ with temperature is smaller than that in the fishbone structure.

# Acknowledgements

The authors would like to thank the staff of UMC for their helpful comments and the staff of the High Frequency Technology Center in NDL for measurement support. This work was supported in part by the R.O.C.'s National Science Council through contract NSC96-2221-E-492-014.

- A. Wood, C. Dragon, and W. Burger: IEDM Tech. Dig., 1996, p. 87.

- S. M. Nam, B. J. Lee, S. H. Hong, C. G. Yu, J. T. Park, and H. K. Yu: Proc. Int. Conf. VLSI and CAD (ICVC), 1999, p. 174.

- 3) Y. S. Lin: Microwave Opt. Technol. Lett. 44 (2005) 180.

- J. G. Su, S. C. Woni, C. Y. Chang, K. Y. Chiu, T. Y. Huang, C. T. Ou, C. H. Kao, and C. J. Chao: Proc. IEEE Hong Kong Electron Devices Meet., 2000, p. 40.

- M. A. Belaïd, K. Ketata, K. Mourgues, M. Gares, M. Masmoudi, and J. Marcon: Microelectron. J. 38 (2007) 164.

- G. M. Dolny, G. E. Nostrand, and K. E. Hill: IEEE Trans. Electron Devices 39 (1992) 990.

- Z. Radivojevic, K. Andersson, J. A. Bielen, P. J. van der Wel, and J. Rantala: Microelectron. Reliab. 44 (2004) 963.

- H. H. Hu, K. M. Chen, G. W. Huang, C. Y. Chang, Y. C. Lu, Y. C. Yang, and E. Chen: Jpn. J. Appl. Phys. 46 (2007) 2032.

- F. M. Rotella, G. Ma, Z. Yu, and R. W. Dutton: IEEE Trans. Microwave Theory Tech. 48 (2000) 991.

- 10) I. M. Filanovsky, A. Allam, and S. T. Lim: Analog Integrat. Circuits

- Signal Process. 27 (2001) 227.

- Y. S. Koo, M. S. Kang, C. Choi, and C. An: J. Korean Phys. Soc. 39 (2001) 352.

- M. Kodama, T. Sugiyama, and T. Uesugi: Electron. Commun. Jpn., Part II 84 (2001) No. 5, 55.

- D. S. Jeon and D. E. Burk: IEEE Trans. Electron Devices 36 (1989) 1456.

- 14) Y. S. Lin: IEEE Trans. Electron Devices **52** (2005) 1442.

- 15) P. J. Tasker and B. Hughes: IEEE Electron Device Lett. 10 (1989)

- T. C. Lim and G. A. Armstronga: Solid-State Electron. 50 (2006) 774.

- S.-S. Lu, T.-W. Chen, H.-C. Chen, and C. Meng: IEEE Trans. Microwave Theory Tech. 49 (2001) 333.