Home Search Collections Journals About Contact us My IOPscience

High-Performance Solid-Phase Crystallized Polycrystalline Silicon Thin-Film Transistors with Floating-Channel Structure

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2008 Jpn. J. Appl. Phys. 47 3024 (http://iopscience.iop.org/1347-4065/47/4S/3024) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11 This content was downloaded on 25/04/2014 at 16:55

Please note that terms and conditions apply.

©2008 The Japan Society of Applied Physics

# High-Performance Solid-Phase Crystallized Polycrystalline Silicon Thin-Film Transistors with Floating-Channel Structure

Chia-Wen CHANG, Chih-Kang DENG, Che-Lun CHANG, Ta-Chuan LIAO, and Tan-Fu LEI

Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan

(Received September 4, 2007; accepted December 11, 2007; published online April 25, 2008)

High-performance solid-phase crystallized polycrystalline silicon thin-film transistors with a floating-channel active region (FC poly-Si TFTs) are proposed in this study. A high-quality poly-Si channel film accompanied by a larger grain size and fewer microstructural defects could be obtained. Compared with the conventional poly-Si TFTs (CN poly-Si TFTs), the fabricated FC poly-Si TFTs exhibit superior electrical characteristics, including lower threshold voltage, higher field-effect mobility, and lower trap state density. These electrical performance improvements could be attributed to the fact that the  $\alpha$ -Si film with a floating-channel structure can relieve the stress generated from the crystallization process accompanying the trap state density reduction and grain size enhancement. In addition, the FC poly-Si TFTs also exhibit improved hot-carrier stress immunity due to the reduced weak Si–H bonds from fewer grain boundaries in the poly-Si channel. Therefore, the proposed FC poly-Si TFTs can be easily fabricated by conventional solid-phase crystallization, and suitable for future high-performance flat-panel display applications. [DOI: 10.1143/JJAP.47.3024]

KEYWORDS: floating-channel structure, surface nucleation, solid-phase crystallization (SPC), thin-film transistor (TFT)

## 1. Introduction

In recent years, polycrystalline silicon thin-film transistors (poly-Si TFTs) have been widely used for active matrix liquid crystal displays (AMLCDs). High-performance and superior-reliability poly-Si TFTs have the potential to realize the integration of peripheral driving circuits and pixel switching elements on a single glass substrate.<sup>1,2)</sup> To fabricate poly-Si TFTs on an inexpensive glass substrate, low-temperature technology is required for realizing flatpanel displays (FPDs) owing to the maximum process temperature of being lower than 600 °C. The solid-phase crystallization (SPC) process is widely used for phase transformation from amorphous to polycrystalline due to its low fabrication cost and good grain-size uniformity. However, the electrical characteristics of SPC poly-Si TFTs are strongly correlated to the microstructure of poly-Si channel film. It is well known that the presence of a large number of grain boundaries and intragranular defects acting as scattering centers and midgap traps in the poly-Si film degrades the electrical properties of poly-Si TFTs.<sup>3,4)</sup> Therefore, the SPC process plays an important role in determining the device performance. Unfortunately, the traditional SPC process is an interface-nucleation mechanism generating too many nucleation sites at the amorphous silicon/underlying oxide  $(\alpha$ -Si/SiO<sub>2</sub>) interface, resulting in a smaller poly-Si grain size and many grain boundary defects.<sup>5,6)</sup> Various techniques have been employed to improve the device performance either by reducing the trap state density<sup>7,8)</sup> or increasing the grain size of SPC poly-Si film.<sup>9-12)</sup> The hydrogen plasma treatment is widely used to reduce the trap state density due to the passivation of trap states. Although hydrogen plasma treatment can improve the electrical performances, it is difficult to control the optimal processing time for satisfactory performance improvements. In addition, the hydrogenated poly-Si TFTs also suffer from a serious instability in their electrical characteristics under long-term electrical stress due to the easy breaking of weak Si-H bonds at the grain boundaries.<sup>13)</sup> Recently, many SPC processes associated with the surface-nucleation scheme were proposed to improve the microstructure of poly-Si film by utilizing oxygen doping at the  $\alpha$ -Si/SiO<sub>2</sub> interface.<sup>9–11)</sup> It has been known that oxygen atoms retard the crystallization process of an oxygen-implanted  $\alpha$ -Si film during solid-phase epitaxial regrowth.<sup>12)</sup> As interface nucleation is effectively suppressed by the incorporation of oxygen atoms at the  $\alpha$ -Si/SiO<sub>2</sub> interface, the nucleation process will initiate at another preferable nucleation site on the top free surface of the  $\alpha$ -Si film. Because of fewer nucleation sites at the top free surface of the  $\alpha$ -Si film, a larger poly-Si grain size can be obtained. However, these surface-nucleation methods mentioned previously require relatively complicated fabrication procedures, and they are not practical for TFT applications.

In this paper, we take advantage of the SPC surfacenucleation scheme proposed by Bo *et al.*,<sup>14)</sup> and then design the self-aligned formation of a floating channel structure without any additional sacrificial pattern to form the air gap. Experimental results also confirm that the grain size and trap state density of the floating-channel poly-Si film are markedly improved; moreover, relatively better electrical characteristics are also achieved. Therefore, the proposed fabrication procedure for floating-channel poly-Si TFT (FC poly-Si TFT) is very simple and low cost. It is also reproducible and compatible with existing poly-Si TFT manufacturing processes.

#### 2. Experimental Procedure

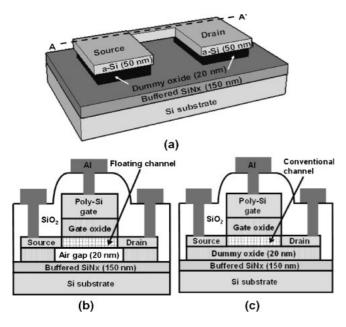

Figures 1(a) and 1(b) schematically depict bird's eye and cross-sectional views of the proposed FC poly-Si TFT. The fabrication processes of the FC poly-Si TFT are exhibited as follows. First, a 150 nm silicon nitride (Si<sub>3</sub>N<sub>4</sub>) layer, a 20 nm tetraethooxysilane (TEOS) oxide, and a 50 nm  $\alpha$ -Si film were successively deposited by low-pressure chemical vapor deposition (LPCVD) to serve as the buffered layer, dummy oxide, and channel film, respectively. After the individual  $\alpha$ -Si active regions were anisotropically patterned and defined, an isotropic wet etching was performed using buffer oxide etchant (BOE) solution with a constituent ratio of HF : NH<sub>4</sub>F = 7 : 1 to remove the dummy TEOS oxide to form the floating-channel  $\alpha$ -Si region, as shown in Fig. 1(a). The etching rates of BOE for dummy TEOS oxide and  $\alpha$ -Si

Fig. 1. (a) Bird's eye view of the FC poly-Si TFT. (b) Cross-sectional view of the FC poly-Si TFT along the AA' line shown in (a). (c) Cross-sectional view of the CN poly-Si TFT.

were 15 nm/s and 0.4 nm/min, respectively. Therefore, the dummy TEOS oxide was etched for 90s to make sure the floating-channel structure could be easily created between the large areas of source/drain pads. Subsequently, the  $\alpha$ -Si film with a floating-channel structure was recrystallized at 600 °C for 24 h in N<sub>2</sub> ambient for phase transformation from amorphous to polycrystalline. After RCA cleaning, a 100 nm TEOS oxide and a 150 nm poly-Si film were deposited to serve as the gate dielectric and gate electrode, respectively. A self-aligned phosphorous ion implantation was performed at dosage and energy values of  $5 \times 10^{15}$  and 15 keV, respectively. A 300 nm passivation SiO<sub>2</sub> layer was deposited by plasma-enhanced CVD (PECVD), followed by the realization of dopant activation at 600 °C for 12 h and the definition of contact holes. Finally, a 400 nm Al electrode was deposited and patterned. An NH<sub>3</sub> plasma treatment was performed at 350 °C for 30 min after the Al electrode formation. For comparison, conventional poly-Si TFT (CN poly-Si TFT) without the removal of dummy TEOS oxide was also fabricated, as shown in Fig. 1(c). Therefore, the distinction between the Si atoms unbounded and bounded to the underlying dummy TEOS oxide could be easily observed from the poly-Si films with floating-channel and conventional structures, respectively.

### 3. Results and Discussion

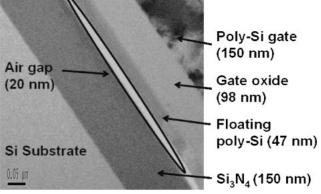

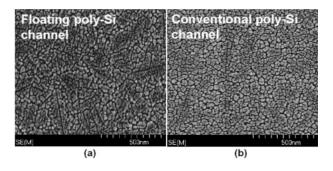

A cross-sectional transmission electron microscopy (TEM) image of the proposed FC poly-Si TFT structure is shown in Fig. 2. From the TEM image, it is clearly observed that the thicknesses of the floating-channel poly-Si film and the air gap are 47 and 20 nm, respectively. Thus, there really exists a floating-channel poly-Si film on the air gap. SEM images of poly-Si films used in the FC poly-Si TFT and CN poly-Si TFT after Secco etching are shown in Figs. 3(a) and 3(b), respectively. These images obviously show that the average grain sizes of poly-Si films for the FC poly-Si TFT and CN poly-Si TFT are approximately 150 and 50 nm,

C.-W. CHANG et al.

Fig. 2. Cross-sectional TEM image of the FC poly-Si TFT.

Fig. 3. SEM images of poly-Si films used in (a) the FC poly-Si TFT and (b) the CN poly-Si TFT, after Secco etching.

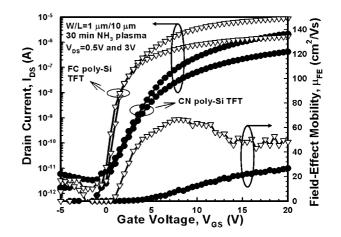

Fig. 4. Transfer characteristics and the extracted field-effect mobility of the FC and CN poly-Si TFTs with dimensions of  $W/L = 1 \,\mu m/10 \,\mu m$ .

respectively. The result indicates that a better polycrystalline structure with larger grain size and fewer intragranular defects can be obtained in the floating-channel poly-Si film.

Figure 4 presents the transfer characteristics  $(I_{DS}-V_{GS})$  of the FC poly-Si TFT and CN poly-Si TFT. The measurements are performed at two different drain voltages of  $V_{DS} = 0.5$ and 3 V. The drawn channel width (*W*) and channel length (*L*) are 1 and 10 µm, respectively. The parameters of the devices, including the threshold voltage ( $V_{TH}$ ), field-effect mobility ( $\mu_{FE}$ ), and subthreshold swing (SS), are extracted at  $V_{DS} = 0.5$  V, whereas the maximum on-state driving current ( $I_{ON}$ ) is defined at  $V_{DS} = 3$  V. The ON/OFF current ratio ( $I_{ON}/I_{OFF}$ ) is defined as the ratio of the maximum on-state driving current to the minimum off-state leakage current

Table I. Comparison of device characteristics for the FC and CN poly-Si TFTs with dimensions of  $W/L = 1 \,\mu\text{m}/10 \,\mu\text{m}$ .

|                                              | FC poly-Si<br>TFT   | CN poly-Si<br>TFT   |

|----------------------------------------------|---------------------|---------------------|

| Threshold voltage (V)                        | 1.62                | 6                   |

| Subthreshold swing (mV/dec)                  | 264                 | 971                 |

| Field-effect mobility $(cm^2 V^{-1} s^{-1})$ | 66.9                | 21.1                |

| Maximum on-state current (A)                 | $8.9 	imes 10^{-6}$ | $1.5 	imes 10^{-6}$ |

| ON/OFF current ratio                         | $5.8 	imes 10^6$    | $6.8 	imes 10^5$    |

at  $V_{\rm DS} = 3$  V. The threshold voltage is defined as the gate voltage required to achieve a normalized drain current of  $I_{\rm DS} = (W/L) \times 100$  nA at  $V_{\rm DS} = 0.5$  V. The measured and extracted device parameters of the FC poly-Si TFT and CN poly-Si TFT are summarized in Table I.

Accordingly, the electrical properties of the FC poly-Si TFT are significantly improved compared with those of the CN poly-Si TFT. The threshold voltage and subthreshold swing of the FC poly-Si TFT are 1.62 V and 264 mV/dec, whereas the CN poly-Si TFT has values of 6 V and 971 mV/ dec, respectively. The threshold voltage and subthreshold swing of the FC poly-Si TFT are found to be superior to those of the CN poly-Si TFT. Some studies indicated that the silicon dangling bonds originating from the deep trap states have energy states near the middle of the silicon bandgap, greatly affecting the threshold voltage and subthreshold swing.<sup>3)</sup> The floating-channel poly-Si film with the surfacenucleation scheme can improve the poly-Si crystallinity with fewer trap states at the grain boundaries. In addition, the maximum on-state driving current and ON/OFF current ratio of the FC poly-Si TFTs are better than those of the CN poly-Si TFT. The FC poly-Si TFT exhibits approximately one order of magnitude enhancement in the maximum onstate driving current compared with the CN poly-Si TFT at  $V_{\rm GS} = 20$  V and  $V_{\rm DS} = 3$  V. Moreover, the ON/OFF current ratio of the FC poly-Si TFT is about eight times larger than that of the CN poly-Si TFT. The result suggests that there must be larger poly-Si grains existing in the floating-channel poly-Si film, and thereby the subthreshold and on-state characteristics can be significantly improved.

Figure 4 also shows the field-effect mobility versus gate voltage for the FC and CN poly-Si TFTs. The field-effect mobility is calculated from the transconductance at  $V_{\rm DS} = 0.5$  V. As can be seen, the maximum field-effect mobility of the FC poly-Si TFT is around three times higher than that of the CN poly-Si TFT. Note that the strain bonds associated with the tail states near the silicon band edge in the poly-Si film, and at the gate oxide/poly-Si interface greatly affect the field-effect mobility. The improvement of field-effect mobility could be attributed to the enhancement of grain size and the reduction of grain boundaries, thereby leading to a better poly-Si grain crystallinity in the floating-channel poly-Si film.

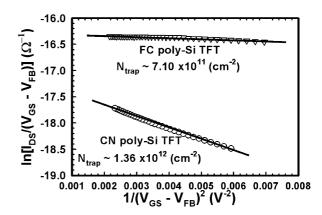

To verify the effect of poly-Si grain enhancement, the effective trap state density  $(N_{\rm trap})$  was extracted from the square root of the slope of the  $\ln[(I_{\rm DS}/(V_{\rm GS} - V_{\rm FB})]$  versus  $1/(V_{\rm GS} - V_{\rm FB})^2$  plots according to the grain-boundary trapping model proposed by Levinson *et al.*<sup>15)</sup> Figure 5 shows the  $\ln[(I_{\rm DS}/(V_{\rm GS} - V_{\rm FB})]$  versus  $1/(V_{\rm GS} - V_{\rm FB})^2$  characteristics at  $V_{\rm DS} = 0.5$  V and a high gate voltage for the FC and

Fig. 5. Plot of  $\ln[(I_{DS}/(V_{GS} - V_{FB})]$  vs  $1/(V_{GS} - V_{FB})^2$  and the extracted effective trap state density ( $N_{rap}$ ) for the FC and CN poly-Si TFTs.  $I_{DS}$  was measured at  $V_{DS} = 0.5$  V.

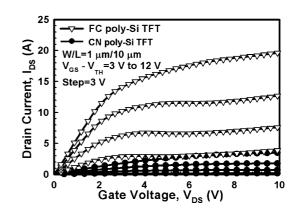

Fig. 6. Output characteristics of the FC and CN poly-Si TFTs with dimensions of  $W/L = 1 \,\mu m/10 \,\mu m$ .

CN poly-Si TFTs. It can be found that the FC poly-Si TFT exhibits a  $N_{\text{trap}}$  of  $7.1 \times 10^{11} \text{ cm}^{-2}$ , whereas the CN poly-Si TFT possesses a  $N_{\text{trap}}$  of  $1.36 \times 10^{12} \text{ cm}^{-2}$ . This result further confirms that the floating-channel poly-Si film has much fewer grain boundaries and microstructure defects than the conventional poly-Si film due to the enlarged grain size.

Figure 6 shows the output characteristics  $(I_{DS}-V_{DS})$  of the FC and CN poly-Si TFTs. As can be seen, the FC poly-Si TFT exhibits a great enhancement in the driving current at  $V_{DS} = 10$  V and common-gate driving voltages of  $V_{GS} - V_{TH} = 3$ , 6, 9, and 12 V. The improvement can be attributed to the field-effect mobility and threshold voltage of the FC poly-Si TFT being higher and lower than those of the CN poly-Si TFT.

These electrical performance improvements strongly related to the crystallinity of poly-Si film could be qualitatively explained as follows. While using the conventional SPC process with the interface-nucleation scheme to crystallize  $\alpha$ -Si into poly-Si, the rearrangement of interfacial Si atoms and volume contraction of bulk Si film induce tensile stress at the Si film/underlying oxide interface. Hence, a large number of crystalline defects, such as microtwins and dislocations, are generated to relieve the tensile stress. Following, numerous nucleation sites could be produced to result in smaller poly-Si grain size.<sup>11,14</sup> Nevertheless, in the case of poly-Si film with a floating-channel structure in this work, the removal of underlying dummy

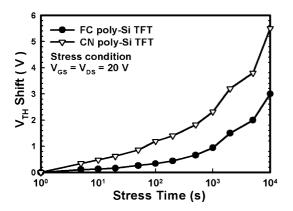

Fig. 7. Variation of threshold voltage versus hot-carrier stress time for the FC and CN poly-Si TFTs.

TEOS oxide makes the silicon atoms barely bound. As a result, the stress formed during the crystallization process could be easily relieved from the free Si surface pursing for fewer nucleation sites, thereby yielding good-quality poly-Si film with lower trap state density and larger poly-Si grain size.

Additionally, hot-carrier stress analysis was applied to investigate the device reliability. The poly-Si TFT devices were bias-stressed at  $V_{\rm DS} = 20 \,\text{V}$  and  $V_{\rm GS} = 20 \,\text{V}$  for  $10^4 \,\text{s}$ to examine the hot-carrier stress immunity. The thresholdvoltage shifts over hot-carrier stressing time for the FC and CN poly-Si TFTs are shown in Fig. 7. The threshold-voltage shift is defined as  $V_{\text{TH,stressed}} - V_{\text{TH,initial}}$ , where  $V_{\text{TH,initial}}$  and  $V_{\text{TH.stressed}}$  represent the measured values before and after stress application. Hot-carrier multiplication occurring on the drain side of poly-Si TFT causes the degradation of threshold voltage. The poly-Si TFT with a floating-channel structure shows less degradation in threshold voltage. Notably, the variation of threshold voltage of the FC poly-Si TFT after a stress time of 10<sup>4</sup> s is found to be 3 V, which is superior to that of the CN poly-Si TFT (5.4 V). It has been reported that the degradations of threshold voltage caused by hot-carrier stress could be attributed to two reasons: the generation of interface states at the gate oxide/poly-Si interface and the formation of deep trap states originating from the broken weak Si–H bonds at the grain boundaries.<sup>13)</sup> The result indicates that the floating-channel poly-Si film crystallized by SPC is formed with larger grain size accompanied by fewer grain boundaries, exhibiting an improved hot-carrier endurance.

#### 4. Conclusions

In this study, we have demonstrated that the  $\alpha$ -Si film with a floating-channel structure crystallized by a solid-phase

crystallization process exhibits a better Si grain crystallinity. Poly-Si TFT with the self-aligned formation of the floatingchannel active region is firstly proposed. The electrical characteristics, including the threshold voltage, subthreshold swing, field-effect mobility, trap state density, and ON/OFF current ratio, are significantly improved using solid-phase crystallized floating-channel poly-Si film. Superior trap state density and field-effec mobility further confirm that poly-Si with good crystallinity, larger grain size, and fewer microstructural defects can be realized in the floating-channel structure. In addition, the FC poly-Si TFTs also present higher immunity against the hot-carrier stress owing to the larger poly-Si grain size with fewer grain boundary defects. Therefore, the proposed FC poly-Si TFTs are not only compatible with conventional fabrication processes but also possess superior electrical properties for large flat-panel display applications.

### Acknowledgements

The authors would like to acknowledge the apparatus support from National Nano Device Laboratories and the Nano Facility Center of the National Chiao-Tung University, and the financial support from the National Science Council, Taiwan, under contact no. NSC 96-2221-E-009-188.

- 1) H. Oshima and S. Morozumi: IEDM Tech. Dig., 1989, p. 157.

- 2) Y. Oano: J. Soc. Inf. Disp. 9 (2001) 169.

- 3) I. W. Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis, and A. Chiang: IEEE Electron Device Lett. **12** (1991) 181.

- G. K. Guist and T. W. Sigmon: IEEE Trans. Electron Devices 45 (1998) 925.

- 5) A. T. Voutsas and M. K. Hatalis: J. Electrochem. Soc. 140 (1993) 871.

- E. Adachi, T. Aoyama, N. Konishi, T. Suzuki, Y. Okajima, and K. Miyata: Jpn. J. Appl. Phys. 27 (1988) 1809.

- 7) Y. S. Lee, H. Y. Lin, T. F. Lei, T. Y. Huang, T. C. Chang, and C. Y. Chang: Jpn. J. Appl. Phys. **37** (1998) 3900.

- F. S. Wang, M. J. Tsai, and H. C. Cheng: IEEE Electron Device Lett. 16 (1995) 503.

- M. K. Ryu, S. M. Hwang, T. H. Kim, K. B. Kim, and S. H. Min: Appl. Phys. Lett. **71** (1997) 3063.

- M. K. Ryu, J. Y. Kwon, and K. B. Kim: Mater. Res. Soc. Symp. Proc. 621 (2000) Q6.3.1.

- I. W. Wu, A. Chiang, M. Fuse, L. Ovecoglu, and T. Y. Huang: J. Appl. Phys. 65 (1989) 4036.

- E. F. Kennedy, L. Csepregi, J. W. Mayer, and T. W. Sigmon: J. Appl. Phys. 48 (1977) 4241.

- 13) I. W. Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis, and A. Chiang: IEEE Electron Device Lett. 11 (1990) 167.

- 14) X. Z. Bo, N. Yao, S. R. Shieh, T. S. Duffy, and J. C. Sturm: J. Appl. Phys. 91 (2002) 2910.

- 15) J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider: J. Appl. Phys. 53 (1982) 1193.