SOLID-STATE ELECTRONICS

www.elsevier.com/locate/sse

Solid-State Electronics 52 (2008) 365-371

# High-performance top and bottom double-gate low-temperature poly-silicon thin film transistors fabricated by excimer laser crystallization

Chun-Chien Tsai <sup>a,\*</sup>, Yao-Jen Lee <sup>b</sup>, Jyh-Liang Wang <sup>a</sup>, Kai-Fang Wei <sup>a</sup>, I-Che Lee <sup>a</sup>, Chih-Chung Chen <sup>c</sup>, Huang-Chung Cheng <sup>a</sup>

a Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

b National Nano Device Laboratories, Hsinchu, Taiwan, ROC

c Chunghwa Picture Tubes Ltd., Taoyuan, Taiwan, ROC

Available online 3 December 2007

The review of this paper was arranged by Guglielmo Fortunato

#### **Abstract**

In this work, high-performance low-temperature poly-silicon (LTPS) thin film transistors (TFTs) with double-gate (DG) structure and lateral grain growth have been demonstrated by excimer laser crystallization (ELC). Therefore, the DG TFTs with lateral silicon grains in the channel regions exhibited better current–voltage characteristics as compared with the conventional solid-phase crystallized (SPC) poly-Si double-gate TFTs or conventional ELC top-gate (TG) TFTs. The proposed ELC DG TFTs ( $W/L = 1.5/1.5 \,\mu$ m) had the field-effect-mobility exceeding 400 cm<sup>2</sup>/V s, on/off current ratio higher than 10<sup>8</sup>, superior short-channel characteristics and higher current drivability.

© 2007 Elsevier Ltd. All rights reserved.

Keywords: Excimer laser crystallization; Double-gate; Thin film transistor (TFT)

# 1. Introduction

Low-temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) fabricated by excimer laser crystal-lization (ELC) have been extensively studied for active matrix liquid crystal displays (AMLCDs), active matrix organic light emitting displays (AMOLEDs), and potential for three-dimension integrated circuits applications owing to their superior mobility performance [1–3]. In recent years, many efforts has been devoted to producing LTPS TFTs with silicon-on-insulator-like (SOI-like) performance by improving the channel material quality and advanced device structures of poly-Si TFTs for system-on-panel

E-mail address: cctsai.ee92g@nctu.edu.tw (C.-C. Tsai).

applications [4–7]. Double-gate (DG) structure is expected to be the alternative device structure for the ultimate highperformance ideal metal oxide semiconductor field-effect transistors (MOSFETs). These devices possess the potential advantages of excellent control of short-channel effects (SCE), drain-induced-barrier-lowering (DIBL), larger on/ off current ratio, and higher channel conductivity [8-17]. If this advanced structure is applied to polycrystalline-Si, the performance of TFTs will be also improved. From the perspective of improving channel quality, excimer laser crystallization (ELC) seems to be the most promising method at this moment for its great potential in mass production and high quality silicon grains without damage to glass substrates. Although large grains can be attained in the super lateral growth (SLG) regime by ELC, many fine grains still spread between these large grains due to the narrow process window for producing large grain poly-Si

<sup>\*</sup> Corresponding author. Tel.: +886 3 5712121x54218; fax: +886 3 5738343

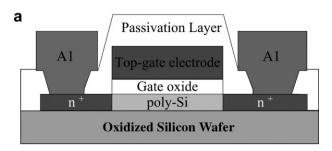

Fig. 1. The schematic cross-sectional view of the different poly-Si TFT devices. (a) Conventional *n*-channel top-gate TFT and (b) *n*-channel DG TFT.

[18,19]. Consequently, non-uniform and randomly distributed poly-Si grains will result in large variation of TFT performance when the laser energy density is controlled in the SLG regime, especially for small-dimension TFTs [20,21]. Thus, many laser crystallization methods have been proposed to produce large grains with uniformly grain size distribution, including SLS [22,23], grain filters method [24], capping the reflective or anti-reflective layer [25], phase-modulated ELC [26], dual beam ELA [27], double-pulsed laser annealing [28,29], selectively floating a-Si active layer [30], continuous-wave laser lateral crystallization [31,32], selectively enlarging laser crystallization [33,34], and so on. However, some of them need complex fabrication process or not readily be attached to the existing excimer laser annealing systems.

In this letter, high-performance double-gate LTPS TFTs with a simple excimer laser crystallization method have been demonstrated. Because of the double-gate operation mode and lateral silicon grains formed in the channel region, the devices have a high driving current, steeper subthreshold slope, superior short-channel effect immunity, and suppression of the floating-body effect. Moreover, not only the fabrication process steps are highly compatible

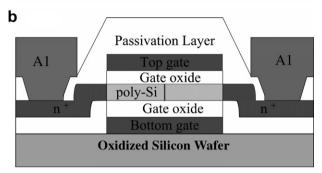

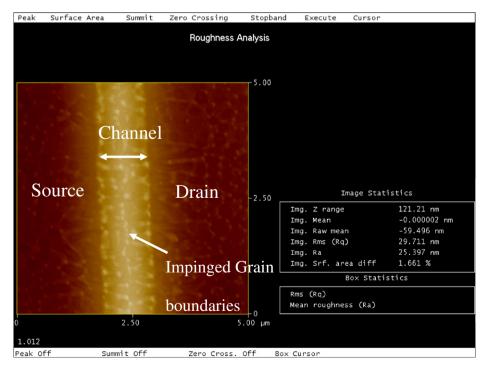

Fig. 2. (a)-(d) The key fabrication processes and (e) the cross-sectional SEM graph of proposed excimer-laser-crystallized double-gate LTPS TFTs.

with the conventional commercial a-Si TFTs but also the uniformity of device performance can be further improved.

#### 2. Device fabrication

For the sake of simple analysis and comparison, a schematic cross-sectional view of the n-channel double-gate poly-Si TFT is shown in Fig. 1b along with the conventional ELC top-gate TFT, as shown in Fig. 1a. The maximum process temperature of n-channel LTPS TFTs fabrication is 600 °C for the dopant activation by furnace annealing. Fig. 2 displays the key fabrication steps for the proposed double-gate short-channel LTPS TFTs structure crystallized with excimer laser annealing. At first, a 1000 Å-thick phosphorus-doped poly silicon layer was deposited by low-pressure chemical vapour deposition (LPCVD) at 550 °C on silicon wafer with oxide thickness of 1 um. After defining the bottom-gate region, a 1000 Åthick tetraethyl orthosilicate (TEOS) bottom-gate oxide layer was deposited by plasma-enhanced chemical vapour deposition (PECVD) at 550 C following a 1000 Å-thick a-Si layer deposited by pyrolysis of pure silane (SiH<sub>4</sub>) using LPCVD at 550 °C. After standard RCA clean process, the samples were then subjected to 248 nm KrF (Lambda Physik Excimer Laser LPX 210i) excimer laser crystallization (ELC). During the laser irradiation, the samples were located on a substrate in a vacuum chamber pumped down to 10<sup>-3</sup> Torr and substrate was maintained at room temperature. The laser beam was homogenized into a semigaussian shape in the short axis and a flat-top shape in the long axis. The number of laser shots per area was 20 (i.e. 95% overlapping) and laser energy density was varied.

A scanning electron microscopy (SEM) (S4700, Hitachi) is used to get the surface micrograph of poly-Si thin films after Secco-etch. After laser crystallization, the poly-Si active layers were etched to define the active channel region, and a 1000 Å-thick TEOS top-gate oxide was subsequently deposited. Poly-Si layer was deposited by LPCVD for formation of the top-gate electrode at 550 °C. Then, the poly-Si thin films were etched by RIE to form top-gate electrodes and a phosphorous ion implantation with dose of  $5\times10^{15}\,\mathrm{cm}^{-2}$  was carried out to form source and drain regions. Next, a TEOS passivation oxide layer was deposited by PECVD and the implanted dopants were activated by thermal annealing at 600 °C for 12 h. Contact holes opening and metallization were carried out to complete the fabrication of DG TFTs. Then, a 30-min sintering process was performed in N<sub>2</sub> ambient at 400 °C to reduce the contact series resistance of the source and drain electrodes. Finally, LTPS TFTs were passivated by 2-h NH<sub>3</sub> plasma treatment to further improve the device performance. Fig. 2e was the cross-sectional SEM graph of the completed excimer-laser-crystallized double-gate LTPS TFTs. For comparison, the conventional SPC DG TFTs and conventional ELC TG ones with using the super lateral growth (SLG) laser annealing condition were also fabricated in the same run.

After TFTs formation, an automatic measurement system that combines IBM PC/AT, semiconductor parameter analyzer (4156C, Agilent Technologies) and a probe station were used to measure the I-V characteristics. The threshold voltage was defined as the gate voltage required to achieve a normalized drain current of  $Ids = (W/L) \times 10^{-8}$  A at Vds = 0.1 V. The field-effect mobility and subthreshold

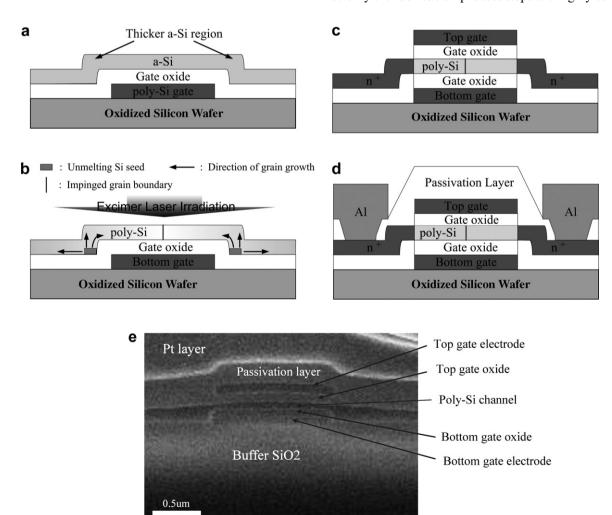

Fig. 3. AFM images of poly-Si thin film with bottom-gate structure after laser irradiation.

swing were extracted at Vds = 0.1 V, and the  $I_{\rm on}/I_{\rm off}$  current ratio was defined at Vds = 3 V. An analytical transmission electron microscopy (TEM) (JEM-2000FX, JEOL Ltd.) was employed to analyze the microstructure of poly-Si films and the device structure of TFTs. Cross-sectional TEM samples were prepared by focused-ion-beam (FIB) technique (Nova 200, FEI Company).

#### 3. Results and discussion

Fig. 2b shows the schematic illustration of lateral grain growth mechanism using plateau structure of a-Si thin film with excimer laser crystallization. When the excimer laser irradiation is applied on the a-Si thin film, the applied laser energy density is controlled to completely melt the thin region of a-Si film in the channel region. Since the laser energy density is almost uniform in a local region, if the thickness of thick region of a-Si film near the edges of bottom-gate is thick enough, the thick region of a-Si film is partially melted, and a lot of un-melting solid seeds remain near the edges of bottom-gate electrode. As a result, a lateral temperature gradient can be produced between the local thin and thick regions of a-Si film, and grains will grow laterally towards the complete melting region from the un-melting solid seeds. Therefore, the lateral grain growth can be artificially controlled in the channel region of DG TFTs and only one grain boundary perpendicular to the direction of current flow is formed in the middle of the channel region. Atomic force microscopy (AFM) analvsis is used to investigate the surface morphology of silicon thin film after laser crystallization. Fig. 3 exhibits that the ridge and hillock occur at the grain boundaries located at the center of channel where two grains collide due to the freezing of capillary waves excited in the melting silicon during laser crystallization [35]. The protruded grain boundaries will cause severe gate leakage and thicker gate dielectric must be integrated into poly-Si TFTs for better reliability.

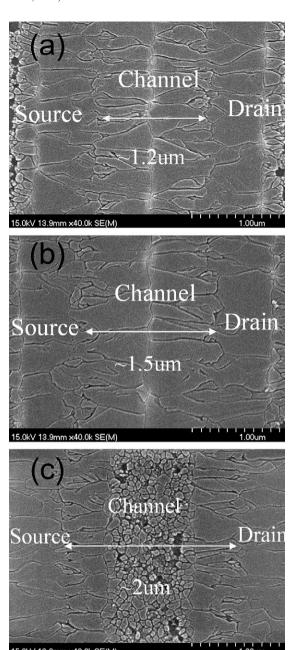

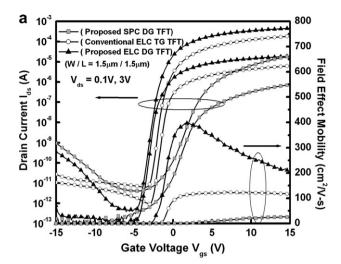

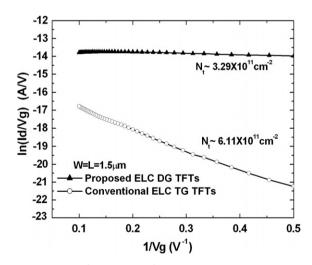

In order to investigate the relationship between laser energy density and length of lateral grain growth, the channel length was adjusted to laser energy density of 450 mJ/ cm<sup>2</sup> and laser shot number of 1 shot. Fig. 4a–c show the SEM graphs of poly-Si thin films irradiated by excimer laser in which the device channel length was 1.2, 1.5, 2 μm, respectively. As the device channel length was less than 1.5 µm, there were always two columns of longitudinal grains colliding in the middle of channel region. Fig. 5 shows the typical transfer and output characteristics of proposed ELC DG LTPS TFT (Fig. 1b) and conventional SPC DG TFT and conventional ELC TG TFT (Fig. 1a) for  $W = L = 1.5 \,\mu\text{m}$ . The nominal mobility of the DG TFT was calculated from transconductance  $(g_m)$ , which we defined as a TG TFT of the same gate length and gate width with a 100 nm gate-SiO2 layer. Owing to both of the uniformly large transverse grains grown in the device channel region and double-gate operation mode, this proposed ELC DG TFT exhibits better electrical char-

Fig. 4. Scanning electron microscope micrographs of excimer laser crystallized poly-Si film with bottom-gate structure after Secco etch, in which the device channel length was 1.2, 1.5, 2  $\mu$ m, respectively.

acteristics, and Table 1 lists several important electrical characteristics of the there different TFTs. Via the top and bottom-gates connected together, the higher electron density in the channel region at on state and the channel is more efficiently modulated by both gate electrodes [36]. Obvious improvement in devices characteristics is obtained for ELC DG TFTs instead of ELC TG TFTs; field-effect-mobility increases from 129 to 396 cm²/V s. But the proposed ELC DG TFT has a high off-current under a large negative gate bias at the Vds = 3 V from the Id–Vg transfer characteristics. The large leakage current indicates that ELC DG TFTs suffer a higher lateral peak electric field

Fig. 5. *I–V* curves of proposed ELC DG TFT, conventional SPC DG TFT, and conventional ELC TG TFT. (a) Transfer characteristics. (b) Output characteristics.

than the ELC TG TFT [37]. If lightly-doped-drain (LDD) and gate-overlapped lightly-doped-drain (GOLDD) structures were applied to the ELC DG TFTs, the severe anomalous off-current could be relieved by reducing the lateral peak electric field in the drain region. In order to avoid the threshold voltage difference, the applied gate driving voltages in Fig. 5b are kept at constant values of |Vg-Vth| = 4, 8, 12 and 16 V, respectively. It is demonstrated that the ELC DG poly-Si TFTs exhibit higher driving capability due to both of the location-controlled silicon grains in the channel and double-gate operation mode. Take the |Vg-Vth| = 16 V as an example, the current drivability of ELC DG poly-Si TFTs is about two times as

large as that of an ELC TG poly-Si TFT and seventeen times as large as that of a SPC DG poly-Si TFT under the same bias condition. At higher gate voltages, however, the current ratio between these three devices decreases. The plausible reason is the self-heating effect due to the large driving current on the poor thermal conducting SiO<sub>2</sub> substrate. It also clearly shows that ELC DG poly-Si TFTs provide better current saturation characteristics than the other two TFTs. The superior short-channel characteristics and driving capability imply that the proposed ELC DG-TFT structure is more suitable for high-resolution AMLCDs, and AMOLEDs application.

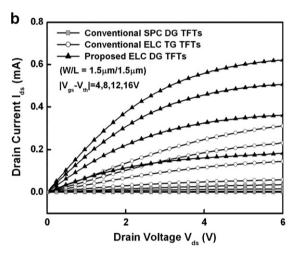

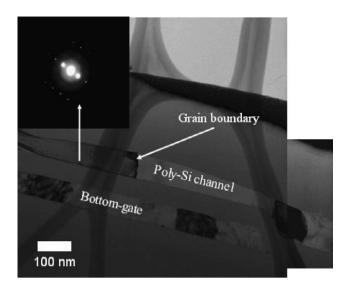

The grain boundary trap state densities (Nt) of the conventional TG and proposed DG poly-Si TFTs were estimated according to the modified Levinsons analysis [38,39]. The Nt was extracted from the slopes of  $\ln(I_{\rm D}/$  $V_{\rm GS}$ ) versus  $1/(V_{\rm GS})$ . Fig. 6 displays that ELC DG poly-Si TFT exhibits a smaller Nt of  $3.29 \times 10^{11}$  cm<sup>-2</sup> than that of conventional ELC TG TFT. This result implies that DG TFTs with lateral silicon grains possess better crystallinity and fewer microstructure defects which are also confirmed by cross-sectional TEM image of excimer laser crystallized poly-Si thin films with plateau structure shown in the Fig. 7. The inset of Fig. 7 shows the electron diffraction pattern of the one of lateral silicon grains in the channel regions above the bottom-gate electrode. The diffraction pattern reveals that the lateral silicon grain exhibits (123) orientation with respect to the normal direction of

Fig. 6. Plot of  $\ln(I_{\rm D}/V_{\rm GS})$  versus  $1/(V_{\rm GS})$  curves at  $V_{\rm DS}=0.1$  V and high  $V_{\rm GS}$  for DG and TG poly-Si TFTs.

Table 1

Measured electrical characteristics of ELC DG TFTs with lateral grain growth, SPC DG TFTs, and conventional ELC TG TFTs

| TFT structures ( $W = L = 1.5 \mu m$ ) | Threshold voltage (V) | Field-effect-mobility (cm <sup>2</sup> /V s) | Subthreshold swing (V/dec) | On/off current ratio |

|----------------------------------------|-----------------------|----------------------------------------------|----------------------------|----------------------|

| Conventional SPC double-gate TFT       | 2.92                  | 29.2                                         | 0.598                      | $4.82 \times 10^{6}$ |

| Conventional ELC top-gate TFT          | -1.17                 | 129                                          | 0.345                      | $4.32 \times 10^{7}$ |

| Proposed ELC double-gate TFT           | -2.48                 | 396                                          | 0.335                      | $9.21 \times 10^{8}$ |

Fig. 7. FIB-prepared cross-sectional TEM image of excimer laser crystallized poly-Si film with plateau structure.

the paper and the crystallinity within this lateral silicon grain is excellent attributed to the clear dot pattern.

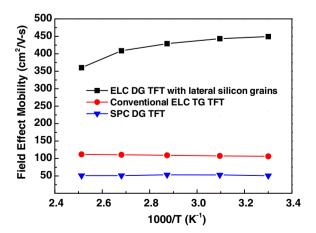

The dependence of field-effect mobility on temperature for ELC DG TFTs with lateral silicon grains, ELC TG TFTs with random silicon grains and SPC DG TFTs was investigated to study the electron-transport-scattering mechanism of poly-Si thin films, as shown in the Fig. 8. For ELC TG TFTs with random silicon grains, the electron field-effect-mobility increases as the temperature increases. Such positive temperature dependency of fieldeffect-mobility is attributed to the reduced grain boundary scattering where the probability of carrier transport over the grain boundary potential barrier height by thermionic emission increases [40]. On the other hand, negative dependency of field-effect-mobility for ELC DG TFTs with lateral silicon grains indicates lattice-phonon scattering is the dominate scattering mechanism because only one grain boundary perpendicular to the direction of current flow in the channel region. The field-effect-mobility of SPC DG

Fig. 8. The dependence of field-effect mobility on temperature for ELC DG TFTs with lateral silicon grains, ELC TG TFTs with random silicon grains and SPC DG TFTs.

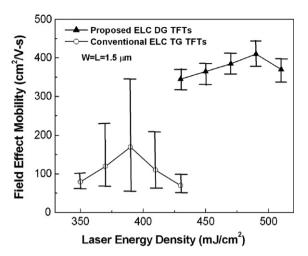

Fig. 9. Dependence of field-effect-mobility on applied laser energy density for ELC DG TFTs with lateral silicon grins and conventional ELC TG ones.

TFTs increase as first and then starts to decrease as the temperature increases, indicating grain-boundary scattering and lattice-phonon scattering compete with each other and dominate under different temperature.

Fig. 9 displays the dependence of field-effect mobility on laser energy densities for DG TFTs and conventional TG ones whose channel length is 1.5  $\mu$ m. Twenty TFTs were measured for each laser irradiation condition to investigate the device-to-device uniformity. Compared to the conventional ELC TG-TFTs, it was found that ELC DG-TFTs with lateral silicon grains exhibited smaller electrical deviation since the number of spontaneous small grains and grain boundaries were reduced and the uniformity of TFTs performance could be improved with artificially laterally-grown grains.

### 4. Conclusions

A novel high-performance DG LTPS TFTs have been fabricated by excimer laser crystallization. Poly-Si TFTs exhibit high field-effect-mobility of 400 cm²/V s and excellent short-channel characteristics because of the large transverse grains artificially grown in the channel region and double-gate structure for better gate controllability. In addition, the experimental results reveal a steeper subthreshold value, higher driving current, and excellent device uniformity in proposed TFTs. The ELC DG TFTs are therefore ideally suitable for future system-on-panel and three-dimensional integrated circuit applications.

# Acknowledgements

The authors thank the National Science Council of Taiwan for financial support of this research under Contract No. NSC 95-2221-E-009-252, and the Nano Facility Center (NFC) of National Chiao Tung University and National Nano Device Laboratories (NDL) for providing process equipment.

## References

- Kim HJ, Kim D, Lee JH, Kim IG, Moon GS, Huh JS, et al. in SID Symp Dig 1999;30:184-7.

- [2] Rajeswaran G, Itoh M, Boroson M, Barry S, Hatwar TK, Kahen KB, et al., in SID Tech Dig 2000;31:974–7.

- [3] Banerjee K, Souri SJ, Kapur P, Saraswat KC. Proceedings of the IEEE 2001;89:602–33.

- [4] Helen Y, Dassow R, Nerding M, Mourgues K, Raoult F, Kohler JR, et al. High mobility thin film transistors by Nd:YVO4-laser crystallization. Thin Solid Films 2001;383:143–6.

- [5] Meng Z, Wang M, Wong M. High performance low temperature metal-induced unilaterally crystallized polycrystalline silicon thin film transistors for system-on-panel applications. IEEE Trans. Electron Dev 2000;47:404–9.

- [6] Lin CW, Cheng LJ, Lu YL, Lee YS, Cheng HC. High performance low-temperature poly-Si TFTs crystallized by excimer laser irradiation with recessed-channel structure. IEEE Electron Dev Lett 2001;22:269–71.

- [7] Zhang S, Han R, Sin JKO, Chan M. Implementation and characterization of self-aligned double-gate TFT with thin channel and thick source/drain. IEEE Trans. Electron Dev 2002;49(5):718–24.

- [8] Farrah HR, Steinberg RF. Analysis of double-gate thin-film transistor. IEEE Trans. Electron Dev 1967;14:69–74.

- [9] Hergenrother JM, Monroe D, Klemens FP, Kornblit A, Weber GR, Mansfield WM, et al. The vertical replacement-gate (VRG) MOS-FET: a 50-nm vertical MOSFET with lithography-independent gate length. in IEDM Tech Dig 1999:71–4.

- [10] Venkatesan S, Neudeck Gerold W, Pierret Robert F. Dual-gate operation and volume inversion in n-channel SO1 MOSFET's. IEEE Electron Dev Lett 1992;13:44-6.

- [11] Guarini KW, Solomon PM, Zhang Y, Chan KK, Jones EC, Cohen GM et al. Triple-self-aligned, planar double-gate MOSFETs: devices and circuits. in IEDM Tech Dig 2001:415–8.

- [12] Philip Wong HS, Chan Kevin K, Yuan Taur. Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel. in IEDM Tech Dig 1997:427–30.

- [13] Colinge JP, Gao MH, Romano-Rodriguez A, Maes H, Claeys C. Silicon-on-insulator Gate-all-around device, in IEDM Tech Dig 1990:595–8.

- [14] Tanaka T, Horie H, Ando S, Hijiya S. Analysis of P+ poly Si double-gate thin-film SOI MOSFETs, in IEDM Tech Dig 1991:683–6.

- [15] Hisamoto D, Lee WC, Kedzierski J, Anderson E, Takeuchi H, Asano K, et al. A Folded-channel MOSFET for deep-sub-tenth micron era, in IEDM Tech Dig 1998:1032–4.

- [16] Wann CH, Tu R, Yu B, Hu C. A comparative study of advanced MOSFET structures, in VLSI Symp Tech Dig 1996:32–3.

- [17] Taur Yuan. An analytical solution to a double-gate mosfet with undoped body. IEEE Electron Dev Lett 2000;21:245–7.

- [18] Im JS, Kim HJ, Thompson MO. Phase transformation mechanisms involved on excimer laser crystallization of amorphous silicon films. Appl Phys Lett 1993;63:1969–71.

- [19] Im JS, Kim HJ. On the super lateral growth phenomenon observed in excimer laser-induced crystallization of thin Si films. Appl Phys Lett 1994;64:2303–5.

- [20] Yamaguchi K. Modeling and characterization of polycrystallinesilicon thin-film transistors with a channel-length comparable to a grain size. J Appl Phys 2001;89:590–5.

- [21] Kimura M, Inoue S, Shimoda T, Eguchi T. Dependence of polycrystalline silicon thin-film transistor characteristics on the grain-boundary location. J Appl Phys 2001;89:596–600.

- [22] Sposili Robert S, Im James S. Sequential lateral solidification of thin silicon films on SiO<sub>2</sub>. Appl Phys Lett 1996;69:2864–6.

- [23] Crowder MA, Carey PG, Smith PM, Sposili RS, Cho HS, Im JS. Low-temperature single-crystal Si TFT's fabricated on Si films processed via sequential lateral solidification. IEEE Electron Dev Lett 1998:19:306–8.

- [24] van der Wilt PC, van Dijk BD, Bertens GJ, Ishihara R, Beenakker CIM. Formation of location-controlled crystalline islands using substrate- embedded seeds in excimer-laser crystallization of silicon films. Appl Phys Lett 2001;79:1819–21.

- [25] Mariucci L, Carluccio R, Pecora A, Foglietti V, Fortunato G, Legagneux P, et al. Lateral growth control in excimer laser crystallized polysilicon. Thin Solid Films 1999;337:137–42.

- [26] Oh CH, Ozawa M, Matsumura M. A novel phase-modulated excimer-laser crystallization method of silicon thin films. Jpn J Appl Phys Part 2 1998;37:L492–5.

- [27] Ishihara R, Burtsev A. Location control of large grain following excimer-laser melting of si thin-films. Jpn J Appl Phys Part 1 1998;37:1071–5.

- [28] Yamazaki K, Kudo T, Seike K, Ichishima D, Jin CG. Double-pulsed laser annealing system and polycrystallization with green DPSS laser, in AMLCD Tech Dig 2002:149–52.

- [29] Sakuragi S, Kudo T, Yamazaki K, Asano T. High field effect mobility poly-Si TFTs fabricated by advanced lateral crystal growth process using double-pulsed laser annealing system, In: Proceeding of the 12th international display workshops, 2005. p. 965–8.

- [30] Kim CH, Song IH, Nam WJ, Han MK. A poly-Si TFT fabricated by excimer laser recrystallization on floating active structure. IEEE Electron Dev Lett 2002;23:325–7.

- [31] Hara A, Takeuchi F, Sasaki N. Selective single-crystalline-silicon growth at the pre-defined active regions of TFTs on a glass by a scanning CW laser irradiation, in IEDM Tech Dig 2000:209–12.

- [32] Hara A, Takei M, Takeuchi F, Suga K, Yoshino K, Chida M, et al. High performance low temperature polycrystalline silicon thin film transistors on non-alkaline glass produced using diode pumped solid state continuous wave laser lateral crystallization. Jpn J Appl Phys Part 1 2004;43:1269–76.

- [33] Hatano M, Shiba T. Selectively enlarging laser crystallization technology for high and uniform performance poly-Si TFTs. in SID Tech Dig 2002:158–61.

- [34] Tai M, Hatano M, Yamaguchi S, Noda T, Park SK, Shiba T, et al. Performance of poly-Si TFTs fabricated by SELAX. IEEE Trans. Electron Dev 2004;51:934–9.

- [35] Fork DK, Anderson GB, Boyce JB, Johnson RI, Mei P. Capillary waves in pulsed excimer laser crystallized amorphous silicon. Appl Phys Lett 1996;68:2138–40.

- [36] Esseni David, Mastrapasqua Marco, Celler George K, Fiegna Claudio, Selmi Luca, Sangiorgi Enrico. An experimental study of mobility enhancement in ultrathin SOI transistors operated in doublegate mode. IEEE Trans Electron Dev 2003;50:802–8.

- [37] Zhang S, Han R, Sin JKO, Chan M. Reduction of off-current in selfaligned double-gate tft with mask-free symmetric LDD. IEEE Trans Electron Dev 2002;49(8):1490–2.

- [38] Levinson L, Shepherd FR, Scanlon PJ, Westwood WD, Este G, Rider M. Conductivity behavior in polycrystalline semiconductor thin film transistors. J Appl Phys 1982;53:1193–202.

- [39] Proano RE, Misage RS, Ast DG. Development and electrical properties of undoped polycrystalline silicon thin-film transistors. IEEE Trans Electron Dev 1989;36:1915–22.

- [40] Seto JY. The electrical properties of polycrystalline silicon films. J Appl Phys 1975;46:5247–54.