# High-Performance and High-Reliability 80-nm Gate-Length DTMOS with Indium Super Steep Retrograde Channel

Sun-Jay Chang, Chun-Yen Chang, Fellow, IEEE, Coming Chen, Tien-Sheng Chao, Member, IEEE, Yao-Jen Lee, and Tiao-Yuan Huang, Fellow, IEEE

Abstract— In this paper, we demonstrate for the first time a high-performance and high-reliability 80-nm gate-length dynamic threshold voltage MOSFET (DTMOS) using indium super steep retrograde channel implantation. Due to the steep indium super steep retrograde (In-SSR) dopant profile in the channel depletion region, the novel In-SSR DTMOS features a low  $V_{th}$  in the off-state suitable for low-voltage operation and a large body effect to fully exploit the DTMOS advantage simultaneously, which is not possible with conventional DTMOS. As a result, excellent 80-nm gate length transistor characteristics with drive current as high as 348  $\mu A/\mu m$  (off-state current 40 nA/ $\mu m$ ), a record-high Gm=1022mS/mm, and a subthreshold slope of 74 mV/dec, are achieved at 0.7 V operation. Moreover, the reduced body effects that have seriously undermined conventional DTMOS operation in narrow-width devices are alleviated in the In-SSR DTMOS, due to reduced indium dopant segregation. Finally, it was found for the first time that hot-carrier reliability is also improved in DTMOS-mode operation, especially for In-SSR DTMOS.

Index Terms—DTMOS, indium, super-steep-retrograde (SSR) channel.

# I. INTRODUCTION

A S MOSFETs scale to subquarter-micrometer regime and beyond, an effective way to improve subthreshold turn-off and to alleviate short-channel effects (SCEs) is to increase the substrate doping. A uniform increase in substrate doping, however, suffers from undesirable channel mobility reduction, junction capacitance increase, and high threshold voltage. To circumvent these shortcomings, MOSFETs with a retrograde channel profile have been proposed [1]. In a retrograde channel, the peak substrate doping is positioned beneath the surface, leaving a lightly doped surface channel region [2]. Super-steep-retrograde (SSR) channel, which features a

Manuscript received March 21, 2000; revised July 26, 2000. This work was supported in part by the National Science Council of the Republic of China under Contract NSC 89-2215-E-317-004.

- S.-J. Chang, C.-Y. Chang, and Y.-J. Lee are with the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R. O. C.

- C. Chen is with the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C., and also with the Technology Development Division, United Microelectronics Corporation, Hsinchu, Taiwan, R.O.C.

- T.-S. Chao is with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C., and also with the Department of Engineering and System Science, National Tsing Hua University, Hsinchu, Taiwan, R.O.C. (e-mail: tschao@ndl.gov.tw).

- T.-Y. Huang is with the Institute of Electronics, National Chiao Tung University and also with the National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(00)10404-6.

sharp transition from the lightly doped surface to the heavily doped substrate, has been proposed for transistors with channel length smaller than 0.1  $\mu$ m [3]–[5]. The SSR scheme allows the transistor to exhibit a high driving current characteristic of the lightly doped surface channel with a low surface impurity scattering, while also simultaneously preserving a good  $V_{th}$ -roll-off behavior due to a reduced channel depletion width which improves punchthrough control. Indium dopant with its low diffusion coefficient at elevated temperature is known to be an ideal candidate to form SSR profile for subquarter-micron nMOSFETs.

On the other hand, the power supply voltage,  $V_{DD}$ , is scaling down at a faster pace than threshold voltage scaling. This has resulted in current drive reduction and therefore speed degradation. To improve the current drive capability of MOSFETs at low supply voltage (e.g.,  $V_{DD} < 0.7 \text{ V}$ ), Assaderaghi et al. [6] proposed the use of **D**ynamic Threshold Voltage **MOS**FET (DTMOS) for ultralow voltage applications. By shorting the gate to the body, the  $V_{th}$  in DTMOS mode is reduced in the on-state to boost the current drive; while the device exhibits the normal  $V_{th}$  in the off-state to maintain a low stand-by power. The DTMOS scheme thus appears to be very promising for future low-power and high-speed circuit applications, since it improves the circuit speed without compromising the stand-by power. Previously reported DTMOS's, however, suffer from a small body-effect-factor ( $\gamma$ ) [7]. This is because the normal  $V_{th}$ suitable for low  $V_{DD}$  operation is usually too small to be compatible with a high substrate doping concentration, resulting in a low  $\gamma$ . A low  $\gamma$  prevents the DTMOS from enjoying a large  $V_{th}$ reduction in the on-state, thus minimizes its gain in on-state current-drive during DTMOS-mode operation [7]–[10]. Recently, we have proposed a new DTMOS using an SSR channel profile by indium implantation to overcome the above shortcomings [11]. In this paper, a comprehensive comparison of the In-SSR DTMOS and conventional BF<sub>2</sub>-DTMOS, with 80-nm channel length has been reported.

# II. EXPERIMENTAL

Devices with channel length down to 80 nm were fabricated on 8-in silicon wafers with resistivity of 15 to 25  $\Omega$ -cm. Wafers were processed using a conventional CMOS twin-well process flow. Shallow trench isolation (STI) was used for device isolation. To form SSR channel, a 150 keV indium channel implant with a dose of  $1 \times 10^{13}$  cm<sup>-2</sup> was conducted. Conventional

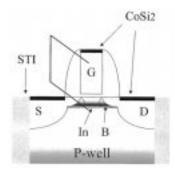

Fig. 1. Schematic of indium super steep retrograde (In-SSR) DTMOS.

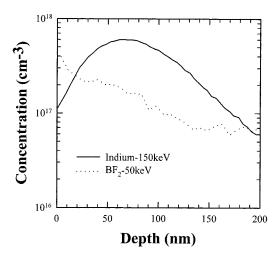

Fig. 2. SIMS profiles of In and B in the channel region.

devices with BF<sub>2</sub>-implant (at 50 keV,  $6 \times 10^{12}$  cm<sup>-2</sup>) were also processed in the same lot to serve as the control. A 2.6-nm gate oxide was grown using rapid thermal oxidation (RTO) at 850 °C, followed by the deposition of a 200-nm polysilicon gate. After gate patterning, a 20-nm offset-space (i.e., a narrow spacer) was used to reduce the gate-to-drain capacitance and suppress the short channel effects. Ultrashallow S/D extensions were then formed by a 4 keV As implant, followed by a boron pocket implant (i.e., 20 keV,  $1 \times 10^{13} \text{ cm}^{-2}$ , tilt angle  $20^{\circ}$ ). Afterwards, a 0.1  $\mu$ m sidewall spacer was formed. Then, a deep source/drain junction was formed by As ion implantation at 40 keV. Finally, wafers were annealed by rapid thermal processing (RTP) at 1000 °C for 20 s, followed by CoSi<sub>2</sub> salicidation. Wafers were then processed through a standard backend flow to completion. The device structure of 80-nm gate-length In-SSR DTMOS is shown in Fig. 1.

# III. RESULTS AND DISCUSSION

# A. Short-Channel In-SSR DTMOS Performance

The resultant channel profiles measured by the secondary ion mass spectroscopy (SIMS) for In-SSR and conventional BF<sub>2</sub>-implanted samples are shown in Fig. 2. The channel profiles are measured after all processing steps. Compared to BF<sub>2</sub>-implanted control, In-implanted sample exhibits a well-behaved Gaussian profile, in which the surface doping concentration is low while the concentration underneath the channel increases abruptly. The surface channel concentration is  $1 \times 10^{17}$  cm<sup>-3</sup>

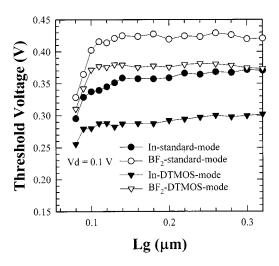

Fig. 3. Threshold voltage versus gate length (Lg) for In-SSR and BF $_2$ -implanted devices, both under standard- and DTMOS-modes. The threshold voltage is taken at  $Vd=0.1~\rm{V}.$

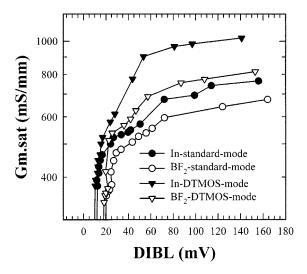

Fig. 4. The gm versus drain-induced-barrier-lowering (DIBL) for In-SSR and BF $_2$ -implanted devices, both under standard- and DTMOS-modes. The DIBL is taken between Vd=0.1 and  $0.7~\rm V$ .

for In-SSR sample, compared to  $4 \times 10^{17}$  cm<sup>-3</sup> for BF<sub>2</sub>-implanted control.  $V_{th}$  roll-off characteristics are shown in Fig. 3. The threshold voltage is deduced from  $Gm_{\text{max}}$  method at Vd = 0.1 V. It can be seen that short-channel effects are effectively suppressed in In-SSR DTMOS due to a smaller drain depletion layer. In addition, In-SSR devices also depict a larger  $V_{th}$  reduction under DTMOS mode, compared to BF<sub>2</sub> counterparts, due to a larger body effect factor  $(\gamma)$ . It has also been explicitly explained that SSR DTMOS shows the improved  $\gamma$  and hence performance [8]. It is worthy to note here that the amount of  $V_{th}$  reduction in 80-nm gate length devices are 40 mV for In-SSR DTMOS, compared to 18 mV for BF<sub>2</sub> DTMOS, despite the fact that the  $V_{th}$  of In SSR device is smaller than that of the BF<sub>2</sub> control. Fig. 4 compares the saturated transconductance (Gm.sat) versus drain-induced-barrier-lowering (DIBL) for In-SSR and BF2-implanted devices both under standard- and DTMOS-modes at 0.7 V operation. For the standard-mode operation, In-SSR device depicts better

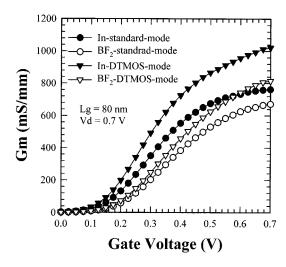

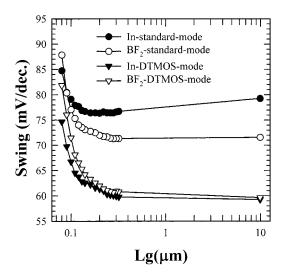

Fig. 5. The Gm-Vg characteristics for In-SSR and BF<sub>2</sub>-implanted devices, both under standard- and DTMOS-modes. The gate length is 80 nm.

characteristics than the BF2-implanted counterpart, and can be attributed to its super steep channel profile. While for the DTMOS-mode operation, In-SSR DTMOS also depicts higher saturated Gm for a given DIBL, compared to BF<sub>2</sub>-DTMOS. Furthermore, the improvement of In-SSR DTMOS is higher than that of BF<sub>2</sub> DTMOS. We believe this is again due to the higher substrate doping and a larger body factor in In-SSR device. This is because the larger body factor of In-SSR DTMOS will lead to a larger current drive increment, and therefore a higher Gm improvement. Furthermore, a larger body factor of In-SSR DTMOS will also result in a more effective reduction in the drain depletion layer, and therefore more effective DIBL suppression. In fact, a record high Gm of 1022 mS/mm was achieved at 0.7 V operation for the 80-nm gate-length In-DTMOS, as shown in Fig. 5. In addition, the Gm ratio  $(Gm_{DTMOS}/Gm_{Standard})$  are 1.34 and 1.21 for In-SSR and for BF2 devices, respectively. It is worthy to note here that the off-state current of In-SSR DTMOS is larger than that of BF<sub>2</sub>-DTMOS (i.e., 40 nA/ $\mu$ m compared to 31 nA/ $\mu$ m) due to the smaller  $V_{th}$ . In general, low  $V_{th}$ devices also show a small body effect (gamma) and thus reduce the dynamic efficiency of DTMOS. On the contrary, In-SSR device shows the combination of low  $V_{th}$  and high body effect simultaneously (i.e., higher dynamic efficiency) which allows a full exploitation of DTMOS. The subthreshold swing factors are plotted as a function of channel length Lqin Fig. 6. It is interesting to note that In-SSR devices actually depict worse subthreshold swing than the BF2-implanted counterparts under standard-mode operation. This is because of a shallower channel depletion layer in the indium-implanted channel, resulting in a larger depletion capacitance and therefore a larger subthreshold swing. However, the subthreshold swing of the In-SSR devices operating under DTMOS mode is significantly improved, and becomes even better than that of the BF<sub>2</sub>-implanted controls operating under DTMOS mode, due to a larger  $\gamma$ . This is because as the Vg increases, the  $V_{th}$  decreases more aggressive for a larger  $\gamma$  DTMOS, thus the drain current increases more rapidly, resulting in a sharp Id-Vg slope (i.e., better subthreshold swing). Fig. 7 shows

Fig. 6. Subthreshold swing as a function of Lg for In-SSR and BF $_2$ -implanted devices, both under standard- and DTMOS-modes.

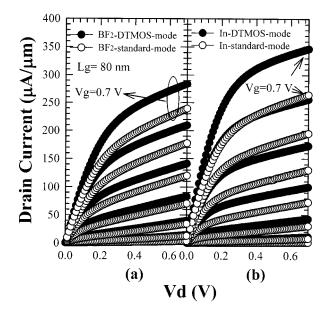

Fig. 7. Drain current of (a), BF $_2$ -implanted, and (b) In-SSR devices, both under standard- and DTMOS-modes. The gate length is 80 nm. Vg varies from 0 to 0.7 V in 0.1 V steps.

the output characteristics of 80 nm BF $_2$ -SSR and In-implanted devices both under standard- and DTMOS-mode operations. The gate voltage is varied from 0 to 0.7 V in 0.1 V steps. The improvement in current drive (measured at  $V_D=Vg=0.7$  V) due to DTMOS-mode operation are 18.8% and 32% for BF $_2$ -DTMOS and for In-SSR DTMOS, respectively.

# B. Narrow-Channel Characteristics

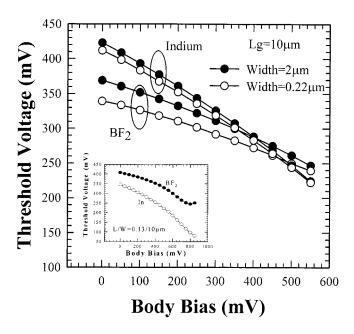

Fig. 8 shows the body effects of nMOSFETs with In-SSR and BF<sub>2</sub>-implant (i.e., control). The device threshold voltage  $V_{th}$  is plotted as a function of the body bias for long channel transistors with narrow- and wide-channel widths. We found that the  $V_{th}$  of In-SSR split is more sensitive to body bias (i.e., it depicts a larger  $\gamma$ ) for both wide and narrow transistors, compared to BF<sub>2</sub>-implanted control. This is primarily due to

Fig. 8. Dependence of threshold voltage on the body bias for BF<sub>2</sub>-implanted and In-SSR devices with channel width of 0.22 and 2  $\mu$ m. Inset shows the result for short-channel devices with  $L/W=0.13~\mu$ m/10  $\mu$ m.

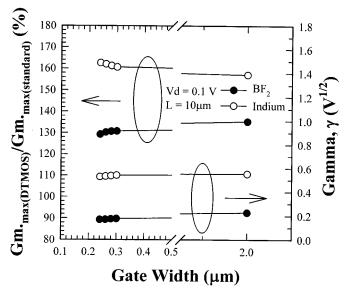

the steep indium dopant profile in the channel depletion layer, as has been confirmed from SIMS analyses (shown previously in Fig. 2). In addition, the  $V_{th}$  of In-SSR devices show a less dependence on channel width, compared to BF2-implanted controls. In the insert of Fig. 8, we plot the  $V_{th}$  as a function of body bias for a short channel (i.e., 0.13  $\mu$ m) device. It is found that In-SSR device indeed depicts a larger body effect, albeit its  $V_{th}$  is lower than that of BF<sub>2</sub>-implanted control. It is worthy to note here that we have chosen an indium implant dose of  $1 \times 10^{13}$  cm<sup>-2</sup>, because it has been previously reported that the achievable body effect factor saturates at around this dose, with a corresponding doping concentration of no more than  $7-8 \times 10^{17} \text{ cm}^{-3}$  [12]. In addition, the  $V_{th}$  of In-SSR devices are larger than BF<sub>2</sub> devices in long channel region (i.e., 10  $\mu$ m), and smaller than BF<sub>2</sub> devices in short channel region. This is mainly because the In-SSR devices suffer from indium de-activation. So the  $V_{th}$  (standard device) shows a long-distance roll-off behavior which have been reported previously [12]. Fig. 9 shows the plot of linear transconductance (Gm) ratio  $(Gm_{DTMOS}/Gm_{Standard})$  and the body effect factor  $(\gamma)$  versus the coded channel width  $W_{\mathrm{coded}}$  for both In-SSR and BF $_2$ -implanted controls. Compared to the BF2-implanted counterparts, In-SSR DTMOSs show a higher Gm ratio and  $\gamma$ . More importantly, while the ratio of BF<sub>2</sub>-implanted devices shows a 6% reduction when Wcoded reduces from 2 to 0.22  $\mu$ m, a 5.5% increase is found for In-SSR devices instead. The undesirable  $\gamma$  and  $V_{th}$  reduction in the narrow-channel devices for the BF2-implanted controls are believed to be due to the boron diffusion and segregation into the edge in the channel width direction [13]. Since In-SSR DTMOS is less susceptible to such undesirable dopant segregation, it can therefore fully exploit the high current drive and low standby power features of DTMOS, even in narrow-channel devices.

Fig. 9. Gm ratio and  $\gamma$  versus gate width for BF2-implanted and In-SSR DTMOS. BF2-DTMOS shows Gm ratio degradation in narrow-channel devices.

Fig. 10. Hot-carrier degradation of 80-nm gate-length standard and DTMOS devices.

# C. Hot-Carrier Reliability

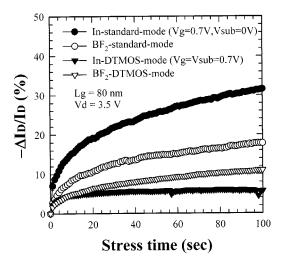

Hot-carrier reliability of In-SSR and BF<sub>2</sub>-implanted 80-nm gate-length devices both under standard- and DT-modes has been investigated. Hot-carrier-induced drain current degradation is plotted in Fig. 10. In-SSR device shows a worse hot-carrier resistance, compared to BF<sub>2</sub>-implanted control, both under standard-mode operation. This is consistent with previous literature report that most channel conducting electrons are located in the lightly doped surface channel in In-SSR device, thus more electrons are available for injection into the oxide [14]. Surprisingly, it is observed for the first time that hot carrier degradation is actually reduced in DTMOS-mode operation for both In-SSR and BF<sub>2</sub>-implanted control. More importantly, the improvement is so dramatic in In-SSR DTMOS that it depicts an even smaller hot-carrier degradation than BF<sub>2</sub>-implanted DTMOS control. This can be attributed to the bulk charge being shared by the high

Fig. 11. Simulated lateral channel electric field distributions for both In-SSR and BF<sub>2</sub>-implanted devices under standard- and DT-modes.

Fig. 12. Hot-carrier lifetime of 80-nm gate-length standard and DTMOS devices.

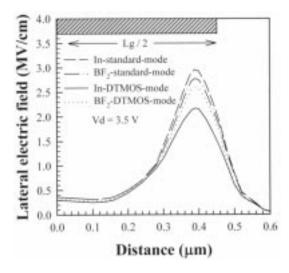

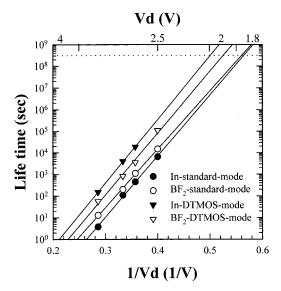

body potential under DTMOS-mode, thus the maximum drain electric field is reduced. The simulated lateral channel electric field distributions for both In-SSR and BF2-implanted devices under standard- and DT-modes are shown in Fig. 11. The simulated lateral channel electric field is at 3 nm below the Si/SiO<sub>2</sub> interface. Although the lateral channel electric field of In-SSR device is larger than that of BF2 under standard-mode operation, the electric field of In-SSR DTMOS is indeed smaller than that of BF<sub>2</sub>-implanted DTMOS. This is because In-SSR device has a higher  $\gamma$ , thus the bulk charge sharing is larger than that of BF<sub>2</sub>-implanted DTMOS with a smaller  $\gamma$ , resulting in a smaller channel electric field. The hot carrier lifetime versus stressing drain voltage is plotted in Fig. 12. Although In-SSR device depicts a worse hot-carrier lifetime than BF<sub>2</sub> control under standard-mode operation, In-SSR DTMOS exhibits a superior lifetime than BF<sub>2</sub>-implanted DTMOS.

### IV. CONCLUSION

A novel high-performance and high-reliability 80-nm gate-length DTMOS suitable for low-voltage ( $V_{DD}$ 0.7 V) applications has been proposed by using indium super-steep-retrograde (SSR) channel implantation. The new In-SSR DTMOS has a large dynamic threshold efficiency at a low  $V_{th}$  compatible with low-voltage applications, due to its low surface concentration and steep channel dopant profile. As a result, In-SSR DTMOS depicts significant performance improvements in terms of driving current, dynamic threshold property, subthreshold swing and Gm, which are difficult to achieve with conventional BF<sub>2</sub>-implanted DTMOS. In addition, contrary to conventional narrow-channel BF<sub>2</sub>-implanted DTMOS that suffers from degraded dynamic threshold gain, In-SSR DTMOS maintains its high performance in narrow-channel devices, due to reduced channel dopant segregation into the isolation edge oxide. Finally, it is found for the first time that the hot-carrier resistance is improved for devices under DTMOS-mode operation, especially for In-SSR DTMOS. The new In-SSR DTMOS thus appears to be a very promising candidate for future ultralow-voltage ULSI applications.

### ACKNOWLEDGMENT

The authors would also like to thank UMC TD/Logic Advanced Device Group for device fabrications and the anonymous reviews for their helpful comments.

## REFERENCES

- G. G. Shahidi, D. A. Antoniadis, and H. I. Smith, "Electron velocity overshoot at room and liquid-nitrogen temperatures in silicon inversion layers," *IEEE Electron Device Lett.*, vol. 9, p. 94, 1988.

- [2] G. G. Shahidi et al., "Indium channel implant for improved short-channel behavior of submicrometer NMOSFET's," IEEE Electron Device Lett., vol. 9, p. 409, 1993.

- [3] Y. V. Ponomarev *et al.*, "Channel profile engineering of 0.1  $\mu$ m-Si MOSFET by through-the-gate implantation," in *IEDM Tech. Dig.*, 1998, p. 635.

- [4] D. A. Antoniadis and J. E. Chung, "Physics and technology of ultra short channel MOSFET devices," in *IEDM Tech. Dig.*, 1991, p. 21.

- [5] G. G. Shahidi and J. Warnock *et al.*, "A high performance 0.15  $\mu$ m CMOS," in *VLSI Tech. Dig.*, 1993, p. 93.

- [6] F. Assaderaghi et al., "A dynamic threshold voltage MOSFET (DTMOS) for ultra-low voltage operation," in IEDM Tech. Dig., 1994, p. 809

- [7] H. Kotaki et al., "Novel bulk dynamic threshold MOSFET (B-DTMOS) with advanced isolation (SITOS) and gate to shallow-well contact (SSS-C) processes for ultra low power dual gate CMOS," in *IEDM Tech. Dig.*, 1996, p. 459.

- [8] C. Wann et al., "Channel profile optimization and device design for low-power high-performance dynamic-threshold MOSFET," in *IEDM Tech. Dig.*, 1996, p. 113.

- [9] T. Tanaka, Y. Momiyama, and T. Sugii, "Fmax enhancement of dynamic threshold-voltage MOSFET (DTMOS) under ultra-low supply voltage," in *IEDM Tech. Dig.*, 1997, p. 423.

- [10] A. Shibata et al., "Ultra low power supply voltage (0.3 V) operation with extreme high speed using bulk dynamic threshold voltage MOSFET (B-DTMOS) with advanced fast-signal-transmission shallow well," in Symp. VLSI Tech. Dig. Tech., 1998, p. 76.

- [11] S. J. Chang, C. Y. Chang, T. S. Chao, and T. Y. Huang, "High performance 0.1 μm Dynamic threshold MOSFET using indium channel implantation," *IEEE Electron Device Lett.*, vol. 21, p. 127, Mar. 2000.

- [12] P. Bouillon, R. Gwoziecki, and T. Skotnicki, "Anomalous short channel effects in Indium implanted nMOSFETs," in *IEDM Tech. Dig.*, 1997, p. 231

- [13] K. Ohe et al., "The inverse-narrow-width effect of LOCOS isolated n-MOSFET in high-concentration p-well," *IEEE Electron Device Lett.*, vol. 13, p. 636, Dec. 1992.

- [14] H. Tian et al., "An evaluation of super-steep-retrograde channel doping for deep-submicron MOSFET applications," *IEEE Trans. Electron Devices*, vol. 41, p. 1880, October 1994.

**Sun-Jay Chang** was born in Taitung, Taiwan, R.O.C., on August 28, 1973. He received the B.S. degree in physics from the National Chung-Hsing University, Taichung, Taiwan, in 1995, and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, in 1997. He is currently pursuing the Ph.D. degree in the Institute of Electronics, National Chiao-Tung University.

His research interests are in the areas of dynamic threshold MOSFET (DTMOS), SOI devices,

process, and characterization of deep submicron CMOS devices.

Chun-Yen Chang (F'88) was born in Feng-Shan, Taiwan, R.O.C. He received the B.S. degree in electrical engineering from Cheng Kung University in 1960, and the M.S. degree from the Institute of Electronics, National Chiao Tung University (NCTU), Hsinchu, Taiwan. His M.S. thesis was entitled "Tunneling in semiconductor–superconductor junctions." He received the Ph.D. degree in 1969 from NCTU with a dissertation entitled "Carrier transport across metal-semiconductor barrier." His work was published in 1970 and has been cited as

a pioneering paper in its field.

He has devoted himself to education and academic research for more than 40 years. He has contributed profoundly to the areas of microelectronics and optoelectronics, including the invention of the method of low-pressure-MOCVD-using tri-ethyl-gallium to fabricate LED, laser, and microwave transistors, Zn-incorporation of SiO2 for stabilization of power devices, and nitridation of SiO<sub>2</sub> for ULSIs, etc. From 1962 to 1963, he fulfilled his military service by establishing at NCTU Taiwan's first experimental TV transmitter, which formed the founding structure of today's CTS. In 1963, he joined NCTU as an Instructor, establishing a high vacuum laboratory. In 1964, he and his colleague established the semiconductor research center (SRC) at NCTU, where they made the nation's first Si planar transistor in April 1965 and the first IC in August 1966. In 1968, he published Taiwan's first semiconductor paper in an international journal, Solid-State Electronics. In 1969, he became a Full Professor, teaching solid state physics, quantum mechanics, semiconductor devices and technologies. From 1977 through 1987, he single-handedly established a strong electrical engineering and computer science program at NCKU where GaAs,  $\alpha$ -Si, poly-Si research projects were established in Taiwan for the first time. From 1987, he served consecutively as Dean of Research (1987-1990), Dean of Engineering (1990-1994), and Dean of Electrical Engineering and Computer Science (1994-1995). Simultaneously, he served as the Founding President of National Nano Devices Laboratories (NDL) from 1990 through 1997. In 1997, he became Director of Microelectronics and Information System Research Center (MIRC), NCTU (1997-1998). Under his technical leadership, NCTU has in recent years become number one worldwide in the number of papers contributed to IEEE journals. He has supervised more than 300 M.S. and 50 Ph.D. students. Many of his former students have since become founders of the most influential Hi-Tech enterprises in Taiwan, including UMC, TSMC, Winbond, MOSEL, Acer, and Leo. In August 1998, he was appointed President of NCTU. As the National Chair, Professor, and President of NCTU, his vision is to lead the university for excellence in engineering, humanity, art, science, management, and biotechnology. To strive forward to world class multidisciplinary university is the main goal to which he and his colleagues have been committed.

Dr. Chang was elected Fellow of IEEE in 1988 for his contribution to semiconductor device development and to education. He became a Member of Academia Sinica in 1996, and a Foreign Associate of the National Academy of Engineering in 2000 for his contribution to Taiwan electronics industry, material technology, and education. He received the IEEE Third Millennium Medal in 2000.

Coming Chen was born in Chiayi, Taiwan, R.O.C., on July 6, 1968. He received the M.S. degree from the Institute of Material Engineering, National Tsing-Hua University, Hsinchu, Taiwan, in 1992. He is currently pursuing the Ph.D. degree in the Institute of Electronics, National Chiao-Tung University, Hsinchu.

His research interests are in the areas of thin dielectric reliability, process, and characterization of deep submicron CMOS devices.

**Tien-Sheng Chao** (S'88–M'92) was born in Penghu, Taiwan, R.O.C., in 1963. He received the Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1992.

He joined the National Nano Device Laboratories (NDL), Hsinchu, as an Associate Researcher in July 1992, and became as a Researcher in 1996. He was engaged in developing the thin dielectrics preparations and cleaning processes. He is presently responsible for the deep submicron device integration at NDL.

Yao-Jen Lee was born in Kaoshiung, Taiwan, R.O.C., in 1976. He received the B.S. degree in physics from the National Chung-Hsing University, Taichung, Taiwan, in 1998, and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, in 2000.

His research interest is in the area of deep submicron devices.

**Tiao-yuan Huang** (S'78–M'80–SM'88–F'95) was born in Kaohsiung, Taiwan, R.O.C., on May 5, 1949. He received the B.S.E.E. and M.S.E.E. degrees from National Cheng Kung University, Tainan, Taiwan, in 1971 and 1973, respectively. After serving two years in the Taiwanese Navy, he joined Chung Shan Institute of Science and Technology, Lungtan, for two years, working on missile development. He received the Ph.D. degree in electrical engineering from the University of New Mexico, Albuquerque, in 1981.

He spent two years with the Semiconductor Process & Design Center, Texas Instruments. He then worked with several IC companies, including Xerox Palo Alto Research Center, Integrated Device Technology, Inc., and VLSI Technology, Inc. He has worked in various VLSI areas including memories (DRAM, SRAM, and nonvolatile memories), CMOS process/device technologies and device modeling/simulation, ASIC technologies, and thin-film transistors for LCD display. In 1995, he returned to Taiwan to become an Outstanding Scholar Chair Professor with National Chiao Tung University and Vice President in charge of R&D, National Nano Device Laboratories, National Science Council. He has published over 100 technical papers in international journals and conference proceedings. He holds over 20 issued U.S. patents.

Dr. Huang served on the technical committee of the IEEE International Electron Devices Meeting (IEDM) in 1991 and 1992. He also served on the program committee of the International Conference on Solid-State Devices and Materials (SSDM) from 1996 to 1998. He received the 1988 Semiconductor International's R&D Technology Achievement Award for his invention of the fully overlapped LDD transistors.