# A Physical Model for Hole Direct Tunneling Current in P<sup>+</sup> Poly-Gate PMOSFETs with Ultrathin Gate Oxides

Kuo-Nan Yang, Huan-Tsung Huang, *Student Member, IEEE*, Ming-Chin Chang, Che-Min Chu, Yuh-Shu Chen, Ming-Jer Chen, *Senior Member, IEEE*, Yeou-Ming Lin, Mo-Chiun Yu, Simon M. Jang, Douglas C. H. Yu, and M. S. Liang

Abstract—A model of the hole direct tunneling gate current accounting for heavy and light hole's subbands in the quantized inversion layer is built explicitly. This model comprises four key physical parameters: inversion layer charge density, hole impact frequency on  $SiO_2/Si$  interface, WKB transmission probability, and reflection correction factor. With the effective hole mass  $m_{oxb} = 0.51 m_o$  for parabolic dispersion relationship in the oxide, experimental reproduction without any parameter adjustment is consistently achieved in p+ poly-gate pMOSFETs with 1.23, 1.85, and 2.16 nm gate oxide thicknesses. The proposed model can thereby serve as a promising characterization means of direct tunnel oxides. In particular, it is calculated that the secondary subbands and beyond, although occupying few holes, indeed contribute substantially to the direct tunneling conduction due to effective lower barrier heights, and are prevailing over the first subbands for reducing oxide field down below 1 MV/cm.

## I. INTRODUCTION

HE MOSFET gate oxide thickness is rapidly approaching the direct tunneling limit that ultimately leads to intolerably increased standby power [1] and/or impractical applications [2]. Thus, accurate characterization and modeling of ultrathin oxides in the direct tunneling regime is essential and crucial. A series of models have recently been published concerning the electron direct tunneling in n<sup>+</sup> poly-gate nMOSFETs: a self-consistent numerical method of solving Schrödinger's and Poisson's equations [1] and computationally efficient models [3], [4]. The latter can provide more transparent understandings since it is made up of four key physical parameters: accumulation or inversion layer charge density, electron impact frequency on interface, WKB transmission probability, and specially, the reflection correction factor [3], [4]. As to another complementary devices, namely, p<sup>+</sup> poly-gate pMOSFETs, the hole direct tunneling under channel inversion condition was found to dominate over valence electron direct tunneling [5], followed by

Manuscript received March 8, 2000. This work was supported by the National Science Council under the Contract NSC88-2215-E-009-047. The review of this paper was arranged by Editor C.-Y. Lu.

K.-N. Yang, H.-T. Huang, M.-J. Chang, C.-M. Chu, Y.-S. Chen, and M.-J. Chen are with the Reliability Physics Laboratory and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: mjchen@RPL.ee.nctu.edu.tw)

Y.-M. Lin, M.-C. Yu, S. M. Jang, D. C. H. Yu, and M. S. Liang are with the R&D Department, Taiwan Semiconductor Manufacturing Company, Hsinchu 300. Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(00)09621-0.

more evidences [6], [7]. In this paper, we present a model of the hole direct tunneling current featuring the above four similar physical parameters. This model can serve as a promising means of sensitively characterizing direct tunnel oxides and can enable in-depth understandings of the roles of the subbands in the quantized inversion layer.

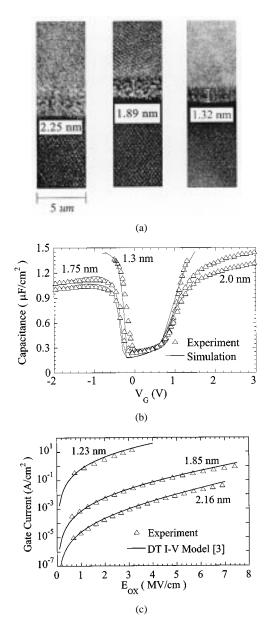

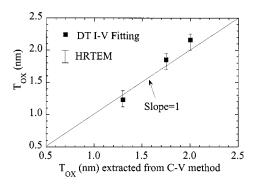

#### II. CHARACTERIZATION AND PARAMETER EXTRACTION

The p<sup>+</sup> poly-gate pMOSFETs were fabricated by a 0.18- $\mu$ m process technology [8] with gate oxides grown in diluted wet oxygen ambient to three different thicknesses. The gate dimension was drawn to  $100 \times 100 \ \mu \text{m}^2$ . Accurate determination of ultrathin oxide thickness  $T_{ox}$  is strongly demanded. Three techniques in terms of high resolution TEM(HRTEM), polysilicon depletion and quantum mechanics corrected capacitance-voltage (C-V) [9]-[11], and direct tunneling (DT) I-V[3] were adopted as shown in Fig. 1, through which consistent results were achieved as compared in Fig. 2. Fig. 1(a) just shows highly-localized HRTEM cross section while the variation across the wafer is depicted in Fig. 2 in terms of a bar. Our C-V data in Fig. 1(b) was measured in parallel mode with 1-MHz AC frequency. QM corrected C-V fitting based on van Dort's model for surface quantization [9], [10] was carried out to extract physical  $T_{ox}$ . In particular, the singular point problem encountered around the flat-band voltage  $V_{FB}$  was eliminated by adopting a modified version [11]. In Fig. 1(b), C–V fitting for  $T_{ox} = 1.3$  nm is limited to nondistorted range, -0.6 V  $< V_G <$ 0.6 V, where the tunneling current effect or others can be neglected. C–V fitting in Fig. 1(b) also produced the p<sup>+</sup> polysilicon dopant concentration  $N_{poly}=4.2\times10^{19}~{\rm cm}^{-3}$  and the effective channel dopant concentration  $N_{well} = 4 \times 10^{17} \, \text{cm}^{-3}$ , all being found to be consistent with the SIMS doping profile. In Fig. 1(c), the devices were biased in channel accumulation (positive gate voltage) with source, drain, and n-well tied to ground, and the oxide field strength  $E_{ox}$  was get in advance by means of the well-known C–V integration technique. With the effective electron mass  $m_{oxe} = 0.61 m_o$  for Franz-type dispersion relationship in the oxide, the conduction electron DT *I–V* fitting in Fig. 1(c) extracted  $T_{ox} = 1.23$ , 1.85, and 2.16 nm from three samples. Note that as all data go closer to the straight line with the unity slope in Fig. 2, more confidence for DT I-V extracted  $T_{ox}$ , as well as its subsequent applications in consistently calculating the DT hole current, can all be ensured.

Fig. 1. (a) HRTEM images of three pMOSFET gate stacks.  $T_{ox}$  values extracted from the canvases correspond to 2.25, 1.89, and 1.32 nm, respectively. (b) The oxide thickness extraction using C–V method was based on van Dort's model [9] and successive researchers [10], [11]. Best fitting produces  $T_{ox}$  of 2.0, 1.75, and 1.3 nm, respectively. (c) I–V fitting to find  $T_{ox}$ .  $T_{ox}$  values extracted by electron direct tunneling model [3], including quantization effect in accumulation layer under  $V_G > V_{FB}$ , are 2.16, 1.85, and 1.23 nm, respectively.

Fig. 2. Comparing  $T_{ox}$  extracted from several techniques.

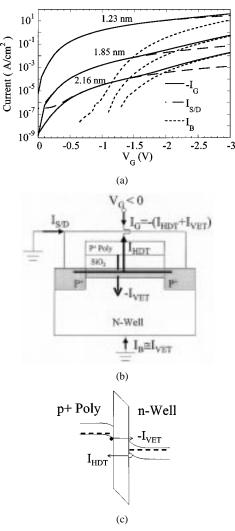

Fig. 3. (a) Measured hole direct tunneling current  $I_{HDT}(\simeq I_{S/D})$  and valence electron tunneling current  $I_{VET}(\simeq I_B)$  of three different  $T_{ox}$  under  $V_G < 0V$ . (b) The carrier separation configuration and (c) band diagram representation are schematically drawn.

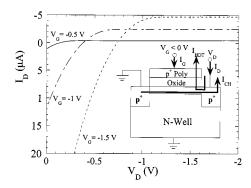

With source, drain, and n-well tied to ground, the source/drain current  $(I_{S/D})$ , bulk current  $(I_B)$ , and gate current  $(I_G)$  measured in inversion are plotted in Fig. 3(a) versus gate voltage  $(V_G)$ . The corresponding carrier separation configuration and the band diagram representation are schematically drawn in Fig. 3(b) and (c), respectively. It can be identified that the hole direct tunneling is responsible for source/drain current while the valence electron direct tunneling constitutes bulk current. It is seen from Fig. 3 that the hole direct tunneling dominates over the valence-band electron direct tunneling in gate voltage of 0 V to certain crossover point, which is consistent with [5]–[7]; however, the magnitude of this crossover gate voltage increases with decreasing oxide thickness, a phenomenon not mentioned before. A specific criterion of 1 A/cm $^2$  at gate voltage of -1V sets an ultimate limit of slightly thicker than 1.23 nm, again consistent with [2]. The impact of hole direct tunneling on normal device operation can be found in Fig. 4, revealing that the hole direct tunneling from inverted channel can reverse the polarity of the linear drain current. The similar drain current degradations for the n-channel counterpart have been reported

Fig. 4. Measured output I-V characteristics with  $W/L=10~\mu{\rm m}/50~\mu{\rm m}$  and  $T_{ox}=1.23~{\rm nm}.~I_D$  reverses its polarity at small  $|V_D|$  due to direct hole tunneling.

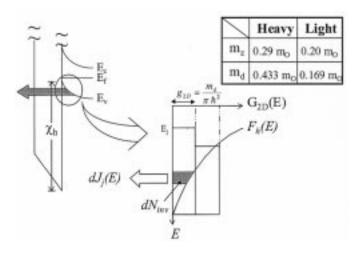

Fig. 5. Physical picture of valence hole quantized phenomenon along  $\langle 100 \rangle$  direction.  $G_{2D}(E)$  indicates density of states relative to hole's energy.  $F_h(E)$  represents Fermi–Dirac distribution function of hole and  $E_j$  means the quantized extremity energy of the jth subband.

previously [12], [13]. The impact of hole DT as outlined in Fig. 4 is one of the primary motivations of the underlying study. To clarify the essential mechanisms, however, the work focuses on the case of tying source and drain to a common potential.

# III. PHYSICAL MODEL

The two valence bands (heavy and light band), which are degenerate at k=0 ( $\Gamma$  point), have the form of warped spheres; therefore, the  $k \cdot p$  method concerning degenerate perturbation is necessary for the valence band [14]:

$$E_{V_{1,2}}(k) = \frac{\hbar^2}{2m_o} \{Ak^2 \pm (B^2k^4 + C^2[k_x^2k_y^2 + k_y^2k_z^2 + k_z^2k_x^2])^{1/2} \}.$$

Fig. 5 schematically shows the physical picture of the valence-band hole tunneling from the silicon inversion layer. In Fig. 5, a table lists the effective mass  $(m_z)$  along  $\langle 100 \rangle$  direction and density of states mass  $(m_d)$  of each type of hole as cited in [15]. The direct tunneling hole current from each subbands can be formulated in analogy with the mathematical treatment of

electron direct tunneling in [3]. Hole current density contributed by jth subband with energy E to E+dE can be written as

$$dJ_j(E) = qf_jg(E)P_t(E)dE \tag{1}$$

where

q elemental charge;

$f_j$  impact frequency of hole's wave packet on SiO<sub>2</sub>/Si interface;

g(E) inversion layer charge density per unit area and magnitude of E associated with jth subband;

$P_t(E)$  transmission probability through SiO<sub>2</sub> layer.

Denoting  $z_j$  as the classical turning point at the jth subband edge and  $v_{\rm Si, \perp}(z) (= \sqrt{2(E_j - qV(z))/m_z})$  as the velocity of wave packet

$$f_j = \left[2 \int_0^{z_j} \frac{dz}{v_{\text{Si},\perp}(z)}\right]^{-1} = \frac{q\epsilon_{ox}|E_{ox}|}{4\epsilon_{\text{Si}}} \left(\frac{m_z E_j}{3}\right)^{-1/2}. (2)$$

Triangle-like electrostatic potential is a good approximation for V(z). Using Sommerfeld-Wilson's quantization rule, we are able to get quantized energy along z-direction or  $\langle 100 \rangle$  direction in reciprocal space

$$E_j = \left(\frac{\hbar^2}{2m_z}\right)^{1/3} \left[\frac{3\pi q \epsilon_{ox} |E_{ox}| (j-1/4)}{2\epsilon_{Si}}\right]^{2/3}.$$

For inversion charge increment

$$dN_{inv} = \int_{E}^{E+dE} g_{2D} F_h(E) dE \simeq g_{2D} F_h(E) dE$$

$$g(E) = \frac{dN_{inv}}{dE} = g_{2D} F_h(E). \tag{3}$$

In (3), density of states per unit area for two-dimensional hole gas (2DHG),  $g_{2D}$ , is equal to  $m_d/\pi\hbar^2$  and Fermi–Dirac distribution function  $F_h(E)$  associated with valence holes is  $1/(1+\exp(E_f-E/k_BT))$ .  $E_f$  is the quasi–Fermi level and  $k_B$  is Boltzmann's constant. Under the inversion condition, it is easy to build that  $|V_G-V_{FB}|=\phi_p+T_{ox}|E_{ox}|+\phi_s$ .  $\phi_p$  means the potential drop on the p+-poly gate, and  $\phi_s$  signifies that on the n-well. Considering the poly-depletion effect, we know that  $\phi_p$  can be expressed as  $\epsilon_{ox}^2 E_{ox}^2/(2q\epsilon_{\rm Si}N_{poly})$ . Note that the values of oxide field strength  $E_{ox}$  are obtained by the C-V integration technique so that the surface potential,  $\phi_s$ , can be computed directly. Thus,  $E_f$  is equal to  $\phi_{Bn}-\phi_s$ . Here  $\phi_{Bn}(=[E_g-K_BT \ln(N_C/N_D)]/q)$  is the potential difference between the quasi–Fermi level  $(E_f/q)$  and valence band  $(E_V/q)$  in the charge neutrality region of n-well.

Following [3],  $P_t(E)$  can be modeled by

$$P_t(E) = T_{WKB}(E)T_R(E) \tag{4}$$

where

$$T_{WKB}(E) = \exp\left[-\frac{2}{\hbar} \left| \int_0^{T_{ox}} \sqrt{2m_{oxh}(E - qV(z))} dz \right| \right]$$

$$= \exp\left(\frac{4\sqrt{2m_{oxh}}(\varphi_{cath}^{3/2} - \varphi_{an}^{3/2})}{3q\hbar|E_{ox}|}\right).$$

$\varphi_{cath}$  is the barrier height of tunneling hole with total energy E at cathode side or p<sup>+</sup>-poly gate/SiO<sub>2</sub> interface, and  $\varphi_{an}$  is

that at anode side or SiO<sub>2</sub>/n-well interface.  $\varphi_{cath} = q\chi_h - q|E_{ox}|T_{ox} - E$  and  $\varphi_{an} = q\chi_h - E$ . In our work, the SiO<sub>2</sub>/Si barrier height  $q\chi_h$  is 4.7 eV for both heavy and light hole. The total energy, E, consists of the transversal and longitudinal energies

$$E = \frac{\hbar^2 (k_x^2 + k_y^2)}{2m_t} + E_j$$

where  $m_t$  is the transversal mass. On the other hand,  $T_R$  is a justified factor concerning wavefunction's reflection phenomenon occurring at  $\mathrm{SiO}_2/\mathrm{Si}$  interfaces as discussed in [3] and [4], as follows:

$$T_R(E) = \frac{4v_{\text{Si}, \perp}(E)v_{ox}(\varphi_{an})}{v_{\text{Si}, \perp}^2(E) + v_{ox}^2(\varphi_{an})} \times \frac{4v_{\text{Si}, \perp}(E + q|E_{ox}|T_{ox})v_{ox}(\varphi_{cath})}{v_{\text{Si}, \perp}^2(E + q|E_{ox}|T_{ox}) + v_{ox}^2(\varphi_{cath})}$$

where  $v_{\mathrm{Si},\perp}(E)$  and  $v_{\mathrm{Si},\perp}(E+q|E_{ox}|T_{ox})$  are the group velocities of the holes incident and leaving the oxide, respectively. The group velocity of hole with energy E along  $\langle 100 \rangle$  direction within the jth subband at  $\mathrm{SiO}_2/\mathrm{Si}$  interfaces is independent of E with the following expression:

$$v_{\text{Si},\perp}(E) = v_{\text{Si},\perp}(z=0) = \sqrt{\frac{2E_j}{m_z}}.$$

Besides,  $v_{ox}(\varphi_{an})$  and  $v_{ox}(\varphi_{cath})$  are the magnitudes of the purely imaginary group velocities of holes at the cathode and anode side within the oxide, respectively. Parabolic dispersion relation,  $E_{\rm SiO_2} = q\chi_h - E - qV_{ox}(x) = \hbar^2 k_{ox}^2/2m_{oxh}$ , is adopted to gauge the tunneling hole's behavior within the oxide film. Consequently, the imaginary group velocity which is dependent on E within oxide can be described by

$$v_{ox} = \frac{1}{\hbar} \frac{dE_{\rm SiO_2}}{dk_{ox}} = \sqrt{\frac{2E_{\rm SiO_2}}{m_{oxh}}}.$$

This factor could not be neglected when electrostatic potential V(x) changes acutely with respect to position or the intensity of incident wave cannot be treated to being equal to that of reflection wave.

Recalling (1)–(4), the tunneling current density contributed by the jth subband with energy E ranging from  $E_j$ , the subband extremity, to infinity can be shown below:

$$J_{j} = \int_{E_{j}}^{\infty} dJ_{j}(E)$$

$$= \int_{E_{j}}^{\infty} qf_{j}g(E)P_{t}(E) dE$$

$$= qf_{j}g_{2D} \int_{E_{j}}^{\infty} F_{h}(E)P_{t}(E) dE.$$

An explicit model of hole direct tunneling current from all heavy and light holes, subbands is readily built as follows:

$$J_t = \sum_{j} \left[ \int_{E_{j,H}}^{\infty} qf_{j,H}g_H(E)P_{t,H}(E) dE + \int_{E_{j,L}}^{\infty} qf_{j,L}g_L(E)P_{t,L}(E) dE \right]$$

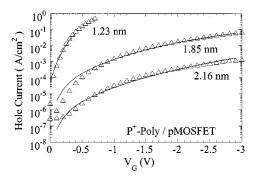

Fig. 6. Simulated results (lines) and experimental data (symbols) for pMOSFET direct tunneling hole current of three different  $T_{ox}$  under  $V_G < 0$  V.  $V_G$  can be related to  $E_{ox}$  by means of the C-V integration technique.

$$= q \sum_{j} \left[ f_{j,H} g_{2D,H} \int_{E_{j,H}}^{\infty} F_{h}(E) P_{t,H}(E) dE + f_{j,L} g_{2D,L} \int_{E_{j,L}}^{\infty} F_{h}(E) P_{t,L}(E) dE \right]. (5)$$

Index H and L mean heavy and light holes, respectively.

#### IV. CALCULATION AND DISCUSSION

Essentially, there are three input parameters to the model: the oxide field  $E_{ox}$ , the effective hole mass  $m_{oxh}$  for parabolic relationship in the oxide, and the oxide thickness  $T_{ox}$ . The other physical parameter values are unique and cannot be arbitrarily adjusted when fitting data. Fortunately, the well-recognized integration technique carried out directly on the C-Vcurves in Fig. 1(b) can easily quantify  $E_{ox}$ . An effective hole mass  $m_{oxh} = 0.51 m_o$  for heavy and light hole was found to be capable of modeling reasonably well the hole direct tunneling I–V characteristics as plotted in Fig. 6 for three different oxide thicknesses. The corresponding oxide thicknesses were consistently identical to those involved with conduction-band electron tunneling in Fig. 1(c) due to the same samples used. Excellent reproduction in Fig. 6 can lead to one argument that the proposed model can find its potential applications in terms of a sensitive means of characterizing direct tunnel oxides.

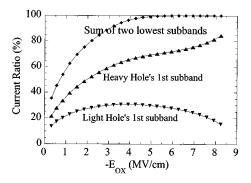

Ten subbands for heavy hole and six subbands for light hole were used in above modeling. Based on the simplified method to calculate the subband energies [16], in-depth understandings concerning the roles of different subbands in the quantized inversion layer can be created fully. First of all, the occupation ratio, defined as  $N_{inv,j}/\sum N_{inv,j}$ , of the subbands was calculated versus oxide field as shown in Fig. 7. It can be seen that the heavy hole lowest (first) subband occupies most (90%) of all inversion holes and this ratio drops with lowering  $-E_{ox}$ . However, the light hole first subband, which occupies considerably 10%, exhibits opposite trend. Fig. 7 also reveals that the remaining subbands get few due to their higher quantized states whereas as we go toward lower  $-E_{ox}$ , more and more holes are filling the secondary subbands and beyond. Although higher energy states share far less carriers, the other factor such as the transmission probability can be much larger than the ground state due to effective lower barrier heights for tunneling. The resulting tunneling current thus contains a substantial component from the secondary subbands

Fig. 7. Occupation ratio  $N_{inv,\,j}/\sum N_{inv,\,j}$  of all the subbands versus oxide field.  $N_{well}=4\times 10^{17}$  cm<sup>-3</sup>.

Fig. 8. Partial fraction  $J_j/\sum J_j$  of direct tunneling hole current contributed by two lowest subbands versus oxide field.  $T_{ox}=1.85$  nm;  $N_{well}=4\times10^{17}$  cm<sup>-3</sup>;  $N_{poly}=4.2\times10^{19}$  cm<sup>-3</sup>.

and beyond. This is valid, in particular, under the condition of small  $-E_{ox}$  as clearly depicted in Fig. 8 in terms of the partial fraction defined as  $J_j/\sum J_j$ . For the first time, this figure points out that the hole direct tunneling from the secondary subbands and beyond prevails over the first subbands for reducing oxide field down below around 1 MV/cm.

# V. CONCLUSION

A physical model of the hole direct tunneling through ultrathin oxides has been built and experimental reproduction has been consistently achieved in p<sup>+</sup> poly-gate pMOSFETs for different oxide thicknesses. This model has evidenced its potential applications in sensitively characterizing direct tunnel oxides as well as enabling in-depth understandings of the role of the different subbands in affecting hole direct tunneling conduction.

### REFERENCES

- S. H. Lo, D. A. Buchanan, Y. Taur, and W. Wang, "Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thin-oxide nMOSFET's," *IEEE Electron Device Lett.*, vol. 18, pp. 209–211, 1997.

- [2] G. Timp et al., "Process toward 10 nm CMOS devices," in IEDM Tech. Dig., 1998, pp. 615–618.

- [3] L. F. Register, E. Rosenbaum, and K. Yang, "Analytic model for direct tunneling current in polycrystalline silicon-gate metal-oxide-semiconductor devices," *Appl. Phys. Lett.*, vol. 74, pp. 457–459, 1999.

- [4] N. Yang, W. K. Henson, J. R. Hauser, and J. J. Wortman, "Modeling study of ultrathin gate oxides using direct tunneling current and capacitance-voltage measurements in MOS devices," *IEEE Trans. Electron Devices*, vol. 46, pp. 1464–1471, July 1999.

- [5] T. Matsuoka *et al.*, "Direct tunneling  $N_2O$  gate oxynitrides for low-voltage operation of dual gate CMOSFET's," in *IEDM Tech. Dig.*, 1995, pp. 851–854.

- [6] Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, "Polarity dependent gate tunneling currents in dual-gate CMOSFET's," *IEEE Trans. Electron Devices*, vol. 45, pp. 2355–2360, Nov. 1998.

- [7] W. C. Lee, T. J. King, and C. Hu, "Evidence of hole direct tunneling through ultathin gate oxide using P<sup>+</sup> poly-SiGe gate," *IEEE Electron Device Lett.*, vol. 20, pp. 268–270, Jan. 1999.

- [8] C. H. Diaz et al., "A 0.18 um CMOS logic technology with dual gate oxide and low-k interconnect for high-performance and low-power applications," in Proc. Symp. VLSI Technology, 1999, pp. 11–12.

- [9] M. J. van Dort, P. H. Woerlee, and A. J. Walker, "A simple model for quantization effects in heavily-doped silicon MOSFET's at inversion conditions," *Solid-State Electron.*, vol. 37, pp. 411–414, 1994.

- [10] S. A. Hareland *et al.*, "Computationally efficient models for quantization effects in MOS electron and hole accumulation layers," *IEEE Trans. Electron Devices*, vol. 45, pp. 1487–1493, 1998.

- [11] C. H. Choi et al., "MOS C-V characterization of ultrathin gate oxide thickness (1.3-1.8 nm)," *IEEE Electron Device Lett.*, vol. 20, pp. 292–294, July 1999.

- [12] H. S. Momose et al., "1.5 nm direct-tunneling gate oxide Si MOSFET's," IEEE Trans. Electron Devices, vol. 43, pp. 1233–1242, 1996

- [13] G. Timp et al., "Low leakage, ultra-thin gate oxides for extremely high performance sub-100 nm nMOSFETs," in *IEDM Tech. Dig.*, 1997, pp. 930–932.

- [14] B. K. Ridley, Quantum Processes in Semiconductors, 3rd. ed. ed. Oxford, U.K.: Clarendon, 1993, ch. 1.

- [15] S. Takagi, M. Takayanagi, and A. Toriumi, "Characterization of inversion-layer capacitance of holes in Si MOSFET's," *IEEE Trans. Electron Devices*, vol. 46, pp. 1446–1450, July 1999.

- [16] H. H. Mueller and M. J. Schulz, "Simplified method to calculate the band bending and the subband energies in MOS capacitors," *IEEE Trans. Electron Devices*, vol. 44, pp. 1539–1543, Sept. 1997.

**Kuo-Nan Yang** was born in Yuen-Lien, Taiwan, R.O.C. He received the B.S. and M.S. degrees in electronics engineering from National Chiao-Tung University (NCTU), Taiwan, in 1998 and 1999, respectively. he is currently pursuing the Ph.D. degree in electronics engineering with the research group of Prof. M.-J. Chen at the Department of Electronics, NCTU.

His interests include modeling and reliability physics of MOSFETs structure.

Huan-Tsung Huang (S'98) received the B.E. degree in electrical engineering from the National Cheng-Kung University, Taiwan, R.O.C., and the M.S. and Ph.D. degrees in electronics engineering from the National Chiao-Tung University, Hsinchu, Taiwan, in 1988, 1990, and 2000, respectively.

From 1990 to 1992, he served in the Chinese army as a Tactical Control Officer. Since 1992, he has been with Ta-Hua Institute of Technology, Chung-li, Taiwan. His research interests are currently the reliability issues such as TDDB, soft breakdown,

trap-assisted tunneling leakage, etc., in deep submicron CMOS.

Ming-Chin Chang was born in Yuen-Lien, Taiwan, R.O.C., in 1975. She received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, respectively, in 1998 and 2000.

Her primary research interest is gate dielectric reliability.

**Che-Min Chu** was born in Taiwan, R.O.C., on September 14, 1976. He received the B.S. degree in electrical engineering from the National Chiao-Tung University, Hsinchu, Taiwan, in 1999. He is currently pursuing the M.S. degree and engages in modeling and physics of submicron MOSFET reliability.

Mo-Chiun Yu was born in Hsinchu, Taiwan, R.O.C., in 1968. He received the B.S. degree in electrical engineering from National Tsing-Hua University, Hsinchu, in 1991, and the M.S. degree in electrical engineering from Tohoku University, Sendai, Japan in 1997, under the sponsorship of the Ministry of Education of Taiwan.

In 1997, he joined Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu, where he has been engaging in research and development for ultrathin gate dielectric process and characterization.

Yuh-Shu Chen was born in Kaoshiung, Taiwan, R.O.C., on January 6, 1974. He received the B.S. degree in electronic engineering from the National Chung Hsing University in 1996, and the M.S. degree from the Institute of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, in 1999.

His research interests include C-V simulation and analysis in MOSFETs, and quantum-mechanical effects in deep submicron MOS structure.

Ming-Jer Chen (S'78–M'79–S'80–M'84–SM'98) received the B.S. degree in electrical engineering with highest honors from National Cheng-Kung University, Taiwan, R.O.C., in 1977, and the Ph.D. in electrical engineering form National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1985. Since 1985, he has been with the Department of Electronics Engineering, NCTU, where he is Professor. From 1987 to 1992, he was a Principal Consultant sy TSMC, where he led a team to build process window and design rule. In 1996 and 1997,

he enabled the ERSO/ITRI video A/D converters and the TSMC mixed-mode CMOS processes, respectively. His current areas are nanoscale reliability physics and next-generations electronics. He has graduated six Ph.D. students and has been granted four U.S. patents and six Taiwan patents.

Professor Chen is a Co-Winner of the 1992 and 1993 Chinese Young Engineer Paper Award, and a Co-Winner of the 1996 Acer Distinguished Ph.D. Dissertation Award. He is a Member of Phi Tau Phi.

Yeou-Ming Lin was born in Taipei, Taiwan, R.O.C., in 1968. He received the B.S. degree in electrical engineering from the Tatung Institute of Technology in 1991, the M.S. degree in electrical engineering from the National Hsin-Hua University in 1993, and Ph.D. degree in electronic engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1997. His Ph.D. dissertation focused on process issues of interpoly-silicon dielectric and intermetal dielectric and their impacts on device reliability.

From 1994 to 1995, he worked on intermetal dielectric development for 0.35- $\mu$ m CMOS at Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu. Since September 1999, he is responsible for gate quality silicon and high-k gate dielectric for 0.1- $\mu$ m CMOS at TSMC. He nis now with Sematech for process development and reliability of gate quality silicon.

Simon M. Jang received the B.S. and M.S. degrees from the National Tsing-Hua University, Hsinchu, Taiwan, R.O.C., in 1985 and 1987, and the Ph.D. degree from the Massachusetts Institute of Technology (MIT), Cambridge, in 1993, all in materials science and engineering. His dissertation work included SiGe CVD technology, kinetics, and thermal stability for HBT application. Sponsored by IBM and SRC, his research was conducted in the Microsystems Technology Laboratories, MIT, under the guidance of Prof. R. Reif in electrical engineering.

He joined Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu Taiwan, in 1993. He has successfully developed ozone-TEOS, spin-on coating, HDPCVD dielectrics, PECVD SiON anti-reflection layer, and CMP processes for 0.5–0.18  $\mu m$  CMOS technologies. He is now the Manager of Dielectric/CMP/Diffusion Projects in the Advanced Module Technology Division, R&D, responsible for the modules of shallow trench isolation, gate stack, ultrashallow junction, interpoly-metal dielectric, low-dielectric-constant intermetal dielectric, and oxide, tungsten, and copper CMP for 0.13  $\mu m$  generation and beyond. He has authored or co-authored more than 40 technical papers and received 48 U.S. patents and 50 Taiwanese patents.

Dr. Jang is a Member of Phi Tau Phi.

**Douglas C.H. Yu** received the Ph.D. degree from the Material Engineering Department, Georgia Institute of Technology, Atlanta.

He was with AT&T Bell Laboratories, Allentown, PA. The projects he involved include PECVD thin film processing, 256 k/1 Mb SRAM process integration and yield improvement,  $0.35/0.25~\mu m$  ultrahigh performance logic device development, modular BiCMOS and MiM process integration. He later joined Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu, Taiwan, R.O.C., where he

lead a module team to successfully develop TSMC  $0.5~\mu$ m,  $0.35~\mu$ m, and  $0.18~\mu$ m core logic technologies. He performed yield improvement and transferred the process to manufacturing. He also managed an advanced technology team to develop and qualify TSMC 1st Cu technology for  $0.18~\mu$ m technology. Currently he manages a module team to develop TSMC Cu/low-k interconnect, gate stack, salicide, and shallow-trench-isolation, etc. He has been awarded 91 U.S. patents with another 90 patent applications pending. Also, he has numerous publications in technical journals and conferences, all in VLSI processing/device/integration area.

M.S. Liang, photograph and biography not available at the time of publication.