# Reduction of Source/Drain Series Resistance and Its Impact on Device Performance for PMOS Transistors with Raised $Si_{1-x}Ge_x$ Source/Drain

Hsiang-Jen Huang, Kun-Ming Chen, Chun-Yen Chang, Fellow, IEEE, Liang-Po Chen, Guo-Wei Huang, and Tiao-Yuan Huang, Fellow, IEEE

Abstract—P-channel MOS transistors with raised Si<sub>1-x</sub>Ge<sub>x</sub> and Si source/drain (S/D) structure selectively grown by ultra high vacuum chemical vapor deposition (UHVCVD) were fabricated for the first time. The impacts of  $Si_{1-x}Ge_x$  and Si epitaxial S/Dlayer on S/D series resistance and drain current of p-channel transistors were studied. Our result show that the new device with  $Si_{1-x}Ge_x$  raised S/D layer depicts only half the value of the specific contact resistivity and S/D series resistance  $(R_{\rm SD})$ , compared to the device with Si raised S/D layer. The improvement is even more dramatic, when comparing to the conventional device without any raised S/D layer, i.e.,  $R_{\mathrm{SD}}$  of the new device with  $Si_{1-x}Ge_x$  raised S/D is only about one fourth the value of the conventional device. Moreover, the device with raised SiGe S/D structure produces a 29% improvement in transconductance  $(g_m)$  at an effective channel length of 0.16  $\mu$ m. These performance improvements, together with several inherent advantages such as self-aligned selective epitaxial growth (SEG) nature and the resultant T-shaped gate structure, make the new device with raised  $Si_{1-x}Ge_x$  S/D structure very attractive for future sub-0.1  $\mu$ m p-channel MOS transistors.

Index Terms—RSD MOSFET, selective epitaxial growth, source and drain series resistance (( $R_{\rm S\,D}$ ), strained  ${\rm Si}_{1-x}{\rm Ge}_x$ , ultra high vacuum chemical vapor deposition.

## I. INTRODUCTION

S the device is scaled down to sub-0.1  $\mu$ m region, the source/drain area needs to be scaled proportionally, while keeping a low specific contact resistivity ( $\rho_c$ ) in order to maintain a high current drive on the scaled transistors [1]. However, it has become increasingly difficult to use conventional ion-implantation to form shallow junctions, due to channeling effects and the tradeoff between radiation damage annealing and low thermal budget [2]. Recently, out-diffusion from a doped layer has received renewed interest for ultra-shallow junction formation [3]. Shallow junctions obtained by out-diffusion from in-situ doped or ion-implanted p<sup>+</sup>/n<sup>+</sup> SiGe layer have been reported [4]. Si<sub>1-x</sub>Ge<sub>x</sub> is particularly suitable for such application, because it can be selectively deposited onto

Manuscript received July 26, 1999; revised January 26, 2000. This work was supported in part by the National Science Council under Contract NSC88-2215-E009-048. The review of this letter was arranged by Editor C. Wann.

H.-J. Huang, K.-M. Chen, C.-Y. Chang, and T.-Y. Huang are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. (e-mail: cyc@cc.nctu.edu.tw).

L.-P. Chen and G.-W. Huang are with the National Nano-Device Laboratory, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(00)07259-1.

the exposed S/D areas. Besides,  $Si_{1-x}Ge_x$  can be selectively etched with high selectivity to Si and  $SiO_2$  [5]. Furthermore,  $Si_{1-x}Ge_x$  has lower Schottky barrier height with respect to  $p^+$  junctions because of the reduced band gap, which is beneficial for achieving low contact resistivity [6], [7]. However, to the best of our knowledge, there has been no literature report regarding the application of  $p^+$ -SiGe epitaxial layer to form p-channel transistors with raised S/D structure. Although Uchino *et al.*[8] has reported the use of  $n^+$ -SiGe epitaxial layer to form n-channel transistors with raised S/D, however, the raised S/D structure in their p-channel transistors were formed by  $p^+$ -Si material only. In this work, p-channel MOS transistors with raised  $Si_{1-x}Ge_x$  S/D structure were fabricated, for the first time. The impacts of using  $Si_{1-x}Ge_x$  S/D layer on contact resistance and device performance are reported.

# II. EXPERIMENT

P-channel MOS transistors with raised source/drain structure were fabricated on 6-in (100) 10–15  $\Omega$ -cm wafers. Briefly, 550 nm LOCOS field oxide was used for device isolation. After  $V_T$ -adjust implant and anti-punchthrough implant, a 4-nm gate oxide and polysilicon gate were formed. The gate was defined by g-line lithography and further asked down to 0.18  $\mu$ m. Afterward, the source/drain extension implant was performed by BF<sub>2</sub> at 10 KeV with  $1 \times 10^{15}$  cm<sup>-2</sup> dosage. An 800 °C, 20 min furnace anneal and RTA 1050°C, 10 s for activation of gate and S/D extension took place at this stage. The activation anneal must be processed before SiGe epitaxy because strained SiGe layer cannot tolerate large thermal budget. Next, a 150 nm sidewall spacer was formed by a conformal TEOS deposition and subsequent RIE-etch. Then, wafers were split to receive SiGe or Si selective epitaxial growth (SEG) on the exposed S/D regions by ANELVA SRE-612 cold-wall ultra-high vacuum chemical vapor deposition (UHVCVD) system. The standby base pressure was kept at  $2 \times 10^{-10}$  torr. For growing B-doped strained Si<sub>1-x</sub>Ge<sub>x</sub> layers, Si<sub>2</sub>H<sub>6</sub>, GeH<sub>4</sub>, and 1% B<sub>2</sub>H<sub>6</sub> diluted in H<sub>2</sub> were introduced with a growth rate of 41 Å/minute for  $Si_{0.91}Ge_{0.09}$  and 43 Å/minute for  $Si_{0.86}Ge_{0.14}$  at 550 °C. The maximum available time for selective epitaxial growth of Si<sub>0.91</sub>Ge<sub>0.09</sub> or Si<sub>0.86</sub>Ge<sub>0.14</sub> layer (i.e., epitaxy on Si region but not on oxide region) at 550 °C is above 90 min. Samples with epitaxial thickness of 50 nm and 100 nm were processed in order to study the effect of the epitaxial layer thickness on the device performance. Afterward, p<sup>+</sup> S/D implant was

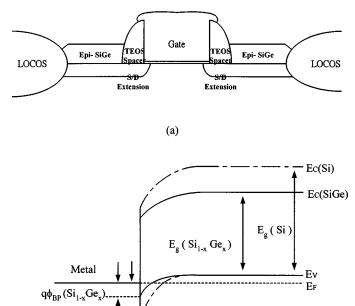

Fig. 1. (a) Schematic cross section of raised source/drain transistors and (b) energy band diagram of metal/ $p^+Si_{1-x}Ge_x$  junction.

(b)

performed by BF<sub>2</sub> at 20 KeV with  $5 \times 10^{15}$  cm<sup>-2</sup> dosage. This is followed by rapid thermal annealing (RTA) at 950 °C for 10 s. For comparison, conventional MOS transistors (i.e., without any raised S/D layer) were also fabricated in the same run. The schematic cross-section of the resultant raised source/drain MOS transistor (RSDMOSFET) is shown in Fig. 1(a). It is worthy to note that a T-shaped gate structure is formed simultaneously as a result of lateral overgrowth during S/D epitaxial growth. Finally, Ti/TiN/Al-Si-Cu/TiN was deposited and patterned to complete the contact metallization.

# III. RESULTS AND DISCUSSION

The barrier height  $(q\phi_{\rm BP})$  formed at metal/semiconductor interface is known to be a critical factor in determining the contact resistivity. Fig. 1(b) shows the energy band diagram of a metal/p<sup>+</sup>Si<sub>1-x</sub>Ge<sub>x</sub> junction. The energy-band gap (Eg) of Si<sub>1-x</sub>Ge<sub>x</sub> changes from 1.12 to 0.66 eV with increasing Ge mole fraction [9]. The conduction band edges are almost at the same level in metallurgical Si and SiGe junction. However, the potential difference of the valence band will cause the lowering of the Schottky barrier height (SBH) in metal/p<sup>+</sup>Si<sub>1-x</sub>Ge<sub>x</sub> junction [10]. For pseudomorphic p-Si<sub>0.86</sub>Ge<sub>0.14</sub> layer, the SBH is expected to be lower than that of metal/p<sup>+</sup>Si by 0.07 eV [10], thus effectively reduces the specific contact resistivity ( $\rho_C$ ).

Measured S/D series resistance  $(R_{\rm SD})$ , specific contact resistivity  $(\rho_C)$ , and sheet resistance  $(\rho_{\rm SH})$  are summarized in Table I for samples with different process conditions. The specific contact resistivity was measured by transmission line method (TLM), while the S/D series resistances  $(R_{\rm SD})$  were extracted by "shift and ratio" (S&R) method [11]. From Table I, it can be seen that  $R_{\rm SD}$  is significantly improved for devices

TABLE I MEASURED S/D SERIES RESISTANCE ( $R_{\rm SD}$ ), SPECIFIC CONTACT RESISTIVITY ( $\rho_C$ ), AND SHEET RESISTANCE ( $\rho_{\rm SH}$ )

| PMOS           | Epi.      | Ge mole  | Spec. Contact         | Sheet                                        | S/D Series       |

|----------------|-----------|----------|-----------------------|----------------------------------------------|------------------|

| Sample         | Thickness | Fraction | Resistivity pc        | Resistance                                   | Resistance       |

| No.            | (Å)       | x (%)    | $(\Omega-cm^2)$       | $\rho_{\mathrm{SH}}\left(\Omega/\Box\right)$ | $R_{SD}(\Omega)$ |

| Control Sample | 0         | 0        | 3.91×10 <sup>-6</sup> | 130.68                                       | 93.25            |

| 1              | 500       | 0        | 3.20×10 <sup>-6</sup> | 105.88                                       | 43.92            |

| 2              | 500       | 9        | 2.12×10 <sup>-6</sup> | 111.22                                       | 31.45            |

| 3              | 1000      | 9        | 1.93×10 <sup>-6</sup> | 84.46                                        | 19.23            |

| 4              | 500       | 14       | 1.62×10 <sup>-6</sup> | 113.78                                       | 23.85            |

| 5              | 1000      | 14       | 1.81×10 <sup>-6</sup> | 96.62                                        | 21.19            |

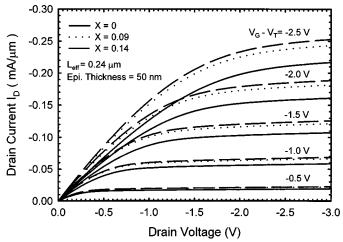

Fig. 2. Measured drain current  $I_D$  versus drain voltage  $V_D$  characteristics for RSD-MOSFET with different Ge mole fraction x. The effective channel length ( $L_{\rm eff}$ ) is 0.24  $\mu$ m, and the epitaxial thickness is 50 nm.

with SiGe RSD ( $\sim 20 \Omega$ ), compared to devices with Si RSD  $(\sim 44~\Omega)$  and conventional MOSFET without RSD  $(\sim 93~\Omega)$ . By comparing Samples 1 (50 nm Si), 2 (50 nm Si<sub>1-x</sub>Ge<sub>x</sub> with x = 9%), and 4 (50 nm  $Si_{1-x}Ge_x$  with x = 14%), it can be seen that for a given epitaxial thickness (e.g., 50 nm),  $\rho_C$ and  $R_{\rm SD}$  decrease as Ge fraction (x) increases. It is believed that the decrease in  $\rho_C$  is the main reason for  $R_{\rm SD}$  reduction. However, the sheet resistance ( $\rho_{SH}$ ) shows a slight increase with increasing x, which is probably due to incremental defects in pseudomorphic  $p^+Si_{1-x}Ge_x$  layer. The value of  $\rho_C$  for Sample 2 (50 nm  $Si_{1-x}Ge_x$  with x = 9%) and Sample 3 (100 nm  $Si_{1-x}Ge_x$  with x = 9%) should be about the same. This is also true for Sample 4 (50 nm  $Si_{1-x}Ge_x$  with x = 14%) and Sample 5 (100 nm  $Si_{1-x}Ge_x$  with x = 14%), because  $\rho_C$ should be independent of the epitaxial thickness. The observed difference could be attributed to calculation errors, or defects during epitaxial process. On the other hand, by comparing Samples 2 (50 nm  $Si_{1-x}Ge_x$  with x = 9%) and 3 (100 nm  $Si_{1-x}Ge_x$  with x = 9%), there is about 24% improvement in  $\rho_{\rm SH}$  as the epitaxial layer becomes twice as thicker, which also leads to a reduction of  $R_{\rm SD}$ .

Fig. 2 displays the  $I_D$ - $V_D$  characteristics of RSDMOSFET's with the same epitaxial thickness (50 nm) but different Ge mole fraction x. The effective channel length was extracted by S&R method. It can be seen that the device with  ${\rm Si_{0.86}Ge_{0.14}}$  RSD produces a drive current (measured at  $V_D=-2.5~{\rm V}$ ) and  $V_G-V_T=-2.5~{\rm V}$ ) of 246  $\mu{\rm A}/\mu{\rm m}$ , which is 17%

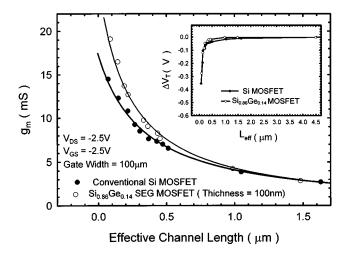

Fig. 3. Transconductance  $g_m$  as a function of effective channel length  $(L_{\rm eff})$  for both RSD-MOSFET and conventional transistors. The insert figure shows the  $\Delta V_{\rm TH}$  roll-off characteristics. The gate oxide thickness is 4 nm.

more than that of the device with Si RSD, both with the same effective channel length (e.g.,  $0.24 \mu m$ ). The transconductance  $(g_m)$  as a function of effective channel length for both RSD Si<sub>0.86</sub>Ge<sub>0.14</sub> MOSFET and the conventional Si MOSFET are plotted in Fig. 3. For  $L_{\rm eff} = 0.5 \, \mu \rm m$ ,  $\rm Si_{0.86}Ge_{0.14}$ MOSFET exhibits roughly 15%  $g_m$  improvement over the conventional Si MOSFET. However, as  $L_{

m eff}$  reduces to 0.16  $\mu$ m, the  $g_m$  improvement of Si<sub>0.86</sub>Ge<sub>0.14</sub> MOSFET's reaches 29% over that of the conventional counterparts. This illustrates the importance of maintaining a low series resistance as devices are scaled down, and makes the devices with Si<sub>0.86</sub>Ge<sub>0.14</sub> RSD even more attractive for future sub-0.1  $\mu$ m technologies. The short channel characteristics  $(\Delta V_T = V_T \text{ (long channel)} - V_T \text{ (short channel)})$  are shown in the insert of Fig. 3, it can be seen that a slight improvement in threshold voltage lowering is also obtained on the devices with  $Si_{0.86}Ge_{0.14}$  RSD.

# IV. CONCLUSION

In this study, p-channel MOS transistors with raised  $Si_{1-x}Ge_x$  source/drain were fabricated, for the first time, to study its impact on extrinsic resistance and device character-

istics. Significant reduction of source/drain contact resistance by the epitaxial  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  has been demonstrated. By employing a  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  raised source/drain structure, the extrinsic component of the parasitic source-drain resistance can be reduced remarkably, resulting in improved drive current and transconductance for p-channel transistors. These performance improvements, together with several inherent advantages such as the self-aligned nature of selective epitaxial growth (SEG) and the resultant T-shaped gate structure, make it a very attractive device structure for future sub-0.1  $\mu$ m salicided or nonsalicided p-channel MOS transistors.

### ACKNOWLEDGMENT

The authors would like to thank Dr. H. C. Lin and Dr. T. S. Chao for their support and experimental assistance.

### REFERENCES

- Y.-S. Chieh, A. Y. Perera, and P. Krusius, "Series resistance of silicided ohmic contacts for nanoelectronics," *IEEE Trans. Electron Devices*, vol. 39, pp. 1882–1890, Aug. 1992.

- [2] R. B. Fair and G. A. Ruggles, "Thermal budget issues for deep submicron ULSI," *Solid State Technol.*, vol. 1990, p. 107, 1990.

- [3] M. Ono et al., "Sub-50 nm gate length n-MOSFET's with 10 nm phosphorus source and drain junction," in IEDM Tech. Dig., 1993, pp. 119–122.

- [4] J. Sakano and S. Furukawa, "Study of shallow p<sup>+</sup>n junction formation using SiGe/Si system," *Jpn. J. Appl. Phys.*, vol. 32, pp. 6163–6167, 1993

- [5] F. S. Johnson, D. S. Miles, D. T. Grider, and J. J. Wortman, "Selective chemical etching of polycrystalline SiGe alloys with respect to Si and SiO<sub>2</sub>," *J. Electron. Mater.*, vol. 21, pp. 805–810, 1992.

- [6] V. Aubry, F. Meyer, P. Warren, and D. Dutartre, "Schottky barrier heights of W on Si<sub>1-x</sub>Ge<sub>x</sub> alloys," *Appl. Phys. Lett.*, vol. 63, pp. 2520–2522, 1993

- [7] H. Shinoda et al., "Electrical properties of metal/Si<sub>1-x</sub>Ge<sub>x</sub>/Si(100) heterojunctions," Appl. Surf. Sci., vol. 100/101, pp. 526–529, 1996.

- [8] T. Uchino et al., "A raised source/drain technology using in-situ P-doped SiGe and B-doped Si for 0.1 um CMOS ULSIs," in *IEDM Tech. Dig.*, 1997, pp. 479–482.

- [9] M. Arienzo et al., "Si-Ge alloys: Growth, properties and applications," Appl. Surf. Sci., vol. 48/49, pp. 377–386, 1991.

- [10] C. G. Van de Walle and R. Martin, "Theoretical calculations of heterojunction discontinuities in the Si/Ge system," *Phys. Rev. B*, vol. 34, pp. 5621–5634, 1986.

- [11] Y. Taur et al., "A new "shift and ratio" method for MOSFET channel-length extraction," IEEE Electron Device Lett., vol. 13, pp. 267–269, 1992.