# Robust Ultrathin Oxynitride Dielectrics by NH<sub>3</sub> Nitridation and N<sub>2</sub>O RTA Treatment

Tung Ming Pan, Student Member, IEEE, Tan Fu Lei, Member, IEEE, and Tien Sheng Chao, Member, IEEE

Abstract—In this paper, a method to grow robust ultrathin  $(E_{\rm OT} = 28 \text{ Å})$  oxynitride film with effective dielectric constant of 5.7 is proposed. Samples, nitridized by NH<sub>3</sub> with additional N<sub>2</sub>O annealing, show excellent electrical properties in terms of very low bulk trap density, low trap generation rate, and high endurance in stressing. This novel dielectric appears to be very promising for future ULSI devices.

Index Terms—EEPROM, flash memory, NH<sub>3</sub>, N<sub>2</sub>O, oxynitride, RTA.

# I. INTRODUCTION

THE CONTINUOUS scaling of thermal  $SiO_2$  as the gate dielectric has run into difficulties, where high leakage currents are inevitable due to direct tunneling when oxide thickness is less than 25 Å [1]. Recently, ultra-thin silicon nitride gate dielectrics are proposed to replace the conventional oxide to meet the need for increased capacitance and while maintain a low gate leakage. Moreover, in EEPROM and flash memory devices, the thickness of the tunnel oxide is limited by the stress-induced-leakage-current (SILC) after many write/erase (WE) cycles. Ultrathin nitride or oxynitride films [2]–[4] have been reported with good performance in SILC. Hence, it becomes the most promising candidate to replace thermal SiO<sub>2</sub> film as the tunneling dielectric to improve WE endurance. However, the Si<sub>3</sub>N<sub>4</sub>/Si interface is not yet as good as the SiO<sub>2</sub>/Si interface and the density of interface defects is also relatively high. An additional N<sub>2</sub>O treatment can reduce this interface state and bulk trap densities [5]. In this paper, an ultrathin oxynitride is grown by nitridizing the silicon substrate in NH3 and with an additional N<sub>2</sub>O treatment is proposed. Excellent electrical and reliability characteristics are found for this oxynitride film.

#### II. EXPERIMENTAL

Samples were fabricated on 4-in p-type (100)-oriented silicon wafers with resistivity of 14–21  $\Omega$ -cm. All the wafers were first cleaned by standard RCA clean method. A 15 Å Si<sub>3</sub>N<sub>4</sub> film was first grown by NH<sub>3</sub> (flow rate is 105 sccm, pressure is 500 mtorr) nitridation of the Si substrate in LPCVD system at 850 °C for 1 h. All samples were immediately annealed in

T. M. Pan and T. F. Lei are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

T. S. Chao is with the National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(00)06302-3.

a N<sub>2</sub>O rapid thermal annealing (RTA) treatment at 800, 900, and 1000 °C, respectively. Polycrystalline Si films with a thickness of 3000 Åwere deposited by LPCVD. The poly-Si film was doped with POCl<sub>3</sub> at 900 °C for 30 min. A 5000 Å Al film was deposited on the wafer by a thermal coater. The gate of metal-oxide-semiconductor (MOS) capacitor was defined by lithography, and then Al and poly-Si films were etched by wet etch chemistry. A 5000 Å Al film was also deposited on backside of wafers after stripping the oxide on the backside. Finally, all the samples were sintered at 400 °C for 30 min in an N<sub>2</sub> ambient to form a good ohmic contact. The gate dielectrics of MOS capacitors with area of  $10^{-4}$  cm<sup>2</sup> were measured. The thickness of ultrathin Si<sub>3</sub>N<sub>4</sub> film was determined by using spectroscopic ellipsometer. The equivalent oxide thickness  $(E_{OT})$ was calculated by high frequency capacitance–voltage (C-V)of 0.1 MHz at operating range of  $-3 \sim 2$  V in strong accumulation region without considering quantum mechanical effects. The physical thickness was doubly checked by TEM to obtain the dielectric constant. The electrical properties and reliability characteristics of MOS capacitors were measured by using the Hewlett-Packard (HP) 4156B semiconductor parameter analyzer.

### **III. RESULTS AND DISCUSSION**

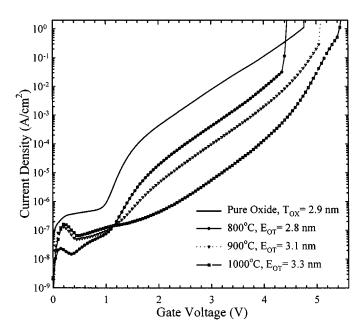

The resultant equivalent oxide thickness  $(E_{OT})$  of oxynitride film for a 15 Å nitride annealed in a N<sub>2</sub>O ambient at 800, 900, and 1000 °C is 28, 31, and 33 Å, respectively. The thickness of oxynitride film increases as the RTA temperature increases. Physical thickness of 800 °C sample measured by TEM (not shown) is 40 Å. The effective dielectric constant of 5.7 was obtained for this sample. Fig. 1 shows J-V characteristics for pure thermal oxide and these samples after treatment at different RTA temperature. It is found that samples with  $E_{\rm OT} = 28$  Å (annealed at lowest temperature of 800 °C) shows a lower leakage current than pure thermal oxide with  $T_{\text{OX}} = 29$  Å and exhibits the lowest leakage current at voltage of  $0 \sim 1 \text{ V}$  among three samples. This leakage increases as the RTA temperature increases even with a thicker  $E_{\rm OT} = 31$  Å for 900 °C sample or 33 Å for 1000 °C sample. This result can be attributed to the fact that more positive trapped charges are generated due to more nitrogen incorporation at high temperature annealing in N<sub>2</sub>O ambient [6], [7]. These positive charges will assist tunneling in the low field.

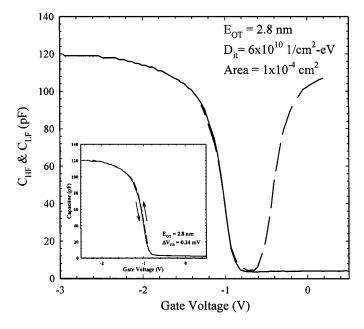

Fig. 2 shows the quasistatic and high frequency of C-V curves for the sample with  $E_{\rm OT} = 28$  Å. The interface state density of this sample was deduced as low as  $6 \times 10^{10}$  eV<sup>-1</sup> cm<sup>-2</sup>. This implies that Si<sub>3</sub>N<sub>4</sub> film annealed at 800 °C in N<sub>2</sub>O gas by using RTA system can produce a good interface

Manuscript received March 13, 3000; revised April 25, 2000. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 89-2215-E009-306. The review of this letter was arranged by Editor C.-P. Chang (e-mail: u85611515@cc.nctu.edu.tw).

Fig. 1. J-V characteristics of pure thermal oxide and 15 Å Si<sub>3</sub>N<sub>4</sub> films annealed at various temperature.

Fig. 2. Quasistatic and high frequency of C-V curves and inset shows hysteresis curves of a 15 Å Si<sub>3</sub>N<sub>4</sub> film annealed at 800 °C.

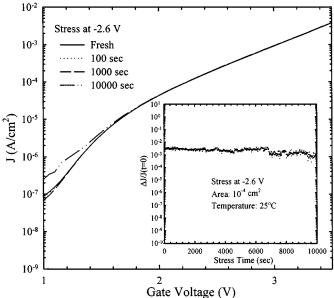

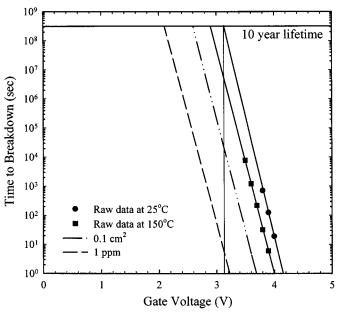

quality. Hysteresis of the high-frequency C-V characteristics of this oxynitride film was shown in the insert by the amount of flat-band voltage shift between opposite sweep directions. Negligible amount of hysteresis ( $\Delta V_{\rm FB} = 0.34$  mV) is observed, indicating very low bulk or interface trap densities in the film. Fig. 3 shows the result after constant voltage stress at -2.6 V for sample with  $E_{\rm OT} = 28$  Å annealed at 800 °C. No significant SILC was observed after 10 000-s stressing. In the insert, the sample after 10 000-s stressing shows gate current ( $\Delta J/J(t = 0)$ , where  $\Delta J = [J(t) - J(t = 0)]$ ) for constant voltage stressing. In Fig. 4 the cumulative impact of area scaling, 1 ppm failure rate, and temperature acceleration in ten years is evaluated [8], [9]. For  $E_{\rm OT} = 28$  Å annealed at 800 °C,

Fig. 3. SILC under constant voltage stress and inset shows  $\Delta J/J(t = 0)$  versus stress time plots of a 15 Å Si<sub>3</sub>N<sub>4</sub> film annealed at 800 °C.

Fig. 4. Illustration of loss in the maximum operating voltage by temperature acceleration, scaling to effective area, and calculation of 1 ppm failures for 15 Å Si<sub>3</sub>N<sub>4</sub> film annealed at 800 °C.

figures drawn well fit to the measured time-to-breakdown ( $T_{\rm BD}$ ) at room temperature and 150 °C. The area scaling is calculated by assuming a Weibull distribution (63% value) with a random distribution of breakdown sites [10]. The 150 °C-data have been a scaling of  $10^{-4}$  cm<sup>2</sup> to 0.1 cm<sup>2</sup>, and finally the 1 ppm-line was calculated from the 150 °C-data. The maximum operating voltage could be as high as 2.1 V in these conditions.

Although this oxynitride with  $E_{\text{OT}}$  of 28 Å has demonstrated, ultrathin  $E_{\text{OT}}$  dielectric films should be developed. The oxynitride with  $E_{\text{OT}}$  of 15 Å or less can be also achieved by reducing the temperature and/or time of NH<sub>3</sub> nitridation or using diluted N<sub>2</sub>O RTA annealing process.

# IV. CONCLUSION

In this letter, we reported a very promising method to obtain a robust ultra-thin oxynitride by  $NH_3$  nitridation and with a  $N_2O$  RTA treatment. This oxynitride film exhibits excellent reliability properties in terms of low leakage currents, low interface state density and high reliability during stressing. This novel dielectric appears to be very promising for future ULSI devices.

## ACKNOWLEDGMENT

The authors would like to express their appreciation to all the staff of Semiconductor Research Center, National Chiao Tung University and National Nano Device Laboratory for their technical help.

#### REFERENCES

C. Hu, "Gate oxide scaling limits and projection," in *IEDM Tech. Dig.*, 1996, pp. 319–322.

- [2] S. C. Song *et al.*, "Ultra thin (<20 Å) CVD Si<sub>3</sub>N<sub>4</sub> gate dielectric for deep-sub-micron CMOS devices," in *IEDM Tech. Dig.*, 1998, pp. 373–376.

- [3] Y. Shi, X. Wang, and T. Ma, "Electrical properties of high-quality ultrathin nitride/oxide stack dielectrics," *IEEE Trans. Electron Devices*, vol. 46, pp. 362–368, 1999.

- [4] S. C. Song *et al.*, "Ultra thin high quality stack nitride/oxide gate dielectrics prepared by in-situ rapid thermal N<sub>2</sub>O oxidation of NH<sub>3</sub>-nitride Si," in *VLSI Tech. Symp. Dig.*, 1999, pp. 137–138.

- [5] L. K. Han, J. Kim, G. W. Yoon, J. Yan, and D. L. Kwong, "High quality oxynitride gate dielectrics prepared by reoxidation of NH<sub>3</sub>-nitrided SiO<sub>2</sub> in N<sub>2</sub>O ambient," *Electron. Lett.*, vol. 31, pp. 1196–1198, 1995.

- [6] Y. H. Lin, C. L. Lee, and T. F. Lei, "Monitoring trapped charge generation for gate oxide under stress," *IEEE Trans. Electron Devices*, vol. 44, pp. 1441–1446, 1997.

- [7] , "Correlation of stress-induced leakage current with generated positive trapped charges for ultrathin gate oxide," *IEEE Trans. Electron Devices*, vol. 45, pp. 567–570, 1998.

- [8] J. H. Stathis and D. J. DiMaria, "Reliability projection for ultra-thin oxides at low voltage," *IEDM Tech. Dig.*, pp. 167–170, 1998.

- [9] R. Degraeve *et al.*, "Temperature acceleration of oxide breakdown and its impact on ultra-thin gate oxide reliability," in *VLSI Tech. Symp. Dig.*, 1999, pp. 59–60.

- [10] R. Degraeve *et al.*, "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Devices*, vol. 45, pp. 904–911, 1998.