## Effects of composition and N 2 plasma treatment on the barrier effectiveness of chemically vapor deposited WSi x films

M. T. Wang, M. H. Chuang, L. J. Chen, and M. C. Chen

Citation: Journal of Vacuum Science & Technology B 18, 1929 (2000); doi: 10.1116/1.1305273

View online: http://dx.doi.org/10.1116/1.1305273

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/18/4?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Effect of NH 3 thermal treatment on an atomic layer deposited on tungsten films and formation of W–B–N J. Vac. Sci. Technol. B **21**, 1466 (2003); 10.1116/1.1585064

Atomic-layer-deposited WN x C y thin films as diffusion barrier for copper metallization Appl. Phys. Lett. **82**, 4486 (2003); 10.1063/1.1585111

Effectiveness of Ti, TiN, Ta, TaN, and W 2 N as barriers for the integration of low-k dielectric hydrogen silsesquioxane

J. Vac. Sci. Technol. B 18, 221 (2000); 10.1116/1.591176

Properties and thermal stability of chemically vapor deposited W-rich WSi x thin films

J. Vac. Sci. Technol. B 17, 385 (1999); 10.1116/1.590567

Thermal stability of selective chemical vapor deposited tungsten contact and effects of in situ N 2 plasma treatment

J. Vac. Sci. Technol. B 16, 2026 (1998); 10.1116/1.590124

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

## Effects of composition and N<sub>2</sub> plasma treatment on the barrier effectiveness of chemically vapor deposited WSi<sub>x</sub> films

M. T. Wang<sup>a)</sup> and M. H. Chuang

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan

L. J. Cher

Department of Submicron Technology Development, ERSO/ITRI, Hsinchu, Taiwan

M. C. Chen

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan

(Received 1 May 1998; accepted 21 April 2000)

This work investigates the thermal stability of chemically vapor deposited amorphous  $WSi_x$  layers used as a diffusion barrier between Cu and Si substrate, in which the  $WSi_x$  layers were deposited to a thickness of about 50 nm using the  $SiH_4$  reduction of  $WF_6$  at various  $SiH_4/WF_6$  flow ratios. For 30 min annealing in nitrogen ambient, the effectiveness of the  $WSi_x$  layers as barriers between a copper overlayer and a  $p^+-n$  junction diode decreases as the Si/W atomic ratio, x, increasing from 1 to 1.3. This composition change is obtained by raising the  $SiH_4/WF_6$  flow ratio from 3 to 50. As deposited, all films are x-ray amorphous. Their resistivity increases roughly linearly with x. The barrier capability of  $WSi_x$  layers can be significantly improved by an  $in \ situ \ N_2$  plasma treatment. The  $N_2$  plasma treatment produces a very thin layer of WSiN (about 5 nm) on the surfaces of  $WSi_x$  layers. In particular, the  $Cu/WSiN/WSi_x/p^+-n$  junction diodes with the  $WSi_x$  layers deposited with a  $SiH_4/WF_6$  flow ratio of 3 were able to remain intact up to at least 600 °C. © 2000 American *Vacuum Society*. [S0734-211X(00)03204-2]

#### I. INTRODUCTION

Copper (Cu) has been extensively studied as a potential metallization material for future ultralarge scale integrated circuits because of its low electrical resistivity, superior electromigration resistance, 1-3 and possibility of deposition by electroplating as well as the chemical vapor deposition (CVD) method.<sup>4-6</sup> Moreover, copper has a better thermal conductivity, higher melting point, and less potential of hillocks' formation than the conventionally used Al alloys. However, Cu metallization is faced with many challenges in practice, such as the lack of a stable self-passivated oxide, poor adhesion to dielectric layers, difficulty of dry etching, and the formation of Cu-Si compounds at low temperatures (about 200 °C).8 In addition, copper diffuses fast in silicon and causes deep-level trapping;9 it also drifts through oxide layers under accelerated electric field. 10,11 Therefore, a diffusion barrier between Cu and its underlying layers is considered as a prerequisite for practical applications of Cu metallization.

Various materials have been studied as diffusion barriers between Cu and its underlying layers. Sputter deposited nitride-based diffusion barriers, such as TiN, <sup>12,13</sup> WN, <sup>14,15</sup> TaN, <sup>16–18</sup> MoN, <sup>19,20</sup> and TiWN, <sup>21,22</sup> have attracted extensive attention for a long time. However, these barriers are generally polycrystalline, and grain boundaries in the barriers provide fast paths for Cu diffusion. Typically, the atomic diffusivities in the amorphous phase are orders of magnitude below those of the corresponding polycrystalline phase. <sup>23,24</sup> Thus, the amorphous diffusion barrier is of great interest. In

a)Electronic mail: mcchen@cc.nctu.edu.tw

this work, we used chemically vapor deposited amorphous WSi<sub>x</sub> (CVD-WSi<sub>x</sub>) layers as a diffusion barrier between Cu and Si substrate. The effects of composition on the barrier capability of the amorphous CVD-WSi<sub>x</sub> layers were studied using electrical measurements as well as material analyses. We found that the barrier effectiveness depended on the composition of the amorphous WSi<sub>x</sub> layers. To improve the barrier capability of the WSi<sub>x</sub> layers, we formed a very thin WSiN layer on the surfaces of WSi<sub>x</sub> layers using an *in situ* N<sub>2</sub> plasma treatment. The resultant WSiN/WSi<sub>x</sub> barrier bilayer was proven to possess a much improved barrier capability against Cu diffusion.

#### **II. EXPERIMENT**

The thermal stability of barrier layers was evaluated by measuring the leakage current of thermally annealed Cu/barrier/ $p^+-n$  junction diodes. The starting materials used for the diodes fabrication were n-type, (100) oriented silicon wafers with 4–7  $\Omega$  cm nominal resistivity. After Radio Corporation of America standard cleaning, the wafers were thermally oxidized to grow a 500 nm oxide layer. Diffusion regions with area sizes of  $500\times500$  and  $1000\times1000~\mu\text{m}^2$  were defined on the oxide covered wafers using the conventional photolithographic technique. The  $p^+-n$  junctions with a junction depth of about 0.3  $\mu$ m were formed by BF<sub>2</sub><sup>+</sup> implantation at 40 keV to a dose of  $3\times10^{15}\,\text{cm}^{-2}$  followed by furnace annealing at 900 °C for 30 min in N<sub>2</sub> ambient.

After the junctions were formed, the wafers were divided into three groups for the preparation of the following devices:  $Cu/p^+-n$ ,  $Cu/WSi_r/p^+-n$ , and  $Cu/WSiN/WSi_r/p^+$

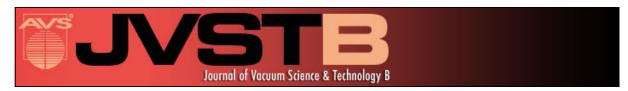

Fig. 1. Si/W atomic ratio, x, of WSi $_x$  films deposited at various SiH $_4$ /WF $_6$  flow ratios. The films were deposited at a temperature of 250 °C, total gas pressure of 12 mTorr, and WF $_6$  flow rate of 2 sccm.

$p^+-n$  junction diodes, in which the WSi<sub>x</sub> layers were deposited by the CVD method to a thickness of about 50 nm using the SiH<sub>4</sub> reduction of WF<sub>6</sub> at various SiH<sub>4</sub>/WF<sub>6</sub> flow rates. In this study, the WSi<sub>x</sub> layers were deposited using a load-locked cold wall CVD system with the following deposition conditions: substrate temperature 250 °C, total gas pressure 12 mTorr, WF<sub>6</sub> flow rate 2 sccm, and SiH<sub>4</sub> flow rate ranging from 6 to 100 sccm. For the formation of WSiN/WSi<sub>x</sub> barrier bilayers, an *in situ* N<sub>2</sub> plasma treatment was performed on the surfaces of CVD–WSi<sub>x</sub> layers without breaking the vacuum. The N<sub>2</sub> plasma treatment was performed with the following conditions: N<sub>2</sub> flow rate 80 sccm, total gas pressure 25 mTorr, plasma power 100 W, and treatment time 300 s. Finally, Cu metallization was applied to all samples.

To investigate the thermal stability of the variously metallized junction diodes, the samples were thermally annealed in  $N_2$  flowing furnace for 30 min at a temperature ranging from 200 to 700 °C. Reverse bias leakage current measurements on the thermally annealed diodes were used to evaluate the barrier capability. An HP-4145B semiconductor parameters analyzer was used for the measurement, and at least 30 diodes were measured in each case. Unpatterned samples of  $WSi_x/Si$ ,  $Cu/WSi_x/Si$ , and  $Cu/WSiN/WSi_x/Si$  multilayer

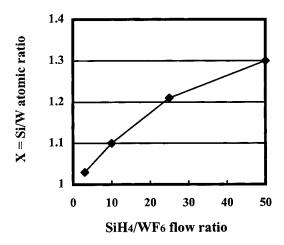

Fig. 2. Resistivity of  ${\rm WSi}_x$  films vs x. The  ${\rm WSi}_x$  films were deposited at a substrate temperature of 250 °C, total gas pressure of 12 mTorr, and WF<sub>6</sub> flow rate of 2 sccm.

structures were also prepared for material analysis. Sheet resistance of the multilayer structures was measured using a four point probe. Auger electron spectroscopy (AES) was used to determine the composition of  $WSi_x$  films. Rutherford backscattering spectroscopy (RBS) was used to determine the Si/W atomic ratio. Scanning electron microscopy (SEM) was employed to observe the surface morphology and microstructure. X-ray diffraction (XRD) analysis was used for phase identification.

#### **III. RESULTS AND DISCUSSION**

#### A. Properties of CVD-WSi, films

Before investigating the thermal stability of  $Cu/WSi_x/p^+-n$  junction diodes, properties of  $CVD-WSi_x$  films, including the Si/W atomic ratio, electrical resistivity,

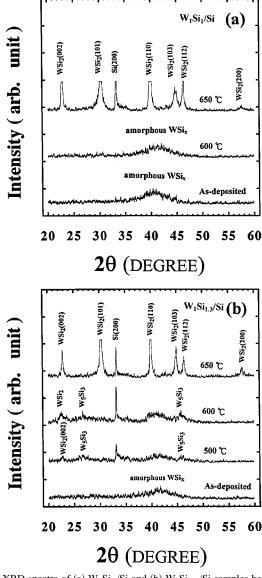

Fig. 3. XRD spectra of (a)  $W_1Si_1/Si$  and (b)  $W_1Si_{1,3}/Si$  samples before and after annealing at various temperatures. The  $W_1Si_1$  and  $W_1Si_{1,3}$  layers are 150 nm thick.

Table I. Crystalline phases of  $\text{CVD-WSi}_{\chi}$  films after annealing for 30 min in  $\text{N}_2$  ambient at various temperatures.

| Annealing               | Si/W atomic ratio x |                                                             |                                                             |  |  |

|-------------------------|---------------------|-------------------------------------------------------------|-------------------------------------------------------------|--|--|

| temperatures            | 1.0 1.1             |                                                             | 1.3                                                         |  |  |

| As-deposited Amorphous  |                     | Amorphous                                                   | Amorphous                                                   |  |  |

| 400 °C                  | Amorphous           | Amorphous                                                   | Amorphous                                                   |  |  |

| 500 °C                  | Amorphous           | Amorphous                                                   | Weak WSi <sub>2</sub> , weak W <sub>5</sub> Si <sub>3</sub> |  |  |

| 600 °C                  | Amorphous           | Weak WSi <sub>2</sub> , weak W <sub>5</sub> Si <sub>3</sub> | Weak WSi <sub>2</sub> , weak W <sub>5</sub> Si <sub>3</sub> |  |  |

| 650 °C                  | WSi <sub>2</sub>    | WSi <sub>2</sub>                                            | WSi <sub>2</sub>                                            |  |  |

| 800 °C WSi <sub>2</sub> |                     | WSi <sub>2</sub>                                            | WSi <sub>2</sub>                                            |  |  |

and crystalline phase were investigated. Figure 1 shows the Si/W atomic ratio of WSix layers deposited with various SiH<sub>4</sub>/WF<sub>6</sub> flow ratios, as determined by RBS measurements. We found that the Si/W atomic ratio, x, in the WSi<sub>x</sub> layer increased from 1.0 to 1.3 as the SiH<sub>4</sub>/WF<sub>6</sub> flow ratio was increased from 3 to 50. The resistivity of the  $WSi_x$  films also increased with increasing SiH<sub>4</sub>/WF<sub>6</sub> flow ratio, as shown in Fig. 2; it increased from 210 to 340  $\mu\Omega$  cm as the SiH<sub>4</sub>/WF<sub>6</sub> flow ratio was increased from 3 to 50. The increase in resistivity is presumably due to increasing amount of Si incorporated in the WSi, layer. Similar results were reported by Kottke et al. that higher flow ratios of SiH<sub>4</sub>/WF<sub>6</sub> resulted in WSi<sub>r</sub> films of higher resistivities and Si/W atomic ratios, although the WSix films in their study were deposited at a substrate temperature of 360 °C and a SiH<sub>4</sub>/WF<sub>6</sub> flow ratio of 94 to 438, and the resultant WSi<sub>x</sub> layers were nonstoichiometric silicon-rich (Si/W atomic ratios larger than 2.0).<sup>25</sup>

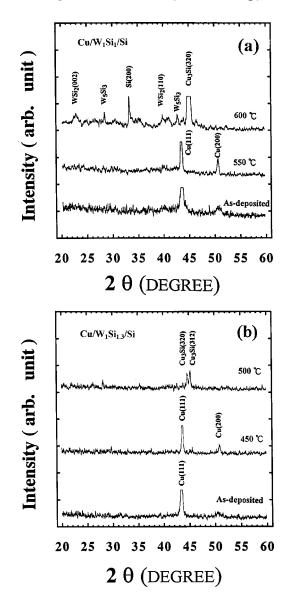

The phase of the WSi<sub>x</sub> layers was identified by XRD analysis using a 30 keV copper- $K\alpha$  radiation. Figures 3(a) and 3(b) show XRD spectra for the 150-nm-thick films with x=1 and 1.3 on silicon substrates before and after annealing at various temperatures. For x=1, the as-deposited films were amorphous and the amorphous state remained unchanged even after annealing at 600 °C for 30 min in N<sub>2</sub> ambient [Fig. 3(a)]. It has been reported that the absence of grain boundaries in the amorphous barrier layer contributes to the excellent barrier property, because fast diffusion paths of the grain boundaries are prevented.<sup>26</sup> In this work, the nature of amorphous phase makes the W1Si1 layers very attractive in barrier application. Diffraction peaks of WSi2 phase appeared in the W<sub>1</sub>Si<sub>1</sub> samples after annealing at 650 °C for 30 min in N<sub>2</sub> ambient [Fig. 3(a)], indicating silicidation of the layer.

For the  $W_1Si_{1.3}/Si$  samples, the as-deposited films were also amorphous [Fig. 3(b)]. Weak peaks of tungsten silicides were detected after annealing at 500 °C, and the diffraction peaks slightly intensified after annealing at 600 °C, indicating the grain growth of tungsten silicides. Similar results were reported that Si-rich (x>2.0) CVD films converted to tungsten silicides after annealing at 500 °C.  $^{27-29}$  We found that the crystallization temperature of amorphous CVD–WSi $_x$  layers decreased with increasing Si/W atomic ratio x. Table I summarizes the crystalline states of different CVD–WSi $_x$  films after annealing at various temperatures, as determined by XRD analysis.

### B. Composition effects on the barrier capability of $CVD-WSi_x$ films

#### 1. Electrical measurements

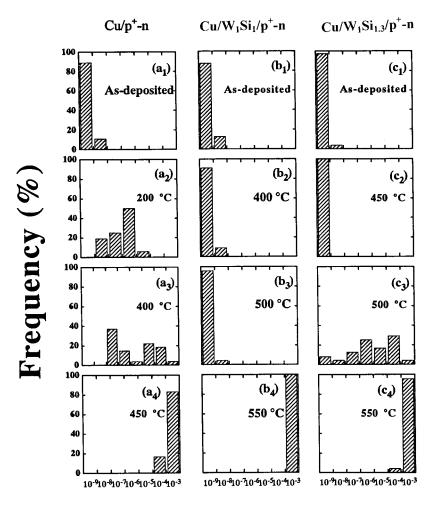

Figure 4 illustrates the statistical distributions of reverse bias current density measured at -5 V for the  $Cu/p^+-n$ ,  $Cu/W_1Si_1/p^+-n$ , and  $Cu/W_1Si_{1.3}/p^+-n$  junction diodes annealed at various temperatures; both layers of W1Si1 and W<sub>1</sub>Si<sub>1,3</sub> were 50 nm thick. Since copper reacts with Si at low temperatures (200 °C), 9,10 diodes without a barrier layer between Cu and Si substrate failed after annealing at 200 °C for 30 min [Fig. 4(a)]. With a 50-nm-thick WSi<sub>x</sub> barrier layer between Cu and Si substrate, the junction diodes of  $Cu/W_1Si_1/p^+-n$  and  $Cu/W_1Si_{1,3}/p^+-n$  were able to retain their electrical integrity up to 500 and 450 °C, respectively [Figs. 4(b) and 4(c)]. The barrier capability of amorphous WSi, layers decreased with increasing Si/W atomic ratio, and the decrease in thermal stability  $Cu/W_1Si_{1,3}/p^+-n$  junction diodes correlated with the lower crystallization temperature of the amorphous W<sub>1</sub>Si<sub>1,3</sub> layers.

#### 2. XRD analyses

The drastic increase in sheet resistance of the Cu/WSi<sub>x</sub>/Si samples was attributed to the formation of high resistivity  $\eta''$ -Cu<sub>3</sub>Si precipitates, as confirmed by XRD analyses shown in Fig. 5. The XRD spectra of as-deposited samples did not reveal the broadband of amorphous WSi, layers presumably because the WSi, layers were only 50 nm thick and were covered with 300-nm-thick Cu overlayers. Strong diffraction peaks of Cu<sub>3</sub>Si appeared in the XRD spectra of Cu/W<sub>1</sub>Si<sub>1</sub>/Si and Cu/W<sub>1</sub>Si<sub>1,3</sub>/Si samples annealed at 600 and 500 °C, respectively. It is clear that the stability of the WSi<sub>x</sub> layers in contact with Cu decreases with increasing Si/W atomic ratio. Furthermore, by comparing the XRD spectra of Cu/W<sub>1</sub>Si<sub>1</sub>/Si samples [Fig. 5(a)] with those of W<sub>1</sub>Si<sub>1</sub>/Si samples [Fig. 3(a)], we found that the crystallization temperature of WSi<sub>r</sub> layers in the Cu/W<sub>1</sub>Si<sub>1</sub>/Si samples is about 50 °C lower than that in the W<sub>1</sub>Si<sub>1</sub>/Si samples. This discrepancy is presumably due to the presence of Cu overlayers for the Cu/W<sub>1</sub>Si<sub>1</sub>/Si samples. It was reported that the crystallization temperature of W<sub>80</sub>Si<sub>20</sub> film on SiO<sub>2</sub> dropped from 800 to 650 °C when the W80Si20 film was in contact with a polycrystalline copper layer.<sup>30</sup> It was also reported that the formation temperature of tantalum (Ta) silicide in Ta/Si system dropped from 700 to 650 °C when the Ta film was in contact with a polycrystal-

Fig. 4. Histograms showing statistical distributions of reverse bias current density for (a)  $\text{Cu}/p^+-n$ , (b)  $\text{Cu}/\text{W}_1\text{Si}_1/p^+-n$ , and (c)  $\text{Cu}/\text{W}_1\text{Si}_{1,3}/p^+-n$  junction diodes annealed at various temperatures. The  $\text{WSi}_x$  layers are 50 nm thick.

### Reverse Bias Current Density (A/cm<sup>2</sup>)

line copper layer.<sup>31</sup> In this work, the  $W_1Si_1/Si$  samples remained stable up to 600 °C with no detection of tungsten silicide formation [Fig. 3(a)], while diffraction peaks of tungsten silicide phases were detected for the  $Cu/W_1Si_1/Si$  samples annealed at the same temperature [Fig. 5(a)]. This suggests that the accelerated crystallization for  $W_1Si_1$  layers was related to the contact with polycrystalline Cu overlayers. The accelerated crystallization is presumably due to the penetration of Cu atoms through  $W_1Si_1$  layers via localized defects, forming  $Cu_3Si$  phase and promoting silicidation at the  $W_1Si_1/Si$  interface.<sup>31</sup> Table II summarizes the silicides formed on thermally annealed Cu/Si and  $Cu/WSi_x/Si$  samples.

#### 3. SEM observations

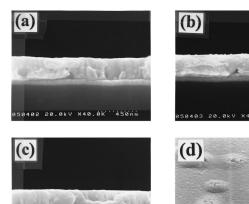

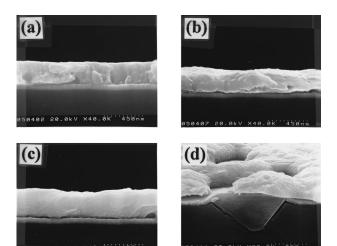

SEM was used to investigate the surface and cross-sectional morphology of thermally annealed Cu/barrier/ $p^+$ -n junction diodes. Figure 6 shows SEM micrographs for the as-deposited as well as 500 °C annealed Cu/W<sub>1</sub>Si<sub>1</sub>/ $p^+$ -n and Cu/W<sub>1</sub>Si<sub>1.3</sub>/ $p^+$ -n junction diodes. The barrier structure remained unchanged for the Cu/W<sub>1</sub>Si<sub>1</sub>/ $p^+$ -n diodes after annealing at 500 °C [Fig. 6(b)]; however, large localized Cu<sub>3</sub>Si protrusions were ob-

served on the  $\text{Cu/W}_1\text{Si}_{1.3}/p^+-n$  diodes after annealing at the same temperature [Fig. 6(d)]. Failure of the 500 °C annealed  $\text{Cu/W}_1\text{Si}_{1.3}/p^+-n$  diodes is likely associated with these localized  $\text{Cu}_3\text{Si}$  protrusions, which were presumably caused by the diffusion of Cu atoms through the weak points (such as vacancy-accumulated voids and grain boundaries of crystallized  $\text{W}_1\text{Si}_{1.3}$  layers) in the  $\text{W}_1\text{Si}_{1.3}$  barrier layers.

Based on the earlier results, we concluded that the higher the Si/W atomic ratio in  $WSi_x$  films is, the lower the crystallization temperature of the  $WSi_x$  films becomes (Fig. 3). Accordingly,  $WSi_x$  films of higher Si content are not suitable for diffusion barrier application. Moreover, failure of  $WSi_x$  barrier layer in the  $Cu/WSi_x/Si$  structure was closely related to the presence of  $Cu_3Si$  phase, indicating that the barrier failure was due to the interdiffusion of Cu and Si through the  $WSi_x$  barrier at elevated temperatures. This suggests that the thermal stability of  $Cu/WSi_x/p^+ - n$  diodes can be improved if the barrier structure of  $WSi_x$  can be modified so as to suppress or retard the interdiffusion of Cu and Si.

#### C. Effects of N<sub>2</sub> plasma treatment

It was reported that a very thin (4 nm) layer of WSiN formed on the surface of WSi<sub>x</sub> by electron cyclotron reso-

Fig. 5. XRD spectra of (a)  $\text{Cu/W}_1\text{Si}_1/\text{Si}$  and (b)  $\text{Cu/W}_1\text{Si}_{1,3}/\text{Si}$  samples annealed at various temperatures. The WSi<sub>1</sub> layers are 50 nm thick.

nance  $N_2$  plasma nitridation was able to function as an excellent barrier to dopant diffusion.<sup>32</sup> It was also reported that a  $WN_x$  layer about 2 nm thick was formed on the chemically vapor deposited tungsten (CVD-W) surface using a capacitively coupled plasma nitridation, and that the  $WN_x$  layer

TABLE II. Silicides formed on Cu/Si and Cu/WSi, /Si samples.

| Annealing            | Layered structure  |                                                                       |                                                                       |  |  |

|----------------------|--------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| temperatures<br>(°C) | Cu/Si              | Cu/W <sub>1</sub> Si <sub>1</sub> /Si                                 | Cu/W <sub>1</sub> Si <sub>1.3</sub> /Si                               |  |  |

| 200                  | Cu <sub>3</sub> Si | ×a                                                                    | ×                                                                     |  |  |

| 450                  | Cu <sub>3</sub> Si | X                                                                     | ×                                                                     |  |  |

| 500                  | Cu <sub>3</sub> Si | X                                                                     | Cu <sub>3</sub> Si, W <sub>5</sub> Si <sub>3</sub>                    |  |  |

| 550                  |                    | Cu <sub>3</sub> Si                                                    | Cu <sub>3</sub> Si, W <sub>5</sub> Si <sub>3</sub>                    |  |  |

| 600                  |                    | Cu <sub>3</sub> Si, W <sub>5</sub> Si <sub>3</sub> , WSi <sub>2</sub> | Cu <sub>3</sub> Si, W <sub>5</sub> Si <sub>3</sub> , WSi <sub>2</sub> |  |  |

| 650                  |                    | Cu <sub>3</sub> Si, WSi <sub>2</sub>                                  | Cu <sub>3</sub> Si, WSi <sub>2</sub>                                  |  |  |

a"X" indicates no observation of silicide phase.

Fig. 6. Cross-sectional view SEM micrographs of  $\text{Cu/W}_1\text{Si}_1/p^+-n$  diodes (a) as-deposited sample and (b) 500 °C annealed sample; SEM micrographs of  $\text{Cu/W}_1\text{Si}_{1,3}/p^+-n$  diodes; (c) cross-sectional view of as-deposited sample; and (d) oblique view of 500 °C annealed sample.

effectively suppressed the increase in resistance of thermally annealed Al/CVD–W/Si interconnects.<sup>33</sup> In addition, we found in a previous study that the barrier effectiveness of a 450-nm-thick selective CVD–W film in the structure of Al/CVD–W/Si can be significantly improved by exposing the W film in an *in situ* N<sub>2</sub> plasma prior to the Al metallization.<sup>34,35</sup> In this study, we insert a very thin WSiN layer between Cu and WSi<sub>x</sub> layers to make a structure of Cu/WSiN/WSi<sub>x</sub>/ $p^+$ –n junction diodes so as to suppress the undesirable interdiffusion between Cu and Si, and thus improve the thermal stability of the junction diodes. The very thin WSiN layer (shown latter in Fig. 8) was formed via an *in situ* N<sub>2</sub> plasma treatment on the surfaces of WSi<sub>x</sub> layers.

#### 1. Electrical measurements

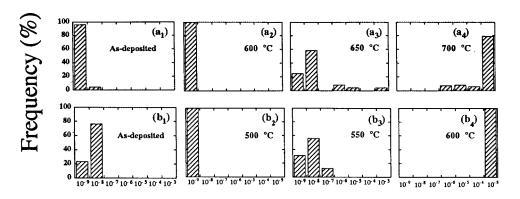

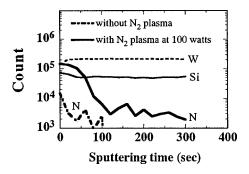

Figure 7 shows the statistical distributions of reverse bias current density for the  $Cu/WSiN/W_1Si_1/p^+-n$  and  $Cu/WSiN/W_1Si_{1,3}/p^+-n$  junction diodes annealed at various temperatures. All the Cu/WSiN/W<sub>1</sub>Si<sub>1</sub>/ $p^+$ -n junction diodes retained their integrity after annealing at temperatures up to 600 °C, and a large majority of the diodes still remained stable even after annealing at 650 °C [Fig. 7(a)]. This is more than 100 °C improvement in thermal stability over the Cu/W<sub>1</sub>Si<sub>1</sub>/ $p^+$ -n junction diodes [Fig. 4(b)], and is attributed to the very thin (about 5 nm) WSiN layer formed on the WSi<sub>x</sub> surfaces by the N<sub>2</sub> plasma treatment, as confirmed by the AES depth profiles shown in Fig. 8. It turned out that the very thin WSiN layer suppressed the diffusion of Cu, thus, the formation of Cu<sub>3</sub>Si was retarded and the accelerated crystallization of WSi, layers was suppressed, which in turn resulted in the improvement of thermal stability for the junc-

For the Cu/WSiN/W<sub>1</sub>Si<sub>1.3</sub>/ $p^+$ -n junction diodes, the devices remained stable after annealing at temperatures up to 500 °C, deteriorated slightly after annealing at 550 °C, and failed completely upon annealing at 600 °C [Fig. 7(b)]. This

Fig. 7. Histograms showing statistical distributions of reverse bias current density for (a) Cu/WSiN/W<sub>1</sub>Si<sub>1</sub>/ $p^+$ -n and (b) Cu/WSiN/W<sub>1</sub>Si<sub>1,3</sub>/ $p^+$ -n junction diodes annealed at various temperatures. The WSi<sub>x</sub> layers are 50 nm thick.

### Reverse Bias Current Density (A/cm<sup>2</sup>)

is an obvious improvement over the  $Cu/W_1Si_{1.3}/p^+-n$  junction diodes without  $N_2$  plasma treatment [Fig. 4(c)]. However, it is clear that the barrier capability of  $WSiN/W_1Si_{1.3}$  bilayer is inferior to that of  $WSiN/W_1Si_1$  bilayer. Failure of the  $WSiN/WSi_x$  barrier bilayers might be correlated with the crystallization temperature of  $WSi_x$  layers, which decreased with increasing Si/W atomic ratio in the  $WSi_x$  layers (Fig. 3).

#### 2. Sheet resistance measurements and XRD analyses

The normalized change in sheet resistance of annealed sample is defined as

$$\frac{\Delta R_S}{R_S} \% = \frac{R_{S_{\text{after anneal}}} - R_{S_{\text{as-deposited}}}}{R_{S_{\text{as-deposited}}}} 100\%.$$

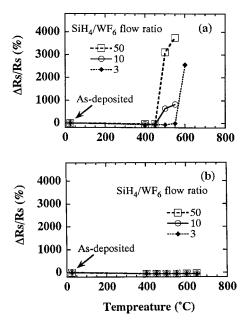

Figure 9 shows the change in sheet resistance of Cu/WSi<sub>x</sub>/Si and Cu/WSiN/WSix/Si samples annealed at various temperatures. All WSi<sub>r</sub> layers were 50 nm thick. The thermal stability of the Cu/W<sub>1</sub>Si<sub>1</sub>/Si samples reached 550 °C; however, a drastic increase in sheet resistance was found after annealing at 600 °C [Fig. 9(a)], implying failure of the Cu/W<sub>1</sub>Si<sub>1</sub>/Si structure. For the Cu/W<sub>1</sub>Si<sub>1,3</sub>/Si samples, the sheet resistance remained unchanged only up to 450 °C, and it increased drastically after annealing at 500 °C. The Cu/WSi<sub>r</sub>/Si structure with a WSi<sub>r</sub> barrier layer deposited at higher SiH<sub>4</sub>/WF<sub>6</sub> flow ratios was obviously less thermally stable. The sheet resistance for all samples of Cu/WSiN/WSi<sub>x</sub>/Si remained stable up to 650 °C, as shown in Fig. 9(b). Comparing these results with those of Cu/WSi<sub>r</sub>/Si samples shown in Fig. 9(a), we found that the barrier effectiveness of WSi<sub>x</sub> layers was improved significantly by forming a thin layer of WSiN on the surfaces of  $WSi_x$  via an *in situ*  $N_2$  plasma treatment.

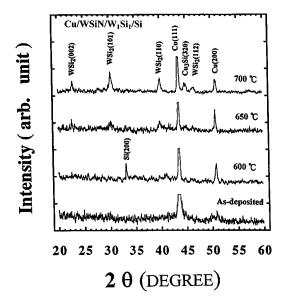

Figure 10 shows the XRD spectra of the Cu/WSiN/W<sub>1</sub>Si<sub>1</sub>/Si samples after annealing at various temperatures. Instead of the formation of various silicides for the 600 °C annealed Cu/W<sub>1</sub>Si<sub>1</sub>/Si samples [Fig. 5(a)], no silicide phase was detected for the Cu/WSiN/W<sub>1</sub>Si<sub>1</sub>/Si samples annealed at 600 °C. This indicates that the accelerated crystallization of WSi<sub>x</sub> layers in contact with a polycrystalline Cu overlayer was suppressed by the presence of a thin WSiN layer sandwiched between the Cu and WSi<sub>x</sub> layers. It has

been reported that a uniform ultrathin (<1 nm) WSiN barrier layer can be formed at the interface of WN/poly-Si by thermal annealing, and the WSiN layer was able to suppress the silicidation reaction between W and poly-Si up to 800 °C. <sup>36</sup> In this study, the very thin but much chemically and thermally stable WSiN layer contributed to retarding the diffusion of copper and suppressing the accelerated crystallization of WSi<sub>x</sub>; thus, the barrier effectiveness of the amorphous CVD–WSi<sub>x</sub> layers is significantly improved.

#### 3. SEM observations

Figure 11 shows SEM micrographs  $Cu/WSiN/W_1Si_1/p^+-n$  junction diodes before and after thermal annealing at various temperatures. The barrier structure remained unchanged after annealing at temperatures up to 600 °C [Fig. 11(b)]. After annealing at 650 °C, some of the diodes were degraded while the others remained intact | Fig. 7(a)]. For the diodes that remained intact after annealing, the cross-sectional SEM micrograph shows that the barrier structure remained unchanged [Fig. 11(c)]. Upon annealing at 700 °C, many large openings were found on the diodes' surfaces, and the fully developed Cu<sub>3</sub>Si precipitates exhibiting a feature of inverted pyramid shape bounded by Si {111} planes were also observed [Fig. 11(d)]. Thus, failure of the WSiN/W1Si1 barrier bilayers was likely associated with these highly localized precipitates, which were presumably caused by the diffusion of Cu through the weak points (such

Fig. 8. AES depth profiles of  $WSi_x/Si$  samples with and without  $N_2$  plasma treatment showing the difference in nitrogen distribution; the sputtering rate was determined to be about 0.1 nm/s.

Fig. 9. Change in sheet resistance vs annealing temperature for (a)  $Cu/WSi_x/Si$  and (b)  $Cu/WSiN/WSi_x/Si$  samples with the  $WSi_x$  layers deposited at various  $SiH_4/WF_6$  flow ratios.

as stress-induced microcracks and grain boundaries of the crystallized W<sub>1</sub>Si<sub>1</sub> layer) in the thermally annealed barrier layers. The results of SEM observations further confirm that the thermal stability of the Cu/WSi<sub>x</sub>/Si structure can be improved significantly by forming a thin layer of WSiN on the surfaces of WSi<sub>x</sub> via an *in situ* N<sub>2</sub> plasma treatment. The thermal stability temperatures of WSi<sub>x</sub>-based barrier layers determined by various techniques of measurement and/or analysis are summarized in Table III.

Fig. 10. XRD spectra of Cu/WSiN/W $_1\mathrm{Si}_1/\mathrm{Si}$  sample annealed at various temperatures.

Fig. 11. Cross-sectional and oblique view SEM micrographs for the  $Cu/WSiN/W_1Si_1/p^+-n$  junction diodes (a) as-deposited, and (b) 600, (c) 650, and (d) 700 °C annealed.

#### **IV. SUMMARY**

The thermal stability of thin amorphous CVD–WSi<sub>x</sub> layers, with and without N<sub>2</sub> plasma treatment, was investigated with respect to the capability of diffusion barrier between Cu and Si substrate. We found that the barrier effectiveness depended on the composition of WSi<sub>x</sub> films. The amorphous WSi<sub>x</sub> films deposited with higher flow ratios of SiH<sub>4</sub>/WF<sub>6</sub> have higher Si/W atomic ratios as well as lower crystallization temperatures; thus, the barrier effectiveness of the WSi<sub>x</sub> films was lowered. For the 50-nm-thick W<sub>1</sub>Si<sub>1</sub> layers deposited with a  $SiH_4/WF_6$  flow ratio of 3, the  $Cu/W_1Si_1/p^+-n$ junction diodes were able to sustain a 30 min thermal annealing at temperatures up to 500 °C without causing degradation to the electrical characteristics. The thermal stability was lowered to 450 °C for the Cu/W<sub>1</sub>Si<sub>1,3</sub>/ $p^+$ -n junction diodes using the W<sub>1</sub>Si<sub>1.3</sub> barrier layers deposited with a SiH<sub>4</sub>/WF<sub>6</sub> flow ratio of 50. The barrier capability of WSi<sub>x</sub> films can be efficiently improved by an in situ N<sub>2</sub> plasma treatment. The N<sub>2</sub> plasma treatment produced a very thin layer of WSiN on the surfaces of WSi<sub>x</sub> layers, and the WSiN/WSi<sub>x</sub> bilayers not only suppressed the diffusion of Cu efficiently, but also prevented the accelerated crystallization of WSix layers in case of direct contact with the Cu overlayers, resulting in improvement on barrier capability. With an in situ N2 plasma

TABLE III. Thermal stability temperatures of WSi<sub>x</sub>-based barrier layers determined by different techniques of measurement/analysis.

|                                     | Barrier layers                         |                                       |                                             |                                               |

|-------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------------|-----------------------------------------------|

| Measurement and/or analysis methods | W <sub>1</sub> Si <sub>1</sub><br>(°C) | W <sub>1</sub> Si <sub>1.3</sub> (°C) | WSiN/W <sub>1</sub> Si <sub>1</sub><br>(°C) | WSiN/W <sub>1</sub> Si <sub>1.3</sub><br>(°C) |

| Reverse current                     | 500                                    | 450                                   | 600                                         | 500-550                                       |

| Sheet resistance                    | 550                                    | 450                                   | 650                                         | 650                                           |

| XRD                                 | 550                                    | 450                                   | 600                                         | 600                                           |

| SEM                                 | 500                                    | 450                                   | 600-650                                     | 500-550                                       |

treatment applied to the  $W_1Si_1$  barrier, the  $Cu/WSiN/W_1Si_1/p^+-n$  junction diodes were able to remain intact up to at least 600 °C.

#### **ACKNOWLEDGMENT**

This work was supported by the National Science Council (ROC) under Contract No. NSC87-2215-E-009-72.

- <sup>1</sup>R. J. Gutmann, T. P. Chow, A. E. Kaloyeros, W. A. Lanford, and S. P. Murarka, Thin Solid Films **262**, 177 (1995).

- <sup>2</sup>N. Awaya, H. Inokawa, E. Yamamoto, Y. Okazaki, M. Miyake, Y. Arita, and T. Kobayashi, IEEE Trans. Electron Devices ED-43, 1206 (1996).

- <sup>3</sup>S. P. Murarka, R. J. Gutmann, A. E. Kaloyeros, and W. A. Lanford, Thin Solid Films **236**, 257 (1993).

- M. Dubin and Y. S. Diamand, J. Electrochem. Soc. **144**, 898 (1997).

D. H. Kim, R. H. Wentorf, and W. N. Gill, J. Electrochem. Soc. **140**, 3273 (1993).

- <sup>6</sup>J. C. Chiou, K. C. Juang, and M. C. Chen, J. Electrochem. Soc. **142**, 177 (1995).

- <sup>7</sup>S. Wolf and R. N. Tauber, *Silicon Processing for the VLSI Era* (Lattice, Sunset Beach, CA, 1986), Vol. II, pp. 268, 273.

- <sup>8</sup>C. A. Chang, J. Appl. Phys. **67**, 566 (1990).

- <sup>9</sup>S. D. Brotherton, J. R. Ayres, A. Gill, H. W. V. Kesteren, and F. J. A. M. Greidanus, J. Appl. Phys. **62**, 1826 (1987).

- <sup>10</sup>Y. S. Diamand, A. Dedhia, D. Hoffstetter, and W. G. Oldham, J. Electrochem. Soc. **140**, 2427 (1993).

- <sup>11</sup>A. L. S. Loke, C. Ryu, C. P. Yue, J. S. H. Cho, and S. S. Wong, IEEE Electron Device Lett. EDL-17, 549 (1996).

- <sup>12</sup>J. O. Olowolafe, J. Li, J. W. Mayer, and E. G. Colgan, Appl. Phys. Lett. 58, 469 (1997).

- <sup>13</sup>S. D. Kim, S. G. Jin, M. R. Hong, and C. T. Kim, J. Electrochem. Soc. 144, 664 (1997).

- <sup>14</sup>H. Ono, T. Nakano, and T. Ohta, Jpn. J. Appl. Phys., Part 1 **34**, 1827 (1995).

- <sup>15</sup>P. J. Pokela, C.-K. Kwok, E. Kolawa, S. Raud, and M.-A. Nicolet, Appl. Surf. Sci. **53**, 364 (1991).

- <sup>16</sup>E. Kolawa, J. S. Chen, J. S. Reid, P. J. Pokela, and M.-A. Nicolet, J. Appl. Phys. **70**, 1369 (1991).

- <sup>17</sup>T. Oku, E. Kawakami, M. Uekubo, K. Takahiro, S. Yamaguchi, and M. Murakami, Appl. Surf. Sci. 99, 265 (1996).

- <sup>18</sup>M. Takeyama, A. Noya, T. Sase, and A. Ohta, J. Vac. Sci. Technol. B **14**, 674 (1996).

- <sup>19</sup>J. Y. Lee and J. W. Park, Jpn. J. Appl. Phys., Part 1 **35**, 4280 (1996).

- <sup>20</sup>V. P. Anitha, A. Bhattacharya, N. G. Patil, and S. Major, Thin Solid Films 236, 306 (1993).

- <sup>21</sup>S. Q. Wang, J. Appl. Phys. **73**, 2301 (1993).

- <sup>22</sup>J. C. Chiou, K. C. Juang, and M. C. Chen, J. Electrochem. Soc. **142**, 2326 (1995).

- <sup>23</sup>M.-A. Nicolet, Thin Solid Films **107**, 415 (1978).

- <sup>24</sup>J. S. Reid, R. Y. Liu, P. M. Smith, R. P. Ruiz, and M.-A. Nicolet, Thin Solid Films **262**, 218 (1995).

- <sup>25</sup>M. Kottke, F. Pintchovski, T. R. White, and P. J. Tobin, J. Appl. Phys. **60**, 2835 (1986).

- <sup>26</sup>T. Nakano, H. Ono, T. Ohta, T. Oku, and M. Murakami, VMIC Proceedings (1994), p. 407.

- <sup>27</sup>Y. Shioya and M. Maeda, J. Appl. Phys. **60**, 327 (1986).

- <sup>28</sup>K. C. Saraswat, D. L. Brors, J. A. Fair, K. A. Monnig, and R. Beyers, IEEE Trans. Electron Devices ED-30, 1497 (1983).

- <sup>29</sup>D. K. Sadana, A. E. Morgan, M. H. Norcott, and S. Naik, J. Appl. Phys. 62, 2830 (1987).

- <sup>30</sup>J. S. Reid, E. Kolawa, R. P. Ruiz, and M.-A. Nicolet, Thin Solid Films 236, 319 (1993).

- <sup>31</sup>K. Holloway, P. M. Fryer, C. Cabral, Jr., J. M. E. Harper, P. J. Bailey, and K. H. Kelleher, J. Appl. Phys. 71, 5433 (1992).

- <sup>32</sup>A. Hirata, T. Hosoya, K. Machida, H. Takaoka, and H. Akiya, J. Electrochem. Soc. **143**, 3747 (1996).

- <sup>33</sup>M. Sekiguchi, T. Fujii, and M. Yamanaka, Jpn. J. Appl. Phys., Part 2 35, 1111 (1996).

- <sup>34</sup>M. T. Wang, P. C. Wang, M. C. Chuang, L. J. Chen, and M. C. Chen, J. Vac. Sci. Technol. B 16, 2026 (1998).

- <sup>35</sup>Y. Shioya, T. Itoh, S. Inoue, and M. Maeda, J. Appl. Phys. **58**, 4194 (1985).

- <sup>36</sup>Y. Akasaka et al., VMIC Proceedings (1995), p. 168.