Home Search Collections Journals About Contact us My IOPscience

Electrical and material characterization of atomic-layer-deposited  $Al_2O_3$  gate dielectric on ammonium sulfide treated GaAs substrates

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2008 J. Phys.: Conf. Ser. 100 042002 (http://iopscience.iop.org/1742-6596/100/4/042002) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11 This content was downloaded on 26/04/2014 at 02:52

Please note that terms and conditions apply.

Journal of Physics: Conference Series 100 (2008) 042002

# Electrical and material characterization of atomic-layer-deposited $Al_2O_3$ gate dielectric on ammonium sulfide treated GaAs substrates

Chao-Ching Cheng,<sup>1</sup> Chao-Hsin Chien,<sup>1,2,\*</sup> Guang-Li Luo,<sup>2</sup> Ching-Chih Chang,<sup>1</sup> Chi-Chung Kei,<sup>3,4</sup> Chun-Hui Yang,<sup>2</sup> Chien-Nan Hsiao,<sup>3</sup> Tsong-Pyng Perng,<sup>4</sup> and Chun-Yen Chang<sup>1</sup>

<sup>1</sup> Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, R.O.C.

<sup>2</sup> National Nano Device Laboratory, Hsinchu, Taiwan 300, R.O.C.

<sup>3</sup> Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu, Taiwan 300, R.O.C.

<sup>4</sup> Department of Material Science and Engineering, National Tsing-Hua University, Hsinchu, Taiwan 300, R.O.C.

\*E-mail: chchien@faculty.nctu.edu.tw

Abstract. This paper has studied the electrical and interfacial properties of atomic-layerdeposited  $Al_2O_3$  thin film on ammonium-sulfide passivated GaAs. It was found that the  $Al_2O_3$ deposited at 300°C relative to that at 100°C showed the nearly four orders of magnitude reduction in gate leakage current at the capacitance-equivalent-thickness of 40 Å. The capacitance–voltage (*C*–*V*) characteristics displayed the higher oxide capacitance, reduced frequency dispersion and less charge trapping when GaAs receiving (NH<sub>4</sub>)<sub>2</sub>S sulfide immersion; these improvements can be reasonably explained by the suppression of both native oxides and the resultant improved interface quality. Annealing as-deposited  $Al_2O_3/GaAs$ structures at high temperatures further reduces the Fermi level pinning effect on accumulation capacitance, however, causes an increase in *C*–*V* frequency dispersion and gate leakage current. We suggested that these phenomena are strongly associated to the amount of As-related defects resided at the dielectric/substrate interface during thermal desorption.

# 1. Introduction

Novel device structures, channel materials, and gate dielectrics are required to further extend Si-based complementary-metal-oxide-semiconductor (CMOS) front-end fabrication beyond the 22 nm node. One oncoming strategy is to heterogeneous integration of III-V compound materials as transport channels with high-*k* dielectrics on traditional Si or silicon on insulator. However, the absence of thermodynamically stable insulators on III-V compound semiconductors, e.g., (In)GaAs and InSb, etc, have become the foremost bottleneck to III-V technology rivaling or exceeding the properties of Si MOSFETs. For more than four decades, numerous efforts have been devoted in intensively questing the competitive, high interface quality insulators and efficient passivation methods, respectively. Except for SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>, (Gd,Ga)<sub>2</sub>O<sub>3</sub> and atomic-layer-deposited (ALD) Al<sub>2</sub>O<sub>3</sub> [1], HfO<sub>2</sub> [2] high-*k*

| IVC-17/ICSS-13 and ICN+T2007                                   | IOP Publishing                     |  |

|----------------------------------------------------------------|------------------------------------|--|

| Journal of Physics: Conference Series <b>100</b> (2008) 042002 | doi:10.1088/1742-6596/100/4/042002 |  |

dielectrics are of particular interest; meanwhile, the sulfur chemical treatment [3], and Si and Ge [4] as the interfacial passivation layers (IPLs) are currently active approaches to protect the III-V surface prior to the dielectric deposition. This study presented the impact of the surface preparation processes, especially for ammonium sulfide (NH<sub>4</sub>)<sub>2</sub>S immersion, and post-deposition annealing (PDA) on the improvement of interface quality of Pt/ALD-Al<sub>2</sub>O<sub>3</sub>/GaAs MOS structures.

# 2. Experimental

Highly-doped n-type GaAs wafers with the doping concentration of ca. 1 x  $10^{18}$  cm<sup>-3</sup> were used. All samples were precleaned by the acetone (ACE) and rinsed by deionized water. Subsequently, HCl-based acid-solutions with various diluted concentration were tested in GaAs cleaning and ammonium sulfide (NH<sub>4</sub>)<sub>2</sub>S aqua solution was used for surface passivation. We employed x-ray photoelectron spectroscopy (XPS) with an Al K $\alpha$  radiation source to examine the surface chemical bonding prior to high-*k* layer deposition. The Al<sub>2</sub>O<sub>3</sub> thin films were deposited by ALD system at substrate temperatures of 100 and 300°C; Trimethylaluminum, Al(CH<sub>3</sub>)<sub>3</sub>, and H<sub>2</sub>O were chosen as the metal source and oxidant pulsed alternatively into the reactor for 1 s per pulse separated by N<sub>2</sub> purge of 10 s to remove redundant reactants. Subsequent PDA in an O<sub>2</sub> ambient performed at 600°C was used for film densification. The top Pt capacitance electrode was formed via a shadow mask with the area of ca. 4 x  $10^{-4}$  cm<sup>2</sup> and Al metal was deposited as the backside contact. The capacitance–voltage (*C–V*) and gate leakage current (*I–V*) curves were measured using an HP4284 and Keithley 4200, respectively.

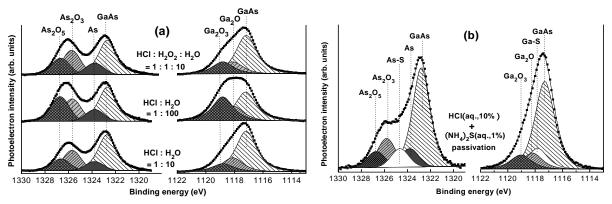

Figure 1. As 2p3 and Ga2p3 XPS spectra of GaAs surfaces after (a) different acid-solution cleanings and (b) (NH<sub>4</sub>)<sub>2</sub>S(aq.) sulfide passivation.

### 3. Results and Discussion

Figure 1(a) displays the As2*p3* and Ga2*p3* core level spectra of GaAs surface after three different acid cleaning solutions; the peak position and contribution of all chemical components are identified. Clearly, an increase in the concentration of HCl solution assisted to reduce the As-rich layer and both kinds of the native oxides,  $As_2O_x$  and  $Ga_2O_x$ . Adding  $H_2O_2$  in HCl solution, like the standard clean-2 (SC-2) in RCA, however, seems to further oxidize the GaAs surface with the increased As layer formation. The immersion in (NH<sub>4</sub>)<sub>2</sub>S solution further reduced the As metal and most of native oxides, especially for the  $As_2O_x$ , as photoemission spectra shown in Fig. 1(b). The sulfur-based chemical treatment effectively passivated GaAs dangling bonding, by forming As-S and Ga-S chemical bonds at GaAs surface.

We calculated the composition ratios of all contributed components through XPS fitting and summarized the results in Table I. It was found that the higher HCl concentration can diminish the amount of  $Ga_2O_x$  with respect to the  $As_2O_x$ , leading to thin As-oxide rich surface, which is consistent with the previous report that the acid-etched GaAs wafer revealed both As-oxide and As rich surfaces [5]. During sulfide passivation, Ga atoms have a higher probability than As atoms in bonding to sulfur atoms; this can be attributed to lower bonding strength of As-S chemical bonds.

IOP Publishing doi:10.1088/1742-6596/100/4/042002

| Journal of Physics: Conference Series 100 (2008) 04200 |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Wet Clean                    | As-As/As <sub>Total</sub> | As-S/As <sub>Total</sub> | Ga-S/Ga <sub>Total</sub> | As <sub>2</sub> O <sub>x</sub> /As <sub>Total</sub> | Ga2Ox/GaTotal |

|------------------------------|---------------------------|--------------------------|--------------------------|-----------------------------------------------------|---------------|

| $HCl: H_2O_2: H_2O = 1:1:10$ | 12.7 %                    |                          |                          | 44.9 %                                              | 37.9 %        |

| $HCl: H_2O = 1:100$          | 12.0 %                    |                          |                          | 48.6 %                                              | 56.9 %        |

| $HCl: H_2O = 1:10$           | 11.1 %                    |                          |                          | 39.6 %                                              | 34.2 %        |

| HCl (aq.,10%) + Sulf.(80°C)  | 9.7 %                     | 9.8 %                    | 14.8 %                   | 23.7 %                                              | 22.1 %        |

Table I. Chemical bonding ratios calculated by XPS fitting results in Fig. 1 and Fig. 2.

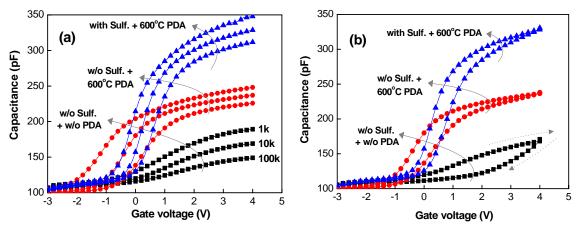

The frequency-dependent and bidirectional C-V curves of Pt/Al<sub>2</sub>O<sub>3</sub>/n-GaAs MOS capacitors are shown in Figs. 3(a) and 3(b), respectively. As can be seen, the as-deposited sample apparently showed C-V stretch-out behavior accompanying with the lower oxide capacitance; the clockwise hysteresis width was also presented. Even though annealing the sample at 600°C in an O<sub>2</sub> ambient exhibited the higher accumulation capacitance, it also caused a large flat-band voltage ( $V_{FB}$ ) shift with respect to the measured frequency, implying the generation of slow states at and/or close to the interface. As the (NH<sub>4</sub>)<sub>2</sub>S treatment was further employed, the highest accumulation capacitance with steep C-V slope presented; meanwhile, the smaller hysteresis behavior was also found. We suggested that the sulfide passivation can improve the interface quality between Al<sub>2</sub>O<sub>3</sub> high-*k* dielectric and GaAs substrate due to the native oxide suppression and enhanced thermal stability.

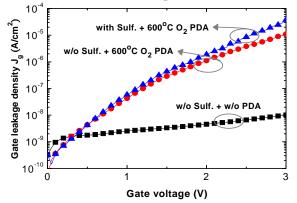

Figure 4 shows the corresponding I-V characteristics. It was noticed that high-temperature PDA obviously increased the gate leakage current  $J_g$  by more than two orders, at gate bias  $V_g$  above 2 V. From XPS analysis (not shown here), we found that a small amount of As metal and both native oxides have been incorporated into bulk Al<sub>2</sub>O<sub>3</sub> during annealing; the resultant contamination are believed to be responsible for a huge increase in  $J_g$ .

Figure 3. (a) Multi-frequency *C*-*V* and (b) bidirectional *C*-*V* (10 kHz) curves of Pt/ALD- $Al_2O_3/n^+$ -GaAs capacitors with different cleaning preparation and annealing processes. The  $Al_2O_3$  thin films were deposited at 100°C for 60 cycles.

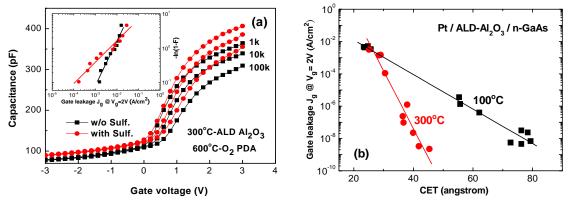

The quality of Al<sub>2</sub>O<sub>3</sub> deposited at 300°C on GaAs are examined in Fig. 5(a); the inset shows the Weibull plot of  $J_g$  distribution at  $V_g = 2V$ . The (NH<sub>4</sub>)<sub>2</sub>S-treated sample relative to the HCl-last sample exhibited the higher oxide capacitance and smaller C-V frequency dispersion, which is similar to the examination in ALD-Al<sub>2</sub>O<sub>3</sub> at 100°C. The corresponding  $J_g$  seemed to be slightly lower than that in the sample without sulfide process, but, with the broad distribution in the Weibull plot, reflecting the fact that the distribution of sulfur bonding is an important role in gate leakage performance. Besides, as illustrated in Fig. 5(b), all 300°C-Al<sub>2</sub>O<sub>3</sub> samples were found to show the better gate leakage

performance, where the nearly four orders of magnitude reduction in  $J_g$  at the capacitance-equivalent-thickness (CET) of 40 Å, with respect to the 100°C-Al<sub>2</sub>O<sub>3</sub> samples.

Figure 4. Gate leakage current  $J_g$  characteristics of Pt/Al<sub>2</sub>O<sub>3</sub>/n-GaAs capacitors. The Al<sub>2</sub>O<sub>3</sub> thin films were deposited at 100°C for 60 cycles.

## 4. Conclusions

We investigated the interfacial chemistry of  $(NH_4)_2S$ -passivated GaAs and the electrical properties with ALD-Al<sub>2</sub>O<sub>3</sub> as gate dielectric. The improvements in *C*–*V* characteristics after sulfur surface treatment, including the higher oxide capacitance, reduced frequency dispersion, and less charge trapping, can be reasonably attributed to the reduction of the native oxide formation and improved interface quality. Further, the Al<sub>2</sub>O<sub>3</sub>/GaAs structure undergoing high-temperature annealing possessed higher accumulation capacitance, however, caused an obvious  $V_{FB}$  shift in frequency-dependent *C*–*V* curves and increased gate leakage  $J_g$ . We suggested that these phenomena depended on the amount of As-related defects remained at the dielectric/substrate interface during thermal processing. In addition, the Al<sub>2</sub>O<sub>3</sub> deposited at 300°C relative to that at 100°C showed the nearly four orders of magnitude reduction in  $J_g$  at the CET of 40 Å.

Figure 5. (a) *C-V* curves of GaAs MOS capacitors with ALD-Al<sub>2</sub>O<sub>3</sub> deposited at 300°C for 60 cycles and (b) Comparison of  $J_g$  versus CET characteristics of ALD-Al<sub>2</sub>O<sub>3</sub>/GaAs capacitors deposited at 100 and 300°C with different surface preparation and annealing processes.

### References

- H.-L. Lu, L. Sun, S.-J. Ding, M. Xu, D. W. Zhang, and L.-K. Wang 2006 Appl. Phys. Lett. 89 152910

- [2] M. Zhu, C.-H. Tung, and Y.-C. Yeo 2006 Appl. Phys. Lett. 89 202903

- [3] M.-K. Lee, C.-F. Yen, J.-J. Huang, and S.-H. Lin 2006 J. Electrochem. Soc. 153 F266

- [4] H.-S. Kim, I. Ok, M. Zhang, T. Lee, F. Zhu, L. Yu, and J. C. Lee 2006 Appl. Phys. Lett. 89 222903

- [5] J. S. Song, Y. C. Choi, S. H. Seo, D. C. Oh, M. W. Cho, T. Yao, and M. H. Oh 2004 J. Cry. Growth 264 98