## Transient effects of positive oxide charge on stress-induced leakage current in tunnel oxides

Nian-Kai Zous, Tahui Wang, Chih-Chich Yeh, C. W. Tsai, and Chimoon Huang

Citation: Applied Physics Letters 75, 734 (1999); doi: 10.1063/1.124497

View online: http://dx.doi.org/10.1063/1.124497

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/75/5?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Stress-induced leakage current and random telegraph signal J. Vac. Sci. Technol. B **27**, 435 (2009); 10.1116/1.3054269

Two-trap model for low voltage stress-induced leakage current in ultrathin SiON dielectrics

J. Appl. Phys. 104, 053718 (2008); 10.1063/1.2969791

Effect of magnetic field on random telegraph noise in the source current of p-channel metal—oxide—semiconductor field-effect transistors

Appl. Phys. Lett. 83, 710 (2003); 10.1063/1.1596381

Improved model for the stress-induced leakage current in thin silicon dioxide based on conduction-band electron and valence-band electron tunneling

J. Appl. Phys. **91**, 1577 (2002); 10.1063/1.1429799

Analysis of the stress-induced leakage current and related trap distribution

Appl. Phys. Lett. 75, 3871 (1999); 10.1063/1.125484

APPLIED PHYSICS LETTERS VOLUME 75, NUMBER 5 2 AUGUST 1999

## Transient effects of positive oxide charge on stress-induced leakage current in tunnel oxides

Nian-Kai Zous, Tahui Wang, a) Chih-Chich Yeh, and C. W. Tsai Department of Electronics Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan, Republic of China

## Chimoon Huang

Winbond Electronics, Hsin-Chu, Taiwan, Republic of China

(Received 18 December 1998; accepted for publication 3 May 1999)

The role of positive oxide charge in excess low-level leakage current in tunnel oxides induced by Fowler/Nordheim stress is investigated. A correlation between stress-induced gate current and substrate current in an *n*-channel metal-oxide-semiconductor field-effect transistor is observed. Both the gate current and the substrate current exhibit a significant transient effect. The mechanisms of the stress-induced currents and their field dependence are explored. Positive oxide charge tunnel detrapping is found to be the cause of the observed transient behavior in the two currents. The stress-created positive oxide charge can be significantly annealed by substrate hot electron injection. © 1999 American Institute of Physics. [S0003-6951(99)02226-3]

High field stressing during program/erase cycles in flash electrical erasable programmable read-only memory (EE-PROM) operation can lead to an increase in pretunneling leakage current in a tunnel oxide. Stress induced leakage current (SILC) has received much attention recently because of its important significance to the data retention and endurance characteristics of a flash memory cell. Although extensive research has been performed on SILC, its physical mechanisms still remain controversial. Dumin<sup>1</sup> and Ricco<sup>2</sup> have shown that neutral trap assisted tunneling is the original cause of SILC. DiMaria and Carter<sup>3</sup> concluded that positive oxide charge plays no part in the SILC conduction mechanism in oxides by Fowler/Nordheim (FN) stress. On the other side, Teramoto et al.4 claimed that the excess leakage current induced by FN stress is due to the injected holes produced by high energy electrons. Matsukawa et al.5 have further shown that the positive oxide charge induced leakage current<sup>6</sup> can be reduced by hot electron injection or ultraviolet (UV) irradiation. More recently, results by Meinertzhagen et al. have shown that the role of positive oxide charge in SILC changes with stress and measurement polarities. In negative gate bias FN stress, positive charge is created near the Si/SiO<sub>2</sub> surface<sup>8</sup> and thus plays a more important role in SILC measured at a positive field.

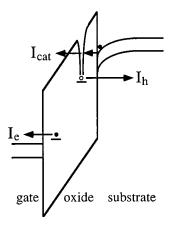

injection contains a transient component and a dc component. In their work, the transient current is attributed to negative oxide charge trapping/detrapping and can be characterized by a 1/t time dependence. Moreover, we have shown that positive oxide charge assisted tunneling current also exhibits a transient effect. 10 The transient behavior arises from the positive oxide charges, which help electrons to tunnel through the oxide, and can themselves escape to the Si substrate in measurement. As a result, the SILC transient should consist of three components in general,  $I_e$ ,  $I_h$ , and  $I_{cat}$  as

In order to measure the stress induced  $I_g$  and  $I_b$  at a small gate bias directly, a large gate area n-channel metaloxide semiconductor field-effect transistor (n-MOSFET) is specially fabricated. The gate area is  $8 \times 10^{-3}$  cm<sup>2</sup> and the tunnel oxide thickness is about 100 Å. Both positive gate

FIG. 1. Illustration of three SILC transient components,  $I_a$ ,  $I_b$ , and  $I_{cat}$  at a positive measurement gate bias. The full circles and the open circle represent electrons and holes, respectively.

In addition, Dumin and Maddux<sup>9</sup> found that SILC by FN

illustrated in Fig. 1, if both positive and negative oxide charges are created during stress. Ie represents negative oxide charge detrapping induced current,  $I_h$  is positive oxide charge detrapping current, and  $I_{\text{cat}}$  denotes positive oxide charge assisted electron tunneling current.  $I_e$  and  $I_h$  have a  $t^{-1}$  time dependence from the tunneling front model<sup>9</sup> while  $I_{\text{cat}}$  has a  $t^{-n}$  time dependence in a certain range of the measurement field. The power factor n is dependent on effective electron and hole tunneling barrier heights and tunneling masses.  $^{10}$  It should be mentioned that  $I_h$  is a hole current flowing to the substrate and  $I_e$  and  $I_{\rm cat}$  are an electron current flowing to the source or the drain. Hence,  $I_h$  can be monitored separately at the substrate while the difference of the gate current  $(I_g)$  and the substrate current  $(I_h)$  accounts for the sum of  $I_e$  and  $I_{cat}$ .

a)Electronic mail: wang@jekyll.ee.nctu.edu.tw

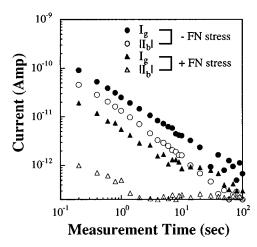

FIG. 2. Stress induced  $I_g$  and  $|I_b|$  transients in *n*-MOSFETs by +FN stress and -FN stress, respectively. The measurement gate bias is +4 V.

bias FN (+FN) stress and negative gate bias FN (-FN) stress are performed. The positive trapped charge effects on SILC in the two stressed devices are compared.

Figure 2 shows the transient characteristics of  $I_g$  and  $I_b$ by +FN stress and -FN stress. The +FN stress is performed at  $V_{gs}$  = 9.5 V for 400 s and the -FN stress is at  $V_{gs}$ =-9.5 V for 400 s. The measurement gate bias is +4 V. In the figure, the -FN stress apparently has a larger SILC. This result is also seen by other researchers<sup>11</sup> and the reason will be given. Another feature to be noted in Fig. 2 is the existence of a significant substrate current in the -FN stressed device. In -FN stress, electrons emitted from the gate gain kinetic energy in SiO2 and produce electron-hole pairs by band gap impact ionization in the Si substrate. Then, the generated holes are injected into the gate oxide. The appearance of the substrate current arises from the discharging of the stress created hole traps and provides direct evidence that positive oxide charge detrapping constitutes an important part in the -FN SILC. Conversely, we performed the same measurement in the +FN stressed device and  $I_b$  is about two orders of magnitude smaller. This distinguished difference suggests that the FN stress created positive charges have a very asymmetrical distribution in the oxide and are accumulated near the anode.8 The larger SILC with opposite stress and measurement polarities therefore can be explained by the positive charge detrapping current and the associated positive charge assisted electron tunneling current.

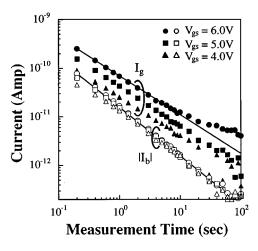

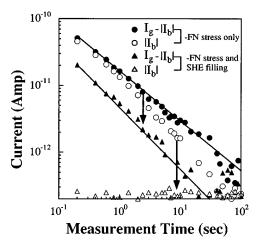

Furthermore, we plot  $I_g$  and  $I_b$  in the  $-{\rm FN}$  stressed device at various measurement voltages in Fig. 3. After each I-t scanning, the  $-{\rm FN}$  stress is applied for 20 s to refill the generated oxide traps. The measurement in Fig. 3 is repeated two times and no significant difference is noticed. The measured SILC and  $I_b$  follow a power law time dependence, i.e., a straight line on a log-log scale in Fig. 3. However, a close look at the time dependence of the SILC and  $I_b$  reveals that they have a slightly different power factor, especially at a relatively large gate bias. The solid lines in the figure represent a linear fit to the measured results at  $V_{gs} = 6$  V. The extracted slope is about -0.75 for  $I_g$  and is -1 for  $I_b$ . The  $t^{-0.75}$  time dependence of  $I_g$  reflects the component of  $I_{cat}$ . The slight deviation of  $I_g$  from the straight line at  $V_{gs} = 6$  V and the scanning of the longer than 20 s is due to a decomposition of  $I_g$  and  $I_g$  and  $I_g$  and  $I_g$  and  $I_g$  and  $I_g$  are solved in the scanning of  $I_g$  and  $I_g$  are solved in the scanning of  $I_g$  and  $I_g$  are  $I_g$  and  $I_g$  and  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  are  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  are  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  are  $I_g$  are  $I_g$  and  $I_g$  are  $I_g$  and  $I_g$  are  $I_$

FIG. 3. The measurement time dependence of  $I_g$  and  $|I_b|$  in a -FN stressed n-MOSFET. The measurement gate voltages are +4.0, +5.0, and +6.0 V. The open symbols represent  $I_b$  and the full symbols represent  $I_g$ . The solid lines represent a linear fit to the measured result at  $V_{gg} = +6.0$  V.

ponent in the SILC. In addition, Fig. 3 shows that  $I_g$  has a stronger dependence on the measurement gate bias than  $I_b$  does. As mentioned previously,  $I_b$  is caused by positive oxide charge detrapping. The weak field dependence of positive oxide charge detrapping is realized due to a trapezoidal barrier for hole tunneling and a large tunneling barrier height. On the other side,  $I_g$  is contributed, to a larger extent, by the electron tunneling currents  $I_e$  and  $I_{\rm cat}$ . Perhaps because of a smaller effective electron tunneling barrier or a smaller electron tunneling mass, the electron tunneling current exhibits a stronger field dependence. Moreover, the distortion of the local oxide field by a positive trapped charge also makes the electron tunneling barrier somewhat look like a triangular barrier (Fig. 1) and thus increases the field dependence of  $I_{\rm cat}$ .

The stress created positive oxide charge can be annealed by using a substrate hot electron (SHE) injection technique. The SHE injection is applied at  $V_{gs} = 2.5$  V and  $V_b = -7$  V for 20 s. Since the injection current is large, the positive trapped charges are neutralized via injected electron and trapped hole recombination. The effects of positive charge neutralization on -FN SILC and  $I_b$  are shown in Fig. 4. The

FIG. 4. Transient characteristics of the electron leakage component ( $I_g = |I_b|$ ) and the hole leakage component ( $|I_b|$ ) in the -FN SILC with and without SHE filling.

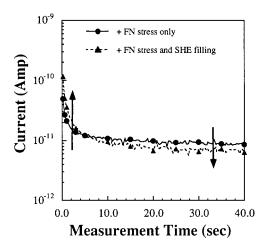

FIG. 5. The time dependence of the +FN SILC with and without SHE filling. The measurement gate bias is +6 V.

measurement gate bias is 4 V. In the figure, the arrows indicate the change of the currents. After the SHE filling,  $I_h$  is completely suppressed and the total electron tunneling current  $(I_g - I_b)$  reduces to about only one-third of its prefilling level. The reduction of the total electron current results from the annealing of  $I_{cat}$ . The remaining electron current accounts for the component  $I_e$ . In fact,  $I_e$  is increased after the filling because more electrons are trapped in the oxide. In other words,  $I_{\text{cat}}$  should occupy at least two-thirds of the total electron leakage component in the -FN SILC. The solid lines in the figure represent a linear fit to the electron tunneling currents without and with the SHE filling. The SHE filling effect on +FN SILC is also examined in Fig. 5. The measurement gate bias is +6 V. The +FN SILC contains both transient and dc components. The transient component is mostly due to  $I_e$  since  $I_b$  is small (Fig. 2). The mechanisms for the dc component are neutral trap assisted tunneling and positive charge assisted tunneling although the amount of positive oxide charges near the Si/SiO<sub>2</sub> surface is small. Unlike the -FN SILC, the transient component of the +FN SILC increases while its dc component declines after the filling. The increase of the transient current results from more electrons stored in the oxide. The decrease of the dc component is attributed to the annihilation of positive charge assisted tunneling. The post-SHE filling dc leakage is still above the leakage current level in a fresh device and is believed due to neutral trap assisted tunneling.

In conclusion, we have observed a positive oxide charge detrapping induced substrate current in a -FN stressed n-MOSFET. The substrate current follows strictly a 1/t time dependence. A correlation between the SILC and stress induced substrate current is noticed. At a small positive oxide field,  $I_b$  is the major component of SILC while at a medium oxide field the electron tunneling current becomes dominant. The role of positive oxide charge in +FN SILC and -FN SILC has been clarified. Our study concludes that positive oxide charge plays an important role in the transient component of -FN SILC and in the dc component of +FN SILC. The stress created positive oxide charge can be annealed by substrate hot electron injection.

The authors would like to acknowledge financial support from National Science Council, Republic of China, under Contract No. NSC88-2215-E009-034.

<sup>&</sup>lt;sup>1</sup>D. J. Dumin, R. S. Scott, and R. Subramoniam, IEEE Proceedings of the International Reliability Phys. Symposium, Atlanta (1993), p. 288.

<sup>&</sup>lt;sup>2</sup>B. Ricco, G. Gozzi, and M. Lanzoni, IEEE Trans. Electron Devices **45**, 1554 (1998).

<sup>&</sup>lt;sup>3</sup>D. J. DiMaria and E. Cartier, J. Appl. Phys. **78**, 3883 (1995).

<sup>&</sup>lt;sup>4</sup>A. Teramoto, K. Kobayashi, Y. Matsui, M. Hirayama, and A. Yasouka, IEEE Proceedings of the International Reliability Phys. Symposium, Dallas (1996), p. 113.

<sup>&</sup>lt;sup>5</sup>N. Matsukawa, S. Yamada, K. Amemiya, and H. Hazama, IEEE Trans. Electron Devices **43**, 1924 (1996).

<sup>&</sup>lt;sup>6</sup>J. Maserjian and N. Zamani, J. Vac. Sci. Technol. **20**, 743 (1982).

<sup>&</sup>lt;sup>7</sup> A. Meinertzhagen, C. Petit, M. Jourdain, and F. Mondon, J. Appl. Phys. **84**, 5070 (1998).

<sup>&</sup>lt;sup>8</sup>Y. B. Park and D. K. Schroder, IEEE Trans. Electron Devices 45, 1361 (1998).

<sup>&</sup>lt;sup>9</sup>D. J. Dumin and J. R. Maddux, IEEE Trans. Electron Devices **40**, 986

<sup>&</sup>lt;sup>10</sup> T. Wang, N. K. Zous, J. L. Lai, and C. Huang, IEEE Electron Device Lett. 19, 411 (1998).

<sup>&</sup>lt;sup>11</sup>R. S. Scott and D. J. Dumin, IEEE Trans. Electron Devices 43, 130 (1996).