# Application of Selective Liquid-Phase Deposition to Fabricate Contact Holes Without Plasma Damage

Ching-Fa Yeh, <sup>z</sup> Chien-Hung Liu, and Jwinn-Lein Su

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan

This work develops an alternative method, selective liquid-phase deposition (S-LPD), to fabricate contact holes instead of reactive ion etching. In preliminary experiments, deep  $n^+/p$  junction diodes with contact holes prepared by S-LPD exhibit much less reverse current, unity ideality factor, larger forward current, lower contact resistance, and higher thermal stability than those prepared by reactive ion etching. Further superiority of plasma damage-free near-surface regions is also investigated using Schottky and ultra-shallow junction diodes. Experimental results indicate that S-LPD can be applied to the submicron contact-hole process. The data after reverse bias temperature stress reveals the satisfactory reliability of S-LPD contact holes. This work demonstrates that the S-LPD technology is a highly promising means of replacing reactive ion etching processes to form submicron contact holes as reliably as those by wet-etching.

© 1999 The Electrochemical Society. S0013-4651(98)08-119-1. All rights reserved.

Manuscript submitted August 31, 1998; revised manuscript received February 17, 1999.

Owing to its anisotropic etching ability, reactive ion etching (RIE) is extensively used to etch silicon oxide to form contact holes or interconnect vias. However, because of inevitable energetic ions and fluoride radicals in the plasma ambient, RIE causes damage, defects, polymer residue, and radical contamination<sup>1-5</sup> on etched surfaces, and induces oxide traps in the SiO<sub>2</sub> or interface states at the SiO<sub>2</sub>/Si interface.<sup>6-8</sup> Therefore, the reverse current, contact resistance, and oxide leakage of devices are inevitably enlarged due to the undesirable effects described previously.<sup>5,9,10,11</sup> Currently, the issue of RIE selectivity has become increasingly critical in ultrashallow junctions because overetch is less tolerated. To alleviate these problems on RIE-etched silicon surfaces, several modified and complex dry-etching techniques, e.g., magnetically enhanced reactive ion etching (MERIE), <sup>2,12</sup> and electron cyclotron resonance (ECR) plasma etching, <sup>10,13</sup> have been developed. Many different etchant sources, e.g., CF<sub>4</sub>, CH<sub>x</sub>F<sub>4-x</sub>, NF<sub>3</sub>, SF<sub>6</sub>, SiF<sub>4</sub>, BCl<sub>3</sub>, and HBr etc., have also been developed to increase etching selectivity or reduce the effects of impurities and defects on the etched surface. 14 Several severe postcleaning and post-treatment methods after RIE have also been developed to remove damage or polymer residues. 5,15-17 Although these post-treatment techniques have been improved once again and the RIE apparatuses have gradually become extremely expensive, RIE cannot be compared with conventional wet-etching in the integrity of the etched surface. 9,10,16 In addition, to improve the overetch problem, many techniques, e.g., laser interferometry, optical emission spectroscopy (OES), invasive Langmuir probes, and radio-frequency power monitoring, have been developed as an end-point detector. 18-20 Despite additional equipment and high cost, each proposed technique has drawbacks and limitations.

To avert these problems, an alternative method without RIE etching must be developed. Our previous studies have investigated liquid-phase deposition (LPD) technology,  $^{21-24}$  and applied it to the gate insulator of thin-film transistors (TFTs).  $^{25,26}$  Many physical and chemical characteristics, such as Auger electron spectroscopy (AES) analysis,  $^{21,22}$  Fourier transform infrared (FTIR) spectra,  $^{22,24}$  X-ray photoelectron spectroscopy (XPS) measurement,  $^{24}$  extraction of interface trap,  $^{25}$  film stress measurement,  $^{23}$  stress hysteresis,  $^{23}$  etc., for LPD dielectric films have been surveyed and analyzed in our proposed papers.  $^{21-25}$  The LPD technique has also been applied to form the interlayer dielectric (ILD) in multilevel tungsten interconnect structures.  $^{28}$  These studies confirm that LPD oxide possesses excellent electrical properties, low dielectric constant (k) $^{22}$  and low stress.  $^{23}$  Due to low stress, LPD oxide exhibits fewer trap states than plasma-enhanced chemical vapor deposited (PECVD) oxide at the oxide/Si interface.  $^{23,25,27}$  This reveals there is a better interface state

between silicon and LPD oxide than conventional PECVD oxide. Especially, LPD oxide can be selectively deposited against photoresist if the deposition condition is adequately controlled.<sup>29,30</sup> This implies the feasibility of applying selective LPD (S-LPD) to create contact holes or vias. In addition, the cost of LPD apparatus is quite low, because no vacuum facilities and no corresponding etching monitors are necessary. In this work, we first apply S-LPD to form contact holes for n<sup>+</sup>/p diodes, Schottky diodes, and Kelvin resistors and thereby study the superiority of utilizing plasma-free S-LPD over the conventional RIE. It is expected that in addition to forming contact holes with submicron meter scale as RIE, S-LPD can also obtain device performance comparable to wet etching.

## Experimental

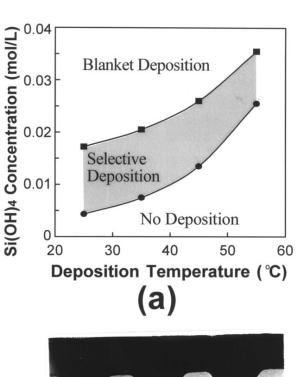

The process and mechanism of S-LPD have been described in our previous literatures.  $^{29\text{-}31}$  Figure 1a indicates that the process window of S-LPD is a function of silicic acid Si(OH)\_4 concentration and deposition temperature. In this work, we mainly perform the S-LPD under a condition at Si(OH)\_4 concentration of  $7.3\times10^{-3}$  mol/L and 23°C. The SEM photograph in Fig. 1b shows the LPD oxide is selectively deposited against photoresist. It preliminarily reveals the absence of particles and indicates the feasibility of forming half-micrometer contact holes with a high aspect ratio.

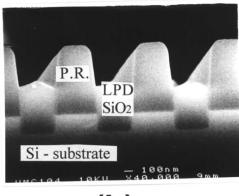

The devices, including n<sup>+</sup>/p diodes, Schottky diodes, and Kelvin resistors, were fabricated with their contact holes prepared using S-LPD and RIE, respectively. The p-type (100) wafers with 15-25  $\Omega$ cm bulk resistivity were adopted in the n<sup>+</sup>/p diodes and Kelvin resistor fabrication. Following the formation of channel stopper and field oxide, phosphorus with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> and energy of 40 keV was implanted to make n<sup>+</sup>/p junction, and then the 30 min annealing at N<sub>2</sub> 900°C was performed for dopant activation. As shown in the left portion of Fig. 2, for S-LPD samples the photoresist on the area defined as the site of contact hole was kept intact. Next, the LPD oxide was selectively grown on the region without photoresist by using S-LPD. After removing the photoresist, the contact holes were automatically formed. For RIE samples, as shown in the right portion of Fig. 2, LPD oxide was globally deposited to cap the n<sup>+</sup>/p diodes. Then the contact holes were defined through lithography and etched using RIE. To increase the etching selectivity of SiO<sub>2</sub>/Si<sup>14</sup> and reduce chamber particles,<sup>32</sup> the RIE was performed under the following conditions: a CHF<sub>3</sub>/O<sub>2</sub>, ratio of 20/5 sccm, 50 mTorr pressure, and 100 W rf power. Before metallization, the contact holes of both S-LPD and RIE were cleaned sequentially with  $H_2SO_4/H_2O_2$ ,  $NH_4OH/H_2O_2$ ,  $HCl/H_2O_2$ , and diluted HF solution (standard RCA cleaning). In addition to Al/Si contact, for some samples, 20 nm thick titanium was used between Al and Si to serve as a titanium silicide barrier to reduce spiking. The purpose of using a

z E-mail: cfyeh@cc.nctu.edu.tw

single Ti barrier is due to low resistance with respect to using TiN/Ti barrier or Al:Si(1-2%) alloy. Especially for Al:Si/n<sup>+</sup>-Si contact, an undesirable increase in contact resistance arises from silicon precipitates which occur preferentially around the contact hole edges. After metallization, some n<sup>+</sup>/p junction diodes were sintered at 400°C for 30 min in N<sub>2</sub>. The temperatures of all processes after S-LPD are below 500°C, the outgassing temperature of fluorine in LPD dielectric,  $^{22}$  so there is no effect due to fluorine outgassing. In addition to n<sup>+</sup>/p diodes, the Kelvin resistors were also fabricated under an identical conditions. For Schottky diodes, the fabrication procedures closely resembled those of n<sup>+</sup>/p diodes except for use of 1-5  $\Omega$  cm, n-type (100) wafers and the fact that no ion-implantation was necessary.

Subsequently, we further applied S-LPD to the ultrashallow  $\rm n^+/p$  junction diodes. All processes closely resembled those mentioned previously except (i) the  $\rm n^+$  region was prepared with 5 keV, As<sup>+</sup>,  $\rm 2\times 10^{15}~cm^{-2}$ , and then annealed with rapid thermal annealing (RTA) in the  $\rm N_2$  ambient. (ii) For the RIE sample, the partial-RIE (P-RIE) was employed to etch contact holes. The P-RIE refers to a situation in which most of the capping oxide thickness was etched with RIE and then the remaining oxide of about 20-30 nm was wet-etched by buffer HF solution. This modification attempts to reduce the RIE overetch, because etching rate nonuniformity easily leads to overetch-through in ultrashallow junctions. (iii) To resemble the common RIE process, P-RIE samples were prepared by using plas-

Figure 1. (a) Process window and (b) SEM photograph for S-LPD.

Figure 2. Process-flow diagram of  $n^+/p$  junction diodes with contact hole fabricated by S-LPD (left) or conventional RIE (right).

ma-enhanced chemical vapor deposited tetraethylorthosilicate (PE-TEOS) oxide as a capping layer. The PE-TEOS oxide was deposited in the TEOS/O $_2$  ratio of 10/200 sccm, 300 mTorr pressure, and 200 W power. (iv) Titanium thickness of all ultrashallow  $n^+/p$  diodes was reduced to 12 nm.

#### **Results and Discussion**

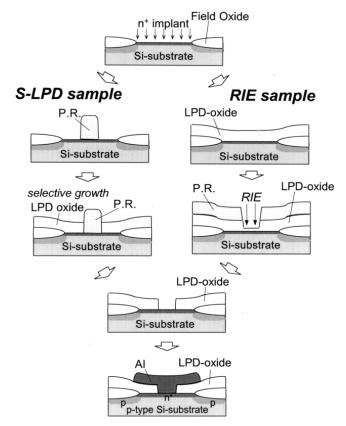

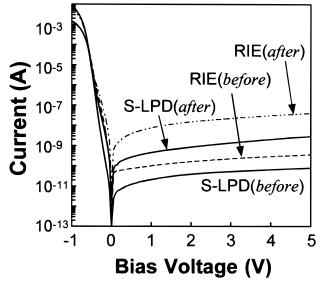

$n^+/p$  junction diode.—Figure 3 shows the typical current-voltage (I-V) characteristics of n<sup>+</sup>/p diodes with contact holes prepared by S-LPD and RIE before and after sintering, respectively. The metal contact of Al/n<sup>+</sup>-Si is  $60 \times 60 \mu m$ , while the junction area is  $100 \times 10^{-1}$ 100 µm. According to this figure, before sintering the reverse current of S-LPD samples is one order less than that of RIE. As for the forward bias, the ideality factor,  $\eta$ , of 1.13 in S-LPD samples is also superior to that of 1.57 in RIE samples. This indicates that relatively few generation-recombination (G-R) centers are in the depletion region of S-LPD diodes such that  $\eta$  approaches 1. Table I summarizes several key characteristic parameters. The reverse current ratio of 400  $\times$  400  $\mu$ m diodes to 100  $\times$  100  $\mu$ m diodes ( $I_{400}/I_{100}$ ) is 3.27 for the S-LPD sample, while it is 5.15 for the RIE sample. The  $I_{400}/I_{100}$  ratio of 5.15 exceeds the geometry ratio of the junction perimeter, i.e.,  $1600/400 \mu m = 4$ . From the fitting with the equation  $I_{\rm R} = J_{\rm RA} \times L^2 + J_{\rm RP} \times (4L)$ , where  $J_{\rm RA}$  and  $J_{\rm RP}$  are the partial current densities due to junction area leakage and junction periphery leakage, respectively, the factor of  $I_{400}/I_{100} > 4$  indicates that the effect of  $J_{\rm RA}$  is rather significant for the RIE sample. The RIE method easily causes lattice defects and bonding defects, which function as deep-level traps<sup>1,34</sup> and donor-like charge states,<sup>35</sup> respectively. For the contact etched by CHF<sub>3</sub>, it has been detected by deep-level transient spectroscopy (DLTS) that a dominant trap arises from H(0.40) Si defects and locates at about 0.65 eV above the valence band. These states and traps serve as G-R centers and significantly enlarge the reverse current. In addition, fluorine-contained ion bombardment and permeation also cause soft breakdown.<sup>36</sup> These factors account for why the reverse current is rather high for

Figure 3. Comparison of I-V characteristics between  $n^+/p$  diodes with S-LPD and RIE contact (Al/Si) holes.

RIE samples. After sintering, the reverse current of RIE samples increases drastically. This large leakage magnitude after sintering indicates a spiking enhanced by RIE damage. It has been proposed that RIE can damage the etched surface to become as rough as 30 nm and makes the spiking effect easily occur during sintering treatment. In contrast, S-LPD can avoid a large reverse current owing to no plasma-induced defects and no energetic ion bombardment damages during contact hole formation.

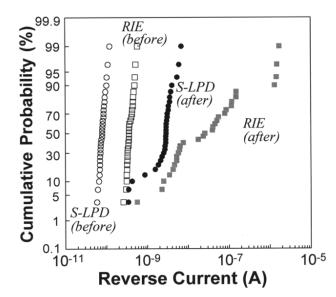

Figure 4 shows the performance of S-LPD and RIE diodes with Al/Ti/Si contact, respectively. Before sintering, the I-V characteristics of S-LPD samples are still superior to those of RIE samples. After sintering, both the reverse currents increase, while RIE samples increase more significantly than S-LPD samples. This can be attributed to many defects and contamination induced by RIE diffusing from contact-hole surfaces into the junction depletion region during sintering. In particular, the metallic contamination sputtered from the RIE chamber wall enlarges reverse current after sintering. The Having no such drawbacks, the S-LPD samples exhibit relatively good thermal stability. Figure 5 shows the accumulative distribution for the reverse

Table I. Comparison for key characteristic parameters of diodes and ohmic contacts between S-LPD and RIE contact holes.

|                                                                                    | S-LPD                | RIE                      |

|------------------------------------------------------------------------------------|----------------------|--------------------------|

| n <sup>+</sup> /p diode                                                            |                      |                          |

| Ideality factor $\eta$ (Al/Si)<br>(-0.4 to -0.5 V) <sup>a</sup>                    | 1.13                 | 1.57                     |

| Dimension current ratio $I_{400}/I_{100}$ (5.0 V) <sup>a</sup>                     | 3.27                 | 5.15                     |

| Ideality factor $\eta$ (Al/Ti/Si)<br>(-0.4 to -0.5 V)                              | 1.17                 | 1.64                     |

| Ohmic Contact resistivity $\rho_{ce}$ $(\Omega \text{ cm}^2)^b$ Sobottly, diedo    | $2.5 \times 10^{-6}$ | $\sim 12 \times 10^{-6}$ |

| Schottky diode<br>Schottky $\eta_{sc}$ (0.1-0.3 V)<br>Schottky barrier height (eV) | 1.11<br>0.83         | >3.0<br>0.60             |

| Ultrashallow $n^+/p$ diode Ideality factor $\eta$ (-0.4 to -0.5 V)                 | 1.03                 | 1.13 <sup>c</sup>        |

<sup>&</sup>lt;sup>a</sup> Diodes with Al/Si contact considered before sintering.

**Figure 4.** Comparison of I-V characteristics between  $n^+/p$  diodes with S-LPD and RIE contact (Al/Ti/Si) holes before and after sintering.

currents of all measured diodes. For S-LPD samples, the reverse currents distribute in a more confined region; however, for RIE samples, they separate from nanoampere to microampere magnitude. This finding indicates another superiority that S-LPD has no nonuniformity problem of RIE etching rate. The superiority of S-LPD can avoid the problem of defects, contamination, rough-etched surfaces, and etching rate nonuniformity caused by RIE. These results preliminarily prove the superiority of S-LPD replacing RIE to form contact holes.

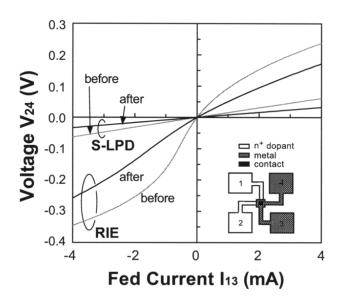

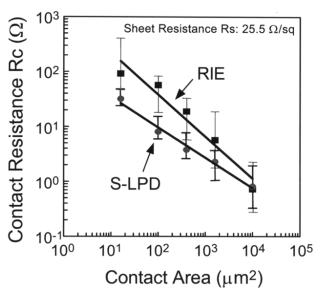

Ohmic contact resistance.—According to Fig. 3 and 4, the forward current of S-LPD samples is larger than that of RIE samples at forward bias -1.0 V, whether a titanium barrier is used or not. This implies that applying S-LPD can effectively reduce forward series resistance. Because all processes are the same except the contacthole formation, it is believed that for RIE samples, the additional resistance must result from contact resistance. To investigate contact resistance, we further fabricated four-terminal Kelvin D-resistors,  $^{39}$  as illustrated in the Fig. 6 inset. The  $^+$  doping region of sheet resistance  $^{25.5}$   $\Omega/\square$  was adopted for all resistors. The Kelvin contact

**Figure 5**. Cumulative distribution for reverse currents, at reverse bias 5.0 V, of all measured S-LPD and RIE  $n^+/p$  diodes before and after sintering.

<sup>&</sup>lt;sup>b</sup> Sheet resistance,  $R_s$ , 25.5  $\Omega/\Box$ .

<sup>&</sup>lt;sup>c</sup> P-RIE was adopted.

resistance,  $R_{\rm C}$ , is defined by the voltage 2 to 4 over the fed current 1-3, i.e., the curve slope of  $V_{24}$ - $I_{13}$  plot. Figure 6 depicts the typical  $R_{\rm C}$  characteristics of the resistor with the contact size  $L \times L = 10 \times 10^{-2}$  $10^{\circ}$  µm and the collar width d = 10 µm at the fed current ranging from -4 to 4 mA. The S-LPD contact shows a linear I-V relationship and exhibits a smaller  $R_C$  than the RIE contact. Meanwhile, the RIE contact shows a nonlinear I-V relationship and therefore exhibits a nonconstant and larger  $R_C$  value, especially at the small fed current. This occurrence is because in the RIE process, the polymer and photoresist residues are difficult to be cleaned owing to the energetic plasma bombardment.<sup>5</sup> In addition, the large  $R_{\rm C}$  can also be attributed to the decreased mobility in the etched surface. 40 Interestingly, the impurities and residues impinged by RIE scatter the drift electrons and holes, thereby reducing the effective mobility. Owing to the scattering, the drift carriers are scattered rather seriously if they move at a low velocity. This is the reason the  $R_C$  of RIE contact becomes large, particularly in small fed current, and exhibits nonlinear I-V characteristics. For S-LPD contact, it is relatively easy to clean the photoresist residues because of no energetic bombardment. Therefore, the I-V characteristics show linearity with low slope and exhibit the superiority of being plasma-damage free.

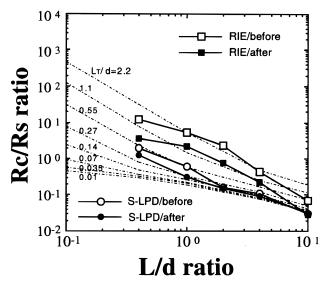

Figure 7 depicts the relationship between contact resistance,  $R_{\rm C}$ , and different contact-hole sizes for the S-LPD and RIE samples. According to this figure, the S-LPD contacts always exhibit a lower contact resistance than the RIE ones for all contact-hole sizes. In addition, compared to RIE contacts, the  $R_{\rm C}$  reduction has a tendency of becoming more apparent in small contact-hole sizes. On the other hand, the  $R_{\rm C}$  values vs. the contact-hole sizes exhibit a linear trend with about −1 slope, regardless of whether for S-LPD or RIE samples. This indicates that our Kelvin resistors can eliminate most of the parasitic resistance and thus can be used to extract specific contact resistivity,  $\rho_{Ce}$ , and make  $\rho_{Ce}$  close to the actual contact resistivity  $\rho_{\rm C}$ .<sup>39</sup> To extract the  $\rho_{\rm Ce}$ , we incorporate the measured  $R_{\rm C}$ values with different L/d ratio into the simulated universal curves of Kelvin D-resistors. As shown in Fig. 8, for resistors with different L/d ratios, the  $R_C/R_S$  values of S-LPD samples are much smaller than those of RIE samples. Following the extraction procedures of  $\rho_{Ce}$ , <sup>41</sup> the specific Al/Si contact resistivity,  $\rho_{\text{Ce}},$  as listed in Table I, is about  $2.5 \times 10^{-6} \ \Omega \ \text{cm}^2$  for the S-LPD contacts; however, it is about 12- $13 \times 10^{-6} \,\Omega$  cm<sup>2</sup> for the RIE contacts. Because the contact resistivity is very sensitive to the cleanness and integrity at the metal/Si interface, the specific  $\rho_{\text{Ce}}$  of RIE must be larger than that of S-LPD.

Schottky diodes and ultrashallow  $n^+/p$  junction diodes.—Now that the S-LPD method has been preliminarily shown feasible to

Figure 6. V-I plot of Kelvin D-resistors with S-LPD and RIE contact holes, respectively.

**Figure 7.** Comparison of contact resistance,  $R_{\rm C}$ , between S-LPD and RIE contact holes for different contact sizes.

replace RIE in contact-hole formation, especially in damage-free and contamination-free processes to further prove its excellence without plasma, the performance in near-surface regions is next investigated thru Schottky and ultrashallow junction diodes.

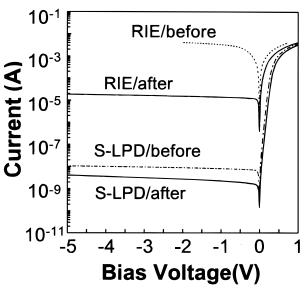

Schottky diodes.—Figure 9 depicts the performance of S-LPD and RIE Schottky diodes with Al/n-Si (1-5  $\Omega$  cm) contact before/after N<sub>2</sub> 400°C sintering, and Table I also summarizes their key characteristic parameters. Before sintering, the RIE sample nearly loses the rectifying characteristics of a Schottky diode under reverse bias, while the S-LPD sample exhibits satisfactory Schottky characteristics. However, after sintering, the S-LPD sample still exhibits about four orders smaller than that of RIE sample in reverse current. Meanwhile, the ideality factor 1.11 of the former is lower than 4.05 of the latter. The worse ideality of RIE samples is attributed to the large surface recombination velocity. According to the curves of  $\ln\{I/[1-\exp(-qV/kT)]\}$  vs. forward-bias voltage, the potential barrier is 0.83 eV for the S-LPD Schottky diodes and 0.60 eV for the RIE ones, respectively. As generally contended, the donor-like bonding defects and the polymer residues make the depletion region

**Figure 8.** Measured  $R_{\rm C}/R_{\rm S}$  within simulated universal curves for the Kelvin D-resistors with S-LPD and RIE contact holes, respectively.

**Figure 9.** Comparison of I-V characteristics between Schottky diodes with S-LPD and RIE contact holes, before and after sintering (Al/n-Si contact area  $500 \times 500 \mu m$ ).

thin<sup>43</sup> and lower the potential barrier. These results indicate that for the RIE Schottky diodes, the sintering is essential to release some of the residues and the defects from the Si surface but is unnecessary for the S-LPD sample. Accordingly, the RIE process becomes more critical and requires additional post-treatment.<sup>16</sup> S-LPD can avert these problems and is indeed a highly promising candidate as a plasma-damage-free, energetic-impurity-free, and polymer-residue-free technology.

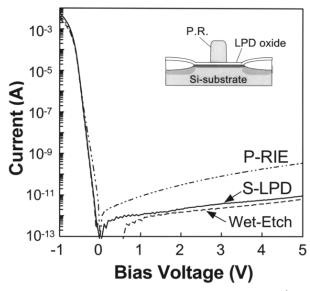

Ultrashallow  $n^+/p$  junction diodes.—Because the demand for plasma-damage free technology has been increasingly urgent in fabricating deep submicron devices, the S-LPD technique was next applied to the formation of contact holes for ultrashallow n<sup>+</sup>/p junctions. Herein, the junction depth estimated with TSUPRUM-4 is about 20-30 nm, while the implantation of 5 keV  $\mathrm{As^+}$ ,  $2 \times 10^{15} \, \mathrm{cm^{-2}}$ is adopted, and following with 15 s, 1050°C RTA. While fabricating the ultrashallow junction diodes, the RIE samples were modified by applying PE-TEOS capping and partial-RIE (P-RIE). Meanwhile, to segregate all lithography residues from the contact region, a simple modification of S-LPD was performed with a thin LPD-oxide (15-20 nm) globally deposited before lithography, as illustrated in the Fig. 10 inset. After finishing S-LPD and removing the photoresist, the thin LPD oxide was removed by dipping buffer HF solution and then the contamination-free contact holes were formed. Besides the large area samples with the Al/Ti/n<sup>+</sup>-Si contact area of  $60 \times 60 \mu m$  and the  $\rm n^+/p$  junction area of 100  $\times$  100  $\mu m$ , the submicron samples with junction area of 2.8  $\times$  50  $\mu m$  and 25 contact holes of 0.8  $\times$  0.8  $\mu m$ were also fabricated. Photoresist removal and cleaning for the submicron samples was performed by 60 s ozone ashing of 300°C and followed by RCA cleaning. In addition to S-LPD and P-RIE, the reference samples (wet-etch) with LPD-oxide capping and completely butter HF wet-etching were also prepared.

Figure 10 shows the typical I-V characteristics of ultrashallow junction diodes with  $60 \times 60 \mu m$  contact holes prepared by S-LPD, wet-etch, and the P-RIE method, respectively, after sintering. The S-LPD diodes as well as wet-etch reference diodes exhibit nearly identical I-V characteristics in both forward bias and reverse bias. This proves that applying S-LPD can form excellent diodes comparable to the wet-etch reference diode. By contrast, the P-RIE diodes still exhibit two orders higher reverse current than the S-LPD ones at 5.0 V. This can be attributed to some energetic ions or accelerated radicals penetrating through the 20-30 nm remaining oxide into the Si substrate. In addition, the microtrenching effect<sup>44</sup> due to ion reflection from the photoresist sidewall also causes overetch at the

**Figure 10.** Comparison of I-V characteristics among ultrashallow n<sup>+</sup>/p junction diodes with S-LPD, wet-etch (LPD), and P-RIE (PE-TEOS) contact holes (Al/Ti/Si contact) after sintering.

contact periphery and enhanced penetration. However, these undesirable problems never occur in the S-LPD diodes.

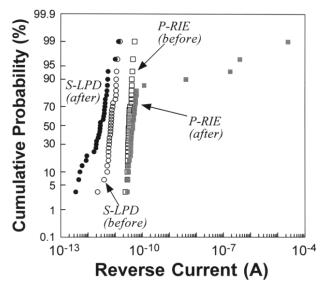

Figure 11 shows the accumulative reverse-current distribution of all measured S-LPD diodes and P-RIE diodes at reverse bias 2.5 V. All reverse currents of S-LPD diodes accumulate at about several picoampere magnitude either before or after sintering. In addition, the S-LPD diodes after sintering show slightly lower reverse currents than those before sintering. This is consistent with the proposed results of Ti-silicide contact reducing reverse current after thermal treatment.  $^{45,46}$  For the P-RIE diodes, exhibit not only high reverse currents but also greatly increase to  $10^{-4}$  Å after sintering. This reveals that the titanium occasionally loses its barrier effect in some P-RIE diodes, yet this failure does not occur in all S-LPD diodes. Cumulatively, our results demonstrate that even if P-RIE has been adopted to avoid overetching, S-LPD samples are still superior to P-RIE samples.

Figure 12 shows the typical diode I-V characteristics of the submicron samples. The satisfactory forward and reverse current reveal the complete cleaning for the photoresist of S-LPD samples by combining

**Figure 11.** Cumulative distribution for reverse currents, at reverse bias 2.5 V, of all measured S-LPD and P-RIE ultrashallow n<sup>+</sup>/p junction diodes before and after sintering.

**Figure 12.** I-V characteristics of S-LPD submicron samples (contact area  $0.8 \times 0.8 \mu m$ ; Al/Ti/Si) (——) before and (-----) after RBTS.

ozone ashing and RCA cleaning. The extremely low reverse leakage proves the superiority of applying S-LPD instead of RIE to 0.8  $\mu m$  contact hole formation. These results indicate that S-LPD can be applied to the submicron contact hole processes. A reverse bias (15.0 V) and temperature (175°C) stress (RBTS)^47 was imposed on the S-LPD submicron samples for reliability examination. After stress of 96 h, shown as the dash-dot line in Fig. 12, junction leakage is still kept at very low leakage magnitude (2.8 pA) and is indeed lower than the leakage of the RIE submicron sample before RBTS. This reliability is much better than the proposed results  $^{47}$  and indicates that a stable TiSi $_2$  structure is formed in S-LPD contact. Our RBTS results suggest S-LPD as a satisfactory method for reliable contact hole formation.

### Conclusion

We have successfully applied the novel S-LPD method to form submicron contact holes and investigated its superiority through n<sup>+</sup>/p diodes, Kelvin contact resistors, and Schottky diodes. The S-LPD n<sup>+</sup>/p diode is superior to the conventional RIE diode with respect to its low reverse current, unity ideality factor, good thermal stability, low contact resistivity, and no problem of etching-rate nonuniformity. Compared with the RIE Schottky diode, the S-LPD Schottky also exhibits excellent rectifying characteristics with high potential barrier, 0.83 eV. The S-LPD ultrashallow junction diodes as well as wet-etch reference diodes show nearly identical I-V characteristics. The similar superiority of S-LPD also exists in our submicron samples. RBTS results suggest S-LPD as a method for reliable contact hole formation. In sum, the S-LPD technique has overcome many undesirable problems induced by RIE. That is, the S-LPD method indeed has the following superiorities in forming contact holes or vias for scaled-down devices: (i) it is a plasma-free process; (ii) it is a damage-free process; and (iii) it is a particle, residue, and contamination-free process. Accordingly, the S-LPD is a promising alternative for replacing conventional RIE for contact hole or via formation. In addition, LPD apparatus costs very little because no vacuum, power, gas-flow equipment, and corresponding etching monitors are needed. Therefore, we believe that in near future, the novel S-LPD method is a good candidate for fabricating the contact holes of deep-submicron devices without plasma damage to fulfill more reliable and more cost-effective requirements in ULSI technologies.

#### Acknowledgment

The authors thank the National Science Council of the Republic of China for financially supporting this research under contract no. NSC 88-2215-E009-036.

National Chiao-Tung University assisted in meeting the publication costs of this article.

#### References

- O. O. Awadelkarim, P. I. Mikulan, T. Gu, R. A. Ditizio, and S. J. Fonash, *IEEE Electron Device Lett.*, EDL-15, 85 (1994).

- O. O. Awadelkarim, T. Gu, R. A. Ditizio, P. I. Mikulan, S. J. Fonash, J. F. Rembetski, and Y. D. Chan, *IEEE Electron Device Lett.*, EDL-14, 167 (1993).

- R. G. Frieser, F. J. Montillo, N. B. Zingerman, W. K. Chu, and S. R. Mader, J. Electrochem. Soc., 130, 2237 (1983).

- 4. M. Ephrath and R. S. Bennett, J. Electrochem. Soc., 129, 1822 (1982).

- Y. Wang, S. W. Graham, L. Chan, and S. T. Loong, J. Electrochem. Soc., 144, 1522 (1997).

- 6. R. L. Guldi and D. R. Wyke, J. Electrochem. Soc., 143, 628 (1996).

- A. Tsukamoto, K. Mizushima, Y. Hidaka, H. Okada, and S. Terakawa, *Jpn. J. Appl. Phys.*, 32, 3058 (1993).

- B. Y. Tsui, S. H. Liu, G. L. Lin, J. H. Ho, C. H. Chang, and C. Y. Lu, *IEEE Electron Device Lett.*, EDL-16, 64 (1995).

- 9. D. Misra and E. L. Heasell, J. Electrochem. Soc., 136, 234 (1989).

- H. Kimura, K. Shiozawa, K. Kawai, H. Miyatake, and M. Yoneda, *Jpn. J. Appl. Phys.*, Part 1, 34, 2114 (1995).

- 11. S. Fang and J. P. McVittie, IEEE Electron Device Lett., EDL-13, 288 (1992).

- H. H. Goto, T. Ohmi, H-D. Lowe, K. Y. Fung, and S. G. Newberry, *IEEE Trans. Semicond. Manufact.*, TSM-5, 337 (1992).

- K. T. Sung, S. W. Pang, M. W. Cole, and N. Pearce, J. Electrochem. Soc., 142, 206 (1995).

- 14. D. R. Sparks, J. Electrochem. Soc., 139, 1736 (1992).

- 15. K. Ueno, V. M. Donnelly, and T. Kikkawa, J. Electrochem. Soc., 144, 2565 (1997).

- H. C. Tseng, C. Y. Chang, F. M. Pan, and L. P. Chen, J. Appl. Phys., 78, 4710 (1995).

- J. P. Simko, G. S. Oehrlein, and T. M. Mayer, J. Electrochem. Soc., 138, 277 (1991).

- M. Sternheim, W. van Gelder, and A. W. Hartman, J. Electrochem. Soc., 130, 655 (1983).

- 19. P. J. Marcoux and P. D. Foo, Solid State Technol., 99, (April 1981).

- H. L. Maynard, E. A. Rietman, J. T. C. Lee, and D. E. Ibbotson, *J. Electrochem. Soc.*, 143, 2029 (1996).

- 21. C. F. Yeh, C. L. Chen, and G. H. Lin, J. Electrochem. Soc., 141, 3177 (1994).

- 22. C. F. Yeh and C. L. Chen, J. Electrochem. Soc., 142, 3579 (1995).

- 23. C. F. Yeh, S. S. Lin, and W. Lur, J. Electrochem. Soc., 143, 2658 (1996).

- 24. C. F. Yeh, C. L. Chen, W. Lur, and P. W. Yen, Appl. Phys. Lett., 66, 938, (1995).

- C. F. Yeh, S. S. Lin, T. Z. Yang, C. L.Chen, and Y. C.Yang, *IEEE Trans. Electron Devices.*, ED-41, 173 (1994).

- C. F. Yeh, T. Z. Yang, and T. J.Chen, IEEE Trans. Electron Devices, ED-42, 307 (1995).

- C. F. Yeh, S. S. Lin, and T. Y. Hong, *IEEE Electron Device Lett.*, EDL-16, 316 (1995).

- T. Homma, T. Katoh, Y. Yamada, and Y. Murao, J. Electrochem. Soc., 140, 2410 (1993).

- 29. C. F. Yeh and C. L. Chen. Semicond. Sci. Technol.. 9, 1250 (1994).

- C. F. Yeh, Y. C. Lee, and J. L. Su, in *Proc. SPIE Int. Soc. Opt. Eng.*, 2879, 260 (1996).

- C. F. Yeh and C. H. Liu, in *Proceedings on Plasma Process Induced Damage* (98'P2ID), p. 223, American Vacuum Society (1998).

- M. M. Smadi, G. Y. Kong, R. N. Carlile, and S. E. Beck, J. Electrochem. Soc., 139, 3356 (1992).

- S. Wolf, Silicon Process for the VLSI Era, Vol. 2, Chap. 3, p. 116, Lattice Press, Sunset Beach, CA (1990).

- 34. D. Misra and E. L. Heasell, J. Electrochem. Soc., 137, 1559 (1990).

- 35. S. Ashok and A. Mogro-Campero, IEEE Electron Device Lett., EDL-5, 48 (1984).

- 36. C. P. Wu, J. T. McGinn, and L. R. Hewitt, J. Electron. Mater., 18, 721 (1989).

- J. P. Gambino, M. D. Monkowski, J. F. Shepard, and C. C. Parks, *J. Electrochem. Soc.*, 137, 976 (1990).

- 38. A. S. Kao and H. G. Stenger Jr., J. Electrochem. Soc., 137, 954 (1990).

- J. Santander, M. Lozano, and C. Cane, *IEEE Trans. Electron Devices*, ED-40, 944 (1993).

- 40. T. Syau and B. J. Baliga, IEEE Trans. Electron Devices, ED-40, 1997 (1993).

- W. M. Loh, S. E. Swirhun, T. A. Schreyer, R. M. Swanson, and K. C. Saraswat, IEEE Trans. Electron Devices, ED-34, 512 (1987).

- M. Biavati, I. Perez-Quintana, A. Poggi, and E. Susi, J. Vac. Sci. Technol. B, 13, 2139 (1995).

- 43. J. M. Shannon, Solid-State Electron., 19, 537 (1976).

- T. J. Dalton, J. C. Arnold, H. H. Sawin, S. Swan, and D. Corliss, *J. Electrochem. Soc.*, **140**, 2395 (1993).

- 45. J. Kanicki, *Appl. Phys. Lett.*, **53**, 1943 (1988).

- L. Rubin, D. Hoffman, D. Ma, and N. Herbots, IEEE Trans. Electron Devices, ED-37, 183 (1990).

- T. Yoshida, H. Kawabara, and S. I. Ogawa, in Proceedings of IEEE International Reliability Physics Symposium (IRPS) 344 (1992).