# A New Quasi-2-D Model for Hot-Carrier Band-to-Band Tunneling Current

Kuo-Feng You, Student Member, IEEE, and Ching-Yuan Wu, Member, IEEE

Abstract—A significant mismatch occurs when we predict the gate-induced drain leakage current (GIDL) by using existing one-dimensional (1-D) models. It's found that the gate-induced drain leakage current is attributed to not only the vertical field but also the lateral field near the drain-to-gate overlap region. Therefore, a new quasi-two-dimensional (quasi-2-D) model considering both the lateral and vertical fields for predicting the gate-induced drain leakage current is proposed by using the drain-induced energy-barrier reduction in our model. The calculated results using the developed quasi-2-D model are in good agreement with measured values for a wide range of gate and drain biases. Therefore, the proposed new model can be used to simulate the hot-carrier band-to-band tunneling current for p-channel flash memory device.

Index Terms— Band-to-band tunneling, gate-induced drain leakage current (GIDL), hot carrier, two-dimensional effect.

### I. INTRODUCTION

S THE GATE-oxide thickness is scaled and the gate electrode is in OFF-state, a significant leakage current passing through the drain electrode can be observed when the drain bias is large but is not large enough for junction breakdown [1]–[5]. This leakage current is so-called "gate-induced drain leakage current (GIDL)," which is commonly attributed to band-to-band tunneling near the gate-to-drain overlap region. Meanwhile, this band-to-band tunneling induced hot-electron injection is recently proposed to be a programming method for p-channel flash memory cell [6].

Since the band-to-band tunneling current is important for flash memory applications, it is necessary that the conducting mechanism should be well-modeled and well-assessed. The model in [1] neglects the dependence of the vertical electric field on the drain doping profile and uses a fixed value of band bending. However, it is well-known that the value of band bending is strongly related to the drain doping concentration and is not a constant value when the drain and gate biases are applied. The model in [4] considers only the vertical field and neglects the lateral field near the gate-to-drain overlap region. The model in [5] only considers the built-in lateral field caused by the lateral gradient of the drain doping concentration and neglects the contribution of the external drain voltage to the lateral field. It is evident that the existing one-dimensional (1-

Manuscript received February 10, 1998; revised September 14, 1998. The review of this paper was arranged by Editor M. Fukuma. This work was supported by the National Science Council, Taiwan, R.O.C. under Contract NSC-88-2215-E009-039.

The authors are with the Advanced Semiconductor Device Research Laboratory and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0018-9383(99)04594-3.

D) models for calculating the band-to-band tunneling current are not valid if both the gate and drain biases are changed. Therefore, a new quasi-two-dimensional (quasi-2-D) gate-induced drain leakage model is proposed in this paper to calculate the band-to-band tunneling current precisely.

#### II. EXPERIMENT

The experimental poly-Si gate p-channel MOSFET's were fabricated in n-well on the  $\langle 100 \rangle$  p-type Si-wafer with the substrate doping concentration of about  $3\text{--}5\times 10^{15}$  cm<sup>-3</sup>. The n-well was formed by the phosphorus implant with a dose of  $7.5\times 10^{13}$  cm<sup>-2</sup> at 80 KeV and the P<sup>+</sup> S/D was formed by implanting BF<sub>2</sub> with a dose of  $2.0\times 10^{15}$  cm<sup>-2</sup> at 60 KeV. The gate-oxide thickness is 100 Å, the channel width is  $25~\mu\text{m}$ , the channel lengths vary from 1 to  $0.8~\mu\text{m}$  and the length of gate-drain overlap is about  $0.1~\mu\text{m}$ . A 3000 Å poly-gate film with a POC1<sub>3</sub> diffusion is formed and the resistivity is  $21.8\text{--}22.5~\Omega/\text{sq}$ . The tested devices are fabricated using conventional P-MOSFET process without threshold-voltage adjustment.

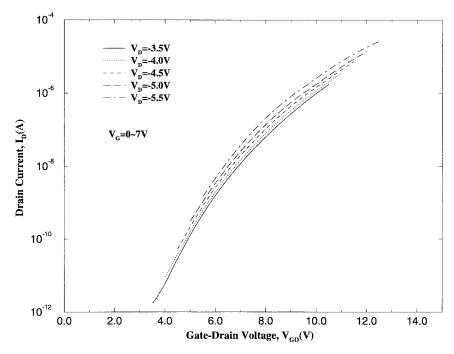

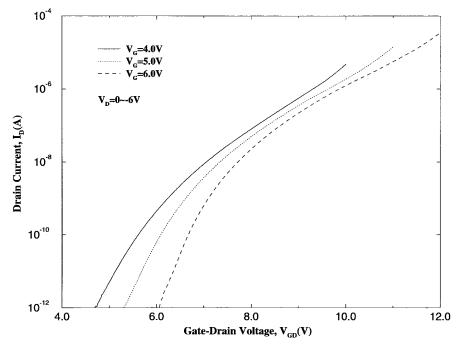

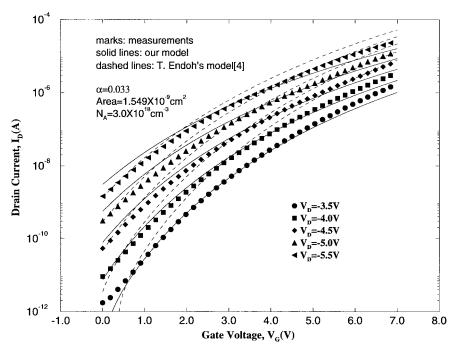

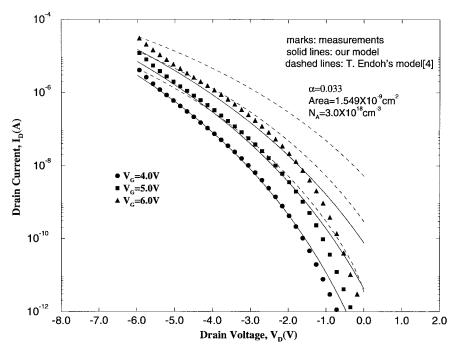

To measure the GIDL current, different bias conditions are tested and a HP4145B is utilized to measure the drain and gate currents. The source terminal is floating. Note that the variation range of gate/drain bias is large and, therefore, the whole characteristics can be obtained. Measured results are shown in Figs. 1 and 2.

From Figs. 1 and 2, some interesting phenomena are observed. One can see that the band-to-band tunneling currents are different under the same  $V_{GD}$ . The conventional 1-D band-to-band tunneling current model [1] can be expressed as

$$I_D = A \cdot E_s \exp(-B/E_s) \tag{1}$$

where A is a preexponential constant;  $B=21.3~{\rm MV/cm}$  [1]; and  $E_s$  is expressed by

$$E_s \simeq \frac{V_{GD} - 1.2}{3T_{ox}}. (2)$$

According to (1) and (2), the drain current should be the same under the same  $V_{GD}$ , regardless of different  $V_G$  or  $V_D$ . Apparently, this prediction conflicts with the characteristics shown in Figs. 1 and 2, in which the larger negative drain bias makes the larger band-to-band tunneling current under a constant  $V_{GD}$ . When the  $V_{GD}$  is fixed, the vertical field near the gate-to-drain overlap region is almost the same regardless of gate biases. However, if the gate voltage is smaller, the drain voltage must be larger under a constant  $V_{GD}$ . The larger drain voltage will render larger lateral field near the gate-to-drain overlap region and this, in turn, causes a larger band-to-band

Fig. 1. Band-to-band tunneling current versus the voltage difference between the gate and drain electrode. The gate electrode is swept from 0 to 7 V and the drain electrode is biased at -3.5, -4.01, -4.5, -5.0, -5.5 V.

Fig. 2. Band-to-band tunneling current versus the voltage difference between the gate and drain electrode. The drain electrode is swept from 0 to -6 V and the gate electrode is biased at 4.0, 5.0, 6.0 V.

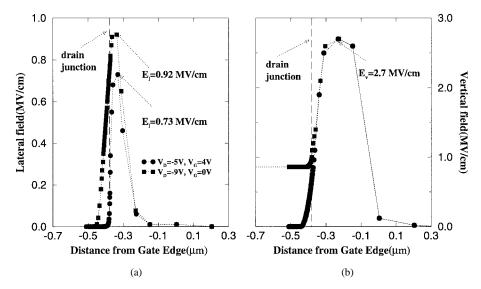

tunneling current. The above variations can be further verified by a two-dimensional (2-D) device simulator and the results are shown in Fig. 3. It is noteworthy that the peak vertical field is larger than the peak lateral field for these two bias conditions, and the smaller lateral field obviously influences the band-to-band tunneling unexpectedly. Therefore, if the lateral field is more influential in causing the band-to-band tunneling, the curves shown in Figs. 1 and 2 would split obviously. This fact can not be obtained from all existing

1-D models, including those in [1], [4], and [5]. Note that the polarities of the drain and gate voltages are negative and positive, respectively. For evaluating the band-to-band tunneling current correctly, the effect caused by the lateral field must be taken into consideration.

# III. A NEW MODEL AND ITS SIMULATED RESULTS

There are several characteristics in our model: a) the band bending value is dependent on the drain doping concentration

Fig. 3. Simulated (a) lateral and (b) vertical electric fields by a 2-D device simulator at two bias conditions ( $V_D = -5$  V,  $V_G = 4$  V, and  $V_D = -9$ V,  $V_G = 0$  V) for the same  $V_{GD}$ .

and the gate/drain bias instead of a fixed value, b) the bandto-band tunneling occurs at a shaded depletion region instead at a fixed position, c) the band-to-band tunneling current is a function of  $V_D$  and  $V_G$  instead of only  $V_{GD}$  as proposed in existing 1-D models, and d) the validity of our model calculation is given for a large variation of both the drain and gate biases instead of a single change in the drain bias.

### A. Potential and Electric Field Distribution

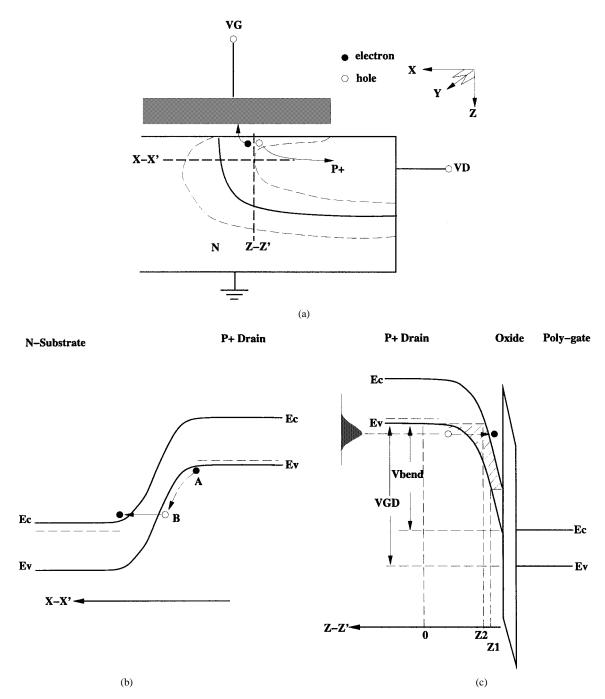

In this subsection, the concept of the new accurate model is described in detail, and a device cross section is shown in Fig. 4(a). The electric field in the drain depletion region can be calculated by using the deep-depletion approximation and is formulated as follows:

$$E_{si}(Z) = \frac{qN_A}{\epsilon_{si}}Z\tag{3}$$

where

$E_{si}$ electric field in the depletion region;

$N_A$ doping concentration in the drain depletion region;

electronic charge;

Zthe coordinate normal to the Si-SiO<sub>2</sub> interface, which is equal to 0 at the edge of the drain depletion region and is positive directed from the depleted edge to the  $Si-SiO_2$  interface, as shown in Fig. 4(c).

Note that the doping concentration is assumed to be constant in the drain depletion region for simplicity. Since the depth where the doping distribution of drain is nearly uniform is about 200-300 Å and the width of the deep depletion layer where band-to-band tunneling occurs is only about 100-200 Å. Therefore, the above assumption in our calculations is acceptable.

Moreover, from Gaussian law, the electric displacement across the Si-SiO2 must be continuous and is described by the following relationship:

$$\epsilon_{si}E_{si}(Z=W) = \epsilon_{ox}E_{ox} = \epsilon_{ox}\frac{(V_{GD} - V_{FB} - V_{bend})}{T_{ox}}$$

(4)

where  $E_{ox}$  is the electric field across SiO<sub>2</sub>;  $T_{ox}$  is the oxide thickness; W is the depletion width, which is equal to  $\sqrt{2\epsilon_{si}V_{\rm bend}/qN_A}$ ;  $V_{FB}$  is the flatband voltage;  $V_{GD}$  is the potential difference between the gate and drain electrode; and  $V_{\rm bend}$  is the band bending value.

One can see that the vertical band bending value could be larger than 1.2 eV or smaller than 1.2 eV, depending on the bias condition and the doping concentration near the gateto-drain overlap region. According to (3) and (4), the band bending value can be calculated by the following equation:

$$V_{\text{bend}} = V_{GD} - V_{FB} + qN_A T_{ox}^2 \epsilon_{si} / \epsilon_{ox}^2 - \sqrt{(V_{GD} - V_{FB} + qN_A T_{ox}^2 \epsilon_{si} / \epsilon_{ox}^2)^2 - (V_{GD} - V_{FB})^2}.$$

(5)

The position that occurs band-to-band tunneling is not fixed at one position but is extended by a shaded region shown in Fig. 4(c). The potential distributions of conduction and valence bands can be separately expressed by

$$\Phi_v = -\frac{V_{\text{bend}}}{W^2} Z^2 \tag{6}$$

$$\Phi_c = -\frac{V_{\text{bend}}}{W^2} Z^2 + E_g \tag{7}$$

where  $E_g$  is the energy gap of Si.

# B. Band-to-Band Tunneling Current

If the drain is biased negatively, a reverse p-n junction (drain to channel) would introduce a large lateral electric

Fig. 4. (a) Cross-sectional view of a planar diode, (b) the energy band diagram in the direction of x-x', and (c) the energy band diagram at the position B based on our new model.

field as shown in Fig. 4(b). This lateral electric field would render electrons in the valence band traveling horizontally, for example, from A to B as depicted in Fig. 4(b) and, in turn, these valence electrons would gain energy from the lateral electric field. If the band-to-band tunneling occurs for these hot valence electrons, the equivalent energy barrier would reduce, as shown in Fig. 4(c). Therefore, the energy barrier which is equal to energy gap for cold electrons could be reduced due to the applied drain bias. We call this phenomenon as the drain-induced energy-barrier reduction effect. Here, we introduce the drain biasing effect on the energy barrier reduction and use a fitting parameter  $\alpha$ . The reduced energy barrier  $E_{qp}$

for hot-electron band-to-band tunneling can be expressed as follows:

$$E_{gp} = E_g - \alpha V_D \tag{8}$$

where  $\alpha$  is an empirical fitting parameter.

To calculate the band-to-band tunneling current, the tunneling probability as a function of electric field in Si is expressed by using the two-band tunneling theory as follows [7]:

$$P(E_{si}) = \frac{q^2 m^{1/2} E_{si}^2}{18\pi \hbar^2 E_{gp}^{1/2}} \exp\left(-\frac{\pi m^{1/2} E_{gp}^{3/2}}{2\hbar q E_{si}}\right)$$

(9)

Fig. 5. Comparisons between measured results and calculated currents using our model. The dashed lines are calculated by the model in [4]. The bias conditions are the same as those used in Fig. 1.

Fig. 6. Comparisons between measured results and calculated currents using our models. The bias conditions are the same as those used in Fig. 2.

where P is the tunneling rate per second per cubic centimeter. The band-to-band tunneling current  $I_d$  can be obtained by integrating the tunneling rate through the whole depletion region as

$$I_{d} = A_{rea} \int_{0}^{Z_{1}} dz \cdot q \cdot P(E_{si})$$

$$= A_{rea} \int_{E_{1}}^{E_{2}} dE_{si} \frac{dz}{dE_{si}} \cdot q \cdot P(E_{si})$$

(10)

where  $Z_1 = W \sqrt{1 - E_{gp}/V_{bend}}$ ;  $Z_2 = W \sqrt{E_{gp}/V_{bend}}$ ;  $E_1 = E_{si}(Z = Z_2)$ ;  $E_2 = E_{si}(Z = W)$  and  $A_{rea}$  is the effective area of band-to-band tunneling near the gate-to-drain overlap region in the direction of x and y, as shown in Fig. 4.

# C. Comparisons Between Simulated and Measured Results

The band-to-band tunneling characteristics are calculated for various bias conditions. In Fig. 5, the gate bias is swept from 0 to 7.0 V and the drain is biased at -3.5, -4.0, -4.5, -5.0,

TABLE I

THE PARAMETERS USED FOR MODEL CALCULATIONS

| device's parameter values |                      | fitting parameter values |                        |

|---------------------------|----------------------|--------------------------|------------------------|

| $T_{ox}(\mathring{A})$    | 100                  | α                        | 0.033                  |

| $\overline{V_{FB}(V)}$    | -1.10                | $A_{rea}(cm^2)$          | $1.549 \times 10^{-9}$ |

| $\overline{N_A(cm^{-3})}$ | $3.0 \times 10^{18}$ |                          |                        |

| $E_g(eV)$                 | 1.12                 |                          |                        |

-5.5 V. It is obvious that the simulated and measured currents are quite matched for various bias conditions. The calculated band-to-band currents using our model agree well with the measured results over a wide range of band-to-band tunneling current from  $10^{-12}$  to  $10^{-5}$  A. In Fig. 6, the drain bias is swept from 0 to -6.0 V while the gate electrode is biased at 4.0, 5.0, 6.0 V. Because the avalanche breakdown voltage of the drain-substrate junction is about 6.5 V, the maximum value of measured drain bias is -6.0 V to avoid the involvement of the avalanche effect. It is clearly seen that the calculated results match well with the measured curves. The dotted lines shown in Figs. 5 and 6 are calculated by using the model in [4]. Note that the parameters used for calculations are identical between our model and conventional one [4] except that  $\alpha$  is set to zero for the conventional model [4], which are listed in Table I. The band-to-band tunneling currents calculated by our quasi-2-D model almost match with experimental results for any bias condition, in which both the vertical and lateral electric fields are significant and can't be neglected. Therefore, our developed band-to-band tunneling current model can be used to predict the subbreakdown current and the band-toband tunneling current induced hot-carrier injection for flash memory programming.

# IV. CONCLUSION

A new accurate quasi-2-D band-to-band tunneling current model considering the effective tunneling barrier lowering has been proposed, which is effective in predicting the subbreakdown current under various gate and drain biases. The calculated currents match well with the measured results over a wide range of current from  $10^{-12}$  to  $10^{-5}$  A. Therefore, our proposed model can be used to simulate the programming of p-channel flash memory, based on hot-carrier band-to-band tunneling.

#### REFERENCES

- J. Chen, T. Y. Chan, I. C. Chen, P. K. Ko, and C. Hu, "Subbreakdown drain leakage current in MOSFET," *IEEE Electron Device Lett.*, vol. EDL-8, p. 515, Nov. 1987.

- [2] C. Chang and J. Lien, "Corner-field induced drain leakage in thin oxide MOSFET's," in *IEDM Tech. Dig.*, 1987, p. 714.

- [3] S. H. Voldman, J. A. Bracchitta, and J. Fitzgerald, "Band-to-band tunneling and thermal generation gate-induced drain leakage," in *Proc. Device Res. Conf.*, paper A-8, 1988.

- [4] T. Endoh, R. Shirota, M. Momodomi, and F. Masuoka, "An accurate model of subbreakdown due to band-to-band tunneling and some applications," *IEEE Trans. Electron Devices*, vol. 37, p. 290, Jan. 1990.

- [5] S. A. Parke, J. E. Moon, H. C. Wann, P. K. Ko, and C. Hu, "Design for suppression of gate-induced drain leakage in LDD MOSFET's using a quasi-two-dimensional analytical model," *IEEE Trans. Electron Devices*, vol. 39, p. 1694, July 1992.

- [6] T. Ohnakado, K. Mitsunaga, M. Nunoshita, H. Onoda, K. Sakakibara, N. Tsuji, N.Ajika, M. Hatanaka, and H. Migoshi, "Novel electron injection method using band-to-band tunneling induced hot electrons (BBHE) for flash memory with a P-channel cell." in *IEDM Tech. Dig.*, 1995, p. 279.

- [7] E. O. Kane, "Zener tunneling in semiconductors," J. Phys. Chem. Solids, vol. 12, p. 181, 1959.

**Kuo-Feng You** (S'91) was born in I-Lan, Taiwan, R.O.C., on August 12, 1969. He received the B.S. degree from the Department of Electronics Engineering, National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1991, and the Ph.D. degree from the Institute of Electronics, National Chiao-Tung University, in 1998. His research areas focus on deep submicrometer MOS device physics and reliability issues, especially the gate oxide damage from plasma-induced wafer charging.

Ching-Yuan Wu (S'72–M'75) was born in Taiwan, R.O.C., on March 18, 1946. He received the B.S. degree in electrical engineering from the National Taiwan University, Taipei, in 1968, and the M.S. and Ph.D. degrees from the State University of New York at Stony Brook in 1970 and 1972, respectively.

During the 1972–1973 academic year, he was appointed as a Lecturer in the Department of Electronical Sciences, SUNY-Stony Brook. During the 1973–1975 academic years, he was a Visiting As-

sociate Professor at the National Chiao-Tung University (NCTU), Hsinchu, Taiwan. In 1976, he became a Full Professor in the Department of Electronics and the Institute of Electronics at NCTU. While there, he was Director of the Engineering Laboratories and Semiconductor Research Center from 1974 to 1980, the Director of the Institute of Electronics from 1978 to 1984, and the Dean of the College of Engineering from 1984 to 1990. He was a principal investigator of the National Electronics Mass Plan-Semiconductor Devices and Integrated-Circuit Technologies from 1976 to 1979, and had been a Coordinator of the National Microelectronics Researches and High-Level Man-Power Education Committee, National Science Council, R O.C., from 1982 to 1988. He has been the Research Consultant of the Electronics Research and Service Organization (ERSO), ITRI, a member of the Academic Review Committee in the Ministry of Education, and the Chairman of the Technical Review Committee on Information and Microelectronics Technologies at the Ministry of Economic Affairs. His research activities have been in semiconductor device physics and modeling, integrated circuit designs, and technologies. His current research areas focus on the development of efficient 2-D and 3-D simulators for deep-submicrometer CMOS devices. He has published more than 180 papers in the semiconductor field and has served as a reviewer for international journals such as IEEE Electron Device Letters, IEEE TRANSACTIONS ON ELECTRON DEVICES, and Solid-State Electronics.

Dr. Wu is a member of the Honorary Editorial Advisory Board of *Solid-State Electronics*, and is a board member of the Chinese Engineering Society. He received the Academic Research Award in Engineering from the Ministry of Education (MOE) in 1979, and the Outstanding Scholar Award from the Chinese Educational and Cultural Foundation in 1985. He received the Outstanding Research Professor Fellowship from the Ministry of Education and National Science Council (NSC), R.O.C., from 1982 to 1999. He received the Distinguished Engineering Professor Medal Award from the Chinese Engineering Society in 1992.