Journal of Crystal Growth 201/202 (1999) 652-655

# Electrical characterization of Al<sub>2</sub>O<sub>3</sub> on Si from thermally oxidized AlAs and Al

C.C. Liao, Albert Chin\*, C. Tsai

Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, ROC

## Abstract

The scaling limit for VLSI gate oxide  $(SiO_2)$  is 15–20 Å that is determined by the large direct-tunneling leakage current. Further scaling to improve device performance can be obtained using a higher dielectric constant material. We have studied the  $Al_2O_3$  to use as an alternative gate dielectric. To ensure good quality,  $Al_2O_3$  is thermally oxidized from MBE-grown AlAs or Al on Si-substrates. Experimental results indicate that the leakage current from oxidized AlAs is larger than that from directly oxidized Al, which may be due to the weak  $As_2O_3$  inside  $Al_2O_3$ . The leakage current of a 53 Å  $Al_2O_3$  is already lower than that of  $SiO_2$  with an equivalent oxide thickness of 21 Å. © 1999 Published by Elsevier Science B.V. All rights reserved.

PACS: 73.40.Qv

Keywords: Si CMOS; Alternative gate dielectrics; High-K; Al<sub>2</sub>O<sub>3</sub>

#### 1. Introduction

It has been shown that the practical scaling limit for gate oxide is due to the leakage current by direct-tunneling process [1], although 11–15 Å direct-tunneling gate oxide has already been demonstrated [2,3]. At present, the thickness of thermally grown gate oxide is scaled down to 35–40 Å for the 0.18-µm VLSI generation, and further scaling down below 15 Å is required within a few years [4]. Unfortunately, the large direct-tunneling

current precludes the use of silicon dioxide (SiO<sub>2</sub>) below 15–20 Å thickness. However, continuously scaling down the gate oxide is necessary to increase

where  $I_{\mathrm{Dsat}}$  is the device saturation current,  $V_{\mathrm{G}}$  is the applied gate voltage and K is the dielectric constant of the gate capacitor. The only solution to overcome this difficulty and to continuously scale down the gate dielectric is to use a thicker dielectric with a higher K value. Therefore, novel high-K gate dielectric has been identified as one of the most

0022-0248/99/\$ - see front matter © 1999 Published by Elsevier Science B.V. All rights reserved.

PII: S0022-0248(98)01441-9

the current drive capability of MOSFETs and the operation speed of ICs. The relationship of drive current and gate oxide thickness is shown as  $I_{\text{Dsat}} = \frac{1}{2} \bar{\mu}_{\text{n}} \frac{W}{L} \frac{\varepsilon_0 KA}{t_{\text{ox}}} (V_{\text{G}} - V_{\text{T}})^2, \tag{1}$

<sup>\*</sup>Corresponding author. Tel.: + 886-35-731841; fax: + 886-35-724361; e-mail: achin@cc.nctu.edu.tw.

important R&D plans [4] for deca-nano CMOS technology. Unfortunately, because of the stringent requirements for device quality gate dielectric, no satisfactory alternatives to SiO2 has so far been found. Recently, aluminum oxide (Al2O3) has attracted much attention because of its very high dielectric constant ( $\sim 10$ ) that can be used for the next generation DRAM and Flash memory application [5]. Moreover, Al<sub>2</sub>O<sub>3</sub> has also been treated as a gate barrier in InAlAs/InGaAs MES-FET using plasma oxidation of deposited Al [6]. In this paper, we have first characterized the electrical property of Al<sub>2</sub>O<sub>3</sub> to use as an alternative gate dielectric of MOSFETs. Because extremely high quality is required for gate dielectric, we have used thermally grown Al<sub>2</sub>O<sub>3</sub> from oxidized AlAs or Al that were grown in an ultra-high vacuum molecular beam epitaxy (MBE) system. In comparison, sputtering deposition and O<sub>2</sub> plasma oxidation have been used in the past to deposit Al<sub>2</sub>O<sub>3</sub>; however, high defects can be expected from Ar bombardment and plasma damage, respectively. In this work, the leakage current of a 53 Å Al<sub>2</sub>O<sub>3</sub> from direct oxidized Al is already better than that of  $SiO_2$  with the equivalent thickness of 21 Å [2]. This result suggests the possible application of Al<sub>2</sub>O<sub>3</sub> to VLSI.

# 2. Experimental procedure

P-type 4" [1 0 0] Si wafers with typical resistivity of  $10 \Omega$  cm are used in this study. After modified RCA cleaning, HF dipping, rinsing in DI water and spun dry, the wafer was treated by HF-vapor passivation and immediately loading into the MBE chamber. The HF-vapor passivation has been used to reduce thermal budget to desorb the native oxide [7]. Then 40–80 Å AlAs or 40–55 Å Al were grown by MBE at 500°C. The oxidation process was performed in a standard furnace at 500°C for 90 min, and the dielectric thickness was measured by an ellipsometer. After oxidation, 3000 Å poly-Si was deposited followed by phosphorus doping using POCl<sub>3</sub> at 850°C. The wafers then received a 30-min nitrogen anneal at 800°C. This anneal was found to be very effective to reduce dielectric leakage current. Subsequently, 3000 Å Al was deposited and

gate electrode was defined by patterning and wet etching. The gate dielectrics were electrically characterized by I-V leakage current using a semiconductor parameter analyzer, and the composition profiles were measured using secondary ion mass spectroscopy (SIMS).

# 3. Results and discussions

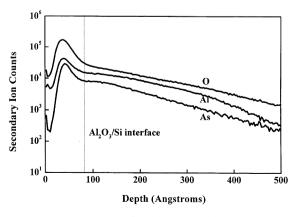

Fig. 1 presents the SIMS profiles of oxidized AlAs at 500°C, where O, Al and As are detected within the oxidized layer. The possible AlAs oxidation process is in the following equation:

AlAs

$$+\frac{3}{2}O_2 \rightarrow \frac{1}{2}Al_2O_3 + \frac{1}{2}As_2O_3$$

. (2)

Therefore, both Al<sub>2</sub>O<sub>3</sub> and As<sub>2</sub>O<sub>3</sub> are formed during AlAs oxidation. As shown in Fig. 1, significant Al and As diffusion into Si is observed. The diffused As into Si will behave as a n-type dopant and change the threshold voltage, while the amount of diffused Al is dependent on the solid solubility of Si. However, none of these effects are desirable for MOS devices. The reduced surface concentration of As is due to the out-diffusion into ambient during oxidation.

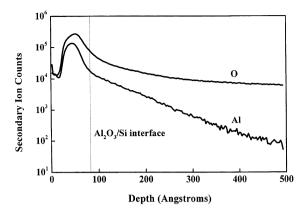

Fig. 2 shows the SIMS profile of oxidized Al. The  $\rm O_2$  concentration decreases to its background value as increasing depth beyond the oxidized layer. This is because the Si oxidation rate is negligibly slow at this temperature. In sharp contrast to AlAs oxidation, the oxidized Al shows a much

Fig. 1. SIMS depth profiles of oxidized AlAs at 500°C.

Fig. 2. SIMS depth profiles of oxidized Al at 500°C.

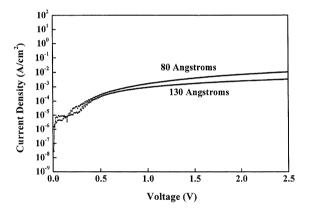

Fig. 3. J–V characteristics of MOS capacitors with oxidized AlAs dielectric. The capacitor area is  $800~\mu m \times 800~\mu m$ .

sharper SIMS profiles. Possible reason may be due to the absence of As-enhanced diffusion during oxidation. Another advantage of direct Al oxidation may be due to the strong bonding energy of Al<sub>2</sub>O<sub>3</sub> instead of As<sub>2</sub>O<sub>3</sub> from oxidized AlAs. Therefore, the oxidized Al films may provide not only better material quality but also lower diffusion into Si during oxidation.

We have further characterized the electrical behavior of these oxides. Fig. 3 shows the typical J-V characteristics of MOS capacitors from oxidized AlAs. The capacitor leakage current reduces with increasing dielectric thickness from 80 to 130 Å. This is a typical behavior because a thicker

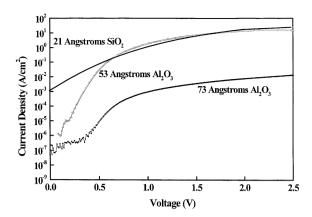

Fig. 4. J-V characteristics of MOS capacitors with oxidized Al dielectric. The capacitor area is  $800 \, \mu\text{m} \times 800 \, \mu\text{m}$ . The J-V characteristic of 21 Å SiO<sub>2</sub> is from Ref. [2].

insulating barrier has lower electric field that can block the electron transport more easily. However, this thicker insulating barrier did not successfully reduce the leakage current at low voltages less than  $\sim\!0.7$  V. Possible reasons may be due to trap-assisted tunneling at low electric field [8]. The traps may be generated by the weak bonding strength of  $As_2O_3$  inside  $Al_2O_3$  matrix or vacancies by As out-diffusion.

To investigate the effect of As-related weak As<sub>2</sub>O<sub>3</sub> or vacancies, we have studied the electric characteristics of capacitors with directly oxidized Al. In comparison the J-V characteristics of  $\sim 80 \,\text{Å}$  oxides in Figs. 3 and 4, a much lower leakage current is observed at gate voltage below 1 V from directly oxidized Al. This leakage current at low gate electric field is related to the intrinsic defects [8] that is similar to stress-induced leakage current (SILC) [7,9]. Therefore, the As-related weak As<sub>2</sub>O<sub>3</sub> or vacancies are responsible to the increased oxide leakage current. The almost same current at high voltages is due to the dominated tunneling mechanism. We have further compared the leakage current of Al<sub>2</sub>O<sub>3</sub> with SiO<sub>2</sub> from the published I-V characteristic [2]. It is important to note that the leakage current of 53 A Al<sub>2</sub>O<sub>3</sub> is already better than the leakage current of MOS capacitors with the same equivalent thickness of 21 Å thick SiO<sub>2</sub> [2].

## 4. Conclusion

We have studied the thermally oxidized AlAs and Al to use as an alternative gate dielectric. The leakage current from AlAs oxidation is larger than that from Al oxidation at low voltages. The leakage current of a 53 Å Al<sub>2</sub>O<sub>3</sub> is already lower than SiO<sub>2</sub> with an equivalent oxide thickness of 21 Å. These results suggest that scaling equivalent oxide thickness below 15–20 Å is possible using the Al<sub>2</sub>O<sub>3</sub> films.

# Acknowledgements

We would like to thank Prof. K.C. Hsieh at the University of Illinois for his great help. The work has been supported by NSC (88-2215-E-009-032) of Taiwan.

## References

- [1] K.F. Schuegraf, C.C. King, C. Hu, Symposium on VLSI, 1992, p. 18.

- [2] H.S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nskamura, M. Saito, H. Iwai, IEEE Trans. Electron Dev. 43 (1996) 1233.

- [3] A. Chin, W.J. Chen, T. Chang, R.H. Kao, B.C. Lin, C. Tsia, J.C-M. Huang, IEEE Electron Dev. Lett. 18 (1997) 417.

- [4] The National Technology Roadmap for Semiconductors, 1997, p. 74.

- [5] W.H. Lee, J.T. Clemens, R.C. Keller, L. Manchanda, Symposium on VLSI, 1997 p. 118.

- [6] T.Y. Chang, R.E. Behringer, R.E. Howard, A.S.H. Liao, L.D. Jackel, E.A. Caridi, W.J. Skocpol, R.W. Epworth, IEDM Tech. Dig. (1984) 356.

- [7] A. Chin, B.C. Lin, W.J. Chen, Y.B. Lin, C. Tsai, IEEE Electron Dev. Lett. 19 (1998) 426.

- [8] C.T. Liu, A. Ghetti, Y. Ma, G. Alers, C.P. Chang, K.P. Cheung, J.I. Colonell, W.Y.C. Lai, C.S. Pai, R. Liu, H. Vaidya, J.T. Clemens, IEDM Tech. Dig. (1997) 85.

- [9] B.C. Lin, Y.C. Cheng, A. Chin, T. Wang, C. Tsai, 30th Solid State Devices and Materials (SSDM), September, 1998.