# Effective Improvement on Barrier Capability of Chemical Vapor Deposited WSi<sub>r</sub> Using N<sub>2</sub> Plasma Treatment

M. T. Wang, Y. C. Lin, J. Y. Lee, C. C. Wang, and M. C. Chen\*, z

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan

This work studies the thermal stability of  $Cu/WSi_x/p^+$ -n and  $Cu/WSiN/WSi_x/p^+$ -n diodes in which the  $WSi_x$  barrier layers were deposited by chemical vapor deposition to a thickness of about 50 nm using  $SiH_4/WF_6$  chemistry with the  $SiH_4/WF_6$  flow rates of 6/2 sccm, while the WSiN layers were formed by in situ  $N_2$  plasma treatment on the chemically vapor deposited  $WSi_x$  ( $CVD-WSi_x$ ) surfaces. Without  $N_2$  plasma treatment, the thermal stability of  $Cu/WSi_x$  (S0 nm)/ $p^+$ -n junction diodes was found to reach  $S00^\circ C$ ; with  $N_2$  plasma treatment, the resultant  $SiN_x = SiN_x = S$

Manuscript submitted September 29, 1997; revised manuscript received December 11, 1998.

Copper (Cu) has been extensively studied as a potential interconnect material for deep submicron integrated circuit (IC) applications because of its low electrical resistivity and superior electromigration resistance as compared with the conventionally used Al and its alloys. 1–3 Moreover, Cu can be deposited using chemical vapor deposition (CVD). 4,5 Unfortunately, Cu diffuses fast in Si and forms Cu–Si compounds at low temperatures (about 200°C). 6 It causes deep-level traps in Si. 7 In addition, it has poor adhesion to interlevel dielectric and drifts through oxide under field acceleration. 8 Therefore, the use of a diffusion barrier between Cu and its underlying layers is considered a prerequisite for Cu to be useful in silicon IC applications.

Various materials have been studied as diffusion barriers between Cu and Si substrates as well as Cu and dielectric layers. Refractory metals are generally regarded as potential barrier materials because of their high thermal stability and good electrical conductivity. 9-13 Sputter-deposited, nitride-based diffusion barriers, such as WN, <sup>10,14–16</sup> TaN, <sup>15,17–20</sup> MoN, <sup>21</sup> and TiWN, <sup>22</sup> have attracted extensive attention for a long time. Most recently, the use of a WSiN layer as a diffusion barrier has also been intensively studied.<sup>23–27</sup> It was reported that the WSiN film has low film stress, low electrical resistivity, excellent thermal stability, good adhesion to insulator and copper films, and a well-matched thermal expansion coefficient with Si. 24,28 It was also reported that a very thin (4 nm) WSiN layer can be formed on the surface of WSix by electron cyclotron resonance (ECR) N<sub>2</sub> plasma nitridation and that it functioned as an excellent barrier to dopant diffusion.<sup>29</sup> Moreover, it was found that a uniform ultrathin (<1 nm) WSiN barrier layer can be formed at the interface of WN/poly-Si by thermal annealing and that the WSiN layer was able to suppress the silicidation reaction between W and poly-Si up to 800°C.30 Although these studies have provided much valuable information regarding WSiN films as a diffusion barrier, no study has been made on the WSiN layer with respect to its barrier effectiveness between Cu and Si substrates using electrical measurement as well as material analysis.

In this study, we use the WSiN/WSi $_x$  bilayer as a diffusion barrier between Cu and Si substrates in which the WSi $_x$  layer was deposited by CVD using the SiH $_4$ /WF $_6$  chemistry, while the WSiN layer was formed by an in situ N $_2$  plasma treatment on the WSi $_x$  surface. According to this scheme, a very thin WSiN (about 5 nm) layer

was formed on the surface of the  $\mathrm{WSi}_x$  layer. We found that the  $\mathrm{WSiN/WSi}_x$  bilayer possesses a much improved barrier capability against Cu diffusion.

### **Experimental**

The thermal stability of barrier layers was evaluated by measuring leakage current of thermally annealed Cu/barrier/p^+-n junction diode. The starting materials for the diodes fabrication were n-type, (100)-oriented silicon wafers with 4–7  $\Omega$  cm nominal resistivity. After RCA standard cleaning, the wafers were thermally oxidized to grow a 500 nm thick oxide layer. Diffusion areas with sizes of 500  $\times$  500 and 1000  $\times$  1000  $\mu m$  were defined on the oxide-covered wafers using conventional photolithographic technique. The p^+-n junctions with junction depth of 0.3  $\mu m$  were formed by BF $_2^+$  implantation at 40 keV to a dose of 3  $\times$  10 $^{15}$  cm $^{-2}$  followed by furnace annealing at 900°C for 30 min in N $_2$  ambient.

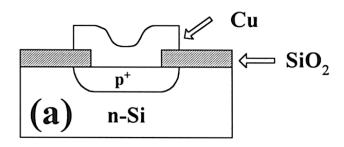

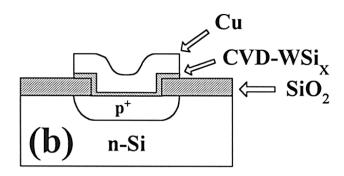

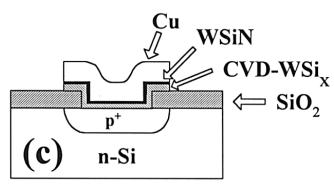

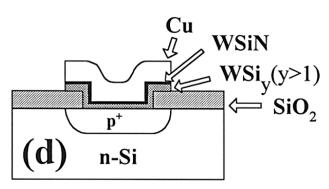

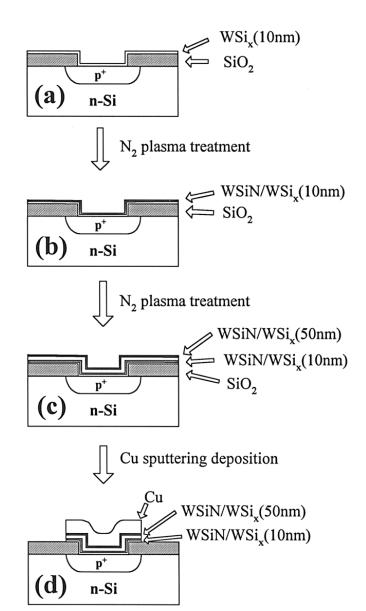

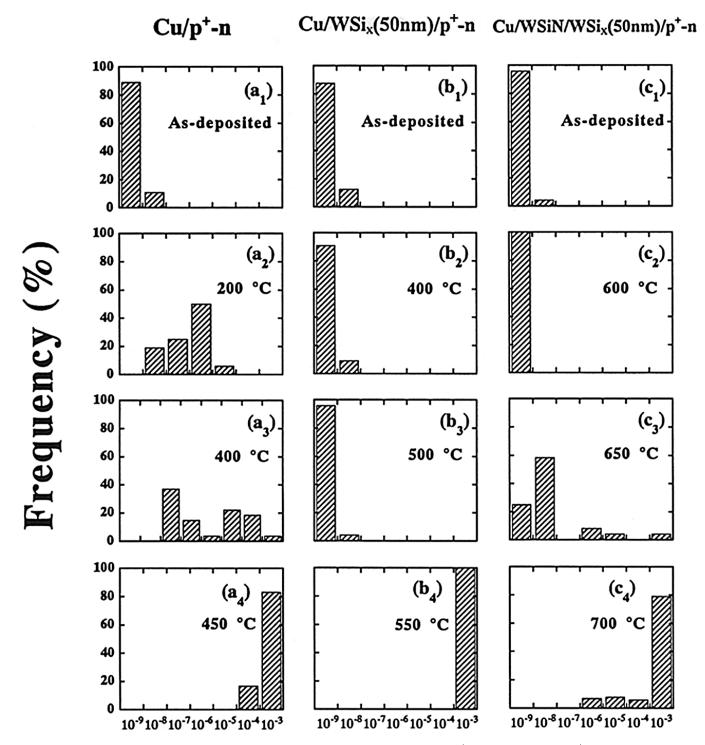

After the junctions were formed, the wafers were divided into five groups for the preparation of the following devices: (a) Cu/p<sup>+</sup>-n; (b)  $Cu/WSi_{x}$  (50 nm)/p<sup>+</sup>-n; (c)  $Cu/WSiN/WSi_{x}$  (50 nm)/p<sup>+</sup>-n; (d)  $Cu/WSiN/WSi_{x}$  (50 nm)/p<sup>+</sup>-n; WSiN/WSiy  $(y > 1)/p^+$ -n; and (e) Cu/WSiN/WSi<sub>x</sub> (50 nm)/WSiN/  $WSi_x$  (10 nm)/p<sup>+</sup>-n junction diodes. Schematic cross sections of the former four differently metallized p<sup>+</sup>-n junction diodes are illustrated in Fig. 1. The WSix layer was deposited by CVD to a thickness of about 50 nm using the SiH<sub>4</sub>/WF<sub>6</sub> chemistry. The subsequent thermal annealing of the WSi<sub>x</sub>/Si sample occurred at 700°C for 30 min in N<sub>2</sub> ambient so that the  $WSi_x$  layer became a Si-rich WSiy (y > 1) layer. The WSiN/WSi<sub>x</sub> and WSiN/WSi<sub>y</sub> barrier bilayers were formed by N<sub>2</sub> plasma treatment on the surface of WSi<sub>x</sub> and WSi<sub>2</sub> layers, respectively. The last barrier of the WSiN/WSi,/WSiN/WSi, multilayer was accomplished by a double-step processing of WSi<sub>x</sub> deposition and N<sub>2</sub> plasma treatment: a 10 nm WSi<sub>x</sub> deposition followed by N<sub>2</sub> plasma treatment plus another 50 nm WSi<sub>x</sub> deposition followed by N<sub>2</sub> plasma treatment. Figure 2 shows the process flow for the Cu/WSiN/WSi<sub>x</sub> (50 nm)/WSiN/WSi<sub>x</sub> (10 nm)/p<sup>+</sup>-n junction diode.

Prior to the  $\mathrm{WSi}_x$  deposition, the wafers were dipped in dilute HF (50:1) for 30 s, followed by a rinse in DI water for 5 min and a spin dry. The wafers were then loaded into a load-locked coldwall CVD system within 5 min and transferred by a robot arm to the deposition chamber without exposure to the atmosphere. The base pressure of the CVD chamber was  $1 \times 10^{-6}$  Torr. In this study, the CVD-WSi<sub>x</sub> was deposited with the following conditions: substrate temperature 250°C, total gas pressure 12 mTorr, WF<sub>6</sub> flow rate 2 sccm, and SiH<sub>4</sub> flow rate 6 sccm. For the formation of WSiN, a very thin (about

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: mcchen@cc.nctu.edu.tw

5 nm) layer of WSiN was formed by in situ  $N_2$  plasma treatment on the surface of the  $WSi_x$  layer without exposure to the air, or by  $N_2$  plasma treatment on the surface of the  $WSi_y$  (y>1) layer with air exposure. The  $N_2$  plasma treatment was performed at 100 W plasma power with  $N_2$  flow rate of 80 sccm and a gas pressure of 25 mTorr; the plasma treating time was 300 s.

Finally, Cu metallization was applied to all samples using a dc magnetron sputtering system with a base pressure of  $1-2 \times 10^{-6}$  Torr and with no intentional substrate heating and bias. A

**Figure 1.** Schematic cross sections of (a)  $Cu/p^+$ -n; (b)  $Cu/WSi_{\chi}$  (50 nm)/p $^+$ -n; (c)  $Cu/WSiN/WSi_{\chi}$  (50 nm)/p $^+$ -n; and (d)  $Cu/WSiN/WSi_{\chi}$  (y > 1)/ p $^+$ -n junction diodes.

200 nm thick Cu film was sputter deposited using a 99.999% purity Cu target in Ar ambient at a pressure of 7.6 mTorr. Cu patterns were defined and etched using dilute (5 vol %) HNO3, while the barrier layers were etched using  $SF_6/N_2$  plasma. For comparison,  $Cu/p^+$ -n junction diodes without barrier layers were also fabricated.

To investigate thermal stability of the diodes, samples were thermally annealed in an  $\rm N_2$  flowing furnace for 30 min at various temperatures from 200 to 800°C. Reverse-bias leakage-current measurement on the thermally annealed diodes was used to evaluate the barrier capability of various barrier layers. An HP-4145B semiconductor parameters analyzer was used for the measurement, and at least 30 diodes were measured in each case. Unpatterned samples with multilayer structures of  $\rm Cu/WSi_{\chi}$  (50 nm)/Si,  $\rm Cu/WSiN/WSi_{\chi}$  (50 nm)/Si, and  $\rm Cu/WSiN/WSi_{\chi}$  (50 nm)/SiO<sub>2</sub>/Si were also prepared for material analysis. Sheet resistance of the multilayer structures was measured using a four-point probe. Auger electron spectroscopy (AES) was used to determine the composition of WSi\_{\chi} films. X-ray diffraction (XRD) analysis was used for phase identification. Scanning electron microscopy (SEM) was employed to observe surface

**Figure 2.** Process flow of Cu/WSiN/WSi $_x$  (50 nm)/WSiN/WSi $_x$  (10 nm)/p $^+$ -n junction diodes: (a) WSi $_x$  (10 nm) deposition, (b) in situ N $_2$  plasma treatment, (c) second layer of WSi $_x$  (50 nm) deposition and in situ N $_2$  plasma treatment, and (d) Cu deposition and patterning.

morphology and microstructure, and secondary ion mass spectroscopy (SIMS) was used to determine the elemental depth profiles.

## **Results and Discussion**

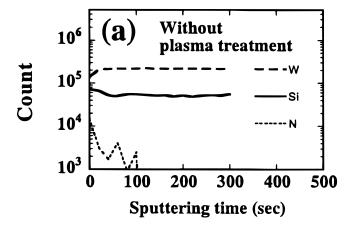

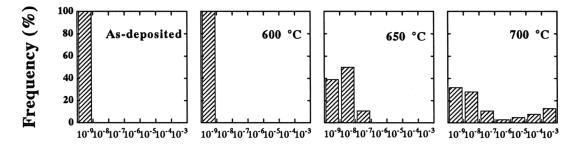

Thermal stability of  $WSi_x$  (50 nm) and  $WSiN/WSi_x$  (50 nm) barriers.—Figure 3 shows the statistical distributions of reverse bias leakage-current density for the  $Cu/p^+$ -n,  $Cu/WSi_x$  (50 nm)/ $p^+$ -n, and  $Cu/WSiN/WSi_x$  (50 nm)/ $p^+$ -n junction diodes annealed at various temperatures. For the diodes without any barrier layer between the

Cu and Si substrate, the  $\text{Cu/p}^+$ -n junction diodes failed after 200°C annealing (Fig. 3a). With a 50 nm thick  $\text{WSi}_x$  barrier between the Cu and Si substrate, the  $\text{Cu/WSi}_x/\text{p}^+$ -n junction diodes were able to retain the devices integrity up to 500°C (Fig. 3b). For the diodes with an N<sub>2</sub>-plasma-treated barrier layer, the  $\text{Cu/WSiN/WSi}_x/\text{p}^+$ -n diodes were able to remain stable after annealing at temperatures up to 600°C (Fig. 3c). Even after annealing at 650°C, about 85% of the annealed diodes survived with leakage current density less than 100 nA/cm². It is clear that the barrier capability of the  $\text{WSi}_x$  layer was significantly improved by in situ N<sub>2</sub> plasma treatment.

**Figure 3.** Histograms showing statistical distributions of reverse-bias leakage-current density for (a)  $Cu/p^+$ -n, (b)  $Cu/WSi_x$  (50 nm)/ $p^+$ -n, and (c)  $Cu/WSiN/WSi_x$  (50 nm)/ $p^+$ -n junction diodes annealed at various temperatures.

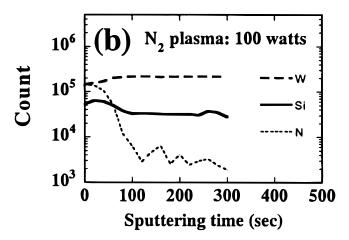

The significant improvement of barrier capability for the  $N_2$ -plasma-treated  $WSi_x$  layer is attributed to a very thin WSiN layer formed on the  $WSi_x$  surface, as confirmed by AES depth profile analysis shown in Fig. 4. Without  $N_2$  plasma treatment, only a very weak signal of nitrogen was detected near the  $WSi_x$  surface (Fig. 4a), presumably due to adsorption of nitrogen gas on the  $WSi_x$  surface prior to loading the test sample into the AES chamber. After an  $N_2$  plasma treatment at 100 W for 300 s, a very thin (about 5 nm) WSiN layer was definitely formed (Fig. 4b). The N/W ratios in the WSiN layer were determined to be about 3/2 at the sample's surface and about 1/1 at 3 nm depth from the sample's surface. In addition, the as-deposited  $WSi_x$  layer has a Si/W atomic ratio of about unity, as determined by Rutherford backscattering (RBS) measurement.

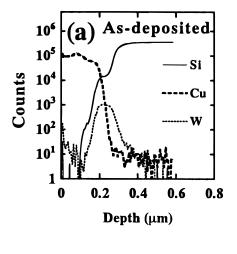

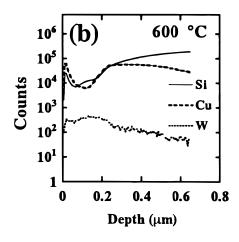

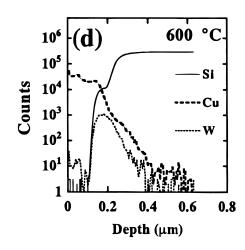

Figure 5 shows the SIMS depth profiles for the as-deposited and  $600^{\circ}\text{C}$ -annealed  $\text{Cu/WSi}_x/\text{Si}$  and  $\text{Cu/WSiN/WSi}_x/\text{Si}$  samples. With the  $\text{WSi}_x$  barrier without  $\text{N}_2$  plasma treatment, the interdiffusion among Cu, W, and Si resulted in severe degradation of the  $\text{Cu/WSi}_x/\text{Si}$  structure after annealing at  $600^{\circ}\text{C}$ , as shown in Fig. 5b (compared with Fig. 5a for the as-deposited sample). On the other hand, with the barrier layer treated with  $\text{N}_2$  plasma, the  $\text{Cu/WSiN/WSi}_x/\text{Si}$  sample was able to keep the W and Si profiles nearly unchanged, with only a slight diffusion of Cu into the barrier layer, as shown in Fig. 5d (compared with Fig. 5c). The results of SIMS depth profile analysis further confirm that thermal stability of the  $\text{Cu/WSi}_x/\text{Si}$  structure can be improved effectively by forming a very thin layer of the WSiN on the surface of the WSi $_x$  layer via  $\text{N}_2$  plasma treatment.

**Figure 4.** AES depth profiles of as-deposited  $WSi_{x}/Si$  samples (a) without  $N_2$  plasma treatment and (b) with  $N_2$  plasma treatment at 100 W for 300 s.

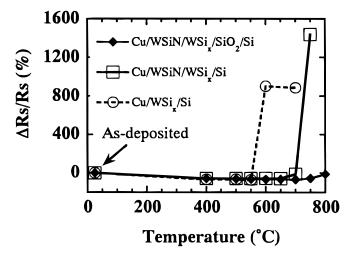

The sheet resistance change of thermally annealed samples, normalized to the as-deposited sheet resistance value, is denoted as  $\Delta Rs/Rs$  percent and defined as follows

$$\frac{\Delta Rs}{Rs}\% = \frac{Rs_{\text{after anneal}} - Rs_{\text{as-deposited}}}{Rs_{\text{as-deposited}}} \times 100\%$$

Figure 6 shows the percentage change of sheet resistance vs. annealing temperature for the samples of  $\text{Cu/WSi}_{\lambda}$  (50 nm)/Si,  $\text{Cu/WSiN/WSi}_{\lambda}$  (50 nm)/Si, and  $\text{Cu/WSiN/WSi}_{\lambda}$  (50 nm)/SiO<sub>2</sub>/Si. For the  $\text{Cu/WSi}_{\lambda}$ /Si sample, the sheet resistance remained constant up to 550°C; it increased drastically after annealing at 600°C. For the samples with a barrier layer treated with  $\text{N}_2$  plasma, the sheet resistance of  $\text{Cu/WSiN/WSi}_{\lambda}$ /Si samples remained stable up to 650°C, and only a slight degradation was observed after annealing at 700°C. This is a significant improvement of barrier effectiveness. Compared with the results of leakage-current measurement shown in Fig. 3, we found that the electrical measurement is a much more sensitive technique for barrier failure detection. Nevertheless, the results of sheet resistance measurement further confirm that thermal stability of the  $\text{Cu/WSi}_{\lambda}$ /Si structure can be significantly improved by forming a thin layer of WSiN on the surface of the WSi, layer via  $\text{N}_2$  plasma treatment.

Failure mechanism of WSiN/WSi<sub>x</sub> (50 nm) barriers.—There are two interfaces, Cu/WSi<sub>x</sub> and WSi<sub>x</sub>/Si, in the Cu/WSi<sub>x</sub>/Si structure. Barrier effectiveness of the WSi, layer can be retained up to a certain temperature only if these two interfaces and the WSi, layer itself are thermally stable up to that temperature. Our previous findings revealed that thermal stability of the Cu/WSix interface can be improved by inserting a WSiN layer between Cu and WSi<sub>x</sub>. However, reaction at the WSi<sub>x</sub>/Si interface might affect thermal stability of the Cu/WSiN/WSix/Si structure. To investigate the effect of the WSi<sub>x</sub>/Si interface reaction on the thermal stability of the Cu/WSiN/ WSi,/Si structure, we examined the thermal stability of the Cu/ WSiN/WSi<sub>x</sub>/SiO<sub>2</sub>/Si structure. The presence of the SiO<sub>2</sub> layer in this structure prevented interdiffusion between WSi, and the substrate Si at elevated temperatures. We found no obvious change in sheet resistance for the Cu/WSiN/WSi<sub>x</sub>/SiO<sub>2</sub>/Si sample after annealing at temperatures up to 750°C (Fig. 6). This indicates that the degradation in the electrical characteristics of Cu/WSiN/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes was due to the reaction that occurred at the WSi,/Si interface at 700°C, as was confirmed further by XRD analysis shown in Fig. 7. This result also suggests that thermal stability of the Cu/WSiN/ WSi<sub>y</sub>/p<sup>+</sup>-n diodes could be further improved if a scheme can be developed to suppress or retard the WSi<sub>r</sub>/Si interface reaction at elevated temperatures.

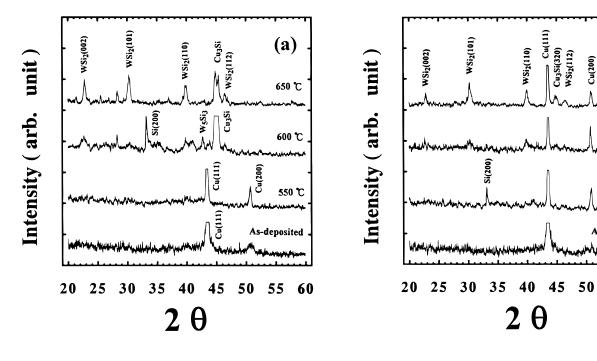

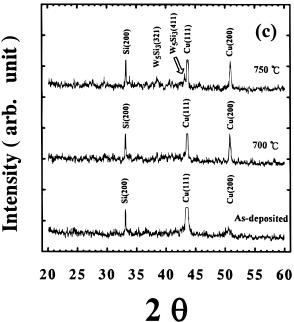

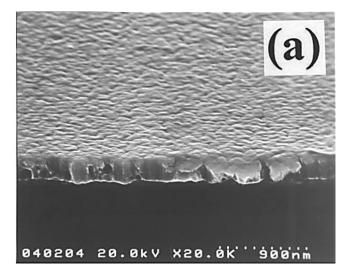

Figure 7 illustrates the XRD spectra for the as-deposited and thermally annealed Cu/WSi,/Si, Cu/WSiN/WSi,/Si, and Cu/WSiN/ WSi<sub>x</sub>/SiO<sub>2</sub>/Si samples. The formation of Cu<sub>3</sub>Si, W<sub>5</sub>Si<sub>3</sub>, and/or WSi<sub>2</sub> phases for the Cu/WSi<sub>x</sub>/Si sample annealed at 600°C and above, as shown in Fig. 7a, resulted in drastic increase in sheet resistance. Similarly, the increase in sheet resistance for the Cu/WSiN/WSi<sub>x</sub>/Si sample after annealing at 700°C reflects the formation of both Cu<sub>3</sub>Si and WSi<sub>2</sub> phases, as shown in Fig. 7b; in fact, weak peaks of WSi<sub>2</sub> already appeared when the sample was annealed at 650°C. It should be noted that no diffraction peak relating to the formation of WSi<sub>2</sub> was detected for the Cu/WSiN/WSi<sub>x</sub>/Si sample annealed at 600°C (Fig. 7b), while a strong peak of copper silicide and weaker peaks of tungsten silicides were detected for the Cu/WSi<sub>x</sub>/Si sample annealed at the same temperature (Fig. 7a). It has been reported that the amorphous state of WSiN can be preserved even after annealing at 850°C.<sup>29</sup> For the Cu/WSiN/WSi<sub>x</sub>/Si sample, the thin but chemically and thermally stable WSiN layer contributed to retard the diffusion of copper; thus, the barrier effectiveness was improved. For the Cu/WSiN/WSi<sub>x</sub>/Si sample annealed at 650°C, although weak diffraction peaks of WSi2 appeared, no signal relating to Cu3Si phase was detected. This indicates that Cu diffusion remained suppressed by the WSiN layer, though interface reaction at the WSi,/Si interface had occurred. However, annealing at 700°C resulted in silicidation

**Figure 5.** SIMS depth profiles: (a) asdeposited and (b)  $600^{\circ}$ C annealed Cu/WSi<sub>x</sub>/Si samples; and (c) as-deposited and (d)  $600^{\circ}$ C annealed Cu/WSiN/ WSi<sub>x</sub>/Si samples.

and grain growth of the  $WSi_x$  layer, leading to a net volume change and localized defect formation (such as columnar seams and stress-induced microcracks), which in turn broke the continuity of the WSiN layer. Thus, barrier capability of the WSiN/WSi<sub>x</sub> bilayer was degraded. As for the structure of the Cu/WSiN/WSi<sub>x</sub>/SiO<sub>2</sub>/Si, the diffraction peak of copper silicide was not detected after annealing at temperatures up to 750°C, though weak peaks relating to  $W_5Si_3$

**Figure 6.** Percentage change of sheet resistance vs. annealing temperature for the samples of Cu/WSi<sub>x</sub>/Si, Cu/WSiN/WSi<sub>x</sub>/Si, and Cu/WSiN/WSi<sub>x</sub>/SiO<sub>2</sub>/Si.

phase were found (Fig. 7c). This implies that the reaction occurring at the  $WSi_{x}/Si$  interface played an important role in the failure of the  $Cu/WSiN/WSi_{x}/Si$  structure. Comparative results of thermal stability for the multilayer structures studied in this work based on XRD analysis are summarized in Table I.

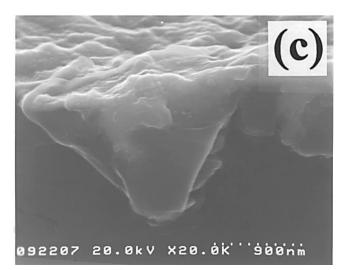

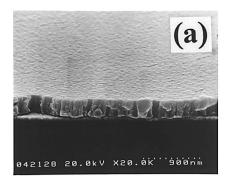

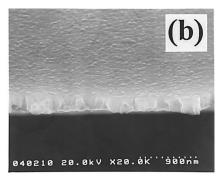

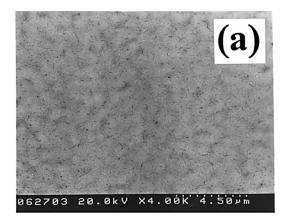

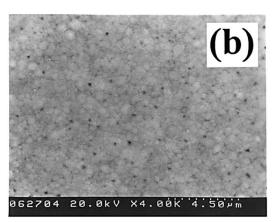

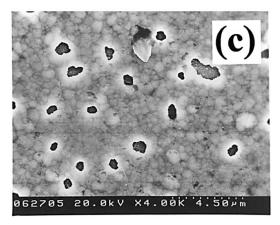

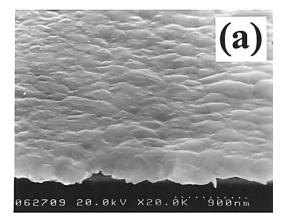

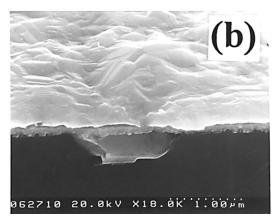

Figure 8 shows the SEM micrographs for the Cu/WSix (50 nm)/p<sup>+</sup>-n junction diodes. The barrier structure remained unchanged after annealing at 500°C (Fig. 8b); however, large Cu<sub>3</sub>Si precipitates (silicide) were formed after annealing at 600°C (Fig. 8c). For the Cu/WSiN/WSi<sub>x</sub> (50 nm)/p<sup>+</sup>-n diode structure, SEM micrographs show that this multilayer structure remained stable after annealing at 600°C, as shown in Fig. 9. After annealing at 650°C, some of the diodes showed degradation while the others remained intact (Fig. 3c). For the diodes that remained intact after annealing, the SEM micrograph shows that integrity of the barrier structure was retained (Fig. 9c). For the degraded diodes, highly localized protrusions were found (Fig. 9d). Thus, failure of the WSiN/WSix (50 nm) bilayer barrier is likely associated with these highly localized protrusions, which were presumably caused by diffusion of Cu through the localized weak points (such as grain boundaries, columnar seams, and stress-induced microcracks) in the barrier layer. These highly localized defects also reveal a common feature of a protrusion at their center, surrounded by a ring of Cu film depletion. After annealing at 700°C, defects were found with larger size as well as higher density (not shown).

Further improvement of barrier capability.—To further improve barrier capability of the  $WSiN/WSi_x$  bilayer, two schemes were designed to either eliminate reaction at the  $WSi_x/Si$  interface or suppress interdiffusion between  $WSi_x$  and Si substrate. According to these schemes, we proposed the following two barrier structures.

**Figure 7.** XRD spectra of (a)  $\text{Cu/WSi}_x$  (50 nm)/Si, (b)  $\text{Cu/WSiN/WSi}_x$  (50 nm)/Si, and (c)  $\text{Cu/WSiN/WSi}_x$  (50 nm)/SiO<sub>2</sub>/Si samples annealed at various temperatures.

**(b)**

700 ℃

650 ℃

600 ℃

As-deposited

55 60

First, we annealed the  $WSi_x$  layer to stabilize the barrier structure, followed by  $N_2$  plasma treatment prior to Cu metallization to make

a Cu/WSiN/WSi<sub>y</sub>  $(y > 1)/p^+$ -n junction diode. Second, we inserted an extra thin WSiN/WSi<sub>x</sub> (10 nm) bilayer between the original WSi<sub>x</sub>

Table I. Compound phases detected by XRD analysis for various multilayer structures studied in this work.<sup>a</sup>

|                        | Multilayer structure                                                        |                                            |                                                |  |

|------------------------|-----------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------|--|

| Annelaing temperatures | Cu/WSi <sub>x</sub> /Si                                                     | Cu/WSiN/WSi <sub>x</sub> /Si               | Cu/WSiN/WSi <sub>x</sub> /SiO <sub>2</sub> /Si |  |

| 550°C                  | ×                                                                           | ×                                          | X                                              |  |

| 600°C                  | Weak WSi <sub>2</sub> , W <sub>5</sub> Si <sub>3</sub> , Cu <sub>3</sub> Si | ×                                          | ×                                              |  |

| 650°C                  | WSi <sub>2</sub> , Cu <sub>3</sub> Si                                       | Weak WSi <sub>2</sub>                      | ×                                              |  |

| 700°C                  | *WSi <sub>2</sub> , Cu <sub>3</sub> Si                                      | WSi <sub>2</sub> , weak Cu <sub>3</sub> Si | ×                                              |  |

| 750°C                  | 2 0                                                                         | *WSi <sub>2</sub> , Cu <sub>3</sub> Si     | $W_5Si_3$                                      |  |

$<sup>^{\</sup>rm a}$   $\times$  indicates no observation of compound phase; \* indicates XRD spectra not shown in Fig. 7.

(b) 040205 20.0kV X20.0k'''900nm

**Figure 8.** SEM micrographs for the  $Cu/WSi_x$  (50 nm)/p<sup>+</sup>-n junction diodes (a) as-deposited (oblique view), (b) annealed at 500°C (oblique view), and (c) annealed at 600°C (cross-sectional view).

(50 nm) layer and Si substrate to make a  $\text{Cu/WSiN/WSi}_x$  (50 nm)/ $\text{WSiN/WSi}_x$  (10 nm)/p<sup>+</sup>-n junction diode so as to suppress interdiffusion between the 50 nm  $\text{WSi}_x$  and Si substrate.

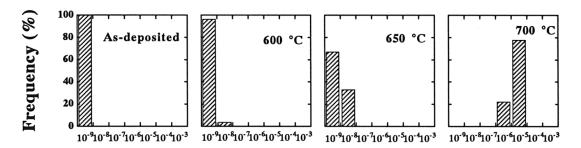

$Cu/WSiN/WSi_v$   $(y > 1)/p^+$ -n junction diodes.—We thermally annealed the WSi<sub>x</sub> (50 nm)/p<sup>+</sup>-n junction diodes at 700°C in N<sub>2</sub> ambient for 30 min so that the  $WSi_x$  layer became a Si-rich  $WSi_y$  (y > 1)layer. After the formation of the Si-rich WSi<sub>v</sub> layer, N<sub>2</sub> plasma treatment was performed on the Si-rich WSi<sub>v</sub> surface to produce a WSiN/WSi<sub>v</sub> bilayer. Figure 10 shows the statistical distributions of reverse-bias leakage-current density for the Cu/WSiN/WSi,/p<sup>+</sup>-n junction diodes annealed at various temperatures. All junction diodes retained the integrity of their electrical characteristics up to 600°C. After annealing at 650°C, they were slightly degraded; however, even after annealing at 700°C, about 60% of the diodes survived with leakage current density less than 100 nA/cm<sup>2</sup>. Compared with the results of electrical measurement for the Cu/WSiN/WSi<sub>x</sub>/ p<sup>+</sup>-n junction diodes shown in Fig. 3c, we found that the barrier capability of WSiN/WSi, bilayer is superior to that of WSiN/WSi. This indicates that the annealing before nitridation stabilized the barrier structure, presumably due to the formation of Si-rich WSi<sub>v</sub>, and thus efficiently improved the barrier capability.

$Cu/WSiN/WSi_x$  (50 nm)/WSiN/WSi<sub>x</sub> (10 nm)/p<sup>+</sup>-n junction diodes.— We found that the Cu/WSiN/WSi<sub>x</sub> (50 nm)/p<sup>+</sup>-n junction diodes degraded after annealing at 650°C (Fig. 3c). It is possible that Si outdiffusion took place at the WSi<sub>x</sub>/Si interface at such a temperature. Presumably, the Si out-diffusion together with formation and grain growth of tungsten silicide (as confirmed by XRD analysis shown in Fig. 7b) generated local defects and thus led to degradation of the diodes electrical characteristics. To prevent the undesirable interdiffusion between WSi<sub>x</sub> and Si, a thin WSiN/WSi<sub>x</sub> (10 nm) bilayer was introduced between the WSiN/WSi<sub>x</sub> (50 nm) bilayer and Si substrate to make a four-layer barrier structure of WSiN/WSi<sub>r</sub> (50 nm)/WSiN/ WSi<sub>x</sub> (10 nm). Figure 11 shows the statistical distributions of reverse-bias leakage-current density for the Cu/WSiN/WSi,/WSiN/ WSi<sub>y</sub>/p<sup>+</sup>-n junction diodes annealed at various temperatures. The junction diodes retained their integrity after annealing at temperatures up to 650°C. This is an obvious improvement over the Cu/ WSiN/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes. It appeared that the out-diffusion of Si substrate at WSi<sub>x</sub> (50 nm)/Si interface was suppressed by the presence of WSiN/WSi<sub>r</sub> (10 nm). The WSiN/WSi<sub>r</sub> (10 nm) underlayer blocked the Si out-diffusion and thus retarded the formation of WSi<sub>2</sub> and suppressed the grain growth of the WSi<sub>3</sub> (50 nm) layer, which in turn resulted in the improvement of junction diodes thermal stability. However, all the diodes were severely degraded after annealing at 700°C, presumably due to the crystallization and grain growth of the  $WSi_x$  (50 nm) layer. The reaction at the  $WSi_x$  (10 nm)/ Si interface at such a high temperature was also responsible for the degradation of electrical characteristics.

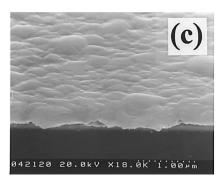

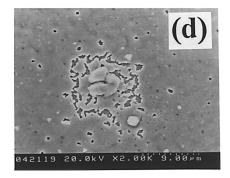

Figure 12 shows the surface morphology of the Cu/WSiN/WSi<sub>v</sub>  $(y > 1)/p^+$ -n junction diodes. No obvious defect was found on the diodes annealed at 650°C (Fig. 12b) as compared with the as-deposited sample (Fig. 12a). For the diodes annealed at 700°C, some of the diodes retained their integrity with very low leakage current while others were severely degraded (Fig. 10). A number of small openings were found on the diodes that have a low leakage-current density (not shown), while dense and large openings were found for the diodes with degraded electrical characteristics (Fig. 12c). Figure 13 shows SEM micrographs for the Cu/WSiN/WSi<sub>x</sub> (50 nm)/  $WSiN/WSi_x$  (10 nm)/p<sup>+</sup>-n junction diodes annealed at 650 and 700°C. No obvious defect was found on the diodes annealed at 650°C (Fig. 13a). This is consistent with the results of electrical measurement shown in Fig. 11. After annealing at 700°C, a highly localized trapezoidal section precipitate was found throughout our SEM inspection (Fig. 13b). Thermal stability temperatures of WSi<sub>r</sub>based barrier layers determined by various techniques of measurement or analysis are summarized in Table II.

**Figure 9.** Oblique and top-view SEM micrographs for the Cu/WSiN/WSi $_x$ /p<sup>+</sup>-n junction diodes (a) as-deposited, (b) annealed at 600°C, and (c) and (d) annealed at 650°C.

#### Conclusion

Thermal stability of CVD amorphous  $WSi_x$  layers, with and without  $N_2$  plasma treatment, was investigated with respect to the diffu-

sion barrier capability between Cu and Si substrates. We found that the barrier capability of  $WSi_x$  films can be efficiently improved by  $N_2$  plasma treatment. Without  $N_2$  plasma treatment, the thermal stability

# Leakage Current Density (A/cm<sup>2</sup>)

Figure 10. Histograms showing statistical distributions of reverse-bias leakage current density for the Cu/WSiN/WSi<sub>y</sub>  $(y > 1)/p^+$ -n junction diodes annealed at various temperatures.

# Leakage Current Density (A/cm<sup>2</sup>)

Figure 11. Histograms showing statistical distributions of reverse-bias leakage-current density for the  $Cu/WSiN/WSi_{\chi}$  (50 nm)/ $WSiN/WSi_{\chi}$  (10 nm)/ $p^+$ -n junction diodes annealed at various temperatures.

**Figure 12.** Top-view SEM micrographs for the Cu/WSiN/WSi $_y$ /p $^+$ -n junction diodes (a) as-deposited, (b) annealed at 650°C, and (c) annealed at 700°C.

of Cu/WSi $_x$  (50 nm)/p<sup>+</sup>-n junction diodes was found to reach 500°C. With N $_2$  plasma treatment applied to the WSi $_x$  barrier, a nitrogen-con-

**Figure 13.** Oblique-view SEM micrographs for the  $Cu/WSiN/WSi_x/WSiN/WSi_x/p^+$ -n junction diodes annealed at (a) 650 and (b) 700°C.

taining thin layer of WSiN was formed on the surface of WSi $_x$ , and the Cu/WSiN/WSi $_x$  (50 nm)/p<sup>+</sup>-n junction diodes were able to remain intact up to at least 600°C. Barrier failure mechanism for the WSiN/WSi $_x$  bilayer was closely related to the WSi $_x$ /Si interface reaction and the crystallization of the WSi $_x$  layer. The thermal stability was further raised to 650°C by using a multilayer barrier structure of WSiN/WSi $_x$  (50 nm)/WSiN/WSi $_x$  (10 nm) or a WSiN/WSi $_y$  (y > 1) barrier. We conclude that the post-CVD-WSi $_x$  treatment with in situ N $_2$  plasma is a simple, practical, and efficient method of improving the WSi $_x$ -based barrier capability for Cu metallization.

### Acknowledgments

This work was supported by the National Science Council (ROC) under contract no. NSC86-2215-E-009-040.

National Chiao-Tung University assisted in meeting the publication costs of this article.

Table II. Thermal stability temperatures of WSi<sub>x</sub>-based barrier layers determined by different techniques of measurement/analysis.

| Measurement/analysis methods | Barrier structure        |                               |                             |                                                                      |

|------------------------------|--------------------------|-------------------------------|-----------------------------|----------------------------------------------------------------------|

|                              | WSi <sub>x</sub><br>(°C) | WSiN/WSi <sub>x</sub><br>(°C) | $WSiN/WSi_{y} (y > 1)$ (°C) | $\frac{\text{WSiN/WSi}_{x}/\text{WSiN/WSi}_{x}}{(^{\circ}\text{C})}$ |

| Leakage current              | 500                      | 600                           | 650                         | 650                                                                  |

| SEM                          | 500                      | 600                           | 650                         | 650                                                                  |

| XRD                          | 550                      | 650                           |                             |                                                                      |

| Sheet resistance             | 550                      | 650                           |                             |                                                                      |

#### References

- S. P. Murarka, R. J. Gutmann, A. E. Kaloyeros, and W. A. Lanford, *Thin Solid Films*, 236, 257 (1993).

- N. Awaya, H. Inokawa, E. Yamamoto, Y. Okazaki, M. Miyake, Y. Arita, and T. Kobayashi, *IEEE Trans. Electron Devices*, ED-43, 1206 (1996).

- C.-K. Hu, B. Luther, F. B. Kaufman, J. Hummel, C. Uzoh, and D. J. Pearson, *Thin Solid Films*, 262, 84 (1995).

- 4. D. H. Kim, R. H. Wentorf, and W. N. Gill, J. Electrochem. Soc., 140, 3273 (1993).

- 5. J. C. Chiou, Y. J. Chen, and M. C. Chen, J. Electron. Mater., 23, 383 (1994).

- 6. C. A. Chang, J. Appl. Phys., 67, 566 (1990).

- S. D. Brotherton, J. R. Ayres, A. Gill, H. W. V. Kesteren, and F. J. A. M. Greidanus, J. Appl. Phys., 62, 1826 (1987).

- Y. S. Diamand, A. Dedhia, D. Hoffstetter, and W. G. Oldham, J. Electrochem. Soc., 140, 2427 (1993).

- 9. M.-A. Nicolet, Thin Solid Films, 54, 415 (1978).

- T. Nakano, H. Ono, T. Ohta, T. Oku, and M. Murakami, in Proceedings of the VLSI Multilevel Interconnection Conference, VMIC, p. 407, June (1994).

- 11. H. Ono, T. Nakano, and T. Ohta, Appl. Phys. Lett., 64, 1511 (1994).

- 12. K. Holloway and P. M. Fryer, Appl. Phys. Lett., 57, 1736 (1990).

- 13. S. Q. Wang, J. Appl. Phys., 73, 2301 (1993).

- P. J. Pokela, C.-K. Kwok, E. Kolawa, S. Raud, and M.-A. Nicolet, *Appl. Surf. Sci.*, 53, 364 (1991).

- W. K. Yeh, T. T. Wu, M. H. Tsai, S. C. Sun, J. C. Chuang, and M. C. Chen, in Proceedings of the VLSI Multilevel Interconnection Conference, VMIC, p. 541, June (1996).

- 16. H. Ono, T. Nakano, and T. Ohta, Jpn. J. Appl. Phys., 34, 1827 (1995).

- 17. M. Wittmer, Appl. Phys. Lett., 36, 456 (1980).

- X. Sun, E. Kolawa, J. S. Chen, J. S. Reid, and M. A. Nicolet, *Thin Solid Films*, 236, 347 (1993).

- 19. M. Takeyama, A. Noya, T. Sase, and A. Ohta, J. Vac. Sci. Technol., B14, 674 (1996).

- K. Holloway, P. M. Fryer, C. Cabral, Jr., J. M. E. Harper, P. J. Bailey, and K. H. Kelleher, *J. Appl. Phys.*, 71, 5433 (1992).

- 21. J. Y. Lee and J. W Park, Jpn. J. Appl. Phys., 35, 4280 (1996).

- 22. J. C. Chiou, K. C. Juang, and M. C. Chen, J. Electrochem. Soc., 142, 2326 (1995).

- Y. Shimooka, T. Iijima, S. Nakamura, and K. Suguro, *Jpn. J. Appl. Phys.*, 36, 1589 (1997).

- G. Minamihaba, T. Iijima, Y. Shimooka, H. Tamura, T. Kawanoue, H. Hirabayashi,

N. Sakurai, H. Ohkawa, T. Obara, and K. Suguro, *Jpn. J. Appl. Phys.*, 35, 1107 (1996).

- P. M. Smith, J. S. Custer, J. G. Fleming, E. R. Osmun, M. Cohn, and R. V. Jones, in *Proceedings of the VLSI Multilevel Interconnection Conference*, VMIC, p. 162, June (1996).

- T. Iijima, Y. Shimooka, G. Minamihaba, T. Kawanoue, H. Tamura, H. Hirabayashi, N. Sakurai, H. Ohkawa, T. Kubota, Y. Mase, M. Koyama, J. Ooshima, J. Wada, and K. Suguro, in *Proceedings of the VLSI Multilevel Interconnection Conference*, VMIC, p. 168, June (1996).

- J. S. Reid, E. Kolawa, R. P. Ruiz, and M. A. Nicolet, *Thin Solid Films*, 236, 319 (1993).

- 28. A. Lahav and K. A. Grim, J. Appl. Phys., 67, 734 (1990).

- A. Hirata, T. Hosoya, K. Machida, H. Takaoka, and H. Akiya, *J. Electrochem. Soc.*, 143, 3747 (1996).

- Y. Akasaka, S. Suehiro, K. Nakajima, T. Nakasugi, K. Miyano, K. Kasai, H. Oyamatsu, M. Kinugawa, M. Takagi, K. Agawa, F. Matsuoka, M. Kakumu, and K. Suguro, in *Proceedings of the VLSI Multilevel Interconnection Conference*, VMIC, p. 168, June (1995).