## Formation of silicided shallow p + n junctions by BF 2 + implantation into thin amorphous-Si or Ni/amorphous-Si films on Si substrates and subsequent Ni silicidation

M. H. Juang, M. C. Hu, and C. J. Yang

Citation: Journal of Vacuum Science & Technology B 17, 392 (1999); doi: 10.1116/1.591030

View online: http://dx.doi.org/10.1116/1.591030

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/17/2?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Nitride-mediated epitaxy of CoSi 2 on Si(001)

Appl. Phys. Lett. 82, 1833 (2003); 10.1063/1.1555708

Comparison of low energy BF 2 + , BCl 2 + , and BBr 2 + implants for the fabrication of ultrashallow P + -N junctions

J. Appl. Phys. 91, 2023 (2002); 10.1063/1.1433926

Surface characterization of a low dielectric constant polymer–SiLK \* polymer, and investigation of its interface with Cu

J. Vac. Sci. Technol. B 17, 2336 (1999); 10.1116/1.590914

Removal of end-of-range defects in Ge + -pre-amorphized Si by carbon ion implantation

J. Appl. Phys. **85**, 3114 (1999); 10.1063/1.369694

Comparison of ultralow-energy ion implantation of boron and BF 2 for ultrashallow p + /n junction formation Appl. Phys. Lett. **74**, 1248 (1999); 10.1063/1.123514

### Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Formation of silicided shallow $p^+n$ junctions by $BF_2^+$ implantation into thin amorphous-Si or Ni/amorphous-Si films on Si substrates and subsequent Ni silicidation

M. H. Juanga) and M. C. Hu

Department of Electronics Engineering, National Taiwan University of Science & Technology, Kee-Lung Rd., Taipei, Taiwan

C. J. Yang

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, Republic of China

(Received 7 May 1998; accepted 18 December 1998)

The process scheme that forms NiSi-silicided shallow  $p^+n$  junctions by BF<sub>2</sub><sup>+</sup> implantation into thin amorphous-Si (a-Si) or Ni/a-Si films on Si substrates and subsequent Ni silicidation has been studied. As for the scheme using a-Si as an implantation barrier, an NiSi-silicided junction with a leakage of about  $0.7 \, \text{nA/cm}^2$  at  $-5 \, \text{V}$  is obtained by the sample Ni silicided at  $700 \, ^{\circ}\text{C}$  for 30 min. The implantation energy and the crystallinity of the deposited Si films after annealing would greatly affect the junctions formed at various temperatures, attributable to different implantation effects and boron depth profile. However, the junctions formed by rapid thermal processing or high implant energy are considerably degraded at  $800 \, ^{\circ}\text{C}$ , attributable to anomalous Ni penetration into the Si substrate with the further silicidation of NiSi into NiSi<sub>2</sub>. On the other hand, the specimens with Ni/a-Si as an implantation barrier sustain few defects, thus significantly suppressing the junction degradation at  $800 \, ^{\circ}\text{C}$ . However, the formed junctions are worse than those by the former scheme, mainly due to lower dopant drive-in efficiency. ©  $1999 \, American \, Vacuum \, Society$ . [S0734-211X(99)03902-5]

#### I. INTRODUCTION

With the progress of the ultralarge-scale-integration (ULSI) technology, the metal-oxide-semiconductor fieldeffect transistor (MOSFET) channel length has been scaled down to deep submicron dimensions. Hence, a concomitant reduction in source/drain junction depth is required to minimize short channel effects. Moreover, metal silicides can be used to reduce the parasitic resistance in LSI circuits, thus enhancing the performance of deep submicron complementary metal-oxide-semiconductor (CMOS) devices. The selfaligned-silicide (salicide) technology has become an essential part of the fabrication process for recent ultrahigh-speed CMOS logic LSI circuits.<sup>2</sup> Titanium silicide (TiSi<sub>2</sub>) is used exclusively as the material for this purpose.<sup>3-6</sup> However, the sheet resistance of TiSi<sub>2</sub> formed at annealing temperatures lower than 800 °C is relatively high because of the C49 structure. In addition, the sheet resistance of a TiSi<sub>2</sub> line increases as it is made narrower.8

Shallow  $p^+n$  junctions were conventionally difficult to be realized in part ascribed to the rapid anomalous diffusion of boron in Si. Several methods have been proposed to form shallow junctions, such as very-low-energy boron implantation, gas immersion laser doping, and so on. However, a high-temperature TiSi<sub>2</sub> process would further deepen the junction. In addition, in terms of the salicide technology, when silicide is formed on source/drain regions, a portion of the heavily doped junction is consumed as the silicidation

Therefore, new schemes should be employed to form silicided shallow junctions. Excellent silicided shallow junctions have been prepared by implanting dopant into thin metal or metal silicide layers and then driving the dopant into the Si substrate. 14-17 However, some inherent problems occur when these schemes are used, such as poor drive-in efficiency, difficult process control, and so on. 17-19 By implanting the dopant into thin polycrystalline-Si (poly-Si) films, good junctions can be formed without the above problems. 19-22 Devices made by this scheme have been described previously.<sup>20</sup> However, subsequent silicidation may affect the resultant junction characteristics, especially for  $p^+n$  junctions heavily doped by boron.<sup>21</sup> On the other hand, nickel-monosilicide (NiSi) has a resistivity of about 20  $\mu\Omega$  cm at annealing temperatures below 600 °C with a Si consumption of only about 0.82 Å for 1 Å NiSi (only 1.8 Å Si for 1 Å Ni). 13 In addition, the silicidation of Ni has good resistance to bridging between the gate and the source/drain.<sup>23</sup> Hence, NiSi silicides may be a proper material for low-temperature processing. Several articles have previously reported the applications of NiSi technology for deep submicron devices.<sup>23–25</sup>

In this study, the scheme that forms Ni-silicided shallow

392

proceeds. As the junction depth is reduced, the variation in the amount of Si consumed by the silicide makes it increasingly difficult to achieve the proper junction depth. Though the CoSi<sub>2</sub> process can achieve small sheet resistance at a low temperature as 700 °C, the consumed Si is significant. The Si consumption is about 1.04 Å for 1 Å CoSi<sub>2</sub> (3.6 Å Si for 1 Å Co) and is about 0.9 Å for 1 Å TiSi<sub>2</sub> (2.2 Å Si for 1 Å Ti).

a)Electronic mail: jmh@et.ntust.edu.tw

$p^+n$  junctions by BF<sub>2</sub><sup>+</sup> implantation into thin amorphous-Si (a-Si) or Ni/a-Si films on Si substrates and subsequent Ni silicidation has been investigated. Various thermal cycles and process conditions have been examined to clarify their effects on the resultant silicided shallow junctions.

#### II. EXPERIMENT PROCEDURE

Phosphorus-doped n-type Si wafers, (100)-oriented, 0.55–1.1  $\Omega$  cm, were first chemically cleaned by using the standard RCA process. A 500-nm-thick thermally grown oxide was used for patterning the active regions of diodes as well as for an etch mask for selective etching. The size of the diodes was  $1000\times1000~\mu\text{m}^2$ . After the patterning, 150-nm-thick films of a-Si were deposited onto the wafers by using a low-pressure-chemical-vapor-deposition (LPCVD) system at 550 °C. Furthermore, an additional patterning was done to etch off the a-Si films on the field oxide for performing the salicide process.

Some of the postpatterned samples were then BF<sub>2</sub><sup>+</sup> implanted at 25 or 75 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>, referred to as the implant through amorphous-silicon (ITA) samples. This reflects the usage of the thin a-Si films as an implantation barrier. After implantation, the specimens were covered with a Ni film of about 30 nm thickness using an electrongun evaporation system with a base pressure better than 1.5  $\times 10^{-6}$  Torr. Immediately, an a-Si capping layer of 5 nm thickness was deposited to prevent Ni oxidation during annealing. A two-step annealing process, by rapid thermal annealing (RTA) for 30 s or conventional furnace annealing (CFA) for 30 min in an N<sub>2</sub> ambient, was used for the salicide technique and dopant drive-in. The first step annealing was at 400 °C, and then the unreacted Ni on the field oxide was chemically removed by an etchant which consists of a 1:1:6 volume mixture of HCl, H<sub>2</sub>O<sub>2</sub>, and H<sub>2</sub>O, used at 55 °C. The second step annealing was performed at 500-800 °C for dopant drive-in and better silicide crystallinity. The reaction of thin Ni films with Si would form NiSi when the annealing temperature is higher than 350 °C. And, the NiSi would be further transformed into NiSi2 when an annealing temperature above 750 °C is undertaken. 26 The reported sheet resistivity for NiSi was about 20-30  $\mu\Omega$  cm, but that for NiSi<sub>2</sub> was about 35-60  $\mu\Omega$  cm.<sup>26</sup> The Si consumption is about 1.02 Å for 1 Å NiSi<sub>2</sub> (3.7 Å Si for 1 Å Ni). 13

Part of the former postpatterned samples were first covered by a thin Ni film with a capping layer, and then  $BF_2^+$  implanted at 25 or 75 keV to a dose of  $5 \times 10^{15} \, \mathrm{cm}^{-2}$ , called the implant through metal/amorphous-silicon (ITMA) samples. This reflects the usage of the thin Ni films and the underlying a-Si films as an implantation barrier. Similarly, a two-step annealing process was done after the implantation. It is noted that the technology discussed here is not a fully salicide process, since an extra mask was required for pattern definition of the a-Si films. This scheme would become a substantial salicide process, when a selective Si technique growth is used.

The junction depth beneath the silicides was determined by conducting a spreading-resistance-probe (SRP) measure-

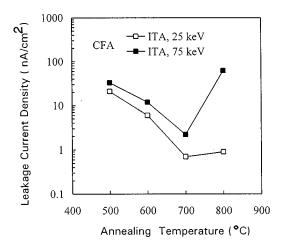

Fig. 1. Dependence of leakage current density on annealing temperature for the 25 and 75 keV implanted ITA samples Ni silicided by CFA processing.

ment. A JEOL-2000FX scanning transmission electron microscope (STEM) operating at 160 kV was used to examine the crystallinity of the silicide films. The electrical characteristics of the silicided junctions were achieved by utilizing an HP 4145B semiconductor parametric analyzer. At least ten diodes for each sample were taken to attain the average values. The average leakage current density of a junction is defined as the leakage at -5 V and at  $25\,^{\circ}$ C.

#### III. RESULTS AND DISCUSSION

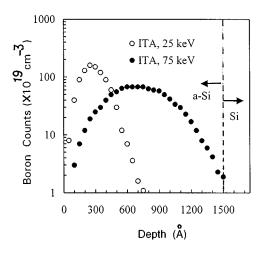

When the ITA scheme was used, the resultant silicided junctions exhibited good characteristics. Figure 1 shows the dependence of the leakage current density on the annealing temperature for the 25 and 75 keV implanted ITA samples Ni silicided by CFA processing. The forward ideality factor, n, corresponding to Fig. 1 is shown in Fig. 2. From the TRIM (transport of ion in matter) program simulation, the 25 keV implantation led to a distribution profile with most of the implanted dopant being confined in the thin a-Si films. The 75 keV implantation would result in considerable dopant penetration into the Si substrate. Figure 3 shows the TRIM

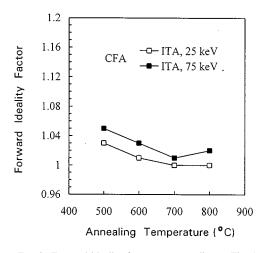

Fig. 2. Forward ideality factor corresponding to Fig. 1.

Fig. 3. TRIM simulation results for the  $BF_2^+$  implantation into thin  $\alpha$ -Si (150 nm) films on an Si substrate. The implantation is done at an energy of 25 or 75 keV to a dose of  $5\times10^{15}\,\mathrm{cm}^{-2}$ .

simulation results for the ITA samples implanted at 25 and 75 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup>, respectively. For the 25 keV implant sample, a silicided junction with a leakage of about  $0.7 \text{ nA/cm}^2$  and an n value of about 1.00 was obtained by CFA at  $700 \,^{\circ}\text{C}$ , and a junction leakage of about  $6 \,^{\circ}\text{nA/cm}^2$  can be achieved even at  $600 \,^{\circ}\text{C}$ .

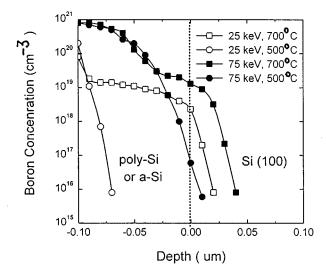

Moreover, better junctions were obtained with increasing CFA temperature until 700 °C, attributable to increased dopant activation, the dopant drive-in from the stacked silicide/poly-Si layer, the better defect recovery, and the better crystallinity of the deposited Si films after annealing. Figure 4 shows the boron concentration profile for the 25 and 75 keV implanted ITA samples annealed at 500 and 700 °C, respectively. In terms of the 500 °C annealing, the junctions formed by the 25 keV implanted samples were still within the *a*-Si films, and thus the junction leakage was considerable due to poor crystallinity of the implanted *a*-Si films. In addition, for the 75 keV implanted samples, the junctions

Fig. 4. Depth profiles of boron concentration for the 25 and 75 keV implanted samples annealed at 500 and 700 °C, respectively.

were formed near the a-Si/Si(100) interface. The resultant junction leakage was even larger than that for the 25 keV implanted specimens due to the higher number of substrate defects and the worse crystallinity of the 75 keV implanted a-Si films. On the other hand, the a-Si film would be transformed into the poly-Si structure at temperatures higher than about 600 °C. Hence, the junctions formed at 600 °C were further improved due to increased dopant activation and better crystallinity of deposited Si films after annealing. A grain size of about 0.3  $\mu$ m was observed. On the other hand, for the 700 °C annealing, the resultantly electrical junction depths for the 25 and 75 keV implanted samples were about 0.02 and 0.04 µm below the poly-Si/Si(100) interface. As a result, the junctions formed at 700 °C showed good characteristics. Moreover, the 25 keV implant samples resulted in a smaller junction leakage than the 75 keV implant ones due to lower implant-induced damage in the Si substrate. As a result, a lower implant energy is more helpful to lowtemperature junction formation by this scheme.

However, from Fig. 1, a significant increase of leakage from 2 to about 80 nA/cm<sup>2</sup> was found for the 75 keV implant samples, when the annealing temperature was raised from 700 to 800 °C. For a nonsilicided ITA sample, the dopant activation, the dopant drive-in, and the damage annihilation would be improved with increasing the annealing temperature. Accordingly, the junction deterioration for the 75 keV implant ITA samples Ni silicided at 800 °C was primarily ascribed to the further silicidation of NiSi into NiSi2 at this temperature. Anomalous dopant diffusion in Si was reported to occur during annealing due to interstitial defects.<sup>27</sup> In addition, the residual poly-Si thickness after the NiSi2 formation was reduced from about 100 to about 40 nm, and the grain size of the poly-Si was examined to be about 50 nm at 800 °C. Anomalous Ni diffusion through the poly-Si layer, directly via the grain boundaries, would thus probably occur during the silicidation of NiSi into NiSi<sub>2</sub>. Accordingly, the Ni penetration into the Si substrate would be further caused due to the presence of implant-induced defects in the Si substrate. Since the silicide formed at temperatures below 700 °C was still kept to be the NiSi structure formed at 400 °C of the first step annealing, no further silicidation and thus no anomalous Ni penetration would be induced at temperatures below 700 °C. Owing to more defects in Si substrates, the 75 keV implant ITA samples Ni silicided at 800 °C would result in much more serious junction deterioration than the 25 keV implant ones, as indicated in Figs. 1 and 2.

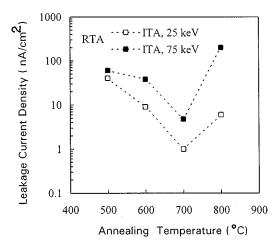

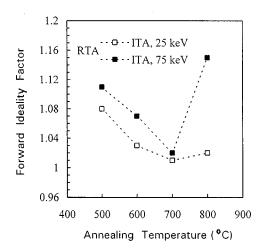

Moreover, as the ITA samples were Ni silicided by RTA processing, the results were not so good as those by CFA. Figure 5 shows the dependence of leakage current density on the annealing temperature for the 25 and 75 keV implant ITA samples Ni silicided by RTA processing. The forward ideality factor, n, corresponding to Fig. 5 is shown in Fig. 6. Rapid thermal processing was reported to effectively reduce the dopant diffusion, activate the dopant, and annihilate the implantation defects. <sup>28,29</sup> However, by this ITA method, the dopant for forming junctions, which was schemed to out dif-

Fig. 5. Dependence of leakage current density on annealing temperature for the 25 and 75 keV implanted ITA samples Ni silicided by RTA processing.

fuse from the stack NiSi/poly-Si layer, would be reduced due to the short annealing time. The dopants, boron, and arsenic, were reported to be forced out of the Ni silicides during silicidation, in contrast to the dopant absorption for the Ti silicidation. <sup>22,23</sup> As a result, the resultant junctions were still improved with increasing the RTA temperature until 700 °C, due to increased dopant activation and better crystallinity of the deposited Si films after annealing. For the 25 keV implant samples, a silicided junction with a leakage of about  $1 \text{ nA/cm}^2$  and an *n* value of about 1.01 was obtained by RTA at 700 °C, and a junction leakage of about 9 nA/cm<sup>2</sup> can be achieved at 600 °C. On the other hand, the further silicidation of NiSi into NiSi2 occurred when the annealing temperature was raised to 800 °C, which would confine more dopant within the NiSi2 silicide. And, RTA could not provide sufficient time to efficiently drive the dopant out of the NiSi2 silicides. A junction with smaller dopant concentration would lead to a larger depletion width at reverse bias. As a result, for a 800 °C anneal, RTA led to more serious junction degradation caused by anomalous Ni penetration than CFA, which can be inspected from Figs. 1 and 5.

Fig. 6. Forward ideality factor corresponding to Fig. 5.

Fig. 7. Dependence of leakage current density on annealing temperature for the 25 and 75 keV implanted ITMA samples treated by CFA processing.

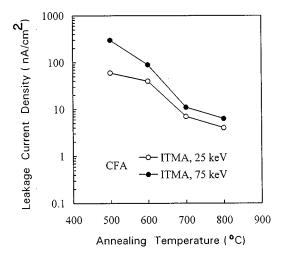

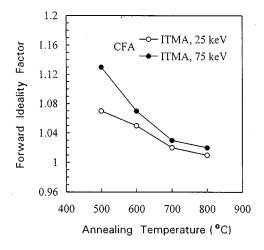

On the other hand, the ITMA scheme was intended to develop an even lower-temperature process. By implanting the dopant into the stacked Ni/a-Si layer, little damage was caused in the Si substrate. Figure 7 shows the dependence of leakage current density on the annealing temperature for the 25 and 75 keV implant ITMA samples treated by CFA processing. The forward ideality factor, n, corresponding to Fig. 7 is shown in Fig. 8. From the TRIM program simulation, the 25 keV implantation led to a distribution profile with most of the implanted dopant being confined in the thin Ni films. The 75 keV implantation would result in considerable dopant penetration into the a-Si film, but the resulting dopant penetration into the Si substrate was small. For the 25 keV implanted ITMA sample, a junction with a leakage of about  $7 \text{ nA/cm}^2$  and an *n* value of about 1.02 was formed by CFA at 700 °C. The dopant was mainly implanted into the thin Ni films of the stacked Ni/a-Si implantation barrier. Hence, as compared to the ITA scheme, the ITMA method produced a shallower boron implant profile and much better dopant confinement by the silicides. Accordingly, the ITMA scheme would lead to worse dopant drive-in efficiency than the ITA

Fig. 8. Forward ideality factor corresponding to Fig. 7.

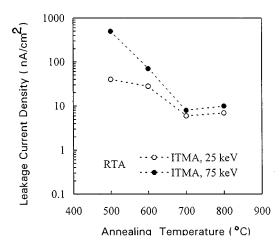

Fig. 9. Dependence of leakage current density on annealing temperature for the 25 and 75 keV implanted ITMA samples treated by RTA processing.

method. As a result, the ITMA samples showed worse junctions than the silicided ITA specimens, though sustaining lower implantation damage. However, unlike the silicided ITA samples, no significant junction degradation was observed at 800 °C for this scheme. As for the ITMA scheme, few defects were present in the Si substrate, thus largely suppressing the anomalous Ni penetration.

Moreover, by RTA processing, the resulting junctions of the ITMA samples were not as good as those of the silicided ITA samples. Figure 9 shows the dependence of leakage current density on the annealing temperature for the 25 and 75 keV implanted ITMA samples treated by RTA processing. A junction with a leakage of about 6 nA/cm<sup>2</sup> was obtained by the 25 keV implanted ITMA samples RTA treated at 700 °C. Though having shorter annealing/drive-in time, RTA can yield better dopant activation and defect recovery. <sup>28,29</sup> In addition, the dopant drive-in efficiency for the ITMA method was still low even by CFA. As a result, for the ITMA samples, RTA could still lead to junction characteristics comparable to those made by CFA. From Figs. 5 and 9 for RTA processing, it was also noted that relative to the silicided ITA samples, the ITMA samples showed less degraded junctions at 800 °C.

#### **IV. CONCLUSIONS**

As for the silicided ITA samples, excellent NiSi-silicided shallow  $p^+n$  junctions can be achieved. A junction with a leakage of about  $0.7 \, \text{nA/cm}^2$  and an ideality factor of about 1.00 is obtained by CFA at  $700\,^{\circ}\text{C}$ . The implantation energy and the crystallinity of the deposited Si films after annealing would greatly affect the junctions formed at various temperatures, attributable to different implantation effects and boron depth profile. By this Ni-silicided ITA scheme, a lower implant energy is more helpful to low-temperature junction formation, due to fewer implant-induced defects. However, while the silicidation of NiSi into NiSi<sub>2</sub>, anomalous Ni penetration into the Si substrate would be induced due to the implant-induced defects in the Si substrate. As a result, the junctions prepared by RTA treatment or higher implant en-

ergy are considerably deteriorated at 800 °C. On the other hand, the ITMA samples would sustain fewer defects, and thus the junction degradation at 800 °C is significantly suppressed. However, since the dopant is mainly implanted into the thin Ni films of the stacked Ni/a-Si layer, the junctions formed by this scheme are worse than those by the silicided ITA scheme, ascribed to lower dopant drive-in efficiency.

#### **ACKNOWLEDGMENTS**

This research was supported in part by the Republic of China National Science Council under the Contract No. NSC 86-2621-E-011-007-T. Valuable discussion with Professor H. C. Cheng at National Chiao-Tung University is with gratitude. In addition, the authors are also grateful for some technical help from the National Nano Device Laboratory, NSC.

- <sup>1</sup>J. R. Brews, W. Fichtner, E. H. Nicollian, and S. M. Sze, IEEE Electron Device Lett. **1**, 2 (1980).

- <sup>2</sup>M. E. Alperins, T. C. Hollaway, R. A. Haken, C. D. Gosmeryer, R. V. Karnaugh, and W. D. Parmantie, IEEE Trans. Electron Devices **32**, 141 (1985).

- <sup>3</sup>T. P. Chow and A. J. Steckl, IEEE Trans. Electron Devices **30**, 1480 (1983).

- <sup>4</sup>J. Hui, S. Wang, and J. Moll, IEEE Electron Device Lett. 6, 479 (1986).

<sup>5</sup>F. J. Lai, J. Y. Sun, and S. H. Dhong, IEEE Trans. Electron Devices 33, 345 (1986).

- <sup>6</sup>S. P. Murarka, M. H. Read, C. J. Dohery, and D. B. Fraser, J. Electrochem. Soc. **129**, 293 (1982).

- <sup>7</sup>V. Probst, H. Schaber, A. Mitwalsky, H. Kabia, and B. Hoffmann, J. Appl. Phys. **70**, 5327 (1991).

- <sup>8</sup>J. B. Laskey, J. S. Nakos, O. J. Chan, and P. J. Geiss, IEEE Trans. Electron Devices **38**, 262 (1991).

- <sup>9</sup>R. B. Fair, J. J. Wortman, and J. Liu, J. Electrochem. Soc. **131**, 2387 (1984).

- <sup>10</sup>A. Bousetta, J. A. Van den Berg, and P. C. Zalm, Appl. Phys. Lett. 58, 1626 (1991).

- <sup>11</sup>P. G. Carey, K. H. Weiner, and T. W. Sigmon, IEEE Electron Device Lett. 9, 542 (1988).

- <sup>12</sup>L. Rubin, D. Hoffman, D. Ma, and N. Herbots, IEEE Trans. Electron Devices 37, 183 (1990).

- <sup>13</sup>M.-A. Nicolet and S. S. Lau, in VLSI Electronics: Microstructure Science (Academic, New York, 1986), Vol. 6, Chap. 6, p. 457.

- <sup>14</sup>D. L. Kwong, D. C. Meyers, N. S. Alvi, L. W. Li, and E. Norbeck, Appl. Phys. Lett. 47, 688 (1985).

- <sup>15</sup>M. H. Juang and H. C. Cheng, Solid-State Electron. 35, 453 (1992).

- <sup>16</sup>D. L. Kwong and N. S. Alvi, J. Appl. Phys. **60**, 688 (1986).

- <sup>17</sup>M. H. Juang and H. C. Cheng, J. Appl. Phys. **71**, 1265 (1992).

- <sup>18</sup>R. Liu, D. S. Williams, and W. T. Lynch, J. Appl. Phys. **63**, 1990 (1988).

- <sup>19</sup>C. Y. Lu, J. J. Sung, R. Liu, N. S. Tsai, R. Singh, S. J. Hellenius, and H. C. Kirsch, IEEE Trans. Electron Devices 38, 246 (1992).

- <sup>20</sup>C. Y. Lu et al., IEEE Electron Device Lett. 9, 388 (1988).

- <sup>21</sup>M. H. Juang, C. T. Lin, and H. C. Cheng, Appl. Phys. Lett. **63**, 1267 (1993).

- <sup>22</sup>K. Maex, R. F. Keersmaecker, G. Ghosh, L. Delaey, and V. Probst, J. Appl. Phys. **66**, 5327 (1989).

- <sup>23</sup>T. Morimoto et al., IEEE Trans. Electron Devices 42, 915 (1995).

- <sup>24</sup>T. Ohguro *et al.*, in IEEE International Electronic Devices Meeting, 1995 (unpublished), p. 453.

- <sup>25</sup>T. Morimoto *et al.*, in IEEE International Electronic Devices Meeting, 1991 (unpublished), p. 653.

- <sup>26</sup>M.-A. Nicolet and S. S. Lau, in VLSI Electronics: Microstructure Science (Academic, New York, 1986), Vol. 6, Chap. 6, p. 417.

- <sup>27</sup>T. O. Sedgwick, A. E. Michel, V. R. Deline, S. A. Cohen, and L. B. Lasky, J. Appl. Phys. **63**, 1452 (1988).

- <sup>28</sup>S. R. Wilson, W. M. Paulson, R. B. Gregory, A. H. Hamdi, and F. D. Mcdaniel, J. Appl. Phys. **55**, 4162 (1984).

- <sup>29</sup>T. O. Sedgwick, J. Electrochem. Soc. **130**, 484 (1983).