Manuscript submitted September 2, 1997; revised manuscript received June 29, 1998.

NTT System Electronics Laboratories assisted in meeting the publication costs of this article.

#### REFERENCES

- D. Hisamoto, K. Nakamura, M. Saito, N. Kobayashi, S. Kimura, R. Nagai, T. Nishida, and E. Takeda, in Techn. Dig. Int. Electron Devices Meet., IEEE, p. 829 (1992).

- Y. Nakamura, N. Kobayashi, D. Hisamoto, K. Umeda, and R. Nagai, Jpn. J. Appl. Phys., 35, 1082 (1996).

T. Tsutsumi, H. Kotani, J. Komori, and S. Nagao, IEEE Trans. Electron Devices, ED-37, 569 (1990).

M. Sekine, N. Itoh, T. Akimoto, T. Shinmura, D. T. C. Huo, Y. Kakuhara, K. Kajiyama, Y. Yamada, K. Yamazaki, and Y. Murao, p. 184, in Solid State Devices and Materials, Extended Abstracts of Japan Society of Applied Physics, Tsukuha, Japan (1992).

- Society of Applied Physics, Tsukuba, Japan (1992).

5. K. Sakuma, K. Machida, K. Kamoshida, Y. Sato, K. Imai, and E. Arai, J. Vac. Sci. Technol., B, 13, 902 (1995).

6. M. Miyake, S. Aoyama, S. Hirota, and T. Kobayashi, J. Electrochem. Soc., 135, 2872 (1988).

- 7. Y. Kusumoto, K. Takakuwa, H. Hashinokuchi, T. Ikuta, and I. Nakayama, in Tungsten and Other Refractory Metals for VLSI Applications III, V. A. Wells, Editor, p. 217, Materials Research Society, Pittsburgh, PA (1987).

- 8. I. M. Band, Yu. I. Kharitonor, and M. B. Trzhaskovskaya, At. Data Nucl. Data Tables, 23, 443 (1979).

- 9. H. F. Winters and J. W. Coburn, Surf. Sci. Rep., 14, 161

- 10. H. Ibach, in Electron Spectroscopy for Surface Analy-

- sis, H. Ibach, Editor, p. 1, Springer, Berlin (1977). 11. M. P. Seah and W. A. Dench, Surf. Interface Anal., 1, 2

- 12. M. L. Yu and B. N. Eldridge, J. Vac. Sci. Technol., A, 7, 625 (1989).

- Takahagi, Oyo Butsuri, 59, 1441 (1990).

M. Ikeda, T. Rusyanto, and N. Nagashima, Hyomen Kagaku, 15, 164 (1994).

T. Ohno, Y. Kado, M. Harada, and T. Tsuchiya, IEEE

- Trans. Electron Devices, ED-42, 1481 (1995).

16. Y. Sato, T. Tsuchiya, T. Kosugi, and H. Ishii, in Proceedings of the 1995 IEEE International Silicon-on-Insulator Conference, p. 28, Tucson, AZ, IEEE (1995).

# Thin-Film Properties and Barrier Effectiveness of Chemically Vapor Deposited Amorphous WSix Film

M. T. Wang, Y. C. Lin, J. Y. Lee, C. C. Wang, and M. C. Chen\*

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan

#### ABSTRACT

Thin-Film properties and barrier effectiveness against copper (Cu) diffusion of a thin amorphous WSi<sub>x</sub> layer were investigated. The amorphous  $WSi_x$  layer was deposited by the chemical vapor deposition (CVD) method using the  $SiH_4/WF_6$  chemistry with the activation energy determined to be 3.0 kcal/mol. The CVD- $WSi_x$  film has a low film stress, low electrical resistivity, and excellent step coverage. The resistivity of the amorphous CVD- $WSi_x$  layer increases with the deposition temperature, but the residual stress of the layer decreases with the deposition temperature. The WSi<sub>x</sub>/Si structure is thermally stable up to at least 600°C, while the copper-contacted Cu/WSi<sub>x</sub>/Si structure with a 50 nm thick WSi<sub>x</sub> barrier is stable only up to 550°C. Moreover, the Cu/WSi<sub>x</sub>/p<sup>†</sup>-n junction diodes can sustain a 30 min thermal annealing up to 500°C without causing degradation in electrical characteristics. Barrier failure of the WSi<sub>x</sub> layer in the Cu/WSi<sub>x</sub>/Si structure at temperatures above 550°C is attributed to Cu atoms diffusion via fast paths in the WSi<sub>x</sub> layer. These fast paths were presumably developed from grain growth of the WSi<sub>x</sub> layer and/or thermal-stress-induced weak points in the WSi<sub>x</sub> layer.

## Introduction

As the interconnect linewidth shrinks continuously to deep-submicron dimensions, Al metallurgy becomes inadequate owing to its poor electromigration resistance; in addition, the resistivity of Al alloys is higher than desired for fast integrated circuits (ICs). Therefore, other metals with lower resistivity and superior electromigration resistance have been extensively studied.<sup>1-3</sup> Copper (Cu) has a lower resistivity than aluminum (Al) and it has an excellent electromigration resistance. Moreover, Cu can be deposited by chemical vapor deposition (CVD).<sup>4-6</sup> However, Cu diffuses fast in Si substrate and forms Cu-Si compounds at low temperatures (about 200°C),7,8 causing deep-level traps in Si. <sup>7</sup> Moreover, Cu adheres poorly to dielectric layers and drifts through oxide under field acceleration. <sup>9,10</sup> Therefore, a diffusion barrier between Cu and its surrounding layers is considered a prerequisite for Cu to be useful in silicon based IC applications.

Although many studies have shown that the sputterdeposited amorphous materials are very effective barriers for Cu metallization due to the absence of grain boundaries, 11-13 it is difficult to deposit metal barriers with acceptable conformity in submicron contact holes using the sputter deposition method. In contrast, CVD generally offers a much better conformal deposition than the physical vapor deposition (PVD) method; therefore, there is increasing interest in depositing amorphous barriers by CVD. Chemically vapor deposited silicon-rich (Si/W atomic ratio larger than 2.0)  $WSi_x$  layers used in polycide application has been extensively investigated using either  $SiH_4/WF_6^{14-21}$  or  $SiH_2Cl_2/WF_6$  chemistry. However, no study has been made on metal-rich (Si/W atomic ratio less than 2.0)  $WSi_x$ layers with respect to their barrier effectiveness against Cu

In this study, film properties and barrier effectiveness of thin, amorphous, metal-rich  $\mathrm{WSi}_x$  layers were investigated using electrical measurement as well as material analysis. The amorphous WSix layers were deposited by low-pressure chemical vapor deposition (LPCVD) using SiH4 reduction of  $WF_6$ . We evaluated the barrier capability of the amorphous WSi<sub>x</sub> layers for Cu metallization using a structure of Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes. Stability of the unpatterned samples of Cu/Si, WSi<sub>x</sub>/Si, and Cu/WSi<sub>x</sub>/Si structures was also investigated. The electrical measurement is believed to be a much more sensitive technique for barrier-failure detection than the material analyses, while the material analyses can provide microscopic information of material change, which is helpful to the understanding of failure mechanisms of the barrier layers. The results of this study may be useful for the integration of the amorphous WSi<sub>x</sub> in Cu metallization applications.

#### **Experimental**

The thermal stability of barrier layers was evaluated by measuring leakage current of thermally annealed Cu/bar-

<sup>\*</sup> Electrochemical Society Active Member.

rier/p $^+$ -n junction diodes. The starting materials for the diodes fabrication were 4 in., (100)-oriented, n-type silicon wafers with 4-7  $\Omega$  cm nominal resistivity. After RCA standard cleaning, the wafers were thermally oxidized to grow a 500 nm oxide layer. Diffusion areas with sizes of 500  $\times$ 500 and 1000  $\times$ 1000  $\mu m$  were defined on the oxide-covered wafers using the conventional photolithographic technique. The p $^+$ -n junctions with junction depth of 0.3  $\mu m$  were formed by  $BF_2^+$  implantation at 40 keV to a dose of 3  $\times$  10 $^{15}$  cm $^{-2}$ , followed by furnace annealing at 900°C for 30 min in  $N_2$  ambient.

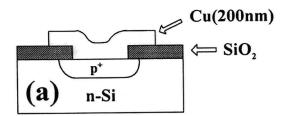

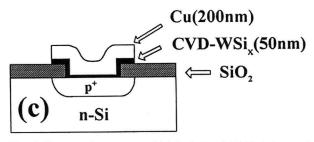

After the junctions were formed, the wafers were divided into three groups for the preparation of the following devices: Cu/p<sup>+</sup>-n, WSi<sub>x</sub>/p<sup>+</sup>-n, and Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes. The WSi<sub>x</sub> layer was deposited by CVD method to a thickness of about 50 nm using SiH<sub>4</sub> reduction of WF<sub>6</sub>. Prior to the CVD-WSi<sub>x</sub> deposition, the wafers were dipped in dilute HF (50:1) for 30  $\bar{s}$ , followed by a rinse in DI water for 5 min and spin dry. The wafers were then loaded into a load-locked coldwall W-CVD system (ULVAC ERA-1000S) within 5 min and transferred to the deposition chamber without exposure to the atmosphere. The ERA-1000S is a fully automatic single-wafer CVD system equipped with a cluster of multichambers, including a load/unload, buffer, and two deposition chambers. The system employs a robot unit in the buffer chamber for wafer transfer in vacuum. The aluminum-alloy reactor was water-cooled and was kept at a high vacuum base pressure of  $1\times 10^{-6}$  Torr by a turbopump. In this study, the CVD-WSix was deposited using the following conditions: substrate temperature 150–450°C, total gas pressure 12 mTorr,  $WF_6$  flow rate 2 sccm, and SiH<sub>4</sub> flow rate 6 sccm. We designated these deposition conditions with substrate temperature at 250°C as the standard deposition condition hereafter.

After the WSi<sub>x</sub> deposition, Cu metallization was applied for the fabrication of Cu/p<sup>+</sup>-n and Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes. Cu films 200 nm thick were sputter-deposited using a pure Cu target (99.99%) in Ar ambient at a pressure of 7.6 mTorr. The base pressure before sputtering was below 2  $\times$  10<sup>-6</sup> Torr. Finally, the Cu layer was patterned and then etched using 5 vol % HNO<sub>3</sub> dilute solution, and the WSi<sub>x</sub> layer was etched using SF<sub>6</sub>/N<sub>2</sub> plasma etching. For comparison, WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes without the Cu overlayer were also fabricated. The completed structures for the Cu/p<sup>+</sup>-n, WSi<sub>x</sub>/p<sup>+</sup>-n, and Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes are illustrated in Fig. 1.

To investigate thermal stability of the diodes, samples were thermally annealed in N2 flowing furnace for 30 min at various temperatures from 200 to 800°C. Reverse bias leakage current measurement on the thermally annealed Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes was used to evaluate the barrier capability of WSi<sub>x</sub>. An HP-4145B semiconductor parameters analyzer was used for the measurement, and at least 30 diodes were measured in each case. Unpatterned samples with structures of Cu/Si,  $WSi_x(250 \text{ nm})/Si$ , and Cu/WSi<sub>x</sub>(50 nm)/Si were also prepared for material analysis. A four-point probe was used for sheet resistance measurement. Film stress of the as-deposited WSi, layers was measured using a commercially available Tencor FLX-2320 system. Auger electron spectroscopy (AES) was used to determine the composition of  $\mathrm{WSi}_x$  films. X-ray diffraction (XRD) analysis using a 30 keV copper Kα radiation was used for phase identification, and scanning electron microscopy (SEM) was used to observe surface morphology.

## **Results and Discussion**

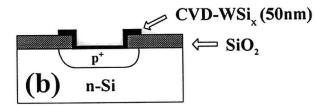

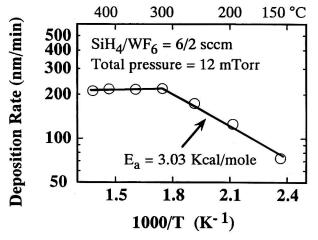

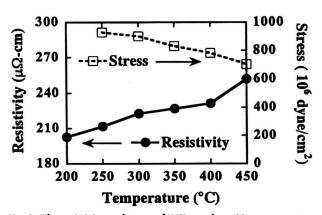

Thin-film properties of  $CVD\text{-}WSi_x$ .—To investigate the effects of deposition temperature on the film properties of the  $CVD\text{-}WSi_x$ , the deposition of  $WSi_x$  films was conducted at temperatures ranging from 150 to 450°C and with a total gas pressure of 12 mTorr,  $WF_6$  flow rate of 2 sccm, and  $SiH_4$  flow rate of 6 sccm. Figure 2 shows the deposition rate of  $WSi_x$  vs. deposition temperature. At temperatures below 300°C, the surface reaction was the rate-limiting process, and the activation energy of  $CVD\text{-}WSi_x$  was determined to be 3.0 kcal/mol. At temperatures above

Fig. 1. Completed structures of (a) Cu/p<sup>+</sup>-n, (b) WSi<sub>x</sub>/p<sup>+</sup>-n, and (c) Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes.

300°C, the deposition rate was independent of temperature and the process was mass-transfer-limited. The asdeposited WSi, layer was amorphous and remained in amorphous phase at temperatures up to 600°C (to be discussed later). Figure 3 shows the resistivity and film stress of the amorphous WSix layer vs. temperature of film deposition. The film resistivity increased with increasing temperature of film deposition. Since the decomposition of SiH<sub>4</sub> is a thermally activated process, the amount of Si incorporated into the WSi<sub>x</sub> film increases with increasing deposition temperature. It was reported that the resistivity of the chemically vapor deposited amorphous WSi<sub>x</sub> increased with increasing Si content in the as-deposited film. $^{15,26}$  The reported observation is consistent with the results of this work that the increase of deposition temperature resulted in increase of resistivity for the asdeposited WSi, film. The film stress of the WSi, layer decreased with increasing deposition temperature. A similar result was reported for silicon-rich WSi, films. The stress of WSi<sub>x</sub> decreased with the deposition temperature.<sup>27</sup> Fig-

Fig. 2. Deposition rate of WSi<sub>x</sub> vs. deposition temperature.

Fig. 3. Film resistivity and stress of WSi<sub>x</sub> vs. deposition temperature.

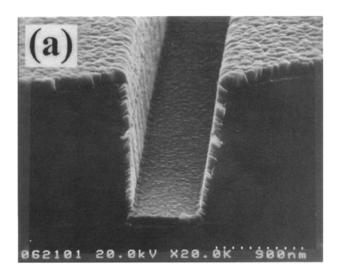

ure 4 shows the  $WSi_r$  films deposited on submicron trenches with aspect ratios of 2 and 5 using the "standard deposition condition." A highly conformal deposition of CVD-WSi, was obtained.

Electrical measurement.—The Cu/p<sup>+</sup>-n, Cu/WSi<sub>x</sub>/p<sup>+</sup>-n, and WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes were thermally annealed in an N<sub>2</sub> flowing furnace for 30 min at various temperatures. Figure 5 shows the statistical distributions of reverse bias leakage current density measured at -5 V for the Cu/p<sup>+</sup>-n,

Fig. 4. Step coverage of WSi<sub>x</sub> films deposited on submicron trenches with aspect ratio of (a) 2.0 and (b) 5.0. The WSi<sub>x</sub> films were deposited at a total gas pressure of 12 mTorr, WF<sub>6</sub> flow rate of 2 sccm, SiH<sub>4</sub> flow rate of 6 sccm, and substrate temperature of 250°C.

Cu/WSi<sub>x</sub>/p<sup>+</sup>-n, and WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes in which the WSi<sub>x</sub> barrier layers were deposited using our standard deposition conditions. The Cu/p<sup>+</sup>-n diodes without any barrier layer between Cu and Si substrate failed after annealing at 200°C (Fig. 5a). With a barrier layer of 50 nm CVD-WSi<sub>x</sub> between Cu and Si substrate, the Cu/WSix/p+-n junction diodes were able to retain the devices integrity up to 500°C. After annealing at 550°C, however, the diodes completely failed (Fig. 5b). For comparison, WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes without a Cu overlayer were also investigated. The WSi<sub>r</sub>/p<sup>+</sup>-n junction diodes retained their integrity up to 700°C and revealed only slight degradation after annealing at 750°C (Fig. 5c), presumably due to WSi2 formation (which consumed the substrate Si) and its grain growth as well as increase of film stress for the thermally annealed WSi, layer. Clearly, the WSi, layer itself did not degrade the electrical characteristics of the WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes up to 700°C, and the complete failure of the Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes at 550°C (Fig. 5b) is attributed to the presence of Cu overlayer on the WSi<sub>x</sub> surface.

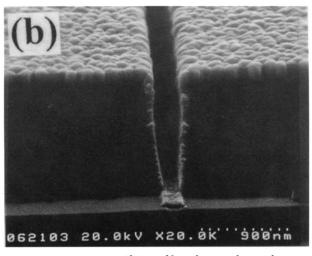

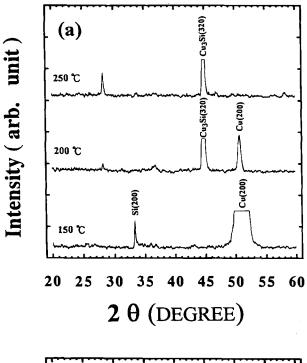

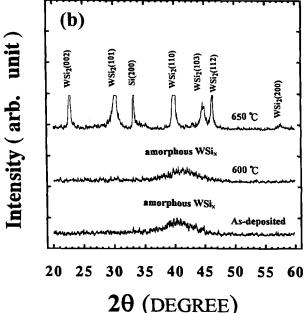

Material analyses.—XRD analysis.—Figure 6 shows XRD spectra for the Cu/Si and WSi<sub>x</sub>(250 nm)/Si samples after annealing at various temperatures. For the sample of Cu/Si annealed at 150°C, the XRD spectrum remained unchanged as compared with the as-deposited sample (not shown). However, a strong Cu<sub>3</sub>Si peak appeared for the sample annealed at 200°C, indicating formation of copper silicide. After annealing at 250°C, the (200) peak of Cu disappeared, indicating that the Cu overlayer might have translated into Cu<sub>3</sub>Si completely (Fig. 6a). For the sample of WSi<sub>x</sub>(250 nm)/Si, the amorphous state of the as-deposited WSi<sub>x</sub> remained unchanged even after annealing at 600°C. With annealing temperature raised to 650°C, a number of peaks belonging to WSi<sub>2</sub> phase appeared, indicating silicidation of the WSi<sub>x</sub> layer (Fig. 6b).

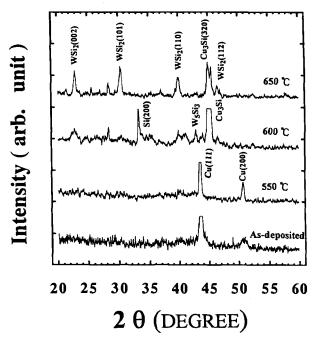

The XRD spectra for the Cu/WSi<sub>x</sub>(50 nm)/Si multilayer structure are illustrated in Fig. 7. Presumably because the WSi<sub>x</sub> layer was too thin and was covered with a 200 nm thick Cu film, the amorphous band belonging to the WSi<sub>x</sub> layer was too weak to be observed. The crystallization temperature of the WSi<sub>x</sub> layer in the Cu/WSi<sub>x</sub>/Si structure

Leakage Current Density (A/cm<sup>2</sup>)

Fig. 5. Histograms showing distributions of reverse bias leakage current density for (a)  $Cu/p^+-n$ , (b)  $Cu/WSi_x/p^+-n$ , and (c)  $WSi_x/p^+-n$  junction diodes annealed at various temperatures.

was found to be around 600°C. By comparing XRD spectra of the Cu/WSi\_x/Si sample with that of the WSi\_x/Si sample shown in Fig. 6b, we found that the crystallization temperature of WSi\_x layer in the Cu/WSi\_x/Si structure is about 50°C lower than that in the WSi\_x/Si sample. This discrepancy is presumably due to the presence of Cu overlayer for the Cu/WSi\_x/Si sample. It was reported that the crystallization temperature of amorphous  $\rm Ta_{36}Si_{14}N_{50}$  deposited on sapphire dropped from 1100 to 900°C when the  $\rm Ta_{36}Si_{14}N_{50}$  film was in contact with a polycrystalline copper layer.  $^{28}$  In this study we found that the WSi\_x/Si structure remained stable up to 600°C with no silicide phase formation (Fig. 6b); however, silicide phase appeared for the Cu/WSi\_x/Si sample annealed at 600°C due to the presence of Cu layer in contact with WSi\_x (Fig. 7).

The fact that the presence of Cu overlayer in the Cu/WSi<sub>x</sub>/Si sample reduced the crystallization temperature of WSi<sub>x</sub> may presumably be explained as follows.

Fig. 6. XRD spectra for (a) Cu/Si and (b) WSi<sub>x</sub>/Si samples annealed at various temperatures.

Fig. 7. XRD spectra for Cu/WSi<sub>x</sub>/Si samples annealed at various temperatures.

First, a small amount of Cu atom penetrated the WSi<sub>x</sub> layer to form Cu<sub>3</sub>Si phase at the WSi<sub>r</sub>/Si interface during thermal annealing at 600°C. This penetration probably occurred via localized defects, such as vacancy-accumulated voids, thermal-stress-induced microcracks of the WSi<sub>r</sub> layer, and/or grain boundaries which developed from grain growth of the  $\mathrm{WSi}_x$  layer. Second, the  $\mathrm{Cu}_3\mathrm{Si}$  formation at the WSi<sub>x</sub>/Si interface generated point defects, e.g., Si self-interstitial or vacancy in the Si lattice, 29,30 promoting silicidation of WSi, at the WSi, Si interface. Another possible mechanism for the accelerated silicidation of the WSi<sub>r</sub> can be the introduction of nucleation sites by the penetrated Cu atoms. The formation of copper silicide and tungsten silicide at the WSi,/Si interface resulted in a net volume change and produced more fast paths for Cu diffusion, thus further degrading the  $\mathrm{WSi}_x$  barrier capability. Table I summarizes the formation of silicides on thermally annealed Cu and/or WSi<sub>x</sub> contacted structures.

Sheet resistance measurement.—The sheet resistance change of annealed samples, normalized to the as-deposited sheet resistance value, is denoted as  $\Delta Rs/Rs$  % and defined as follows

$$\frac{\Delta Rs}{Rs} \% = \frac{Rs_{\rm after\,anneal} - Rs_{\rm as-deposited}}{Rs_{\rm as-deposited}} \times 100\%$$

Figure 8 shows the percentage change of sheet resistance vs. annealing temperature for the Cu/Si and WSi<sub>x</sub>/Si samples. The sheet resistance of Cu/Si remained constant following anneal at temperatures up to 175°C but increased drastically after annealing at 200°C. The drastic increase in sheet resistance is attributed to the formation of high-

Table I. Silicide formation on various Cu and WSi<sub>x</sub> contacted structures.

| Annealing temperature (°C) | Contact structure  |                      |                                                      |  |  |

|----------------------------|--------------------|----------------------|------------------------------------------------------|--|--|

|                            | Cu/Si              | WSi <sub>x</sub> /Si | Cu/WSi <sub>x</sub> /Si                              |  |  |

| 200                        | Cu <sub>2</sub> Si | ×                    | ×                                                    |  |  |

| 500                        | Cu₃Si<br>Cu₃Si     | ×                    | ×                                                    |  |  |

| 600                        | Ü                  | ×                    | $W_5Si_3$ , $WSi_2$ , $Cu_3Si$<br>$WSi_2$ , $Cu_3Si$ |  |  |

| 650                        |                    | $\mathrm{WSi}_2$     | $WSi_2$ , $Cu_3Si$                                   |  |  |

Note: "X" indicates no observation of silicide phase.

Fig. 8. Percentage change of sheet resistance vs. annealing temperature for the samples of Cu/Si and WSi<sub>x</sub>/Si.

resistivity  $\eta''$ -Cu<sub>3</sub>Si precipitate, as confirmed by XRD analysis shown in Fig. 6a. For the WSi<sub>x</sub>/Si sample, the sheet resistance remained stable up to 600°C. With the sample annealed at temperatures above 650°C, the sheet resistance decreased slightly with increasing annealing temperature. This is attributed to the formation of low-resistivity WSi<sub>2</sub> phase at temperatures above 650°C, as shown in Fig. 6b.

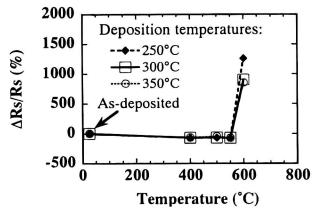

Fig. 9. Percentage change of sheet resistance vs. annealing temperature for the  $Cu/WSi_x/Si$  samples with the  $WSi_x$  films deposited at different substrate temperatures.

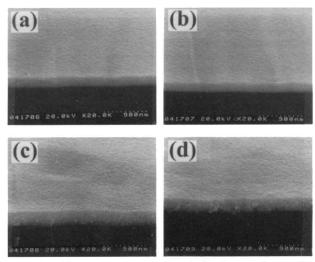

Fig. 10. Oblique view SEM micrographs for the  $WSi_x/Si$  samples (a) as-deposited and thermally annealed at (b) 600, (c) 650, and (d)  $800^{\circ}C$ .

Figure 9 shows the percentage change of sheet resistance vs. annealing temperature for the Cu/WSi\_x/Si samples in which the WSi\_x layers were deposited at different temperatures. It can be seen that the change of sheet resistance is not sensitive to the deposition temperature of the WSi\_x layer. The sheet resistance of the Cu/WSi\_x/Si samples decreased slightly after annealing at 400°C, presumably due to out-diffusion of impurities, grain growth of the Cu layer, and the annealing out of sputter-induced damage in the Cu film. Thermal stability of the Cu/WSi\_x/Si multilayer structure reached  $550^{\circ}$ C. After annealing at  $600^{\circ}$ C, drastic increase in sheet resistance was found for all samples, implying failure of the Cu/WSi\_x/Si structure. This is consistent with the results of XRD analysis shown in Fig. 7.

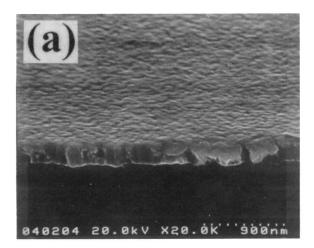

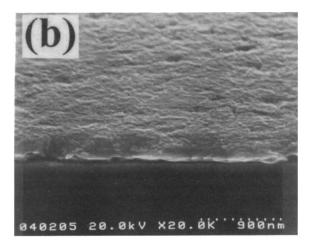

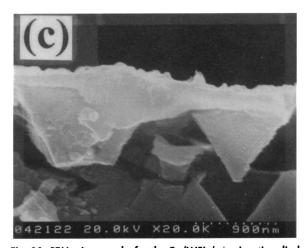

Fig. 11. SEM micrographs for the Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes (a) as-deposited and thermally annealed at (b) 500 and (c) 550°C.

Table II. Comparative results of barrier effectiveness for WSi<sub>x</sub> determined by different techniques of measurement and/or analysis.

| Leakage curre                                                                                         | ent measurement                          | Measurement/analysis methods Materials analysis          |                                         |                   |                   |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------|-----------------------------------------|-------------------|-------------------|--|

| Diode structure                                                                                       | Thermal stability<br>temperature<br>(°C) | Layered<br>structure                                     | Sheet resistance<br>measurement<br>(°C) | XRD<br>(°C)       | SEM<br>(°C)       |  |

| Cu/p <sup>+</sup> -n<br>Cu/WSi <sub>x</sub> /p <sup>+</sup> -n<br>WSi <sub>x</sub> /p <sup>+</sup> -n | 150<br>500<br>700                        | Cu/Si<br>Cu/WSi <sub>x</sub> /Si<br>WSi <sub>x</sub> /Si | 175<br>550<br>650                       | 150<br>550<br>600 | 175<br>500<br>600 |  |

SEM observation.—Figure 10 shows the SEM micrographs for the WSi<sub>x</sub>(250 nm)/Si samples before and after thermal annealing. No grain-like structure was observed for both the as-deposited as well as the 600°C-annealed samples (Fig. 10a and b). Grain-like structure was observed for the WSi<sub>x</sub> film annealed at 650°C, and it became more obvious at 800°C (Fig. 10c and d). This is consistent with the results of XRD analysis (Fig. 6b) and sheet resistance measurement (Fig. 8). Figure 11 shows the SEM micrographs for the Cu/WSi<sub>x</sub>(50 nm)/p<sup>+</sup>-n junction diodes before and after thermal anneal. The integrity of the Cu/barrier/Si structure basically remained unchanged after annealing at 500°C (Fig. 11b); however, large Cu<sub>3</sub>Si precipitates were found after annealing at 550°C. With cross-sectional SEM analysis, it has been determined that a fully developed Cu<sub>3</sub>Si precipitate is inverted pyramid-shaped and bounded by Si{111} planes (Fig. 11c).<sup>29</sup> Comparative results of barrier effectiveness for the WSi<sub>x</sub> layers determined by different techniques of measurement and/or analysis are summarized in Table II.

#### Conclusions

Thin-film properties of amorphous WSi, layers and thermal stability of Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes were investigated. The amorphous WSi<sub>x</sub> layer was deposited by (CVD) method using the SiH<sub>4</sub>/WF<sub>6</sub> chemistry with the activation energy determined to be 3.0 kcal/mol. The WSi, film has a low film stress, low electrical resistivity, and excellent step coverage. The WSi<sub>x</sub>/Si structure is thermally stable up to at least 600°C, while the copper-contacted Cu/WSi<sub>x</sub>/Si structure with a 50 nm thick WSi<sub>x</sub> barrier is stable only up to 550°C. Moreover, the Cu/WSi<sub>x</sub>/p<sup>+</sup>-n junction diodes are able to sustain a 30 min thermal annealing at temperatures up to 500°C without causing degradation to the devices electrical characteristics. Barrier failure of the WSi, layer at temperatures above  $550\,^{\circ}\text{C}$  is attributed to Cu diffusion via fast paths, which are presumably developed from grain growth of the  $\mathrm{WSi}_x$  layer and/or thermal stress-induced weak points in the WSi<sub>x</sub> layer.

### Acknowledgments

This work was supported by the National Science Council (ROC) under contract no. NSC86-2215-E-009-040.

Manuscript submitted September 12, 1997; revised manuscript received August 21, 1998.

National Chiao-Tung University assisted in meeting the publication costs of this article.

#### REFERENCES

- 1. S. P. Murarka, R. J. Gutmann, A. E. Kaloyeros, and W. A. Lanford, *Thin Solid Films*, 236, 257 (1993).

- B. Roberts, A. Harrus, and R. L. Jackson, Solid State Technol., 69 (Feb 1995).

- 3. J. M. E. Harper, E. G. Colgan, C. K. Hu, J. P. Hummel,

- L. P. Buchwalter, and C. E. Uzoh, MRS Bull., 23 (Aug 1994).

- V. M. Dubin and Y. S. Diamand, J. Electrochem. Soc., 144, 898 (1997).

- 5. D. H. Kim, R. H. Wentorf, and W. N. Gill, J. Elec-

- trochem. Soc., 140, 3273 (1993).

J. C. Chiou, K. C. Juang, and M. C. Chen, J. Electrochem. Soc., 142, 177 (1995).

C. A. Chang, J. Appl. Phys., 67, 566 (1990).

L. Stolt and F. M D'Heurle, Thin Solid Films, 189, 269

- (1990).

- 9. Y. S. Diamand, A. Dedhia, D. Hoffstetter, and W. G. Oldham, J. Electrochem. Soc., 140, 2427 (1993). 10. A. L. S. Loke, C. Ryu, C. P. Yue, J. S. H. Cho, and S. S.

- Wong, IEEE Electron Device Lett., EDL-17, 549 (1996).

- 11. M. A. Nicolet, *Thin Solid Films*, **107**, 415 (1978). 12. R. S. Nowicki and M.-A. Nicolet, *Thin Solid Films*, **96**, 317 (1982)

- 13. J. S. Reid, R. Y. Liu, P. M. Smith, R. P. Ruiz, and M.-A. Nicolet, Thin Solid Films, 262, 218 (1995)

- 14. D. L. Brors, J. A. Fair, K. A. Monnig, and K. C. Saraswat, Solid State Technol., 183 (April 1983)

- T. E. Clark, J. Vac. Sci. Technol., B6, 1678 (1988).

M. Kottke, F. Pintchovski, T. R. White, and P. J. Tobin, J. Appl. Phys., 60, 2835 (1986)

- 17. Y. Shioya, T. Itoh, I. Kobayashi, and M. Maeda, J. Elec-

- Trochem. Soc., 133, 1475 (1986).

Y. Shioya and M. Maeda, J. Appl. Phys., 60, 327 (1986).

D. K. Sadana, A. E. Morgan, M. H. Norcott, and S. Naik, J. Appl. Phys., 62, 2830 (1987).

D. Dobkin, L. Bartholomew, G. McDaniel, and J. Department, L. Electrophys. Soc. 127, 1633 (1990).

- Dontney, J. Electrochem. Soc., 137, 1623 (1990). 21. N. Thomas, A. M. Dutron, C. Vahlas, C. Bernard, and R.

- Madar, *J. Electrochem. Soc.*, **142**, 1608 (1995). 22. T. H. Wu, R. S. Roster, B. C. Lamartine, R. B. Gregory,

- and H. G. Tompkins, J. Vac. Sci. Technol., B6, 1707 (1988)

- S. G. Telford, M. Eizenberg, M. Chang, A. K. Sinha, and P. R. Gow, Appl. Phys. Lett., 62, 1766 (1993).

T. Hara, T. Miyamoto, and T. Yokoyama, J. Electrochem. Soc., 136, 1177 (1989).

J. E. J. Schmitz, Chemical Vapor Deposition of Tungaton and Transactor Silvidge for VI SIJIJI SI Applies.

- sten and Tungsten Silicides for VLSI/ULSI Applications, pp. 171–208, Noyes Publications, Park Ridge, NJ (1992).

- 26. J. H. Sone and H. J. Kim, in Advanced Metallization J. H. Sone and H. J. Kim, in Advanced Metallization and Processing for Semiconductor Devices and Circuits, A. Katz, S. P. Murarka, Y. I. Nissim, and J. M. E. Harper, Editors, Vol. 260, p. 621, Materials Research Society, Pittsburgh, PA (1990).

Y. Shioya, T. Itoh, S. Inoue, and M. Maeda, J. Appl. Phys., 58, 4194 (1985).

E. Kolawa, J. S. Chen, J. S. Reid, P. J. Pokela, and M. A. Nicolet, J. Appl. Phys., 70, 1369 (1991).

K. Holloway, P. M. Fryer, C. Cabral, Jr., J. M. E. Harper, P. J. Bailey, and K. H. Kelleher, J. Appl. Phys., 71, 5433 (1992).

- 5433 (1992).

- 30. M. Ronay and R. G. Schad, Phys. Rev. Lett., 64, 2042 (1990).