# The Effect of Native Oxide on Thin Gate Oxide Integrity

Albert Chin, Senior Member, IEEE, B. C. Lin, W. J. Chen, Y. B. Lin, and C. Tsai

Abstract—We have studied the effect of native oxide on thin gate oxide integrity. Much improved leakage current of gate oxide can be obtained by in situ desorbing the native oxide using a HF-vapor treated and  $\mathbf{H}_2$  backed process. Furthermore, extremely sharp interface between oxide and Si is obtained, and good oxide reliability is achieved even under a high current density stress of 11 A/cm² and a large charge injection of  $7.9 \times 10^4$  C/cm². The presence of native oxide will increase the interface roughness, gate oxide leakage current and stress-induced hole trap.

# I. INTRODUCTION

CALING down the thickness of gate oxide has been studied extensively because of the improved CMOS device performance [1]–[7]. The key issues for these thin oxides are thickness uniformity and interface smoothness; unfortunately, native oxide roughens the initial surfaces. Furthermore, the reliability of oxide is also strongly degraded by the presence of native oxide [8]. Recently, we have demonstrated the *in situ* desorption of native oxide at 950 to 1000 °C, and achieved atomically smooth oxide interface [9]. In this letter, we have studied the effect of native oxide on thin gate oxide integrity. We have used HF-vapor passivation [10] to reduce the formation of native oxide and lower down the thermal budget. In combination of H<sub>2</sub> bake, HF-vapor treatment can result in improved oxide integrity at a growth temperature of 850 °C for the 27 Å oxide.

### II. EXPERIMENTAL

After a modified RCA cleaning, a HF dipping, rinsing in DI water and spun dry, the 4-in [100] wafer was treated by a HF-vapor and immediately loading into the low-pressure furnace. Native oxide was desorbed in this leak-tight low-pressure furnace at 900 °C under a high flow rate of hydrogen, and lowered down to 850 °C for initiating the growth [11]. More detailed process can be found elsewhere [9], [12]. For comparison, control samples were fabricated with the same recipe except without receiving the HF-vapor treatment and *in situ*  $\rm H_2$  bake at 900 °C. AFM, TEM, capacitor  $\rm \it I-V$ ,

Manuscript received December 3, 1997; revised July 15, 1998. This work was supported by the National Science Council, Taiwan, R.O.C. under Grant NSC 87-2215-E-009-069.

- A. Chin, B. C. Lin and C. Tsai are with the Departmenty of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

- W. J. Chen is with the Department of Mechanical Materials Engineering, National Yun-Lin Polytechnic Institute, Huwei, Taiwan, R.O.C.

- Y. B. Lin is with the Department of Electrical Engineering, Chung Hua University, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(98)08173-7.

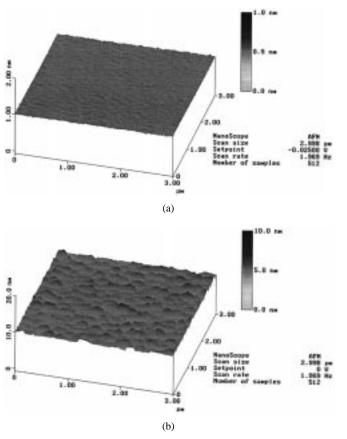

Fig. 1. AFM images of (a) with and (b) without the HF-vapor treatment and  $\rm H_2$  bake, and the rms values are 0.1 Å and 2.9 Å, respectively.

and constant current stress are measured to study the gate oxide integrity.

### III. RESULTS AND DISCUSSION

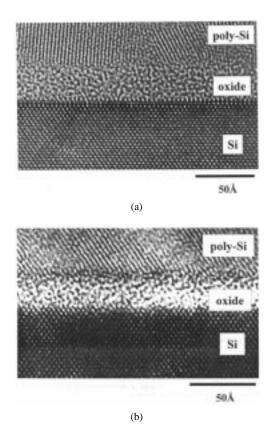

Fig. 1(a) and (b) show the AFM images of the 27 Å oxides with and without the HF-vapor treatment and *in situ*  $H_2$  bake, respectively. Using this process, the surface rms roughness is much improved from 2.9 Å toward 0.1 Å on a broad  $3 \mu m \times 3 \mu m$  area. We have further characterized this very smooth oxide by TEM. Fig. 2(a) and (b) show the atomic lattice image of the 27 Å oxide with and without the HF-vapor treatment and *in situ*  $H_2$  bake, respectively. Very smooth interface between oxide and Si can be observed in Fig. 2(a). Because it is extremely difficult to achieve such smooth surface by wet cleaning, surface atoms migration, after native oxide desorption, may be the explanation for this work and our previous study at higher  $H_2$  baked temperatures [9].

CHIN et al.: EFFECT OF NATIVE OXIDE 427

Fig. 2. Cross-sectional TEM lattice images of (a) with and (b) without the HF-vapor treatment and  $H_2$  bake.

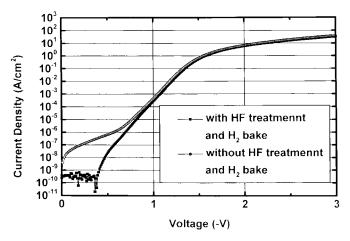

Fig. 3. J-V characteristics of the 27 Å oxide (a) with and (b) without the HF-vapor treatment and  $H_2$  bake. The measured area is 500  $\mu$ m by 500  $\mu$ m.

We have also studied the dependence of leakage current on residual native oxide. Fig. 3 presents the measured J–V characteristics of MOS diodes with a 27 Å oxide. An increased gate leakage current at low voltages (<0.5 V) is observed for the control sample without the HF-vapor treatment and in situ H<sub>2</sub> bake, even considering the typical 1 Å thickness difference among these oxides. This phenomena is very similar to the stress-induced leakage current (SILC) [13], where the increased leakage current is attributed to trap generation or local thinning in oxide [14]. In fact, Liu et al. has also observed such excess leakage and attributed this effect as intrinsic traps

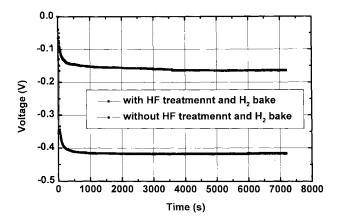

Fig. 4. Capacitor voltage change of the 27 Å oxide (a) with and (b) without the HF-vapor treatment and  $\rm H_2$  bake.

[15]. However, our data suggests that such intrinsic traps are process-dependent and strongly related to the presence of native oxide.

We have further studied the oxide stress effect on the presence of residual native oxide. Fig. 4 shows the measured voltage change of MOS capacitors as a function of time, under a constant stress of 11 A/cm<sup>2</sup>. The voltage change is plotted because it is much clearer to show the stress effect. Very high current density is applied, because almost no variation can be measured at lower values. As shown in Fig. 4, no breakdown can be observed for both oxides even under a large charge injection of  $7.9 \times 10^4$  C/cm<sup>2</sup>. The good reliability is consistent with the previous report by reducing native oxide formation under an ultra-dry environment [8]. However, the voltage change is higher in control sample without HF-vapor treatment and in situ H2 bake. This increased concentration of generated hole trap is consistent with the oxide leakage current and interface roughness. Therefore, the presence of residual native oxide not only creates intrinsic traps but also increases the generation rate of hole trap after stress.

## IV. CONCLUSION

In conclusion, much improved oxide interface roughness, leakage current and stress-induced trap can be obtained by using HF-vapor treated and H<sub>2</sub> baked process.

### ACKNOWLEDGMENT

The authors would like to thank the Prof. K. C. Hsieh at Univ. of Illinois for his great help.

### REFERENCES

- [1] J. Ahn, W. Ting, T. Chu, S. Lin, and D. L. Kwong, "High quality thin gate oxide prepared by annealing low-pressure chemical vapor deposited SiO<sub>2</sub> in N<sub>2</sub>O," *Appl. Phys. Lett.*, vol. 59, no. 3, pp. 283–285, 1991.

- [2] C. T. Liu, Y. Ma, J. Becerro, S. Nakahara, D. J. Eaglesham, and S. J. Hillenius, "Light nitrogen implant for preparing thin-gate oxides," *IEEE Electron Device Lett.*, vol. 18, pp. 105–107, Mar. 1997.

- [3] K. Kumar, A. Chou, A. I. Chou, C. Lin, P. Chowdhury, J. C. Lee, and J. K. Lowell, "Optimization of sub-3 nm gate dielectrics grown by rapid thermal oxidation in a nitric oxide ambient," *Appl. Phys. Lett.*, vol. 70, no. 3, pp. 384–386, 1997.

- [4] H. S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nakamura, M. Saito, and H. Iwai, "1.5 nm direct-tunneling gate oxide Si MOSFET's," *IEEE Trans. Electron Devices*, vol. 43, pp. 1233–1241, Aug. 1996.

- [5] C. Hu, "Gate oxide scaling limits and projection," in *IEDM Tech. Dig.*, pp. 319–322, 1996.

- [6] R.-H. Yan, D. Monroe, J. Weis, A. Mujtaba, and E. Westerwick, "Reducing operating voltage from 3,2, to 1 volt and below-challenges and guidelines for possible solutions," in *IEDM Tech. Dig.*, 1995, pp. 55–58.

- [7] T. Ohguro, M. Saito, E. Morifuji, K. Murakami, K. Matsuzaki, T. Yoshitomi, T. Morimoto, H. S. Momose, Y. Katsumata, and H. Iwai, "High efficiency 2 GHz power Si-MOSFET design under low supply voltage down to 1 V," in *IEDM Tech. Dig.*, 1996, pp. 83–86.

- [8] J. Yugami, T. Itoga, and M. Ohkura, "Highly-reliable gate oxide formation for giga-scale LSI's by using closed wet cleaning system and wet oxidation with ultra-dry unloading," in *IEDM Tech. Dig.*, 1995, pp. 855–858.

- [9] A. Chin, W. J. Chen, T. Chang, R. H. Kao, B. C. Lin, C. Tsai, and J. C.-M. Huang, "Thin oxides with in situ native oxide removal," *IEEE Electron Device Lett.*, vol. 18, pp. 417–419, Sept. 1997.

- [10] J. C. Lou, C. Galewski, and W. G. Oldham, "Dichlorosilane effects on low-temperature selective silicon epitaxy," *Appl. Phys. Lett.*, vol. 58, no. 1, pp. 59–61, 1991.

- [11] B. S. Meyerson, F. J. Himpsel, and K. J. Uram, "Bistable conditions for low-temperature silicon epitaxy," *Appl. Phys. Lett.*, vol. 57, no. 10, pp. 1034–1036, 1990.

- [12] A. Chin, B. C. Lin, and W. J. Chen, "High quality epitaxial Si grown by a simple low-pressure chemical vapor deposition at 550 degrees C," *Appl. Phys. Lett.*, vol. 69, no. 11, pp. 1617–1620, 1996.

[13] S. I. Takagi, N. Yasuda, and A. Toriumi, "Experimental evidence of

- [13] S. I. Takagi, N. Yasuda, and A. Toriumi, "Experimental evidence of inelastic tunneling and new *I-V* model for stress-induced leakage current," in *IEDM Tech. Dig.*, 1996, pp. 323–326.

- [14] S. H. Lee, B. J. Cho, J. C. Kim, and S. H. Choi, "Quasibreakdown of ultrathin gate oxide under high field stress," in *IEDM Tech. Dig.*, 1994, pp. 605–608.

[15] C. T. Liu, A. Ghetti, Y. Ma, G. Alers, C. P. Chang, K. P. Cheung,

- [15] C. T. Liu, A. Ghetti, Y. Ma, G. Alers, C. P. Chang, K. P. Cheung, J. I. Colonell, W. Y. C. Lai, C. S. Pai, R. Liu, H. Vaidya, and J. T. Clemens, "Intrinsic and stress-induced traps in direct tunneling current of 2.3–3.8 nm oxides and unified characterization methodologies of sub-3 nm oxides," in *IEDM Tech. Dig.*, 1997, pp. 85–88.