# Field Inversion Generated in the CMOS Double-Metal Process Due to PETEOS and SOG Interactions

Shun-Liang Hsu, Lu-Min Liu, Chung-Hsin Fang, Shu-Lan Ying, Tien-Li Chen, Mou-Shiung Lin, Member, IEEE, and Chun-Yen Chang, Fellow, IEEE

Abstract-Severe field inversion has been observed in the circuits fabricated by the CMOS double metal process using PETEOS/inorganic SOG/PEOX as the inter-metal dielectrics and PEOX/PECVD nitride as the passivation layer. We have performed detailed studies to conclude that the field inversion is caused by the interaction between PETEOS and non-carbonbased SOG, triggered by the H+ released from PECVD nitride during the sintering. No field inversion is observed when PEOX/ inorganic SOG/PEOX is used as the inter-metal dielectrics. The effect of field inversion on the circuit yield is also discussed.

#### I. Introduction

PIN-ON GLASS (SOG) sandwiched by either PECVD Itetraethylorthosilicate (PETEOS) or PECVD silanebased oxide (PEOX) has been widely used as the intermetal dielectrics in the CMOS double-metal process. The dielectric structure provides good planarization and dielectric isolation. However, it has been reported that carbon-based spin-on glass causes field inversion in CMOS circuits under certain process conditions [1]. The inorganic spin-on glass has been shown to be free of the field inversion problem [1]. In this paper, we report severe field inversion when the inorganic spin-on glass is used in the presence of PETEOS. We have performed systematic experiments to identify causes of the field inversion. The impact of field inversion on the circuit yield are also discussed.

### II. EXPERIMENTAL

The devices were fabricated using the conventional 1.0μm CMOS process. The field oxide thickness was 7500 Å as-grown, and 4500 Å on finished wafers. The field isolation was enhanced by a p field implant with a boron dose of  $9 \times 10^{13} / \text{cm}^2$ , and 150-keV energy. For comparison, four types of inter-metal dielectric schemes were

Manuscript received January 10, 1991; revised June 26, 1992. The review of this paper was arranged by Associate Editor J. Fonash.

- S. L. Hsu, L. M. Liu, C. H. Fang, S. L. Ying, and M. S. Lin are with Taiwan Semiconductor Manufacturing Company, Hsin-Chu, Taiwan, ROC.

- T. L. Chen was with Taiwan Semiconductor Manufacturing Company, Hsin-Chu, Taiwan, ROC. He is now with Charter Semiconductor Corporation, Singapore.

- C. Y. Chang is with the Department of Electronic Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan, ROC. IEEE Log Number 9204305.

fabricated, namely, PETEOS/SOG/PEOX, PEOX/SOG/ PEOX, 10 000-Å PETEOS, and 10 000-Å PEOX. Here SOG material used is non-carbon-based. The bottom PETEOS or PEOX film was 3000 Å thick, while the top PEOX film was 5000 Å thick for the first two types of inter-metal dielectric schemes. The SOG was doublecoated with total thickness of 2000 Å and was cured at 420°C. The passivation was formed by 5000-Å-thick PEOX deposition, followed by 7000- Å-thick PECVD nitride deposition. Sintering at 410°C in the 80% N<sub>2</sub>/20% H<sub>2</sub> ambient was performed after the passivation via etch. For comparison, some wafers were sintered before PECVD nitride deposition.

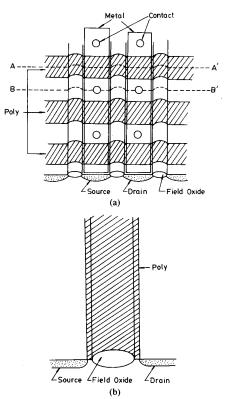

A special field device, as shown in Fig. 1(a), was designed to evaluate the integrity of the inter-metal dielectrics. This test structure was similar to the one used in [1]. The source and drain of the field device formed a comb structure with polysilicon running perpendicular to the source and drain. Metal lines were running on the top of source and drain and contacting the diffusion areas through contact vias. This test structure actually consisted of two parallel field devices: one was along the cross section of line AA', which has a polysilicon gate but no n<sup>+</sup> implants in the source and drain regions; the other was along the cross section of line BB', which has n<sup>+</sup> implants in the source and drain regions, but no polysilicon gate. The field structure along cross section of line BB' was very sensitive in detecting the amount of charges in the dielectric films deposited during backend processes. The channel length of the field device was 2.4  $\mu$ m, and the width was 1200 µm. For comparison, a regular field device, as shown in Fig. 1(b), with 2.4-μm channel length and 20 µm channel width was also designed. In our experiments, we measured the threshold voltages of these two types of field devices to examine the isolation integrity of CMOS process.

## III. RESULTS AND DISCUSSIONS

# A. General Observations

It has been known that the backend process can damage the MOS devices [1]-[4]. Many precautions are being taken to prevent damage, and many extra processes are

Fig. 1. (a) A special field device test structure consisting of two parallel field devices: one along the cross section of line AA', which has a polysilicon gate but no  $\mathfrak{n}^+$  implants in the source and drain regions; the other along the cross section of line BB', which has  $\mathfrak{n}^+$  implants in the source and drain regions, but no polysilicon gate. A regular field device is shown in (b).

used to anneal the damage in modern VLSI technologies. During the development of our 1.0-µm CMOS doublemetal process, we have initially used silicate-based SOG sandwiched with PETEOS (i.e., PETEOS/SOG/ PETEOS) as the inter-metal dielectrics. Very low threshold (~0 V) of n-type special field devices (as depicted in Fig. 1(a)) was routinely found. We have tried to replace the top PETEOS layer by PEOX (i.e., PETEOS/SOG/ PEOX), and found the threshold voltage of n-type special field devices increases, though still low (<8 V). However, the p-type special field devices, the n- and p-type regular field devices (as depicted in Fig. 1(b)), and the n- and p-type thin-oxide devices behave normally, even when the n-type special field devices have field inversion problems. The field inversion can be suppressed by applying a back-gate bias. These observations are similar to those reported in [1]. The channel inversion is believed to be due to changes in the dielectric films above the field oxide where polysilicon is not present. The charging effects induced during the backend process can be blocked by the presence of polysilicon or metal-1 due to the shielding phenomena. This explains why normal thin oxide devices as well as regular field oxide devices can be obtained, even when there are charges generated during the backend process.

## B. Systematic Studies

In order to identify causes of the charging effects in dielectric films, we have performed the following systematic experiments. Fig. 2(a) shows the thresholds of n-type special field devices for 12 wafers with four splits of different intermetal dielectric schemes (i.e., 3 wafers in each split). From now on, the field threshold voltages indicate the threshold voltage of n-type special field devices, unless it is particularly specified. The wafers in the group using PETEOS/SOG/PEOX show field inversion, while wafers in groups using PEOX/SOG/PEOX, PEOX, and PETEOS do not show the field inversion problem. We also experience significant fluctuations in the field threshold voltage when there is field inversion. Our experiments confirm the reported results that inorganic SOG does not cause field inversion when sandwiched in PEOX material [1]. The field inversion occurs only when inorganic SOG is interfacing with PETEOS. The effect of carbon on the field inversion problem has been previously addressed by comparing the carbon-based and non-carbon-based SOG [1]. Since PETEOS is a carbon-based material, it may supply carbon to silicate-based SOG, and induce the reaction as described in [1].

The impacts of the field inversion on the chip yield for a particular ASIC chip design (a microcontroller chip, chip size ~ 100 kmil²) fabricated on the wafers used for Fig. 2(a) are shown in Fig. 2(b). This microcontroller chip design is so sensitive to field inversion that the yield is almost zero for wafers with PETEOS/SOG/PEOX as intermetal dielectrics. For other typical ASIC chip products, we have usually observed a yield loss between 10 and 20% due to field inversion based on our other experiments. In Fig. 2(b), the circuit yield for wafers using 10 000-Å PETEOS and 10 000-Å PEOX is also very low. From SEM cross sections, we found the low yield for these two cases is caused by metal opens and shorts due to lack of planarization.

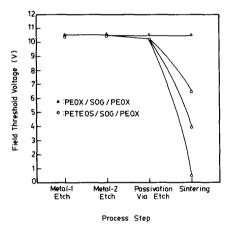

To understand mechanisms of charge generation in dielectric films, we monitored the field threshold of various processing steps during the backend process, and the results are summarized in Fig. 3. For the PETEOS/SOG/ PEOX inter-metal dielectric scheme, minor degradation of special field devices is shown at the measurement after the passivation via etch, and dramatic decrease in the field threshold is detected after sintering at 410°C in an 80%  $N_2/20\%$  H<sub>2</sub> ambient. No degradation is found through the backend process for the PEOX/SOG/PEOX intermetal dielectric scheme. It has been shown that PECVD nitride can release H<sup>+</sup> during sintering [1]-[3]. The released H+ diffuses into the bottom dielectric films, and triggers interaction between PETEOS and SOG. Combining experimental data in Figs. 2 and 3, we conclude that the charges are generated by the PETEOS and SOG interactions and the interaction is triggered by H+ released from the PECVD nitride and diffused into the bottom films during the sintering process.

To further locate the existence of charges, we first remove the PECVD nitride film, measure the field thresh-

Fig. 2. (a) Field threshold voltages of field devices with four different inter-metal dielectric schemes. (b) The circuit yield of a given ASIC design fabricated on the same wafer the field threshold of which is shown in (a).

Fig. 3. Field threshold voltages measured in steps during the backend of line process for PETEOS/SOG/PEOX and PEOX/SOG/PEOX inter-metal dielectric schemes.

old, then remove the PETEOS/SOG/PEOX structure, and measure the field threshold again. Plasma dry etch is used to remove dielectric films, and sintering is performed after the films are removed to fix damage caused by plasma etch. Our experimental results show that the field threshold voltage slightly increases after PECVD nitride is removed, and the field threshold is completely recovered to the original value previously measured at metal-1 after the PETEOS/SOG/PEOX structure is removed. This experi-

Fig. 4. Field threshold voltages for wafers with PETEOS/SOG/PEOX inter-metal dielectric schemes and with the sintering process performed after and before PECVD nitride deposition, respectively.

ment proves that the charges exist mainly in the PETEOS/SOG/PEOX inter-metal dielectric structure.

Since the interaction between PETEOS and SOG is triggered by the H<sup>+</sup> diffused from the top layer of PECVD nitride, we can prevent this interaction by performing the sintering process before, instead of after, the PECVD nitride deposition. By doing this, we improve the quality of underlying PEOX films to prevent the H+ from diffusing down to the SOG and PETEOS films. Futhermore, the probability of H<sup>+</sup> released from PECVD nitride as well as the diffusion rate of H+ are reduced by omitting the sintering temperature after the PECVD nitride deposition. Fig. 4 shows field threshold voltages for wafers subjected to the sintering process before and after the PECVD nitride deposition, respectively. Significant improvements in field threshold voltages are found when the sintering is performed before the PECVD nitride deposition. This is a typical example that process integration is as important as the individual process step in mordern VLSI techologies.

## IV. SUMMARY

We have found severe field inversion caused by the backend process when the PETEOS/SOG/PEOX scheme is used as the inter-metal dielectrics, even if the SOG material is non-carbon-based. Systematic experiments have been conducted to identify causes of the degradation. No field inversion is found when PEOX/SOG/PEOX is used as the inter-metal dielectric. The field oxide device degrades slightly after the PECVD nitride deposition, and its field threshold voltage dramatically decreases after the sintering process. We have also performed experiments to find the location of charges. The charges are found to exist mainly in the PETEOS/SOG/PEOX inter-metal dielectric films. The field inversion problems can be improved by performing the sintering process before the deposition of PECVD nitride, instead of after. Based on our experimental results, we conclude that the field inversion is due to charges generated from the PETEOS and inorganic SOG interactions, which is possibly triggered by H<sup>+</sup> released from PECVD nitride passivation layer during the sintering process.

## REFERENCES

- D. Pramanik, S. Nariani, and G. Spadini, "Field inversion in CMOS double metal circuits due to carbon based SOGs," in *Proc. IEEE VMIC*, 1989, p. 454.

- [2] G. Casner, A. Ito, and R. Nowak, "An investigation of device instabilities arising from the encapsulation material and composition," in *Proc. IEEE VMIC*, 1990, p. 354.

- Proc. IEEE VMIC, 1990, p. 354.

[3] G. Mitsuhashi, H. Muto, Y. Ohno, and T. Matsukawa, "Effect of p-SiN passivation layer on time-dependent dielectric breakdown in SiO<sub>2</sub>," in Proc. Int. Reliability Physics Symp., 1987, p. 60.

- [4] G. Butler, G. Allen, A. Hall, and R. Nowak, "Electrical characterization of doped and undoped PECVD TEOS oxides," in *Proc. IEEE VMIC*, 1990, p. 387.

Shun-Liang Hsu was born in Taipei, Taiwan, in 1958. He received the B.S. and M.S. degrees in the material science and engineering from National Tsing-Hua and Cheng-Kung Universities in 1982 and 1984, respectively.

From 1984 to 1986, he was with ERSO/ITRI for process and module development. Since then, he joined the Taiwan Semiconductor Manufacturing Corporation (TSMC) to involve setting up the fab in 1987. At TSMC, he has been engaged in development of ASIC integration processes and

modules from 1.5 to 0.8  $\mu$ m. He is now the mixed-mode program manager of the R&D Division at TSMC. He is also currently part-time working towards the Ph.D. degree at the Institute of Electronics of National Chiao-Tung University. His current research interest is in the tungsten silicide process integration and analog device characteristics.

Lu-Min Liu received the B.S. and M.S. degrees in materials science and engineering from National Tsin-Hua University in 1978 and 1981, respectively. She received the Ph.D. degree in materials science and engineering from the University of Florida, Gainesville, in 1988.

From 1981 to 1983, she worked for Material Research Laboratory, ITRI, at Hsin-Chu, where she was involved in the development of light-emitting diodes of GaAs and GaP. From 1983 to 1988, she focused on the interaction between Au

and GaAs as her disertation. From 1988 to 1989, she spent a year on ZnSe study at the University of Florida, Gainesville. Since 1990, she has been with TSMC at Hsin-Chu, Taiwan. She was involved in the development of ASIC and mix-mode CMOS. She lead the project of intrinsic gettering. She is now the section manager of module development of the R&D Division at TSMC.

Chung-Hsin Fang was born in Miauli, Taiwan, on November 9, 1964. He received the B.S. degree in the physics from Cheng-Kung University, Taiwan, in 1986 and the M.S. degree from the Institute of Electronics, National Chiao-Tung University, Taiwan, in 1988.

Since 1988, he has been with the Taiwan Semi-conductor Manufacturing Corporation. He has been engaged in development of ASIC integration processes and device characterization from 1.2 to  $0.8~\mu m$  technology.

Shu-Lan Ying was born in Taipei, Taiwan, on August 20, 1965. She received the B.S. degrees in material science and engineering from National Tsing-Hua University, Taiwan, in 1987.

From 1987 to 1990, she was with Hualon Micro-electronics Corporation, working on process development. In August, 1990, she joined the Taiwan Semiconductor Manufacturing Corporation (TSMC) to work on the development of generic ASIC process. Currently, she is working towards the M.S. degree in electrical engineering at

the University of Massachusetts.

Tien-Li Chen was born in Taipei, Taiwan, in 1960. He received the B.S. and M.S. degrees from National Tsin-Hua University, Taiwan, in 1983 and 1986, respectively.

From 1986 to 1990, he was with Taiwan Semiconductor Manufacturing Corporation and was engaged in ASIC process integration development. In 1991, he joined Charter Semiconductor Corporation, Singapore, to work on sale marketing.

Mou-Shiung Lin (M'82) received the B.S. degree in physics from the National Taiwan University in 1975, and the M.S. and Ph.D. degrees in applied physics from Harvard University, Cambridge, MA, in 1978 and 1982, respectively. He was a visiting scientist at the Massachusetts Institute of Technology while working on the Ph.D. dissertation.

From 1982 to 1984, he worked at IBM Corp. at Essex Junction, VT, where he was involved in the development of IBM first two generations of

CMOS technologies, CMOS I and CMOS II. He joined AT&T Bell Laboratories at Murray Hill, NJ, in December 1984. At Bell Labs, he spent the first five years working on the advanced VLSI packaging (AVP) technology for multichip interconnection based on the silicon substrate and flipchip solder joint approaches. He had widely and greatly impacted this program by defining and shaping the AVP technology. He then spent a year working on semiconductor lasers and optical amplifiers for use in optical communication lasers and optical amplifiers for use in optical communication systems. He is now the deputy director of the R&D Division at Taiwan Semiconductor Manufacturing Company, and is in charge of the company-wide R&D activities. He is also an adjunct professor at the National Taiwan University and the National Chiao-Tung University. He authored or coauthored about 40 journal or conference papers in areas of semiconductor devices, VLSI technologies, VLSI packaging, and semiconductor lasers. He is listed in Marquis' "Who is Who in Frontiers of Science and Technology," 2nd ed., 1985.

Dr. Lin is a member of APS and Phi-Tau-Phi.

Chun-Yen Chang (S'69-M'70-SM'81-F'88) was born in Kaohsing, Taiwan, Republic of China, on October 12, 1937. He received the B.S. degree in electrical engineering from National Chen-Kung University, Tainan, Taiwan, in 1960, and the M.S. and Ph.D. degrees from National Chiao-Tung University in 1962 and 1970, respectively.

From 1962 to 1966, he was a research assistant and then an Instructor at Chiao Tung University working on organizing a semiconductor research laboratory. During 1966–1976, he was first an as-

sociate professor and later a professor in solid-state electronics and semiconductor physics and technologies; he was also chairman of the Department of Electrophysics at Chiao Tung University, and has been a professor and director of the Institute of Electrical Engineering, National Chen Kung University, during 1977-1987, where he has established a strong research and development base in electrical and computer engineering. In 1981, he became member of the technical staff at Bell Laboratories, Murray Hill, NJ, working in the VLSI Device Group. He was a visiting professor at the University of Florida, Gainesville, in 1987 and the University of Stuttgart, Stuttgart, W. Germany, in 1989, where he taught MBE technologies and devices. He has consulted ERSO/ITRI, Nippon Seiki Co., UMC, etc., on VLSI, Scanner and flat-panel display devices. He is currently a professor at the Institute of Electronics and Dean of the College of Engineering of the National Chiao-Tung University. His recent interests include silicon VLSI physics and technologies including III-V compound devices and materials using MBE and MOCVD, and amorphous-silicon devices. He has taught the majority of senior semiconductor engineers in Taiwan since 1962,

and published more than 120 technical papers in international journals. He has contributed carrier transport theory and specifice contact resistivity in metal-semiconductor systems (1970, 1971). He invented a method for MOS surface stabilization (1966), the method of low-pressure MOCVD using TEG source (1981), amorphous Si phototransistors (1986), the quantum-well base high-speed transistor (1986), and the bipolar-unipolar transition negative resistance transistor (BUNDR) (1987), etc. He was the recipient of an academic achievement award in engineering from the Ministry of Education and the distinguished research award of the National Science Council, Republic of China, as well as the recipient of the 1989–1990 international traveling award granted by the China Foundation to the distinguished scholars in the Republic of China.

Dr. Chang is a member of Phi Tau Phi, the American Electro-Magnetics Academy, the Chinese Institute of Electrical Engineers, the American Physical Society, and the Electrochemical Society. He has been elected an IEEE fellow for "his contribution to semiconductor devices development and to education."