# Novel Metamorphic HEMTs With Highly Doped InGaAs Source/Drain Regions for High Frequency Applications

Kartika Chandra Sahoo, Chien-I Kuo, Yiming Li, Member, IEEE, and Edward Yi Chang, Senior Member, IEEE

Abstract—In this paper, we report the first result of a strained  $In_{0.52}Ga_{0.48}As$  channel high-electron mobility transistor (HEMT) featuring highly doped  $In_{0.4}Ga_{0.6}As$  source/drain (S/D) regions. A lattice mismatch of 0.9% between  $In_{0.52}Ga_{0.48}As$  and  $In_{0.4}Ga_{0.6}As$  S/D has resulted in a lateral strain in the  $In_{0.52}Ga_{0.48}As$  channel region, where the series resistance is reduced with highly doped S/D regions. An experimentally validated device simulation is advanced for the proposed HEMT, and the results of this paper have shown that there are 60% drive-current and 100% transconductance improvements, compared with the conventional structure. A remarkable 150-GHz increase in the cutoff frequency has been seen for the proposed structure over the conventional one as well for the shown devices.

Index Terms—Device simulation, DC and ac characteristics, HEMT, InGaAs, strained channel.

## I. INTRODUCTION

THE III–V high-electron mobility transistors (HEMTs) have emerged as potential candidates for high-speed and low-power applications beyond CMOS technology [1]. The submillimeter-wave frequency range, 300 GHz–3 THz, will be the major resources of a radio wave in the near-future communication systems similar to the millimeter-wave one (e.g., 30–300 GHz). The HEMTs have been the most promising devices for operating in the submillimeter-wave frequency range because the materials used for the device fabrication provide higher electron mobilities, higher saturation velocities, and higher sheet electron densities.

Manuscript received June 10, 2010; revised July 2, 2010; accepted July 15, 2010. Date of publication September 2, 2010; date of current version September 22, 2010. This work was supported in part by the National Science Council of Taiwan under Contract NSC-97-2221-E-009-154-MY2 and in part by the InnoLux Display Corporation, Miaoli, Taiwan, under a 2009–2011 grant. The review of this paper was arranged by Editor S. Bandyopadhyay.

K. C. Sahoo is with the Department of Electrical Engineering, National Chiao Tung University, Hsinchu 300, Taiwan and also with the Institute of Communications Engineering, National Chiao Tung University, Hsinchu 300, Taiwan.

C.-I Kuo and E. Y. Chang are with the Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu 300, Taiwan.

Y. Li is with the Department of Electrical Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, Institute of Communications Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, and also with the National Nano Device Laboratories, Hsinchu 300, Taiwan (e-mail: ymli@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2010.2062521

The indium content of the channel plays an important role in the device performance. However, In-rich devices have great radio frequency (RF) performances but suffer from a low breakdown voltage, kink effect, and high output conductance caused by impact ionization [2]. Moreover, the parasitic source/drain (S/D) series resistance ( $R_{\rm SD}$ ) should be reduced to derive more performance resulted from enhanced carrier transport. Therefore, the incorporation of high-doping concentration in the S/D regions would be another important direction to be explored.

It has been known that using a uniaxial compressive SiGe S/D is a good solution to boost the deep submicrometer pMOSFETs' performance for its effective enhancement of mobility in the channel due to a stress induced between the Si/SiGe lattice mismatch [3], [4]. The SiGe S/D induced stress enhances many dc parameters such as hole mobility  $(\mu_p)$ , drain current  $(I_d)$ , and transconductance  $(g_m)$ . In addition, the improvement in  $g_m$  also upgrades key RF parameters, e.g., cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{\max})$ [5]. Notably, the effect of strain on carrier transport in many III-V semiconductors, e.g., gallium arsenide (GaAs) and indium gallium arsenide (InGaAs), is well established [6], [7].

In this paper, we demonstrate a novel  $In_{0.52}Ga_{0.48}As$  channel HEMT with  $In_{0.4}Ga_{0.6}As$  highly doped S/D regions. The lattice mismatch between the  $In_{0.4}Ga_{0.6}As$  S/D and  $In_{0.52}Ga_{0.52}As$  channel is exploited to induce a tensile strain in the channel for mobility enhancement. In addition, high S/D doping concentration further reduces  $R_{\rm SD}$  for additional performance enhancement. The dc and ac characteristics of the proposed HEMT and the conventional HEMT structures are investigated by an experimentally validated device simulation. The conventional HEMT and the proposed one are named as HEMT1 and HEMT2, respectively, in the following sections.

# II. EXPERIMENT AND SIMULATION

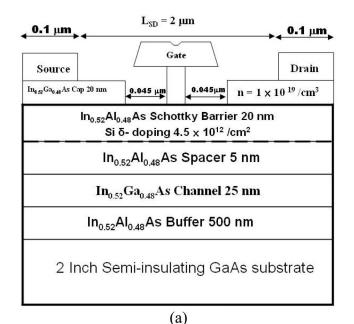

The HEMT1 structure, as shown in Fig. 1(a), is fabricated by the following process steps. The  $In_{0.52}Al_{0.48}As$ - $In_{0.52}Ga_{0.48}As$  MHEMT uses  $In_{0.52}Al_{0.48}As$  as the buffer layer between the GaAs substrate and is grown by the molecular beam epitaxy method on the 3-in-diameter GaAs substrate.

The device fabrication is stated hereinafter; the active area of the device is isolated by wet chemical mesa etching. After that, the  $2 \Omega \cdot \mu m$  S/D spacing ohmic contacts are formed by

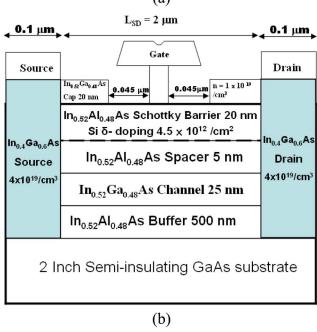

Fig. 1. Schematics of (a) the conventional  $In_{0.52}Ga_{0.48}As$  channel HEMT (HEMT1) and (b) the proposed  $In_{0.52}Ga_{0.48}As$  channel HEMT with heavily doped  $In_{0.4}Ga_{0.6}As$  S/D region (HEMT2).

evaporating Au/Ge/Ni/Au on a heavily doped n-InGaAs cap layer and then alloyed at 250 °C using rapid thermal annealing. The contact resistance measured using the transmission line model is  $0.048\,\Omega\cdot$  mm. To process the T-shaped gate, the 50-kV JEOL electron beam lithography system (JBX 6000 FS) of a 100-pA beam current is used with a conventional trilayer e-beam resist consisting of ZEP-520/PMGI/ ZEP-520. After the gate recess, the Ti (60 nm)/Pt (80 nm)/Au (180 nm) is deposited as a Schottky gate metal and lifted off using a ZDMAC remover (ZEON) to form an 80-nm T-shaped gate. The device is passivated with a 100-nm silicon nitride film by plasma-enhanced chemical vapor deposition.

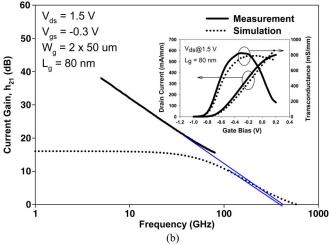

Fig. 2. Comparison between the simulation and measurement for the conventional HEMT. (a) Current–voltage (I-V) characteristics. (b) Current gain  $(h_{21})$  versus frequency (inset shows the drain voltage and the transconductance versus gate current).

The schematic cross sections of HEMT1 and HEMT2 are shown in Fig. 1(a) and (b), respectively. In the HEMT2 structure, we use an  $In_{0.4}Ga_{0.6}As$  S/D heavily doped region. A 2-D hydrodynamic device simulation [8] is performed to compare the measured results for HEMT1 first, where the quantum mechanical correction is considered with a density-gradient approach [9]. Note that the hydrodynamic Canali mobility model considering the constant low-field mobility and high-field saturation is adopted [10], where the material parameters of  $In_xGa_{1-x}As$  and  $In_{0.52}Al_{0.48}As$  follow [10] and [11]. Then, using the same model and the calibrated parameters from the measured characteristics of HEMT1, we advance our simulation to predict the dc and ac electrical characteristics of the HEMT2 structure. In both devices, the gate length is 80 nm, and the S/D distance is 2  $\mu$ m.

### III. RESULTS AND DISCUSSION

To show the validation of the simulation, Fig. 2(a) shows the simulated and measured current–voltage (I-V) characteristics of the HEMT1 structure. The device is well pinched off after an

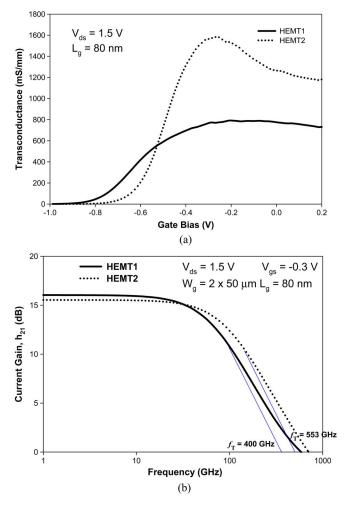

Fig. 3. Comparison between HEMT1 and HEMT2. (a)Transconductance versus gate voltage. (b)Current gain versus frequency.

applied gate bias of -0.8 V. Fig. 2(b) shows the dependence of the current gain on frequency in the 80-nm gate HEMT1 biased at an S/D voltage  $(V_{\rm ds})$  of 1.5 V and a gate–source voltage  $(V_{\rm gs})$  of -0.3 V. The cutoff frequencies  $(f_T)$  of both the simulated and measured current gain are compared as shown in the plot. The plot of the drain current and transconductance with a gate bias is shown in the inset of Fig. 2(b). The simulated and measured results matched quite well. Maximum transconductances of 810 and 790 mS/mm at a drain bias of 1.5 V are obtained for the measured and simulated HEMT1 structure, respectively. We obtained a high  $f_T$  of 440 and 400 GHz for both the measured and simulated HEMT1 structures, respectively, by fitting with a -20-dB/decade slope. Consequently, it confirms the best accuracy in the device simulation of HEMT devices.

Using the same simulation settings on the physical parameters, we thus advance our work to study the electrical characteristics of the HEMT2 structure and compare the dc and ac results with the HEMT1 structure. From our estimations, we find that the HEMT2 structure has a 60.4% larger  $I_d$  (device is biased at  $V_{\rm ds}=1.5~{\rm V}$  and  $V_{\rm gs}=0~{\rm V}$ ) than the HEMT1 structure due to the enhanced electron mobility in the 2DEG channel and the reduced S/D resistance. The maximum dc transconductances  $g_m$  are 790 and 1583 mS/mm (simulated at  $V_{\rm ds}=1.5~{\rm V}$ ) for HEMT1 and HEMT2, respectively, which can be seen from

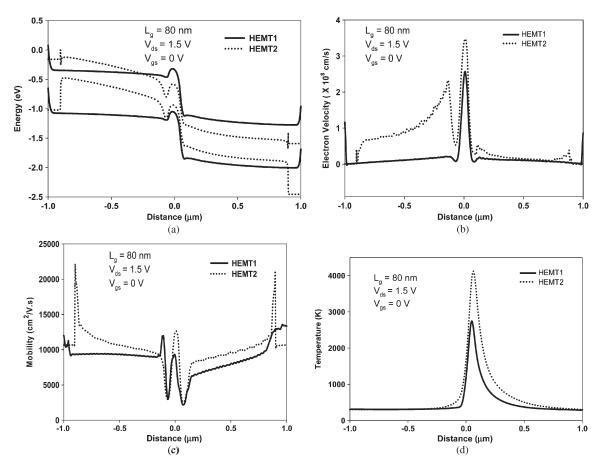

Fig. 3(a). It shows about 100% increase of  $g_m$  for HEMT2 compared to HEMT1. Not only the dc characteristics but also the RF characteristics are improved in HEMT2. Fig. 3(b) plots the simulated high-frequency characteristics of HEMT1 and HEMT2. HEMT2 exhibits superior  $f_T$  of 553 GHz, compared to that of HEMT1 which is 400 GHz. The increase of the drive current, transconductance, and cutoff frequency in the HEMT2 structure is mainly due to the higher mobility in the strained HEMT2 channel and the low S/D resistance, and these are due to the highly doped In<sub>0.4</sub>Ga<sub>0.6</sub>As region used. The strain effect could be explained by the distribution of the band structure, electron velocity, electron mobility, and electron temperature in the channel regions of the HEMT1 and HEMT2 structures at  $V_{\rm ds}=1.5$  V and  $V_{\rm gs}=0$  V, which are plotted in Fig. 4. The band structure comparison in Fig. 4(a) shows that there is narrowing of the barrier under the gate in the case of strained channel HEMT2, which increases the tunneling probability and, hence, the mobility. The average velocity along the HEMT2 channel shown in Fig. 4(b) is higher than that in HEMT1. This is believed to be due to the lower effective mass of electrons entering the channel predominantly in the  $\Gamma$  valley and also due to the self-aligned doping of the source and drain contact regions [10], [11]. Because of the doping concentration in the  $In_xGa_{1-x}As$  S/D regions of HEMT2, the increase of the average velocity under the gate than that of HEMT1 is obviously due to the highly doped S/D region. However, we observe the higher average velocity along the channel of HEMT2 as compared with HEMT1, which is strongly believed to be due to the reduction of effective mass in HEMT2 channel, due to the strain generated, and because of the 0.9% lattice mismatch between In<sub>0.52</sub>Ga<sub>0.48</sub>As channel and In<sub>0.4</sub>Ga<sub>0.6</sub>As S/D region [12].

The electron mobility in the channel for HEMT1 and HEMT2 is compared in Fig. 4(c). It is clearly seen that, in HEMT2, the electron mobility is higher as compared with HEMT1 throughout the device length. This again confirms the strain in the channel due to the lattice mismatch between the channel and S/D material. It is made sure that the energy of the electrons in the channel is increased in HEMT2 as compared to HEMT1, as seen from Fig. 4(d), which confirms the improvement of the mobility in the channel due to the lateral strain. Thus, we conclude that the improvement in the drive current and transconductance in HEMT2 is due to the lower S/D resistance and strain in the channel.

### IV. CONCLUSION

A conventional  $In_{0.52}Ga_{0.48}As$  channel HEMT has been fabricated, and the dc and ac characteristics of the device have been studied both by measurement and simulation. The simulation was performed and calibrated with the measured characteristics. Then, using the same simulation settings, we have explored the possibility of using a highly doped  $In_{0.4}Ga_{0.6}As$  S/D region in the conventional HEMT structure for a high-frequency operation. The results of this paper have suggested that, when compared with a conventional HEMT, the HEMT with a highly doped  $In_{0.4}Ga_{0.6}As$  S/D region has a higher drive current, transconductance, and cutoff frequency. These results

Fig. 4. Compared simulation results of HEMT1 and HEMT2 in channel at  $V_{\rm ds}=1.5~{\rm V}$  and  $V_{\rm gs}=0~{\rm V}$ . (a) Band structure. (b) Average electron velocity. (c) Electron mobility. (d) Electron temperature.

are promising for high-frequency applications of the HEMTs with this structure. The fabrication of the proposed structure is currently under process. The HEMT design proposed in this paper may be of great interest for the communication engineering community.

### REFERENCES

- [1] D. H. Kim and J. A. Del Alamo, "30 nm E-mode InAs PHEMTs for THz and future logic applications," in *IEDM Tech. Dig.*, Dec. 2008, pp. 719–722.

- [2] A. Leuther, R. Weber, M. Dammann, M. Schlechtweg, M. Mikulla, M. Walther, and G. Weimann, "Metamorphic 50 nm InAs-channel HEMT," in *Proc. 17th Int. Conf. IPRM*, May 2005, pp. 129–132.

- [3] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Kaluas, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors," in *IEDM Tech. Dig.*, Dec. 2003, pp. 978–980.

- [4] Y. Li, H.-M. Chen, S.-M. Yu, J.-R. Hwang, and F.-L. Yang, "Strained CMOS devices with shallow-trench-isolation stress buffer layers," *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 1085–1089, Apr. 2008.

- [5] C. Yu and J. S. Yuan, "MOS RF reliability subject to dynamic voltage stress-modeling and analysis," *IEEE Trans. Electron Devices*, vol. 52, no. 8, pp. 1751–1758, Aug. 2005.

- [6] C. Kopf, H. Kosina, and S. Selberherr, "Physical models for strained and relaxed GaInAs alloys: Band structure and low field transport," *Solid State Electron.*, vol. 41, no. 8, pp. 1139–1152, Aug. 1997.

- [7] S. Suthram, Y. Sun, P. Majhi, I. Ok, H. Kim, H. R. Harris, N. Goel, S. Parthasarathy, A. Koehler, T. Acosta, T. Nishida, H. H. Tseng, W. Tsai, J. Lee, R. Jammy, and S. E. Thompson, "Strain additivity in III-V channels for CMOSFETs beyond 22 nm technology node," in VLSI Symp. Tech. Dig., 2008, pp. 182–183.

- [8] Y. Li, S. M. Sze, and T.-S. Chao, "A practical implementation of parallel dynamic load balancing for adaptive computing in VLSI device simulation," *Eng. Comput.*, vol. 18, no. 2, pp. 124–137, Aug. 2002.

- [9] T.-W. Tang, X. Wang, and Y. Li, "Discretization scheme for the density-gradient equations and effect of boundary conditions," *J. Comput. Electron.*, vol. 1, no. 3, pp. 389–393, Oct. 2002.

- [10] M. Han, M.-S. Son, J.-H. Oh, B.-H. Lee, M.-R. Kim, S.-D. Kim, and J.-K. Rhee, "Optimization of sub-0.1-  $\mu$ m offset  $\Gamma$ -shaped gate MHEMTs for millimeter-wave applications," *Microelectron. J.*, vol. 35, no. 12, pp. 973–983, Dec. 2004.

- [11] S. M. Sze, *Physics of Semiconductor Devices.*, 2nd ed. New York: Wiley, 1981.

- [12] T. Krishnamohan, C. Jungemann, D. Kim, E. Ungersboeck, S. Selberherr, P. Wong, Y. Nishi, and K. Saraswat, "Theoretical investigation of performance in uniaxially- and biaxially-strained Si, SiGe and Ge doublegate p-MOSFETs," in *IEDM Tech. Dig.*, San Francisco, CA, Dec. 2006, pp. 937–940.

Kartika Chandra Sahoo received the B.S. degree in physics and the M.S. degree in electronics from Berhampur University, Berhampur, India, in 1998 and 2000, respectively, and the Ph.D. degree from the Department of Materials Science and Engineering, National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 2009.

He is currently a Postdoctoral Fellow with the Parallel and Scientific Computing Laboratory, Department of Electrical Engineering, NCTU. He is also currently with the Institute of Communications

Engineering, NCTU. His research interests include solar cell devices, advanced semiconductor devices, nanotechnology, semiconductor device simulation, including model and programming, and TCAD simulation of CMOS and HEMT devices.

semiconductors.

**Chien-I Kuo** was born in Taiwan. He received the Ph.D. degree in materials science and engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 2008.

He is currently a Postdoctoral Researcher with the Department of Materials Science and Engineering, National Chiao Tung University. His research interests include the fabrication and characterization of compound semiconductor nanodevices for highfrequency and high-speed logic applications and ALD high-k dielectric integration on high-mobility

Yiming Li (M'02) received the B.S. degree in applied mathematics and electronics engineering, the M.S. degree in applied mathematics, and the Ph.D. degree in electronics from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1996, 1998, and 2001, respectively.

In 2001, he was an Associate Researcher with the National Nano Device Laboratories (NDL), Hsinchu, and a Research Assistant Professor with the Microelectronics and Information Systems Research Center (MISRC), NCTU, where he has been engaged in

the field of computational science and engineering, particularly in the modeling, simulation, and optimization of nanoelectronic devices and very large scale integration circuits. In the fall of 2002, he was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst. From 2003 to 2004, he was a Research Consultant with the System on a Chip Technology Center, Industrial Technology Research Institute, Hsinchu. From 2003 to 2005, he was the Head of the Department of Nanodevice and Computational Nanoelectronics with NDL. Since the fall of 2004, he has been a Research Associate Professor with MISRC. From the fall of 2005 to the fall of 2008, he was an Associate Professor with the Department of Communication Engineering, NCTU, where he is currently a Full Professor with the Department of Electrical Engineering, is the Deputy Director of the Modeling and Simulation Center, and is with the Parallel and Scientific Computing Laboratory. He is also the Deputy Director General with NDL. His

current research interests include computational electronics and electromagnetics, experimental and theoretical transport physics of semiconductor nanostructures, device simulation and model parameter extraction for semiconductor and photonic devices, computer-aided-design theory and technology, biomedical and energy harvesting device simulation, parallel and scientific computing, and optimization methodology. He has authored or coauthored over 150 research papers appearing in international book chapters, journals, and conferences.

Dr. Li is a member of Phi Tau Phi and is included in Who's Who in the World. He was the recipient of the 2002 Research Fellowship Award presented by the Pan Wen Yuan Foundation, Taiwan, and the 2006 Outstanding Young Electrical Engineer Award from the Chinese Institute of Electrical Engineering, Taiwan. He has been a Reviewer, Guest Associate Editor, Guest Editor, Associate Editor, and Editor for more than 30 international journals. He has been an Active Reviewer for eight IEEE journals. He has organized and served on several international conferences and was an Editor for the proceedings of international conferences.

Edward Yi Chang (S'85–M'85–SM'04) received the B.S. degree from the Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu, Taiwan, in 1977, and the Ph.D. degree from the Department of Materials Science and Engineering, University of Minnesota, Minneapolis, in 1985.

From 1985 to 1988, he was with the GaAs Component Group, Unisys Corporation, Eagan, MN. From 1988 to 1992, he was with the Microelectronic Group, Comsat Laboratories. He worked on GaAs

MMIC programs on both groups. In 1992, he was with the National Chiao Tung University (NCTU), Hsinchu. In 1994, he helped set up the first GaAs MMIC production line in Taiwan. In 1995, he was the President of Hexawave, Inc., Hsinchu. Since 1999, he has been with the NCTU, where he is currently the Associate Dean of Engineering College. His research interests include new device and process technologies for compound semiconductor RFICs for wireless communication, III–V/Si integration for post-CMOS application, and GaN devices for RF and power applications.

Dr. Chang is a senior member and a Distinguished Lecturer of the IEEE Electron Devices Society.