# The Ballistic Transport and Reliability of the SOI and Strained-SOI nMOSFETs with 65nm Node and Beyond Technology

E. R. Hsieh<sup>1</sup>, Derrick W. Chang<sup>1</sup>, S. S. Chung<sup>1</sup>, Y. H. Lin<sup>2</sup>, C. H. Tsai<sup>2</sup>, C. T. Tsai<sup>2</sup>, G. H. Ma<sup>2</sup>

Department of Electronic Engineering, National Chiao Tung University, Taiwan

United Microelectronics Corporation (UMC), Central R&D Division, Taiwan

Abstract- In this paper, the device performance in terms of its transport charactertifics and reliability of the MOS devices on the SOI and strained-SOI have been examined. For the first time, both the transport and reliability characteristics have been established from experimental SOI and SSOI nMOSFETs. It was characterized by two parameters, the ballistic efficiency and the injection velocity. Experimental verifications on nMOSFETs with both technologies with tensile-stress enhancement have been made. For SSOI devices, it shows the expected drain current enhancements. For the reliability evaluations, SOI shows a smaller lattice such that it exhibits a much worse hot carrier (HC) reliability, while SSOI device shows a poorer interface quality verified from the FN-stress experiment. In general, although SSOI exhibits a worse interface quality while its reliability is much better than that of SOI's. Moreover, SSOI device shows a very high injection velocity as a result of the high strain of the device which makes it successful for drain current enhancement.

Introduction- As device channel length continues to scale beyond 90nm, high-k or strained technology can extend its scalability. For the latter, recent efforts have been paid on the strain engineering [1-2], hybrid substrate technology [3-4], and process-induced strain [5] of CMOS devices. From the scattering theory [6], the two fundamental transport parameters, the ballistic efficiency and the carrier injection velocity from the source side, are strongly related to the strain techniques. On the other hand, none has been reported on the ballistic transport of SOI and SSOI devices.

In this paper, the drain current enhancement of SOI and SSOI devices will be presented. Verifications of the reliabilities will also been demonstrated. A general rule will be provided on which technology is more reliable and with high performance.

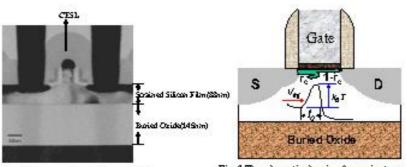

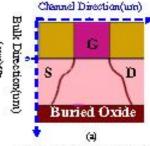

#### I. Device Preparation

SSOI device, as shown in Fig1, is built in a thin (70nm) top silicon film isolated from the substrate by buried oxide (145nm) in UMC 65nm SSDOI technology, and at the same time, biaxial tensile strain in the thin film is formed.[1] Moreover, for NMOS performance enhancement, CESLs are used to give uniaxial tensile strain. The device has 14Å (physical thickness) SION gate oxide. Devices with gate length from 65nm to 0.2um have been used. The control SOI devices were also made for comparison.

## II. Results and Discussion

The drain current for a device in the ballistic regime is governed by

$$I_{dsat} = WC_{eff}V_{inj}B_{sat}(V_{G^{-}}V_{T})$$

(1)

where  $V_{inj}$  and  $B_{sat}$  are the injection velocity and the ballistic efficiency respectively.  $B_{sat}$  is further related to the backscattering or reflection coefficient,  $r_c$ , by  $B_{sat} = (1-r_c)/(1+r_c)$  [2]. As illustrated in Fig. 2, a smaller  $r_c$  (or a larger  $B_{sat}$ ) is desired since a larger  $r_c$  will reduce the drain current. Also, the larger the value of  $V_{inj}$  is the more enhancements the device gains. These two critical parameters  $B_{sat}$  and  $V_{inj}$  are dependent on the device structure, strain engineering etc.

### A. Ballistic transport behavior in SSOI and SOI nMOSFETs

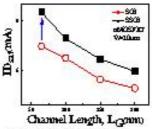

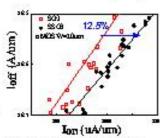

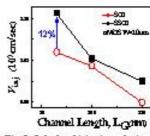

Table 1 shows the formulas to experimentally determine B<sub>sat</sub> and V<sub>inj</sub>. First, comparing SSOI nMOSFETs (SSOIs) and SSOI nMOSFETs (SOIs) in drain current enhancements, we found an average improvement of 22% for SSOIs from long to short channel devices, given in Fig. 3. Furthermore, Fig. 4 shows the I<sub>on</sub>-I<sub>off</sub> results between SSOIs and SOIs. It indicates SSOIs gain more than ~12.5% over SOIs. The ballistic transport behavior between SSOIs and SOIs, and the critical parameters,  $V_{inj}$ ,  $B_{sat}$ , and ••• ••• atio, are then calculated in Fig. 5, Fig. 6, and Fig. 7, respectively. Fig. 5 indicates that injection velocities of SSOI short-channel nMOSFETs are much larger than those of SOIs. But, on other hand, in Fig. 6, B<sub>sat</sub> is not enhanced very much in SSOI short-channel nMOSFETs. From this result, we see that SSOIs are subjected to worse channel interface quality than SOIs such that B<sub>sat</sub> cannot be improved effectively. As a consequence, we conclude that SSOI nMOSFETs gains current enhancements owing to the injection velocity but not ballistic efficiency.

#### B. Reliability Issues in SSOI and SOI nMOSFETs

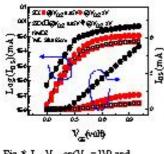

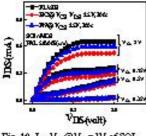

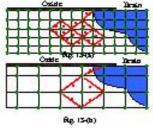

As described above, we realize that bad channel interface quality might be an important issue in SSOI. To prove this, first I<sub>D</sub>V<sub>G</sub>-on and off curves are measured in Fig 8. During off-condition (VDS=0.05V), SSOIs are smaller than SOIs, on the contrary, for on-condition(V<sub>DS</sub>=1V), SSOIs are much enhanced than SOIs ones. Next, simulation results of the channel current density are shown in Fig. 9. Fig. 9 shows that, for off-condition, Fig. 9(b), the carriers transport close to the interface. In contrast, for on-condition, Fig. 9(c), the carriers transport far away from the interface. As an outcome of Fig. 8 and Fig. 9, for off-condition, the interface between channel and insulator is a dominant factor to the transport, thus the curve of SSOIs is degraded instead of enhanced due to bad interface quality. Furthermore, to understand the interface quality, SSOIs and SOIs are stressed by FN-stress and HC-stress. The results are shown in Fig. 10 and Fig. 11. After HC stress, SOI exhibits a much larger degradation, but after FN stress, SOI shows less degradation. On the other hand, for SSOIs after FN stress, the curves are seriously degraded than those after HC stress. Moreover, Fig. 12 shows the Chare Pumping (CP) currents for SOIs and SSOIs. It reveals that CP current level of SOIs after HC stress is higher than that after FN stress. For SSOIs, after FN stress, CP current is larger than that after HC stress. We may confirm that SSOIs exhibit severe damage after FN stress. In other words, SSOIs own much worse channel interface quality. This is why ballistic efficiency cannot be improved. Finally, impact ionization rates of SSOIs and SOIs are shown in Fig. 13. The impact ionization rate of SOIs is much higher than that of SSOÎs. This can be explained that the lattice constant of SOIs, Fig. 14(a), is smaller than that of SSOIs, Fig. 14(b). The smaller the lattice constant is, the higher probability the impact ionization rate is, i.e., a larger hot-carrier effect.

A summarized result of the new results of SSOI devices and previous works is drawn in a roadmap as shown in Fig. 15 for  $V_{\rm inj}.$  This is the first and complete roadmap which has been reported. From  $V_{\rm inj}$  roadmap, in this work, SSOI nMOSFETs exhibits very high  $V_{\rm inj}$  and reaches into the thermal limit region. While, we also show that SSOI nMOSFETs cannot enhance  $b_{\rm sat}$  as a result of poorer interface. Moreover, in general, SSOI device exhibits much better HC reliability comparing to the SOI ones. As long as we can make good quality interface for SSOI, the SSOI device will be very useful in terms of performance and reliability.

Fig. 1 A cross sectional view of SSOI MOSFET in TEM.

r, is the reflection coefficient k<sub>a</sub>T is the barrier determining the injection velocity, V<sub>ij</sub>.

WC BS CO (VG VI, sol) (1)  $I_{0,id}$ where  $I_{O_{FM}} @ V_G - V_{S, occ} - 1V - V_O$ Vs par - Vs participation - DYBL (2) (3) $\{4\}$ Boat No (5)

Fig. 2 The schematic showing the carrier transport. Table 1 The formulas used to determine the two key parameters for device in the ballistic transport regime, injection velocity,  $V_{\omega}$ , and ballistic efficiency,  $B_{\omega}$ .

Fig. 3 Comparison of the ID enhancements from MOSPETs, SOI devices show 22% current gain over control SOI device.

Fig. 4 The companison of Ion Ioff between SSOI and SOI nMOSFETs. It shows that SSOI has a gain of 12.5% overthat of SOI.

Fig. 5 Calculated injection velocity, V. . It gives larger (~12%) values of SSOIn MOSFETs in short channel devices.

Fig. 6 Calculated ballistic efficiency, Beat. The values of SSOI and SOI nMOSPETs are almost the same in shox channel devices.

Fig. 7 Calculated carrier wavelength permean free path,

Fig. 8  $L_{02}V_{02}$  on  $(V_{02}^{-}1V)$  and off  $V_{02}^{-}0.05V$ ) characteristics for SOI and SSOIn MOSPETs.

Fig. 9(a) Simulation of the structure for SOI and SSOI nM OSFETs by ISE TCAD.

Fig. 9(b). Simulation result of the channel current density of  $I_{\rm b2}$   $V_{\rm a2}$  of  $I_{\rm b2}/I_{\rm b2} = 0.05$ V) for SOI and SSOI mMOSPETs by ISE TCAD.

Fig. 9 Simulation result of the channel Fig. 10 L<sub>ss</sub> V<sub>cs</sub>@V<sub>cs</sub>=1V of SOI. current density of I<sub>cs</sub> V<sub>cs</sub> on V<sub>cs</sub>=1V) After HC stress, devices are degraded current density of I or V or on (V or IV) for SOI and SSOI nMOSPETs.

significantly.

Fig. 11 L<sub>cs</sub> V<sub>cs</sub>@V<sub>cs</sub>=1V of SSOI. After Fig. 12 Charge gamping caments of PN stress, devices are degraded significantly. SCI and SSOI nMOSFETs before and It means that SSOI exhibits worse channel after FN stress and HC stress. interface quality than SOI ones.

Fig. 13 L<sub>st</sub> V<sub>cts</sub>@V<sub>cts</sub>=IV of SOI and SSOI rdMOSPETs. The impact ionization rates of SOI rdMOSPETs are much larger than that of SSOI nMOSFETs.

Fig. 14 As a result of different lattice constant of SOI and SSOI nMOSFETs, the impactionization rates of SOI nMOSFETs are much higher.

Fig. 15 A readmap of the injection velocity from reported results and our new work. Note that our new results IEDM, p. 73, 200B. show a much higher V<sub>i</sub>, comparing to (6) M. Lundstram, IEEE EDL, vol. 18, pievious works.

#### References

- [1] K. Rim et al., in Tech. Dig. IEDM, p. 49, 2003

- [2] J. Hayt et al., in Tech. Dig. IEDM, p. 23, 2002

- [3] S. S. Chung et al., in Tech. Dig. TETM(, p. 325, 2006.

- [4] S. S. Chung et al., in Symp. on VLSY Tech., p. 86, 2005.

- C. H. Ge et al., in Tech. Dig. TEDM, p. 73, 2003.

- p. 361, 1997.