# Improving Radiation Hardness of EEPROM/Flash Cell By N<sub>2</sub>O Annealing

Tiao-yuan Huang, Fellow, IEEE, Fuh-Cheng Jong, Tien-Sheng Chao, Horng-Chih Lin, Len-Yi Leu, Konrad Young, Member, IEEE, Chen-Hsi Lin, and Kuang Y. Chiu, Senior Member, IEEE

Abstract— The effects of an  $N_2O$  anneal on the radiation effects of a split-gate electrical erasable programmable read only memory (EEPROM)/flash cell with a recently-proposed hornshaped floating gate were studied. We have found that although the cells appear to survive 1 Mrad(Si) Co<sup>60</sup> irradiation without data retention failure, the write/erase cycling endurance was severely impeded after irradiation. Specifically, the write/erase cycling endurance was degraded to 20 K from the pre-irradiation value of 50 K. However, by adding an N2O annealing step after the interpoly oxidation, the after-irradiation write/erase cycling endurance of the resultant cell can be significantly improved to over 45 K. N<sub>2</sub>O annealing also improves the after-irradiation program and erase efficiencies. The N2O annealing step therefore presents a potential method for enhancing the robustness of the horn-shaped floating-gate EEPROM/flash cells for radiation-hard applications.

Index Terms—EEPROM/flash cells, horn-shaped floating-gate,  $N_2O$  annealing, and radiation hardness.

#### I. Introduction

NON-VOLATILE semiconductor memories are viable candidates for operations under harsh environments such as in military and space applications [1]–[4]. Under such harsh environments, device characteristics such as data retention and write/erase cycling endurance require careful considerations. Traditionally, electrical erasable programmable read only memory (EEPROM) employing metal-nitride-oxide semiconductor (MNOS) technology is employed because of the inherent radiation hardness of the MNOS technology which stores the charge in the nitride layer [1], [2]. Floating-gate EEPROM cells, on the other hand, are known to have less radiation hardness, and therefore remain relatively unexplored [3], [4]. This is because during irradiation, electron/hole pairs are generated. The generated holes could be trapped in the oxide, resulting in oxide degradation and electric field change. Some of the holes could also be injected into the floating-gate,

Manuscript received August 15, 1997; revised March 4, 1998. This work was supported by the R.O.C.'s National Science Council through Contracts NSC86-2722-2317-001 and NSC86-2215-E009-046.

- T. Huang is with the Department of Electronic Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. and National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C.

- F.-C. Jong is with the Department of Electronic Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. and Winbond Electronics Corporation, Hsinchu, Taiwan, R.O.C.

- T.-S. Chao and H.-C. Lin are with National Nano Device Laboratories, Hsinchu, Taiwan, R.O.C.

- L.-Y. Leu, K. Young, C.-H. Lin, and K. Y. Chiu are with Winbond Electronics Corporation, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(98)04778-8.

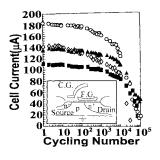

Fig. 1. The effect of write/erase cycling on the cell currents for the cells which were written in the "erase" (i.e., high-conducting) state, and remeasured immediately after irradiation (i.e., without applying an erase pulse after irradiation) for control cells before (square) and after (diamond) irradiation; and N $_2$ O-Cells before (triangle) and after (circle) irradiation. Cell fails when the read current in the "erase" state falls below 40  $\mu$ A (i.e., minimum current required for the sense amplifier to sense as "erase").

neutralizing the stored electrons, causing data loss. Further, the stored electrons could also be emitted over the oxide/floating-gate barrier, causing additional data loss. These would eventually result in data retention failure during irradaition, due to the collapse of the "program" (i.e., high-threshold, low-conducting) state.

However, floating-gate EEPROM/flash cells have in recent years become the mainstream technology for nonvolatile memories. With the aggressive technology scaling and the accompanying reduction in oxide thickness which is known to improve the radiation hardness, it is therefore interesting and technologically important to re-evaluate the suitability of state-of-the-art floating-gate EEPROM/flash cells for the radiation-hard applications. Recently, we have proposed using an  $N_2O$  annealing of interpoly oxide to improve the performance of an EEPROM/flash cell with horn-shaped floating-gate [5], [6]. In this paper, we further report the significant improvement of the EEPROM/flash cell performance in terms of radiation hardness by the addition of an  $N_2O$  annealing [7].

# II. EXPERIMENT

Detailed processing steps for fabricating flash cell with horn-shaped floating-gate, with its cross-sectional schemetics shown in the inset of Fig. 1, are described in [5], [6]. The floating gate length is 0.8  $\mu$ m, the split gate length (i.e., the portion not overlapping the floating-gate) is 0.8  $\mu$ m; while the width of the cell is 2.2  $\mu$ m. Briefly, a 0.8- $\mu$ m, double-level-polysilicon CMOS process was used with a 15-nm first gate oxide. A 170-nm polysilicon layer was deposited to form

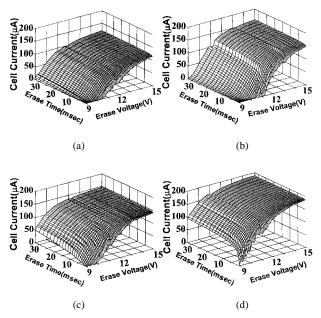

Fig. 2. The erase efficiency for (a) control cell before irradiation, (b) control cell after irradiation, (c)  $N_2O$ -cell before irradiation, and (d)  $N_2O$ -cell after irradiation.

the floating gate. The horn-shaped floating-gate was created by performing a LOCOS-type oxidation on the floating-gate. Wafers were then split to receive the polyoxide oxidation. For the control split, the polyoxide was grown by a conventional dry  $O_2$  oxidation at  $900\,^{\circ}\text{C}$ . While for the  $N_2\text{O}$ -annealed split, polyoxide was first grown in the dry  $O_2$  oxidation at  $900\,^{\circ}\text{C}$ , followed by an  $N_2\text{O}$  anneal for 15 min at  $925\,^{\circ}\text{C}$ . Both splits have comparable final polyoxide thickness. The final oxide thickness at the thickest region is  $220\,\text{nm}$ .

For the write/erase cycling test, a 14-V 800- $\mu$ s pulse was applied to the control gate, with source and drain grounded, so as to facilitate interpoly Fowler-Nordheim tunneling for the erase (i.e., erase to "high-conducting state") operation [6]. For programming (i.e., to low-conducting state) the cell with source-side hot-electron injection [8], the drain was held at 12 V, the source at 0.6 V, the substrate at ground, and a 2-V, 800  $\mu$ s pulse was applied at the control gate. The cell read current was measured by applying 4-V to the control gate, 2 V to the source, while substrate and drain were grounded. For program efficiency test, the cell current was read when the drain voltage was varied with the control gate at 2 V, source at 0.6 V and the substrate at ground. For the erase efficiency test, the cell current was read when the control gate was varied with all other terminals grounded. For radiation study, flash cells were subjected to a radiation from a cobalt-60 source with 1 MRad(Si) dose, and their characteristics were remeasured.

## III. RESULTS AND DISCUSSION

The effects of irradiation on the write/erase cycling endurance are plotted in Fig. 1 for the cell currents on the cells which were written in the "erase" state prior to irradiation, and were remeasured immediately after irradiation (i.e., without applying an erase pulse after irradiation). It is noted that the cell read current actually increases (i.e., an improvement) im-

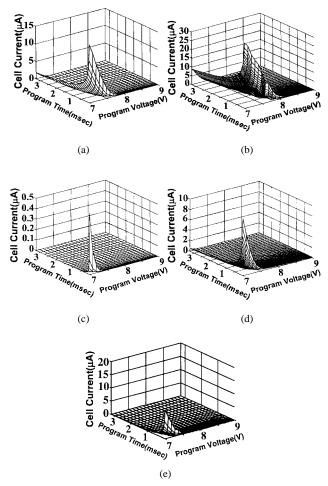

Fig. 3. The program efficiency for (a) control cell before irradiation, (b) control cell after irradiation, (c)  $N_2O$ -cell before irradiation, (d)  $N_2O$ -cell after irradiation, and (e) after subjecting the irradiated  $N_2O$ -cell to a 1000 write/erase cycling.

mediately after irradiation. While for the "program" state, cell current increases (i.e., a degradation) from the pre-irradiation value of 10 pA to about 10 nA immediately after irradiation, and then remains essentially unchanged when subjecting to cycling for both the control and the irradiated cells (data not shown). Since the sense amplifier reference current in our flash cell circuit design is 40  $\mu$ A, our results show that the cells survive the data retention test after subjecting to 1 Mrad(Si) Co<sup>60</sup> irradiation (i.e., no toggling of state by irradiation) under both the "erase" and "program" states. This improvement over previous literature's data is believed to be due, at least in part, to the unique cell structure with a thick polyoxide and thin first gate oxide which is known to be beneficial to radiation hardness [3]. However, despite the improvement of initial cell read current in the "erase" state immediately after irradiation, the irradiated cell's read current degrades much more rapidly than that of its nonirradiated counterpart when subjected to write/erase cycling. The after-irradiation endurance degradation rate during write/erase cycling is especially severe for the control cells without N<sub>2</sub>O annealing. As a result, the irraidated control cell fails cycling endurance at only about 20 K cycles, due to a fast collapse of the "erase" state (i.e., 40  $\mu$ A is the minimum current required for the sense amplifier to sense

as "erase"). In contrast, the irradiated  $N_2O$ -cell fails cycling endurance at about 45 K cycles. The improvements in the  $N_2O$ -cells come from two folds, i.e., a larger initial cell current and a less steep degradation slope during cycling, due to the formation of interfacial oxynitride layer, resulting in a reduced barrier lowering for electron injection and reduced electron trapping by the  $N_2O$  anneal [5].

The effects of irradiation on the program and erase efficiencies are also studied. As shown in Fig. 2, the erase efficiency actually improves after irradiation for both the control and N<sub>2</sub>O-cells. We believe this is due to hole trappings at the oxide/floating-gate interface as a result of irradiation [3], which serve to increase the interpoly electric field during the "erase" operation in our cells. Since our cell employs a strong drain overlap to couple the drain voltage effectively to the floatinggate, the effect of the positive charge in the first gate oxide on the "erase" efficiency is believed to be minimal. On the other hand, the program efficiency after irradiation is degraded, as shown in Fig. 3. This degradation is especially severe for the control cell without N<sub>2</sub>O anneal. This can be explained by hole trappings which occur at the oxide/silicon substrate interface as a result of irradiation. During programming, electrons generated by source-side injection are injected into the gate oxide. Some of these injected electrons will recombine with trapped holes, thus reducing the total amount of electrons which can reach the floating-gate, causing a reduction in the programming efficiency. As shown in Fig. 3(e), our measurements indeed confirmed that during subsequent W/E cycling, part of the holes could be passivated and the program efficiency actually showed a partial recovery.

## IV. CONCLUSION

In this paper, we have studied the effects of  $N_2O$  annealing on the radiation hardness of a recently-proposed EEP-ROM/flash cell with horn-shaped floating gate. Our results show that both the control and  $N_2O$ -annealed cells appear to survive after 1 Mrad(Si)  $Co^{6O}$  irradiation without data retention failure, a significant improvement over previous literature report. However, despite an initial improvement in afterirradiation cell read current in the "erase" state, the cell current degrades more rapidly, especially on the control cells without

$N_2O$  anneal. As a result, the write/erase cycling endurance are significantly degraded after irradiation. By adding an  $N_2O$  annealing step after the interpoly oxidaiton, the afterirradiation cycling endurance can be significantly improved to over 45 K, compared to 20 K for the control cells; thus significantly improving the radiation-hardness of the resultant cell.  $N_2O$  annealing is also shown to improve the afterirradiation program and erase efficiencies. The addition of an  $N_2O$  annealing step thus presents a viable method for further enhancing the robustness of the horn-shaped floating-gate EEPROM/flash cells for radiation-hard applications.

#### ACKNOWLEDGMENT

The authors would like to thank Windbond's Processing Fab and National Nano Device Laboratories for processing the wafers, and Prof. K. S. Chang-Liao, National Tsing Hua University, for the radiation study. They would also like to thank the reviewers for their helpful comments.

### REFERENCES

- P. J. McWhorter, S. L. Miller, and T. A. Dellin, "Radiation response of SNOS nonvolatile transistor," *IEEE Trans. Nucl. Sci.*, vol. NS-33, pp. 1414–1419, 1986.

- [2] P. J. McWhorter, S. L. Miller, T. A. Dellin, and C. A. Axness, "Retention characteristics of SNOS nonvolatile devices in a radiation environment," *IEEE Trans. Nucl. Sci.*, vol. NS-34, pp. 1652–1657, 1987.

- [3] E. S. Snyder, P. J. McWhorter, T. A. Dellin, and J. D. Sweetman, "Radiation response of floating gate EEPROM memory cells," *IEEE Trans. Nucl. Sci.*, vol. 36, pp. 2131–2139, June 1989.

- [4] D. Wellekens, G. Groeseneken, J. V. Houdt, and H. E. Maes, "Single poly cell as the best choice for the radiation-hard floating gate EEPROM technology," *IEEE Trans. Nucl. Sci.*, vol. 40, pp. 1619–1627, June 1993.

- [5] F. C. Jong, T. Y. Huang, T. S. Chao, H. C. Lin, L. Y. Leu, K. Young, C. H. Lin, and K. Y. Chiu, "Improved flash cell performance by N<sub>2</sub>O annealing of interpoly oxide," *IEEE Electron Device Lett.*, vol. 18, pp. 343–345, July 1997.

- [6] S. Kianian, A. Levi, D. Lee, and Y. W. Hu, "A novel 3 volts-only, small sector erase, high density flash E<sup>2</sup>PROM," in 1994 Symp. VLSI Technol. Tech. Dig., 1994, pp. 71–72.

- [7] F. C. Jong, T. Y. Huang, T. S. Chao, H. C. Lin, L. Y. Leu, K. Young, C. H. Lin, and K. Y. Chiu, "A radiation-hard flash cell using horn-shaped floating-gate and N<sub>2</sub>O annealing," in *Int. Conf. Solid State Dev. Mater. Technol. Dig.*, 1997, pp. 102–103.

- [8] A. T. Wu, T. Y. Chan, P. K. Ko, and C. Hu, "A novel high-speed, 5-volt programming EPROM structure with source-side injection," in IEDM Tech. Dig., 1986, pp. 584–587.