# A Novel Two-Step Etching to Suppress the Charging Damages During Metal Etching Employing Helicon Wave Plasma

Huang-Chung Cheng, Wendy Lin, Tzong-Kuei Kang, Yean-Chyi Perng, and Bau-Tong Dai

Abstract—A two-step etching has been performed to eliminate the plasma charging damages during helicon-wave plasma metal etching without selectivity loss. This technique utilized a normal etching recipe to remove the Al film and followed by an optimized etching recipe for the overetching step. By increasing the bias power and decreasing the source power, the optimum etching recipe can cause the plasma more directionally and reduce the Al charging damages. Eventually, the damage mechanism was also reported.

#### I. Introduction

THE dry etching technique is widely used in the manufacturing of ULSI circuits. Unfortunately, recent studies on plasma metal etching indicated that the performance of MOS devices is degraded by charge built-up on gate oxide [1], [2]. Some studies also proposed that the plasma etching of aluminum was one of the main processes which caused gate oxide damages [3], [4]. This problem has become a serious concern in the multilevel metallization schemes because the charges were built up not only through polysilicon gates but also through isolated interconnection metal lines.

The plasma-induced damages can be annealed out at high temperature prior to metallization [5]. But, post metallization can not endure such high temperature. Lin *et al.*, reported that the damages can be minimized by reducing the magnetic field during the overetch step of the metal etching using the magnetically enhanced reactive ion etch (MERIE) system [6]. However, the suppression of charging damages in helicon wave plasma have not been evaluated.

In this letter, the metal etching parameters under helicon wave plasma was therefore optimized to minimize the charging damage. A novel two-step etching were then performed to suppress the oxide damages. The mechanism of the charging damages is also reported to explain the results.

## II. EXPERIMENT

Polysilicon-gate MOS capacitors with 4.5-nm gate oxide were fabricated on p-type substrate. After the polysilicon gate

Manuscript received October 14, 1997; revised February 23, 1998. This work was supported in part by the Republic of China National Science Council (ROC NSC) under Contract NSC-86-2215-E009-023.

H.-C. Cheng, W. Lin, T.-K. Kang, and Y.-C. Perng are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

B.-T. Dai is with the National Nano Device Laboratory, Hsinchu, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(98)04198-6.

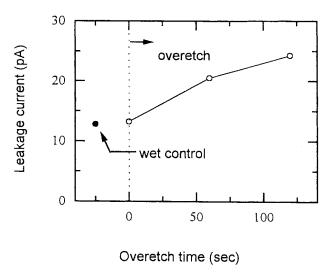

Fig. 1. The leakage current as a function of the overetch time. The leakage current of the wet control sample was also shown for comparison.

was patterned by wet process, aluminum films were deposited by means of thermal evaporation. The aluminum was then etched into antenna structures with the same area but with different peripheral length.

The aluminum etching was done using ANELVA-ILD4100 helicon wave plasma etcher. A recipe with the Cl<sub>2</sub>/BCl<sub>3</sub> flow rates of 70/14 sccm and the source/bias powers of 1900/70 W was performed as the normal etching recipe. The plasma parameters were then optimized to minimize the charging damages. Furthermore, a two-step etching utilized a main Al etching with the normal recipe and an overetch step with the optimum recipe to suppress the charging damages. The leakage currents of the MOS capacitors were also measured to monitor the degrees of the charge damages.

### III. RESULTS AND DISCUSSION

Fig. 1 shows the leakage current as a function of overetch time. The leakage current for the sample without overetch is indistinguishable from that of the wet control sample. It reveals that the damages are not induced during the metal etching. In addition, the leakage currents increase with the overetching time. It suggests that the charges are collected through the edges of the Al patterns but not through the isolated conductor surfaces near the endpoint. Hence, more charges were built-up

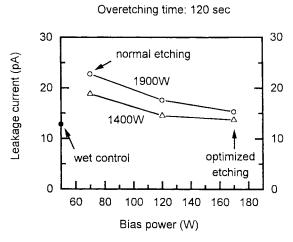

Fig. 2. The leakage current as a function of the normal etching and the optimized etching. The overetch time is set at 120 s.

and result in the increase of leakage current with the overetch time.

Fig. 2 shows the leakage current induced by the plasma charging for the optimized Al etching. A good suppression of antenna effect during Al etching was achieved with the bias power of 170 W and the source power of 1400 W. The leakage current is shown very close to the wet control sample. The leakage current for the normal etching was nearly twice as high as the one with optimized etching. However, a drawback for the optimized condition is that the increased bias power will move the etching from ion-assisted chemical etching toward physical sputtering. It means that the etching selectivity, Al to photoresist and Al to SiO<sub>2</sub>, will be reduced. Therefore, there must be some compromise between the etching selectivity and the charging damages.

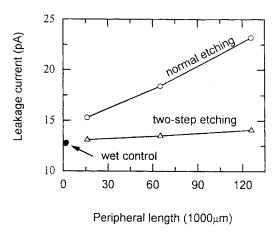

Hence, a novel two-step etching is performed to eliminate the charging damages without selectivity loss. At first, a normal etching recipe with the source/bias power of 1900/70 W is applied for the main etching of Al film. This recipe provide sufficient selectivity of Al to photoresist to define the Al patterns. After the endpoint is detected, a secondstep etching recipe with the source/bias power of 1400/170W, which is also called the optimized recipe in this letter, is applied to provide highly directional and energetic ions which reduce the possibility for the ions to reach the sidewalls of Al patterns. The leakage current as a function of the peripheral length for the normal etching and the two-step etching is shown in Fig. 3. It is clearly seen that the normal etching shows edge intensive antenna effect, i.e., the leakage current increases with peripheral length. The curve of the two-step etching shows lower and simultaneously peripheral-lengthindependent leakage current. Therefore, the elimination of the plasma charging damages can be successfully achieved.

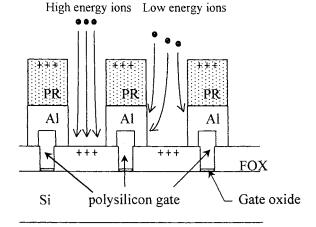

The damage mechanism during helicon-wave plasma metal etching is thus illustrated in Fig. 4. The charges are collected by the sidewalls of Al patterns during the overetching. The ions with higher energy will have better directionality and less influence by the electric field built from the ion charging on the insulators, such as the photoresist and the underlying

Fig. 3. The leakage current for the two-step etching compared to the normal etching.

Fig. 4. Schematic diagram of the plasma charging damage mechanism.

field oxide (FOX). Hence less ions will be collected by the Al patterns and the oxide degradation will be suppressed.

#### IV. CONCLUSION

The plasma charging damages during metal helicon etching have been suppressed by the two-step etching without the selectivity loss. At the first step, a normal etching with source/bias power of 1900/70 W was applied to provide sufficient selectivity for the Al etching. The second step utilizes the optimized recipe, i.e., source/bias power: 1400/170 W, for minimizing the damages during overetching. The leakage currents for the two-step etching are as low as those for the wet-control samples and are independent of the antenna ratios. Furthermore, the edge-intensive charging effect of the helicon wave plasma on the metal etching is also established.

#### ACKNOWLEDGMENT

The authors are grateful for technical support from the National Nano Devices Laboratory and the Semiconductor Research Center at the National Chiao Tung University.

#### REFERENCES

- [1] H. Shin, C.-C. King, T. Horiuchi, and C. Hu, "Thin oxide charging current during plasma etching of aluminum," *IEEE Electron Device Lett.*, vol. 12, pp. 401–406, Aug. 1991.

- [2] H. Hoga, T. Orita, T. Yokoyama, and T. Hayashi, "Charge build-up in magnetron-enhanced reactive ion etching," *Jpn. J. Appl. Phys.*, vol. 30, no. 11B, pp. 3169–3173, 1991.

- no. 11B, pp. 3169–3173, 1991.

[3] F. Shone, K. Wu, J. Shaw, E. Hokelek, S. Mittal, and A. Haranahalli, "Gate oxide charging and its elimination for metal antenna capacitor and transistor in VLSI CMOS double layer metal technology," in *Symp*.

- VLSI Tech. Dig. Papers, 1989, pp. 73-74.

- [4] T. Watanabe and Y. Yoshida, "Dielectric breakdown of gate insulator due to reactive ion etching," *Solid State Technol.*, vol. 27, no. 4, pp. 263–266, 1984.

- [5] J. C. King and C. Hu, "Effect of low and high temperature anneal on plasma-induced damage of gate oxide," *IEEE Electron Device Lett.*, vol. 15, pp. 475–476, Nov. 1994.

- [6] M.-R. Lin, P. Fang, F. Heiler, R. Lee, R. Rakkhit, and L. Shen, "Characterization and optimization of metal etch processes to minimize charging damage to submicron transistor gate oxide," *IEEE Electron Device Lett.*, vol. 15, pp. 25–27, Jan. 1994.