## Evaluation of Plasma Charging Damage in Ultrathin Gate Oxides

Horng-Chih Lin, Member, IEEE, Chi-Chun Chen, Chao-Hsing Chien, Szu-Kang Hsein, Meng-Fan Wang, Tien-Sheng Chao, Member, IEEE, Tiao-Yuan Huang, Fellow, IEEE, and Chun-Yen Chang, Fellow, IEEE

Abstract—Monitoring of plasma charging damage in ultrathin oxides (e.g., <4 nm) is essential to understand its impact on device reliability. However, it is observed that the shift of several device parameters, including threshold voltage, transconductance, and subthreshold swing, are not sensitive to plasma charging and thus not suitable for this purpose. Consequently, some destructive methods, such as the charge-to-breakdown measurement, are necessary to evaluate plasma damage in the ultrathin oxides.

Index Terms— Dielectric breakdown, plasma materialsprocessing applications, semiconductor device reliability.

THE plasma charging damage has attracted much attention in recent years [1]–[9]. As gate oxide thickness is scaled down, the plasma charging damage can potentially degrade oxide integrity significantly. Therefore, how to monitor and minimize the damage becomes important. To this date, most reported studies characterized the charging damage induced in gate oxide which is thicker than 4 nm. In these oxides, Fowler-Nordheim (F-N) tunneling current is the conduction mechanism during high field stressing. Under such situations, electron current injected into the oxide may deposit energy in the oxide and lead to trap creation and interface state generation. These events may shift the device parameters such as threshold voltage  $(V_{th})$ , subthreshold swing  $(S_S)$ , transconductance  $(G_m)$ , etc. Consequently, those device parameters can be used as indicators in monitoring the charging damage. As gate oxide is scaled below 4 nm, however, the situation may change since direct tunneling process replaces the F-N tunneling if oxide voltage  $(V_{\rm ox})$  is smaller than the barrier height of electron at the Si/SiO<sub>2</sub> interface ( $\sim$ 3.2 V). Therefore, the effectiveness of using those device parameters in characterizing the damage should be carefully examined. In this letter, we investigate this issue by performing measurements on devices with 2.6-nm gate oxide. MOS capacitors and n-channel transistors were fabricated on 6-in wafers. Gate oxides were grown after LOCOS isolation, followed by n+

Manuscript received July 25, 1997; revised September 18, 1997. This work was supported by National Science Council of Republic of China under Contract NSC-86-2721-2317-001.

Publisher Item Identifier S 0741-3106(98)01962-4.

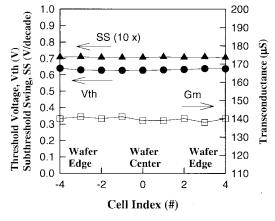

Fig. 1. Threshold voltage, subthreshold swing, and transconductance as a function of cell position. Antenna area ratio of the devices is 15 000.

poly-Si deposition which was employed as the gate electrode. Oxide thickness was determined by fitting the current–voltage characteristics with theory [10] and verified by high resolution TEM [11]. Metal antenna structures attached to the gates were used to monitor the damage. After definition of metal patterns, the photoresist is stripped off in a down-stream type asher. Detailed description of the asher can be found in our previous reports [4]–[6]. Finally, wafers received a 400 °C anneal in forming gas for 20 min. Electrical characterization was then performed with an HP 4145 parameter analyzer.

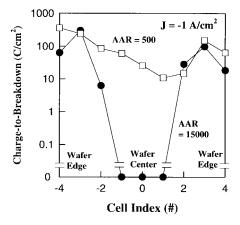

Fig. 1 shows the  $V_{\text{th}}$ ,  $S_S$ , and  $G_m$  of transistors as a function of cell location. The measurements were performed on nine cells along a line that lies across the wafer. The measured devices have a channel length and width of 1.7 and 10  $\mu$ m, respectively; and antenna area ratio (AAR) value of 15000. It is seen that, even with a large AAR value, these parameters vary only slightly across the wafer. In addition, no significant difference is found among transistors with various AAR values. Based on these results, one would tend to conclude that the plasma damage is negligible. However, significant damage is actually identified by the charge-tobreakdown  $(Q_{\rm bd})$  measurements, as illustrated in Fig. 2. Transistors with AAR of 500 and 15000 were measured and compared. Distinctive difference between the two types of devices is found at the wafer center, in which the  $Q_{\rm bd}$  of devices with AAR of 15000 drops to 0, indicating that severe damage has been induced. The damage region is similar to that found in previous reports [3]-[6], and has been identified to be induced during ashing treatment. Comparing the results

H.-C. Lin, and T.-S. Chao are with National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C.

C.-C. Chen, C.-H. Chien, S.-K. Hsein, M.-F. Wang, and C.-Y. Chang are with the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan R.O.C.

T.-Y. Huang is with National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C. and the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Fig. 2. Charge-to-breakdown values as a function of cell position.

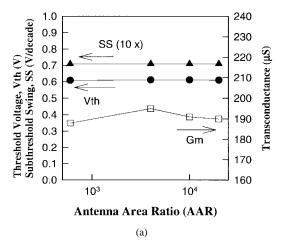

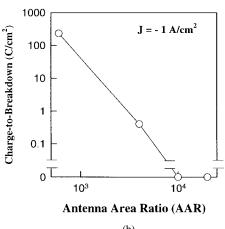

Fig. 3. (a) Threshold voltage, subthreshold swing, and transconductance, and (b) charge-to-breakdown values as a function of antenna area ratio. The test cell is located at the wafer center.

shown in Figs. 1 and 2, it becomes obvious that the parameters used in Fig. 1 are not appropriate to serve as the indicators for monitoring charging damage in ultrathin oxides.

In order to make this point even more clear, we also measured the aforementioned parameters of transistors with various AAR values from a cell located in the wafer center. The results are shown in Fig. 3, in which the channel length and width of the measured devices are 1.2 and 10  $\mu$ m,

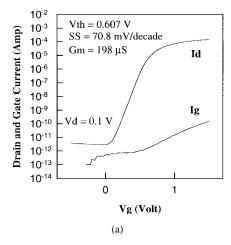

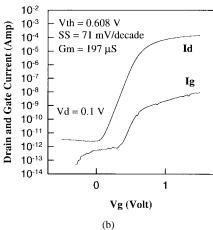

Fig. 4. Drain and gate current as a function of gate voltage measured (a) before and (b) after charge-to-breakdown test. Channel length and width of the measured transistor are 1.2 and 10  $\mu$ m, respectively.

respectively. From Fig. 3(a), it is observed that the  $V_{\rm th}$ ,  $S_S$ , and  $G_m$  are independent of the AAR values. Nevertheless, distinctive antenna effect can be seen from the  $Q_{\rm bd}$  measurement [Fig. 3(b)], consistent with the results shown in Fig. 2. Therefore, it can be concluded that  $Q_{\rm bd}$  is more reliable and sensitive than those device parameters in evaluating charging damage.

Such a finding is reasonable, since the rates of trap creation and interface state generation under high-field stressing decrease significantly as oxides are scaled down [12]. In fact, we also found that the subthreshold characteristics of a transistor with such thin oxide depict little changes even after the charge-to-breakdown test. An example is shown in Fig. 4, in which the  $V_{\rm th}$  only shifts 1 mV after oxide breakdown, while  $S_S$  and  $G_m$  remain almost unchanged. The only parameter that depicts significant changes shown in the figures is the gate leakage  $(I_g)$ , which increases significantly after oxide breakdown. The resultant excessive  $I_g$  could prevent the device from practical applications. However, without actually monitoring the  $I_g$ , the failed device may possibly be regarded as "good". This point has been raised previously [9], and becomes significant as oxide thickness is scaled.

In summary, we have shown that traditional method of monitoring the transistor parameters, including  $V_{\rm th}$ ,  $S_S$ , and

$G_m$ , may not be appropriate for detecting the charging damage in gate oxides as thin as 2.6 nm. In order to access the real damage situation, some destructive measurements, such as charge-to-breakdown, time-dependent dielectric breakdown (TDDB), or breakdown field measurement, maybe indispensable. It is noted that, long-channel devices (e.g., 1.7 and 1.2  $\mu$ m) have been commonly used for characterizing the charging damage to eliminate uncertainties due to channel length variations. However, as devices' dimensions enter the deep submicron regime, the situation may probably become more complicated due to the presence of short-channel and short-width effects, which could make the shift of device's parameters significant.

## ACKNOWLEDGMENT

The authors would like to acknowledge the staffs of NDL for technical assistance.

## REFERENCES

- [1] J. P. McVittie, "Plasma charging damage: An overview," in *Int. Symp. Plasma Process-Induced Damage (P2ID)*, 1996, p. 7.

- [2] S. Fang and J. P. McVittie, "Oxide damage from plasma charging: Breakdown mechanism and oxide quality," *IEEE Trans. Electron Devices*, vol. 41, p. 1034, 1994.

- [3] \_\_\_\_\_\_, "Modeling of oxide breakdown from gate charging during ashing," *IEEE Trans. Electron Devices*, vol. 41, p. 1848, 1994.

- [4] C.-H. Chien, C.-Y. Chang, H.-C. Lin, T.-F. Chang, S.-G. Chiou, L.-P. Chen, and T.-Y. Huang, "Resist-related damage on ultra-thin gate oxide during ashing," *IEEE Electron Device Lett.*, vol. 18, pp. 33–35, 1997.

- [5] H.-C. Lin, C.-H. Chien, M.-F. Wang, T.-Y. Huang, and C.-Y. Chang, "A model for photoresist-induced charging damage in ultrathin gate oxide," in *Int. Symp. Plasma Process-Induced Damage (P2ID)*, 1997, p. 247.

- [6] C.-H. Chien, C.-Y. Chang, H.-C. Lin, S.-G. Chiou, T.-Y. Huang, T.-F. Chang, and S.-K. Hsien, "The role of resist for ultrathin gate oxide degradation during O<sub>2</sub> plasma ashing," *IEEE Electron Device Lett.*, vol. 18, pp. 203–205, 1997.

- [7] K. P. Cheung and C. S. Pei, "Charging damage from plasma enhanced TEOS deposition," *IEEE Electron Device Lett.*, vol. 16, pp. 220–222, 1995.

- [8] K. P. Cheung and C. P. Chang, "Plasma-charging damage: A physical model," J. Appl. Phys., vol. 75, p. 4415, 1994.

- [9] S. R. Nariani and C. T. Gabriel, "A simple wafer-level measurement for predicting oxide reliability," *IEEE Electron Device Lett.*, vol. 16, pp. 242–244, 1995.

- [10] K. F. Schuegraf, C. C. King, and C. Hu, "Ultra-thin silicon dioxide leakage current and scaling limit," in *Symp. VLSI Technol.*, *Dig. Tech. Papers*, 1992, pp. 18–19.

- [11] H. C. Lin, M. F. Wang, C. C. Chen, S. K. Hsein, C. H. Chien, T. S. Chao, T. Y. Huang, and C. Y. Chang, "Characterization of plasma charging damage in ultrathin gate oxides," in 1998 IEEE Int. Reliab. Phys. Symp. (IRPS), to be published.

- [12] L. K. Han, M. Bhat, D. Wristers, J. Fulford, and D. L. Kwong, "Polarity dependence of dielectric breakdown in scaled SiO<sub>2</sub>," in *IEDM Tech. Dig.*, 1994, p. 617.