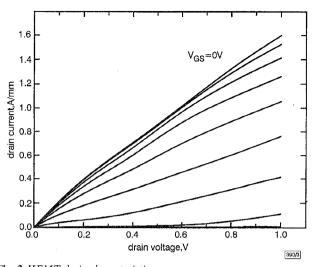

observed which results from the combination of high sheet charge density in the channel and low access resistance. The low-field source-drain resistance at  $V_{GS}=0{\rm V}$  is 0.45  $\Omega$  mm. The devices display a good pinchoff at  $V_{GS}=-1.6{\rm V}$  and a negligible kink effect.

Fig. 3 HEMT drain characteristics  $L_G=0.5\,\mu\text{m},\,L_{SD}=1.2\,\mu\text{m},\,W_G=28\,\mu\text{m},\,V_{GS}=0.2\,\text{V/step}$

A maximum DC transconductance above 1S/mm is measured at  $V_{GS} = 0.5$ V. The S-parameters of the HEMTs were measured onwaser from 1 to 40 GHz. Based on the usual 6dB/octave extrapolation, the device exhibits an  $f_T$  and  $f_{max}$  of 45 and 70 GHz, respectively, at  $V_{GS}=0.4$  and  $V_{GS}=-1.1$ V. At this bias condition, the microwave transconductance and output conductance were 600 and 100mS/mm, respectively, and the gate leakage current was 40uA. An equivalent circuit of the HEMT was developed by fitting the measured S-parameters to a commonly-used circuit topology. After removal of the gate bonding pad capacitance from the equivalent circuit, an  $f_T$  of 60GHz was obtained, which corresponds to an  $f_T L_a$  product of 30GHz µm. At higher drain voltages, the effects of impact ionisation become apparent with the gate leakage current increasing and the low-frequency unilateral gain decreasing significantly. HEMTs with a 0.4µm gate length were also fabricated in material with a similar layer design and sheet charge density, except that a composite GaSb/InAs cap layer was employed. The overall behaviour of these HEMTs was found to be similar to those HEMTs previously described. However, they exhibited a slightly improved performance due to the shorter gate length, yielding an extrinsic  $f_T$  and  $f_{max}$  of 75 and 100 GHz, respectively, at  $V_{DS} = 0.5$  V.

These initial results demonstrate that Si-doping in a thin InAs layer located adjacent to the AlSb barrier can be used to produce HEMTs with high sheet charge density. Optimisation of the present growth process will lead to higher sheet densities and channel mobilities. To realise the performance potential of AlSb/InAs HEMTs, the combination of this doping approach with improved buffer and barrier layer designs is needed to minimise leakage current, improve modulation efficiency, and more effectively manage the holes generated by impact ionisation.

Acknowledgment: This work was supported by the Office of Naval Research. The authors thank H.B. Dietrich and C.R. Marrian for helpful discussions.

© IEE 1998

10 December 1997

Electronics Letters Online No: 19980219

J.B. Boos, B.R. Bennett, W. Kruppa, D. Park, M.J. Yang and B.V. Shanabrook (Naval Research Laboratory, Washington, DC 20375-5320, USA)

E-mail: boos@estd.nrl.navy.mil

## References

- 1 BOLOGNESI, C.R., CAINE, E.J., and KROEMER, H.: 'Improved charge control and frequency performance in AlSb/InAs-based heterostructure field-effect transistors', IEEE Electron. Device Lett., 1994, 15, (1), pp. 16–18

- 2 BOOS, J.B., KRUPPA, W., PARK, D., BENNETT, B.R., and BASS, R.: 'DC, small-signal, and noise characteristics of 0.1 µm AlSb/InAs HEMTs'. Proc. Ninth Int. Conf. IPRM, 1997, pp. 193–196

- 3 WERKING, J.D., BOLOGNESI, C.R., CHANG, L.-D., NGUYEN, C., HU, E.L., and KROEMER, H.: 'High-transconductance InAs/AlSb heterojunction field-effect transistors with δ-doped AlSb upper barriers', *IEEE Electron. Device Lett.*, 1992, **13**, (3), pp. 164–166

- 4 MALIK, T.A., CHUNG, S.J., STRADLING, R.A., YUEN, W.T., HARRIS, J.J., and NORMAN, A.G.: 'Remote doping of InAs/GaSb quantum wells by means of a second InAs well doped with silicon'. Inst. Phys. Conf. Ser., 1995, pp. 229–233 (no. 144)

- 5 SASA, S., YAMAMOTO, Y., IZUMIYA, S., YANO, M., IWAI, Y., and INOUE, M.: 'Increased electron concentration in InAs/AlGaSb heterostructures using a Si planar doped ultrathin InAs quantum well', Jpn. J. Appl. Phys., 1997, 36, pp. 1869–1871

- 6 BENNETT, B.R., YANG, M.J., SHANABROOK, B.V., BOOS, J.B., and PARK, D.: 'Modulation InAs(Si) doping of InAs/AlSb quantum wells', submitted to *Appl. Phys. Lett*.

- 7 BOOS, J.B., KRUPPA, W., PARK, D., MOLNAR, B., BASS, R., GOLDENBERG, M., BENNETT, B.R., and MITTEREDER, J.: 'Pd/Pt/Au and AuGe/Ni/Pt/Au ohmic contacts for AlSb/InAs HEMTs'. Proc. Eighth Int. Conf. IPRM, 1996, pp. 354–357

## Effects of N<sub>2</sub>O-annealed sacrificial oxide on the short-channel effects of *n*MOSFETs

F.C. Jong, T.Y. Huang, T.S. Chao, H.C. Lin, M.F. Wang and C.Y. Chang

The authors report the effects of  $N_2O$ -annealed sacrificial oxide on nMOSFETs. It is demonstrated that by adding an  $N_2O$ -annealing step to the sacrificial oxide which was stripped off before growing the final gate oxide, the reverse short-channel effects (RSCE) can still be effectively suppressed.

Introduction: Recently, the reverse short-channel effect (RSCE) has received much attention [1 - 6]. Unlike the conventional normal short-channel effect (NSCE), in which the threshold voltage  $(V_{th})$  decreases with decreasing channel length, RSCE involves an increase in  $V_{th}$  with decreasing channel length. It has now been generally agreed that RSCE is caused by the non-uniform lateral distribution of channel surface concentration near the source/drain region. This lateral non-uniformity in surface dopant concentration can be attributed to several processing steps, including oxidation-enhanced diffusion (OED), vacancy injection during source/ drain salicidation, or fluorine enhanced boron diffusion, for example. It has also been reported that by nitriding the gate dielectric (i.e. final gate oxide), or by performing the after-gate re-oxidation in an N2O ambient, RSCE can be suppressed [7, 8]. In this Letter we report, for the first time, that RSCE can also be effectively suppressed by performing the nitridation process on the sacrificial oxide, which is stripped off before the final gate oxide is grown.

Fabrication process and results: A typical 0.8 µm, double-level-polysilicon CMOS process was used. After LOCOS processing, the pad oxide was stripped off, and a 25nm sacrificial oxide was grown. The sacrificial oxide is usually employed in a typical MOS process flow for reducing the LOCOS-related gate oxide defect, and for improving the integrity of the final gate oxide by allowing the performance of the  $V_{th}$ -adjust implant and anti-punchthrough implant through the sacrificial oxide, which is then stripped off prior to growing the final gate oxide. In this study, the 25nm sacrificial oxide in the control split was grown by a conventional dry O<sub>2</sub> oxidation. For the N<sub>2</sub>O-annealed split, the 25nm sacrificial oxide was first grown by a dry O2 oxidation, followed by an N2Oannealing for 15mm at 925°C, to produce a final thickness of 25nm. Wafers were then combined to receive an anti-punchthrough implant (boron, 160 keV,  $2.5 \times 10^{11}$  cm<sup>-2</sup>) and a  $V_{th}$ -adjust implant (BF<sub>2</sub>, 90 keV,  $2.2 \times 10^{12}$  cm<sup>-2</sup>) by implanting through the sacrificial oxide. Afterwards, the sacrificial oxide was stripped off in buffered HF, and a 20 nm final gate oxide was grown in dry  $\rm O_2$  ambient at 950°C. A polysilicon layer was subsequently deposited, POCl<sub>3</sub>-doped, and patterned to form the gate of the transistor.

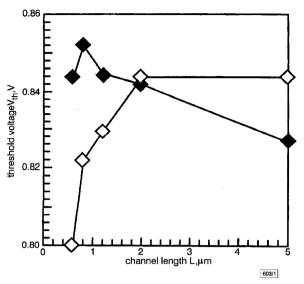

Fig. 1 Threshold voltage against channel length for control devices with conventional  $SiO_2$  sacrificial oxide and devices with  $N_2O$ -annealed sacrificial oxide

SiO₂ sacrificial oxide

N₂O-annealed sacrificial oxide

Threshold voltage  $(V_{th})$  against channel length for all nMOS-FETs is shown in Fig. 1. It is interesting to note that while the control devices with conventional SiO2 sacrificial oxide depict RSCE (i.e.  $V_{th}$  increases first before finally decreasing with decreasing channel length), the devices with N2O-annealed sacrificial oxide depict NSCE (i.e.  $V_{th}$  decreases monotonically with decreasing channel length). This result indicates that, similar to growing the final gate oxide in an N<sub>2</sub>O ambient, or performing the after-gate re-oxidation in an N2O ambient [7, 8], performing the sacrificial oxide in an N<sub>2</sub>O ambient prior to growing the final gate oxide is also effective in suppressing the oxidation-enhanced diffusion, resulting in a more uniform lateral surface concentration in the channel, and thereby suppressing the RSCE. To account for the observed phenomenon, it is speculated that even though the N<sub>2</sub>O-annealed sacrificial oxide was stripped off prior to growing the final gate oxide; the nitrogen which is incorporated at the Si/ SiO<sub>2</sub> interface remains, serving to suppress enhanced boron diffusion during later processing. This is plausible because the buffered

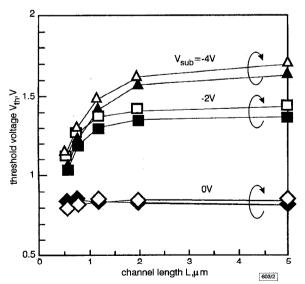

**Fig. 2** Substrate bias effects on threshold voltage against channel length for control devices with conventional  $SiO_2$  sacrificial oxide and devices with  $N_2O$ -annealed sacrificial oxide

$\blacktriangle$ ,  $\blacksquare$ ,  $\bullet$  SiO<sub>2</sub> sacrificial oxide  $\triangle$ ,  $\square$ ,  $\diamondsuit$  N<sub>2</sub>O-annealed sacrificial oxide

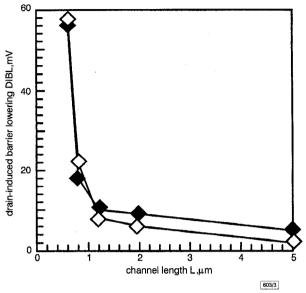

HF solution used to strip off the sacrificial oxide is known to be ineffective in etching silicon nitride. The effects of substrate bias are shown in Fig. 2. Our results confirm previous reports that RSCE subsides with the applied substrate bias [9]. Since substrate bias modulates the depletion width of the source/drain junction, RSCE diminishes with increasing substrate bias. The corresponding drain-induced barrier lowering (DIBL) effects are shown in Fig. 3. Devices with  $N_2$ O-treated sacrificial oxide indeed depict slightly larger DIBL, consistent with the observed NSCE in these devices (i.e. more severe  $V_{th}$ -lowering, compared to devices which depict RSCE).

Fig. 3 Drain induced barrier lowering against channel length for control devices with conventional  $SiO_2$  sacrificial oxide and devices with  $N_2O$ -annealed sacrificial oxide

SiO₂ sacrificial oxide

N₂O-annealed sacrificial oxide

Conclusion: We have reported, for the first time, that RSCE can be effectively suppressed by employing an N<sub>2</sub>O-annealed sacrificial oxide. Even though the sacrificial oxide is stripped off before growing the final gate oxide, our data indicate that the incorporated nitrogen at the Si/SiO<sub>2</sub> interface remains and acts to suppress enhanced boron diffusion during subsequent thermal processing. Our results suggest that the growth condition of sacrificial oxide can also affect the short-channel effects of the resultant submicron transistors, and should therefore be carefully considered in designing the transistor process flow.

Acknowledgments: The authors would like to thank National Nano Device Laboratories for wafer processing. This work was partly supported by the Republic of China's National Science Council through contract #NSC87-2215-E009-057.

© IEE 1998 24 November 1997 Electronics Letters Online no: 19980207

F.C. Jong, T.Y. Huang, M.F. Wang and C.Y. Chang (Department of Electronic Engineering, National Chiao Tung University, Hsinchu, Taiwan, Republic of China)

T.S. Chao and H.C. Lin (National Nano Device Laboratories, Hsinchu, Taiwan, Republic of China)

T.Y. Huang: also with National Nano Device Laboratories, Hsinchu, Taiwan, Republic of China

## References

- 1 MAZURE, C., and ORLOWSKI, M.: 'Guidelines for reverse short-channel behavior', IEEE Electron Device Lett., 1989, EDL-10, pp. 556-558

- 2 ORLOWSKI, M., MAZURE, C., and LAU, F.: 'Submicron short channel effects due to gate reoxidation induced lateral institutional diffusion'. IEDM Tech. Dig., 1987, pp. 632-635

- B HANAFI, H., NOBLE, W., BASS, R., VARAHRAMYAN, K., LI, Y., and DALLY, A.: 'A model for anomalous short-channel behavior in submicron MOSEET's', *IEEE Electron Device Lett.*, 1993, **12**, pp. 575–577

- JACOBS, H., SCHWERRIN, A., SCHARFETTER, D., and LAU, D.: 'MOSFET reverse short channel effect due to silicon intersitial capture in gate oxide'. IEDM Tech. Dig., 1993, pp. 307–310

LU, C., and SUNG, J.: 'Reverse short-channel effects on threshold

- 5 LU, C., and SUNG, J.: 'Reverse short-channel effects on threshold voltage in submicrometer salicide devices', *IEEE Electron Device Lett.*, 1989, EDL-10, pp. 446-448

- 6 CHANG, C., LIN, C., CHOU, J., HSU, C., PAN, H., and KO, J.: 'Anomalous reverse short-channel effect in p+ polysilicon gated p-channel MOSFET', *IEEE Electron Device Lett.*, 1994, **15**, pp. 437–439

- 7 TSUI, P., TSENG, H., ORLOWSKI, M., SUN, S., TOBIN, P., REID, K., and TAYLOR, W.: 'Suppression of MOSFET reverse short channel effect by  $N_2O$  gate poly reoxidation process', IEDM Tech. Dig., 1994, pp. 501-504

- 8 CHAO, T., CHIEN, , LIN, H., CHEN, L., HUANG, T., and CHANG, C.: 'The combination effects of nitrogen implantation at S/D extension and N<sub>2</sub>O gate oxide on 0.18μm nMOSFET'. Int. Symp. on VLSI-TSA, 1997, pp. 316–320

- 9 ARORA, N., and SHARMA, M.: 'Modeling the anomalous threshold voltage behavior of submicron MOSFET's', *IEEE Electron. Device Lett.*, 1992, 13, pp. 92–94

## GalnP/AllnP tunnel junction for GalnP/GaAs tandem solar cells

W. Li, J. Lammasniemi, A.B. Kazantsev, R. Jaakkola, T. Mäkelä and M. Pessa

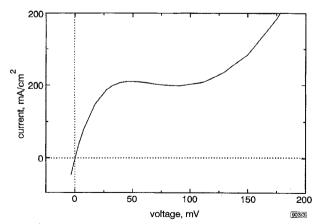

A GaInP/AlInP tunnel diode has been grown by a gas-source molecular beam epitaxy method. A high conductance of 15mA/cm² at 2.7mV has been achieved. Using closely optimised growth conditions, very high carrier concentrations, both in GaInP and AlInP, have been obtained.

A GaInP/GaAs tandem solar cell consisting of a thin GaInP top cell and a GaAs bottom cell has a significantly higher conversion efficiency than conventional single-junction solar cells [1]. One of the critical issues in the growth of such a two-terminal monolithic tandem cell is a tunnel junction for the inter-cell connection. The tunnelling interconnect must not only pass the device current with minimal electrical loss but also transmit the appropriate portion of the optical spectrum to the underlying subcell. The GaInP/AIInP tunnel junction may provide the desired interconnect. It tends to increase the quantum efficiency of the bottom cell by eliminating the absorption loss typical of the GaAs tunnel layer [1]. Conversely, the  $p^+$ - $n^+$  GaInP junction is difficult to prepare for example by metal organic chemical vapour deposition (MOCVD), which is the most commonly used method for the growth of solar cells, because of the rapid diffusion of p-type dopants (Zn).

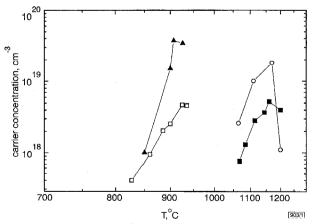

Fig. 1 Net carrier concentrations in AlInP and GaInP layers grown by GSMBE against Be and Si oven temperatures

☐ AlInP: Be ▲ GaInP: Be ■ AlInP: Si ○ GaInPi:Si

Recently, we have shown that it is possible to prepare GaInP/GaAs tandem cells by means of gas source molecular beam

epitaxy (GSMBE) [2]. Compared to MOCVD, GSMBE yields a higher p-type doping efficiency and less severe diffusion of the p-type dopant (Be). In this Letter, we present a  $p^+$ - $n^+$  GaInP/AIInP tunnel diode grown by GSMBE. In GSMBE, elemental solid sources are used to produce the group-III beam fluxes, while As<sub>2</sub> and P<sub>2</sub> are produced from cracked AsH<sub>3</sub> and PH<sub>3</sub>. The growth temperature in our experiments was ~500°C.

Fig. 1 shows the net carrier concentrations in Si and Be-doped GaInP and AlInP, as deduced from Hall-effect measurements. The doping characteristics of AlInP differ significantly from those of GaInP. Doping with Si resulted in the maximum electron concentration of  $1.8 \times 10^{19} \rm cm^{-3}$  in GaInP and  $5.3 \times 10^{18} \rm cm^{-3}$  in AlInP. A further increase in Si concentration caused a decrease in carrier concentration, due to the amphoteric nature of Si. Doping with Be yielded the maximum hole concentration of  $3.7 \times 10^{19} \rm cm^{-3}$  for GaInP and  $4.7 \times 10^{18} \rm cm^{-3}$  for AlInP. The hole concentrations are limited by a non-homogeneous redistribution of Be in the doped layer [3]. The above-mentioned doping levels are among the highest obtained to date by any growth method.

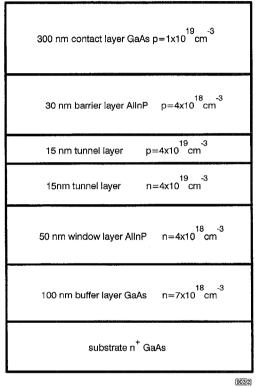

Fig. 2 Schematic structure of GaInP/AlInP tunnel diode

Fig. 3 I-V characteristics of GaInP/AlInP tunnel diode

The schematic structure of a GaInP/AlInP tunnel diode suitable for use in a GaInP/GaAs tandem cell is shown in Fig. 2. We have made the GaInP and AlInP layers lattice-matched to a GaAs:Si (001) substrate within a range of accuracy from  $\Delta a/a = -600$  to 200 ppm. The diodes were fabricated by alloying Ti/Pt/Au contacts to the  $p^+$  GaAs layer and etching photolithographically defined