the pinch-off mode of operation, and found to be 2.11 and 4.06 GHz, respectively. Under optical illumination  $f_T$  was increased by 20%, while  $f_{max}$  was improved by 10% compared with microwave performance under non-illumination.

In summary, a *p*-channel  $In_{0.49}Ga_{0.51}P/GaAs/In_{0.13}Ga_{0.87}As$  pseudomorphic MODFET with 1 µm gate length has been fabricated. DC and microwave performance of the devices were characterised with and without optical illumunation. We observed that the photocurrent was -0.36mA at  $V_{gs} = -0.2$ V and  $V_{ds} = -3.5$ V with incident optical power of 2.15mW. A significantly high responsivity was noted at low incident optical powers. Under the optical illumination, current gain cut-off frequency and maximum available gain cut-off frequency were improved. These results of the optical responses of the *p*-channel InGaP/GaAs/InGaAs pseudomorphic MODFET on a GaAs substrate are reported for the first time.

© IEE 1998

1 September 1997

Electronics Letters Online No. 19980009

H.J. Kim, S.H. Kim, J.I. Lee and K.N. Kang (Division of Electronics and Information Technology, Korea Institute of Science and Technology, Cheongryang PO Box 131, Seoul, 130-650, Korea)

D.M. Kim (Department of Electronics Engineering, Kookmin University, 861-1 Jeongnung-Dong, Seongbuk-Ku, Seoul, 136-702, Korea)

K. Cho (Department of Physics, Sogang University, CPO Box 1142, Seoul, 100-611, Korea)

## References

- 1 ARAFA, M., FAY, P., ISMAIL, K., CHU, J.O., MEYERSON, B.S., and ADESIDA, I.: 'High speed p-type SiGe modulation-doped field-effect transistors', IEEE Electron Device Lett., 1996, 17, (3), pp. 124–126

- 2 HERCZFELD, P.R.: 'Chip level integration of microwave and photonic devices'. European Microw. Conf. Proc., 1994, pp. 3–8

- 3 SINGHAL, A., MISHRA, A., and CHAKRABARTI, P.: 'Optical effects in modulation-doped-field-effect-transistor', Solid-State Electron., 1990, 33, (9), pp. 1214–1216

## Suppression of boron penetration in $p^+$ polysilicon gate using Si-B diffusion source

T.S. Chao, C.P. Kuo, T.F. Lei, T.P. Chen, T.Y. Huang and C.Y. Chang

The authors report a novel Si-B diffusion source for doping  $p^+$ -poly-Si gates in pMOSFETs. It is found that B penetration can be effectively suppressed by using this novel process. All of the electrical properties of the MOS capacitors are significantly improved over those in the conventional BF<sub>2</sub><sup>+</sup> or B<sup>+</sup>-implanted samples. This new process is very promising for future surface-channel pMOSFETs.

Introduction: p\*-polycrystalline silicon (p\*-poly-Si) has been proposed as the gate material for surface-channel p-type metal-oxidesemiconductor transistor (pMOSFETs) in deep submicron complementary metal-oxide semiconductor devices [1]. This is because surface-channel pMOSFETs using  $p^*$ -poly-Si gates have better short-channel and sub-threshold I-V characteristics. They also exhibit improved controllability of the threshold voltage over buried-channel pMOSFETs with an  $n^+$ -poly-Si gate. However, the fast boron diffusion in the poly-Si and gate oxide, results in the susceptibility of boron penetration through the gate into the underlying silicon substrate. The presence of F, due to BF<sub>2</sub><sup>+</sup> implantation, further enhances the diffusion of B [2]. Boron penetration is known to cause device instability such as positive threshold voltage shift, increased subthreshold swing, increased electron trapping rate, low-field hole mobility degradation, and drive current degradation due to poly-Si depletion in pMOSFETs. Many methods have been proposed to suppress boron penetration. The first approach is to retard the boron diffusion in the poly-Si. This can be achieved by stacked or modified poly-Si gate structures [3]. The second approach is to establish a diffusion barrier at the interface of the poly-Si/oxide and/or oxide/Si-substrate. This can be

achieved by nitridation of the gate and/or gate oxide by using  $N_2O$  or NO oxidation/annealing, or an inductive-coupling-nitrogen-plasma to incorporate a nitrogen-rich layer at the  $SiO_2/Si$  interface as a barrier to retard the boron diffusion [4] In this Letter, a novel Si-B layer is proposed, for the first time, as the diffusion source for doping the  $p^+$ -poly-Si. The comprehensive effects of annealing temperature and time on the  $p^+$ -poly-Si MOS capacitors using an Si-B layer are compared with the conventional  $BF_2^+$ - and  $B^+$  ion-implanted counterparts by using secondary ion mass spectroscopy (SIMS) analyses, high/low frequency C-V measurements, J-E characteristics, and charge-to-breakdown ( $Q_{bd}$ ) values. It is found that this new process, which is inherently free of F, has a better capability for suppressing boron penetration than conventional methods employing either  $BF_2^+$  or  $B^+$  implantation.

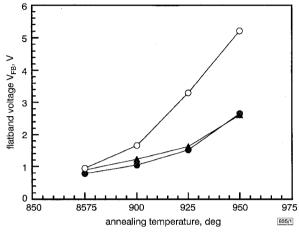

Fig. 1 Flat-band voltage of BF,+-implanted, B+-implanted and Si-B samples annealed at 875–950 °C for 15 min

Si-B

B<sup>+</sup>

BF<sub>2</sub><sup>+</sup>

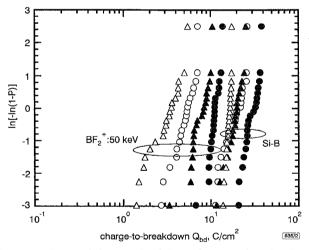

Fig. 2 Distribution of charge-to-breakdown of  $BF_2^+$ -implanted and Si-B samples

● 875°C ○ 900°C ▲ 925°C △ 950°C

Experiment:  $p^*$ -poly-Si gate MOS capacitors were fabricated on n-type (100) Si-wafer with from 2 to  $4\Omega$  cm resistivity. The active area was defined with 550nm of field oxide. A thin 9.5nm gate oxide was grown at 900°C. A 300nm poly-Si was then deposited. Samples with the conventional implanted  $p^*$ -poly-Si gate were fabricated by using BF<sub>2</sub>\*, 50keV, or B\*, 20keV, both to a dose of 5 ×  $10^{15}$ cm<sup>-2</sup>; while for the Si-B samples, they were put instead into a ultra-high-vacuum vapour chemical deposition (UHV/CVD) system to deposit a 35nm Si-B layer upon the undoped poly-Si gate layer by using a 1:1 mixture of pure SiH<sub>4</sub> and B<sub>2</sub>H<sub>6</sub> (1% in H<sub>2</sub>) at 550°C. The base pressure was 2 ×  $10^{-8}$  torr. Afterwards, all samples were annealed in wet O<sub>2</sub>, ambient at temperatures between 875 and 950°C for 15–35min. The Si-B layer was oxidised during

this annealing process to form  $SiO_2$ , while the boron was diffused simultaneously into the underlying poly-Si gate, forming the  $p^+$ -poly-Si gate. The formed oxides on top of the poly-Si gate were then dipped away. Al metal was then deposited and patterned for contacts.

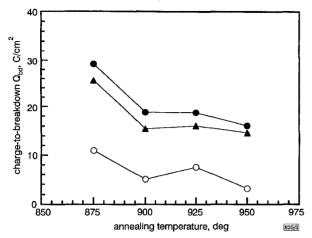

**Fig. 3** Average of charge-to-breakdown of BF $_2^+$ -implanted, B<sup>+</sup>-implanted and Si-B samples annealed at 875–950 °C for 15min

Si-B

▲ B<sup>+</sup>

○ BF<sub>2</sub><sup>+</sup>

Result and discussion: To evaluate boron penetration, the flat-band voltage,  $V_{fb}$ , measured from the high-frequency C-V curves, is applied. Boron penetration causes a positive  $V_{th}$  shift. More severe boron penetration results in a larger  $V_{tb}$  shift. Fig. 1 shows  $V_{tb}$ against different annealing temperatures from 875 to 950°C for 15min. The BF<sub>2</sub>+-implanted sample exhibits the largest  $V_{th}$  shift resulting from the F-enhanced boron penetration. More importantly, although the B+-implanted sample has a smaller value of  $V_{tb}$  than the BF<sub>2</sub>+-implanted sample, the  $V_{tb}$  shift is smallest for the Si-B sample. The Weibull plots of the charge-to-breakdown value for the BF<sub>2</sub>+-implanted and Si-B samples are shown in Fig. 2. The stress current density is 100mA/cm<sup>2</sup> and the gate area of the capacitor is  $4.42 \times 10^{-5}$ /cm<sup>2</sup>. There are two groups clearly separated in the Figure. For the  $BF_2^+$ -implanted samples, the  $Q_{bd}$  is distributed over the wide range 1-10C/cm<sup>2</sup> for the annealing temperatures studied. In addition, they also depict a lower  $Q_{bd}$  value

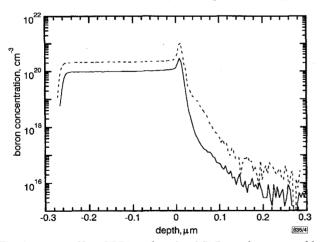

Fig. 4 Boron profiles of  $BF_2^+$ -implanted and Si-B samples, measured by SIMS analyses

compared with the Si-B samples. For the Si-B sample, the  $Q_{bd}$  distribution is much tighter and also higher in value. For the Si-B sample, the  $Q_{bd}$  decreases as the annealing temperature is increased. The average  $Q_{bd}$  for the Si-B, B<sup>+</sup>-, and BF<sub>2</sub><sup>+</sup>-implanted samples are compiled and shown in Fig. 3. The Si-B sample exhibits the largest  $Q_{bd}$  for all of the temperature range. The B<sup>+</sup>-

implanted sample is in-between the Si-B and BF $_2$ \*-implanted samples. Fig. 4 shows the boron profiles of the Si-B and BF $_2$ \*-implanted samples measured by SIMS analyses. The Si-B samples indeed show a smaller B concentration at both the SiO $_2$ /Si interface and in the Si-substrate.

Conclusion: In conclusion, a novel Si-B diffusion source for a  $p^+$ -poly-Si gate in pMOSFETs has been investigated, for the first time, in this study. This process shows a better performance for suppressing boron penetration than conventional BF<sub>2</sub>+-or B+-implanted samples, for a wide range of annealing temperatures and times. This new process is a very promising candidate for fabricating surface-channel pMOSFETs in future deep-submicron CMOS.

© IEE 1998 7 October 1997 Electronics Letters Online No: 19980061

T.S. Chao, T.F. Lei, T.Y. Huang and C.Y. Chang (National Nano Device Laboratories, 1001-1 Ta Hsueh Road, Hsinchu 300, Taiwan, Repubic of China)

C.P. Kuo (Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, Republic of China)

T.P. Chen (United Microelectronics Corporation, Science-Based Industrial Park, Hsinchu, Taiwan, Republic of China)

T.F. Lei, T.Y. Huang and C.Y. Chang: Also with Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, Republic of China

E-mail: tschao@ndl.nctu.edu.tw

## References

- Hu, G.J., and BRUCE, R.H.: 'Design tradeoffs between surface and buried-channel FETs', *IEEE Trans. Electron Devices*, 1985, **32**, pp. 584–588

- 2 TSENG, H.-H., TOHIN, P.J., BAKER, F.K., PFIESTER, J.R., EVANS, K., and FEJES, P.L.: 'The effects of silicon gate microstructure and gate oxide process on threshold voltage instability in p\*-gate MOSFETs with fluorine incorporation', *IEEE Trans. Electron Devices*, 1992, 39, pp. 1687–1693

- 3 WU, S.L., LEE, C.L., and LEI, T.F.: 'Suppression of boron penetration into an ultrathin gate oxide (< 7nm) by using a stacked-amorphous-silicon film'. IEDM Tech. Dig., 1993, pp. 329–332

- 4 CHAO, T.S., and CHU, C.H.: 'Inductive-coupling-nitrogen-plasma process for suppression of boron penetration in BF<sub>2</sub><sup>+</sup>-implanted poly-Si gate', *Appl. Phys. Lett.*, 1997, 70, pp. 55–56

## Thermally evaporated ITO/GaAs Schottky barrier contacts

A. Salehi and K.N. Toosi

ITO/n-GaAs Schottky barrier contacts have been fabricated by thermal evaporation of  $In_2O_3/SnO_2$  on GaAs with various deposition rates  $r_D$ . The variation in the contact characteristics was systematically investigated with respect to the deposition rate. The optimal deposition rate of 0.2Å/s yields a barrier height of 0.80eV and unity ideality factor with a transmittance value of > 80% in the visible region of the spectrum.

In recent years, considerable attention has been given to transparent electrically conducting thin films, especially indium tin oxide (ITO), because of their unique properties which make them useful in many applications. ITO films are characterised by a high visible transparency (T>80%) and a low electrical resistivity ( $\rho\simeq10^{-4}\Omega{\rm cm}$ ), thus providing a very good Schottky contact to GaAs and InP photodiodes, solar cells [1, 2] and, more recently, optical HBTs [3]. In a previous paper [4], we reported the excellent radiation resistance of the ITO films [4]. Despite the significant progress in the use of ITO in device structures, surprisingly little research has been devoted to the fabrication of thermally evaporated ITO layers on semiconductors [5]. At present, there is no information about the role of deposition rate in opto-electronics properties of ITO layers.