# High-Performance Polysilicon Contacted Shallow Junctions Formed by Stacked-Amorphous-Silicon Films

S. L. Wu, Chung-Len Lee, Member, IEEE, and T. F. Lei

Abstract—A high-performance polysilicon contacted shallow junction diode formed by using a stacked-amorphous-silicon (SAS) film as the diffusion source is reported. The diode exhibited a very low leakage current ( $\leq 1$  nA/cm<sup>2</sup> at -5 V), a very high breakdown voltage ( $\geq 100$  V), and a forward ideality factor  $m \leq 1.05$  over 7 decades.

## I. Introduction

THE use of highly doped poly-Si film as the diffusion source to form a shallow junction and simultaneously as the device contact has been widely investigated [1]-[6]. It is generally recognized that the as-deposited poly-Si (ADP) film is an anisotropic structure with its columnar grains perpendicular to the substrate. Dopants diffuse anisotropically and rapidly through the vertical grain boundaries, producing irregular morphologies at the poly-Si/oxide or the poly/monosilicon interfaces. The amorphous silicon ( $\alpha$ -Si) film is of a random structure and has no preferential grain orientation. Smoother  $\alpha$ -Si/SiO<sub>2</sub> or  $\alpha$ -Si/Si interfaces and more shallow junctions may be obtained [3]. However, recently it has been reported that the  $\alpha$ -Si film gives a less uniform junction than does the ADP film [5].

In this letter, we report a high-performance polysilicon contacted shallow junction diode fabricated by using a stacked-amorphous-silicon (SAS) film as the diffusion source.

## II. DEVICE STRUCTURE AND FABRICATION

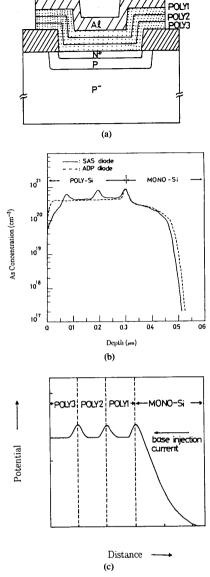

Fig. 1(a) shows the SAS emitter contacted  $n^+$ -p diode. The device is formed by depositing an  $\alpha$ -Si film in three steps with a low-pressure chemical vapor deposition (LPCVD) system onto p-type silicon substrates. After the arsenic implantation and annealing processes, arsenic atoms segregate at the boundaries of  $\alpha$ -Si stacked layers as well as the poly/monosilicon interface, as shown in Fig. 1(b). The segregated atoms will create potential barriers as shown in Fig. 1(c), which retard the minority carriers injected from the base into the poly-Si emitter region [6]. This may reduce the base current.

Manuscript received September 4, 1991; revised October 3, 1991. This work was supported by the National Science Council of the Republic of China through Contract NSC 79-0404-E009-08.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, Republic of China.

IEEE Log Number 9105371.

The detailed fabrication processes of the SAS n<sup>+</sup>-p diodes were as follows: p-type (100), 4-11.5  $\Omega$  · cm silicon wafers were first thermally oxidized and patterned, and the BF2 implanted at 40 keV with a dose of  $5 \times 10^{13}$  cm<sup>-2</sup> to simulate the base doping level of a bipolar transistor. Prior to the α-Si film deposition, all wafers were dipped in a HF:H2O (1:50) solution to remove any native oxide. A three-stacked  $\alpha$ -Si layer with a total thickness of about 3500 Å was deposited at 550°C. During the three-step deposition, the chamber of the LPCVD system was not interrupted. All wafers were then doped with an arsenic implantation at 120 keV with a dose of  $1 \times 10^{16}$  cm<sup>-2</sup>. Subsequently, a thermal oxide film was grown on wafers at 900°C for 5 min in a wet O<sub>2</sub> ambient and then annealed and driven-in at 1000°C for 25 min in a dry O2 ambient. During the oxidation and annealing stage, the  $\alpha$ -Si film was recrystallized into poly-Si and the dopant diffused into the substrate to form the n<sup>+</sup>-p shallow junction. After aluminum film evaporation and pattern definition, all devices were sintered at 400°C for 30 min in an N<sub>2</sub> ambient.

### III. RESULTS AND DISCUSSIONS

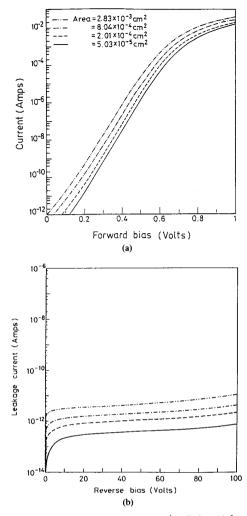

Fig. 2(a) and (b) shows the typical forward and reverse I-V characteristics of SAS  $n^+$ -p diodes with various areas, respectively. It can be seen that all diodes have an ideality factor of 1.05 over 7 decades. The forward saturation currents  $J_{\rm c}$  are proportional to their area respectively. All diodes exhibit a very low leakage current even at -100 V. For example, for the curve of the diode area of  $2.83 \times 10^{-3}$ cm $^{-2}$ , the reverse leakage current is only 11.6 pA at -100V. The leakage currents for these diodes are also proportional to their areas respectively. It can also be seen that the breakdown voltages of all diodes exceed 100 V (actually more than 110 V, measured by a separate HP370A programmable curve tracer). The value of the breakdown voltage approaches that of a conventional single-crystal Si n<sup>+</sup>-p diode with a substrate doping level of  $4 \times 10^{15}$  cm<sup>-3</sup> with an infinite curvature radius [7]. However, the SIMS arsenic profile, as shown in Fig. 1(b), shows that the emitter junction depth is only about  $0.2 \mu m$ . This may be caused by an LDD-like structure on the diffusion profile for this device to give such a high breakdown voltage [8].

In order to make comparisons, n<sup>+</sup>-p diodes were also fabricated by using the ADP film as the diffusion source. These diodes were made with the same procedures as those

0741-3106/92\$03.00 © 1992 IEEE

Fig. 1. (a) The cross-section structure of the SAS emitter contacted  $n^+$ -p diode. (b) SIMS arsenic profiles of the SAS diode (solid line) and the ADP diode (dashed line). (c) The potential distribution inside the SAS emitter region.

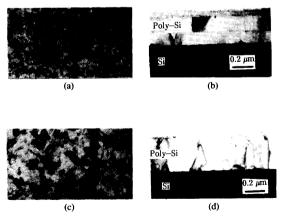

of the SAS n<sup>+</sup>-p diodes except that the silicon film was deposited at 625°C in one step. The SIMS arsenic profile of one of the ADP n<sup>+</sup>-p diodes is also shown in Fig. 1(b) (dashed line). It can be seen that the junction depth of the SAS diode is shallower than that of the ADP diode. This is because the segregated interfaces between a-Si stacked layers had a retardation effect on the arsenic diffusion during the annealing process. Fig. 3(a)-(d) shows TEM micrographs, both in the plan and the cross-sectional views, of the SAS diode and the ADP diode. It can be seen that for the SAS diode, the grain size is smaller because the segregated bound-

Fig. 2. The I-V characteristics of the SAS  $n^+$ -p diodes: (a) forward and (b) reverse.

Fig. 3. The plan and cross-sectional views of TEM micrographs, respectively, for (a), (b) the SAS diode, and (c), (d) the ADP diode.

II.

Fig. 4. Arrhenius plots of the SAS and the ADP n<sup>+</sup>-p diodes. The  $J_R$  was measured at -5 V and the activation energies derived from the plots at 1.13 and 0.937 eV, respectively.

aries in the SAS film limit the grain growth. Also, the realignment of epitaxial growth at the poly/monosilicon interface is also observed. By referencing [5], this may give more uniform junction. Fig. 4 shows the typical Arrhenius plots of  $\log_e(J_R/T^3)$  versus 1/T of the SAS diode and the ADP diode, where  $J_R$  is the reverse current density of diodes measured at -5 V. The activation energies  $E_{g(\text{eff})}$  derived from the plots for the SAS diode and the ADP diode are 1.13 and 0.937 eV, respectively. For the SAS diode, the value of  $E_{g(\text{eff})}$  is approximately equal to the bandgap of Si. This indicates that the reverse leakage current of the SAS diode was mostly contributed by the diffusion current outside the depletion region [7], [8]. For the ADP diode, the genera-

tion current in the depletion region contributed a significant part in the reverse current.

#### IV. CONCLUSION

In conclusion, a high-performance polysilicon contacted  $n^+$ -p diode can be obtained by using a SAS film as the diffusion source. The fabricated diode exhibits a very low leakage current ( $\leq 1 \text{ nA/cm}^2 \text{ at } -5 \text{ V}$ ), a very high breakdown voltage ( $\geq 100 \text{ V}$ ), and a forward ideality factor  $m \leq 1.05 \text{ over } 7 \text{ decades}$ . It is believed that this structure can offer a superior performance for shallow junction diodes in future VLSI applications.

#### ACKNOWLEDGMENT

The authors are grateful to Prof. S. M. Sze for helpful discussions.

#### REFERENCES

- J. M. C. Stork, M. Arienzo, and C. Y. Wong, "Correlation between the diffusive and electrical behavior properties of the interface in polysilicon contacted n\*-p junctions," *IEEE Trans. Electron Devices*, vol. ED-32, pp. 107-111, 1985.

H. K. Park et al., "High-speed polysilicon emitter-base bipolar

- [2] H. K. Park et al., "High-speed polysilicon emitter-base bipolar transistor," *IEEE Electron Device Lett.*, vol. EDL-7, pp. 568-660, 1986.

- [3] T. Kamins, Polycrystalline Silicon for Integrated Circuit Applications. Boston: Kluwer Academic, 1988.

- [4] S. L. Wu, C. L. Lee, and T. F. Lei, "Improvement of electrical characteristics of polycrystalline silicon-contacted diodes after forward bias stressing," *Appl. Phys. Lett.*, vol. 57, pp. 1904–1906, 1990.

[5] K. Park, S. Batra, and S. Banerjee, "Analysis of lateral uniformity of

- [5] K. Park, S. Batra, and S. Banerjee, "Analysis of lateral uniformity of ultrashallow junctions in polycrystalline silicon-on-single crystalline systems," Appl. Phys. Lett., vol. 59, pp. 709-711, 1991.

- [6] B. Jalali and E. S. Yang, "A general model for minority carrier transport in polysilicon emitters," Solid-State Electron., vol. 32, pp. 323-327, 1989.

- [7] S. M. Sze, Semiconductor Devices, Physics and Technology. New York: Wiley, 1985, p. 107.

- [8] S. L. Wu, C. L. Lee, and T. F. Lei, "Characteristics of polysilicon contacted shallow junction diode formed with a stacked amorphous silicon film," to be submitted for publication.