# 國立交通大學

電機學院IC設計產業研發碩士班

# 碩士論文

適用於多模式高速通訊系統之 低複雜度里德所羅門編解碼模組

Low Complexity Reed-Solomon CODEC for Multi-Mode High-Speed Communication Systems

研究生:蘇建毓

指導教授:溫瓌岸 教授

中華民國九十七年一月

## 適用於多模式高速通訊系統之低複雜度里德所羅門編解碼模組 Low Complexity Reed-Solomon CODEC for Multi-Mode High-Speed Communication Systems

研究生:蘇建毓 Student: Jian-Yuh Su

指導教授:溫瓌岸 博士 Advisor:Dr. Kuei-Ann Wen

國立交通大學 電機學院IC設計產業研發碩士班 碩士論文

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program on IC Design

January 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年一月

# 國立交通大學 電機學院IC設計產業研發碩士班

## 論文口試委員會審定書

| 本校    | 電機學院 IC 設計產業研發碩士班 | 蘇建航 | 君 |

|-------|-------------------|-----|---|

| 所提論文: |                   |     |   |

| (中文)  | 適用於多模式高速通訊系統之低複雜度里德索羅門編解                         |

|-------|--------------------------------------------------|

| ,     |                                                  |

| (英文)_ | Low-complexity Reed-Solomon CODEC for Multi-mode |

|       | High-speed Communication Systems                 |

合於碩士資格水準、業經本委員會評審認可。

| 口試委員:       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

|-------------|----------------------------------------|

| 是差差         |                                        |

|             |                                        |

|             |                                        |

| 指導教授: 7000  |                                        |

| 專班主任: 40 80 |                                        |

學生:蘇建毓 指導教授:溫瓌岸 博士

#### 國立交通大學電機學院產業研發碩士班

摘 要

本論文主要討論設計一應用於多模式高速通訊系統之低複雜度里德所羅門編解碼模組。所提出的演算法以係數最簡化為方針。由 PGZ 演算法,Berlekamp演算法,iBMA,到提出的 SiBM 演算法,皆有詳盡的推導及整合比對。尤其著名的廣義牛頓特性,是 Berlekamp 系列演算法的重要精神,在本論文以三種方法來推導驗證,這些皆在第二章以數學表示法呈現。

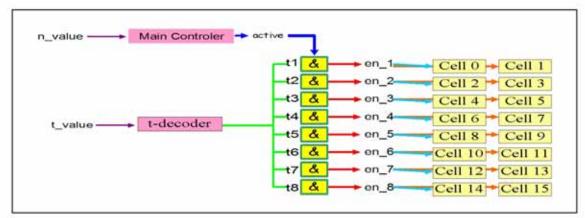

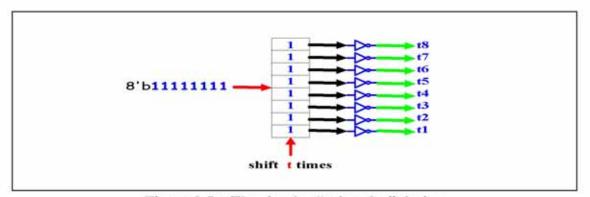

所提出的架構有主要幾個特色,以解碼器的三個主要運算區塊來做介紹: 一、在錯誤症(syndrome)計算區塊,藉由非常簡單的 t 解碼器,來支配十六個症 狀值單元動作,以達到可以運用在多模操作上。

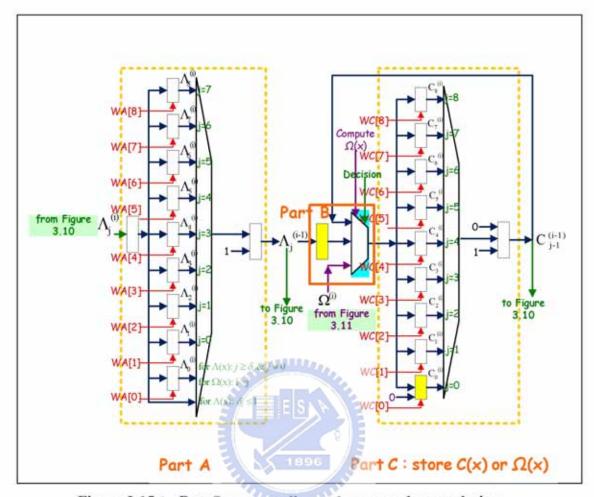

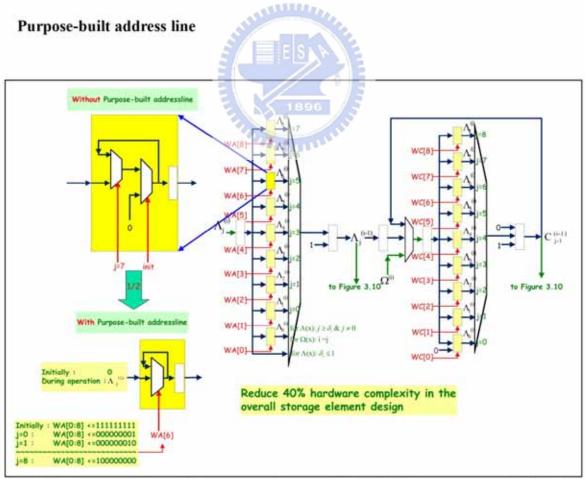

二、在關鍵方程式求解器(KES),為了克服大部分序列式 BM 架構,計算差值接著決定更新校正方程式的關鍵路徑的瓶頸,以及避免在特殊錯誤位置及錯誤值組合所產生的資料危障。此設計藉由判定時序改變,控制迭代及資料流,取代延時(stall)。使得計算錯誤位置方程式的時脈週期數小於2t(t+1),約為 $t\cdot\delta_i+3t$ 個週期數( $\delta_i$ 為第i迭代的 degree)。且藉由在演算法上將係數同化,以致於在設計共用電路時,甚至不需額外硬體來選擇資料流,因此某些關鍵路徑瓶頸得以克服。更進一步利用特製位址線,和較簡單的控制電路聯結技巧,省去許多電路。

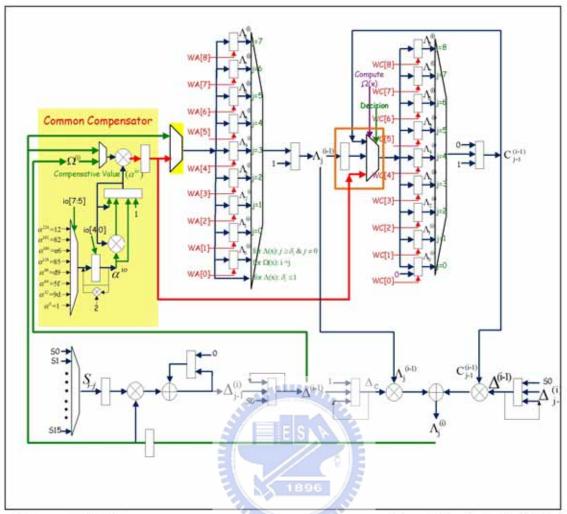

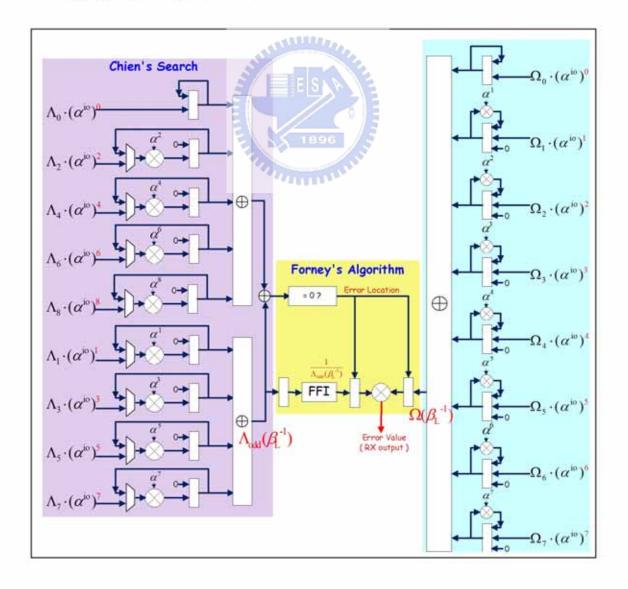

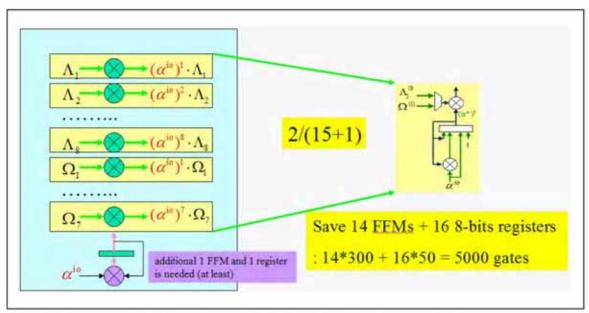

三、在 CSEE 區塊,為符合多模式操作,通常在輸入端加上有限場乘法器,使 Chien's Search 跳至指定搜尋起點及產生對應的錯誤值。本論文提出一個共用補償器的方法,並將其和合併到 KES 中,大幅減少硬體,使得由單模(255,239)至多模僅需增加少許的邏輯閘數,電路示意圖於第三章呈現。

此架構實作於 Xinlinx VirtexE xcv2000e FPGA 和 UMC 0.18 1P6M 製程,經過 204.8 億隨機位元驗證,皆正常運作。在最高時脈頻率(Clock Rate) 730Mhz 下,數據傳輸率(Data Rate)可達 5.84bps,此時僅約 11596 個邏輯閘數。

# Low Complexity Reed-Solomon CODEC for Multi-Mode High-Speed Communication Systems

student: Jian-Yuh Su Advisors: Dr. Kuei-Ann Wen

Industrial Technology R & D Master Program of Electrical and Computer Engineering College National Chiao Tung University

#### **ABSTRACT**

In this thesis, a high-speed and low-complexity design of multi-mode Reed-Solomon codec is proposed. In the beginning of deliberating algorithms, the policy is to simplify the coefficients of equations, so as to construct a simpler structure.

THE PERSON NAMED IN

The proposed RS decoder has some major features introduced as following:

- 1. In the SC block, a simpler t-decoder is exploited to dominate the sixteen cells, so as to answer to multi-mode applications.

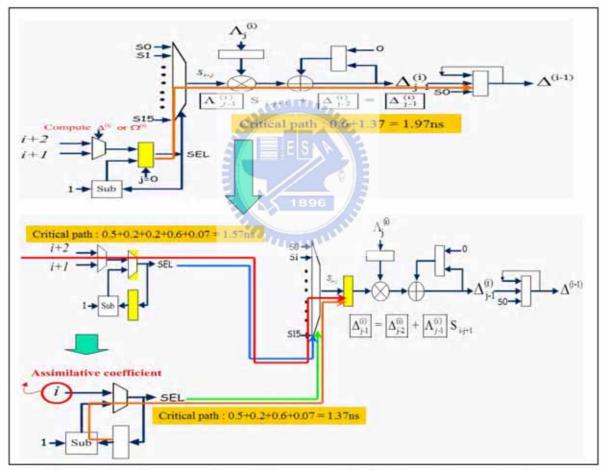

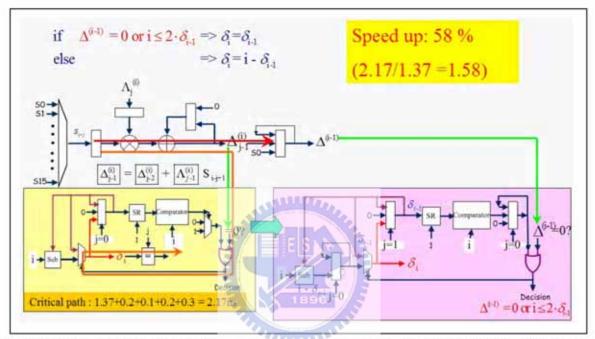

- 2. In the KES, the "Decision Variations" is proposed to break the main speed bottleneck of iBMA in the iterative computation of discrepancies followed by updating the correction polynomial and to prevent the special-case data hazard in the most serial structures. Also, for the sake of keeping the critical path in the reusing hardware is still  $T_{ff} + T_{mult} + T_{xor}$ , the assimilative coefficient knack is adopted. Further, we use the purpose-built address line to simplify the hardware complexity of storage element

- 3. In Chien's Search and Forney's block, fifteen Compensators used to adjust the starting point of search are reduced to one and combined in the KES block.

After 204.8 hundred-million bits transmission and verification regular, the proposed RS decoder for multi-mode applications (n<=255, t<=8) is implemented by Xinlinx VirtexE xcv2000e FPGA and Synopsys DC with UMC018 library. The design possesses higher speed and lower gate count than present decoder design. The data rate of the proposed decoder is 5.84bps at the maximum clock rate of 730MHz with 11596 gates.

在完成本篇論文之際,首先要感謝的是我的指導教授溫瓌岸教授。在就讀研究所的期間,承蒙教授不斷給予研究方向上的指導、督促與研究資源;在此向溫教授致上最誠摯的謝意。此外,亦感謝參與口試審核委員會的交大研發長李鎮宜教授與台大電機系所吳安宇教授,提供寶貴的建議與指教。

接下來要感謝的就是實驗室的學長姐們的指導與照顧:美芬學姐、嘉笙學長、哲生學長、文安學長、晧名學長、立協學長、彥凱學長、懷仁學長、志德學長、俊憲學長等。學長姐們的幫助與指導讓我獲益良多。

還有感謝實驗室的同學們一世基、書旗、昱瑞、建龍、家岱、漢健、閎仁,兩年來在課業和日常生活上總是相互的扶持,一起高興、一起嬉笑、一起度過難關。還有給予我信心與勇氣的學弟們一佳欣、磊中、國爵、柏麟、俊彦、士賢、謙若,同時也要感謝實驗室的助理們一苑佳、淑怡、慶宏、恩齊、怡倩、智伶、宛君、嘉誠,幫忙實驗室裡大大小小的事,讓我們能更專心於研究工作。

最後,我最要感謝的是家人與女友無怨無悔的付出與支持,感謝好友們給我的鼓勵,感謝關心我與幫助我的人,……,要感謝的人族繁不及備載,謹此這篇研究論文,與我的家人及好友分享我的收穫與喜悅。

蘇建毓

2008 年 1 月

# Contents

| Chapter 1  | Introduction                                               | 1  |

|------------|------------------------------------------------------------|----|

| 1.1 Backs  | ground                                                     | 1  |

|            | vation                                                     |    |

|            | nization                                                   |    |

| Chapter 2  | Mathematic Representation of RS codec                      | 9  |

| 2.1 Galoi  | s Field GF(2")                                             | 9  |

| 2.1.1      | Galois field element                                       | 9  |

| 2.1.2      | Primitive Polynomial p(x)                                  | 10 |

| 2.1.3      | Constructing the Galois Field                              | 10 |

| 2.1.4      | The operation of Galois Field                              | 12 |

| 2.2 Encod  | The operation of Galois Field                              | 13 |

|            | Code Generator Polynomial                                  |    |

| 2.2.2      | Forming the codeword                                       | 14 |

| 1          | Method 1: $C(x) = I(x) \cdot g(x)$                         | 14 |

| 1          | Method 2 : $C(x) = I(x) \cdot x^{2t} + p(x) = g(x)q(x)$    | 15 |

| 2.3 Deco   | ding of Reed-Solomon Codes                                 | 16 |

| 2.3.1      | Syndrome Calculation                                       | 17 |

| 2.3.2      | The Key Equation Solver                                    | 19 |

| 2          | 2.3.2.1 The Peterson-Gorenstein-Zierler Algorithm          | 19 |

| 2          | 2.3.2.2 The Berlekamp-Massey Algorithm                     | 22 |

| 2          | 2.3.2.3 Proposed Serial and inversion-less Berlekamp-Masso | ey |

| 2          | algorithm (SiBM):                                          | 30 |

| 2.3.3      | The Chien's Search                                         | 32 |

| 2.3.4      | The Forney's algorithm                                     | 33 |

| Chapter 3  | Schematic-view of Proposed RS CODEC                        |    |

| Architectu | re                                                         | 35 |

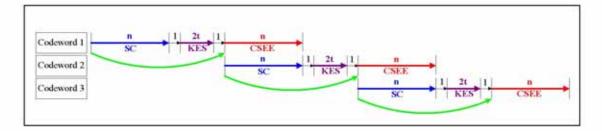

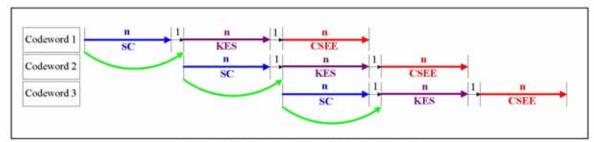

| 3.1 Pipeli | ine Topology                                               | 36 |

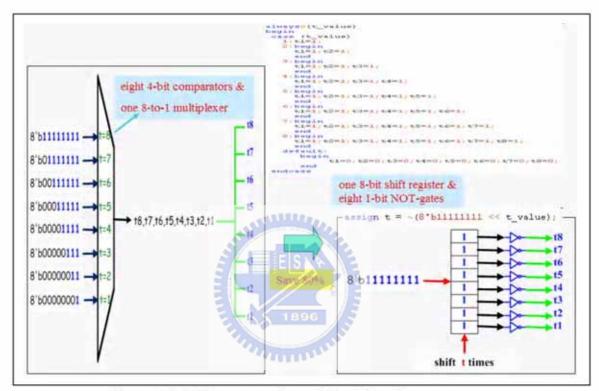

| 3.2 The t-Decoder.                                 | 37 |

|----------------------------------------------------|----|

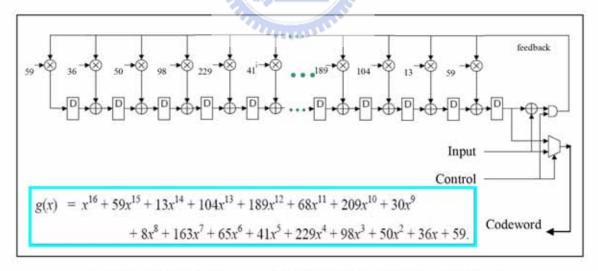

| 3.3 Encoder Architecture                           | 39 |

| 3.4 Syndrome Calculator (SC)                       | 41 |

| 3.5 Key Equation Solver (KES)                      |    |

| 3.6 Shorten Code Compensator                       |    |

| 3.7 Chien's Search and Error Evaluator(CSEE) Block |    |

| Chapter 4 Implementation & Verification            | 54 |

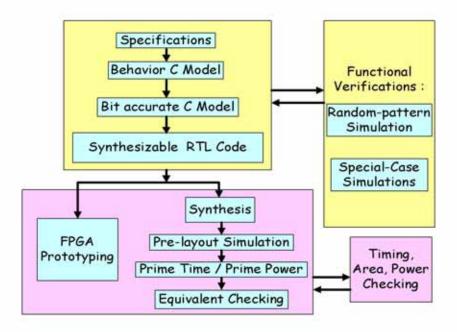

| 4.1 Design Flow                                    | 54 |

| 4.2 Functional Verifications                       | 55 |

| 4.2.1 Random Simulation                            | 56 |

| 4.2.2 Special-Case Simulation                      | 57 |

| 4.3 FPGA prototyping                               | 58 |

| 4.4 Synthesis Result                               | 60 |

| Chapter 5 Comparisons                              | 61 |

| 5.1 Algorithm Compare                              | 61 |

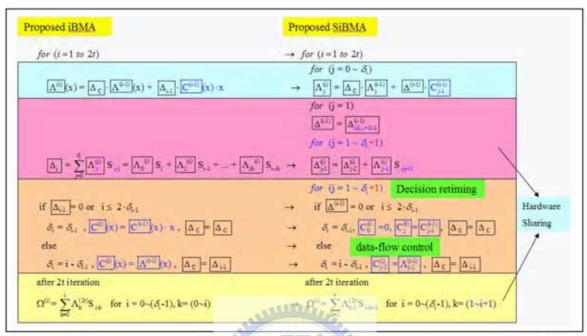

| 5.1-1 Conventional iBMA versus Proposed iBMA       | 61 |

| 5.1-2 Proposed iBMA versus Proposed SiBMA          | 62 |

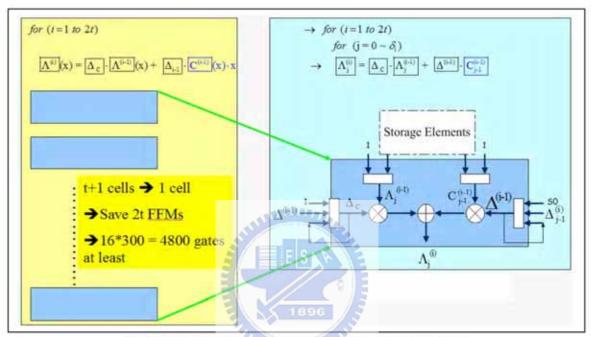

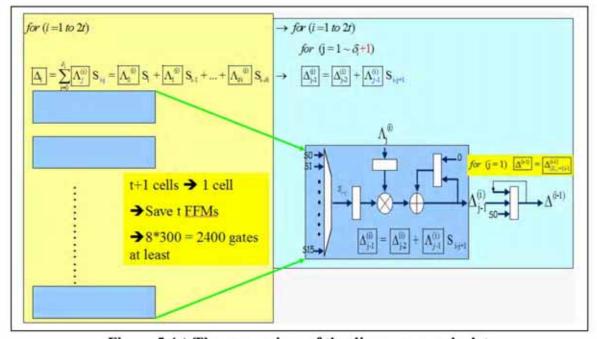

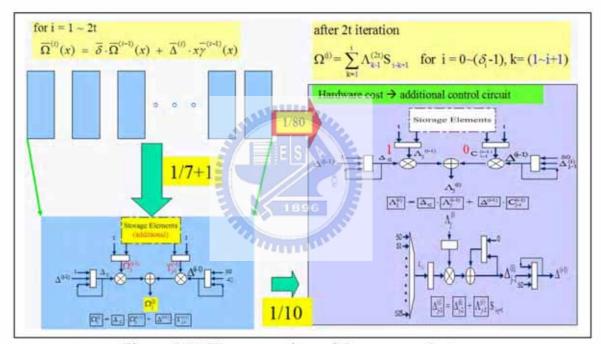

| 5.2 Architecture Compare                           | 63 |

| 5.2-1 Parallel to Serial                           | 63 |

| 5.2-2 Speed up                                     | 65 |

| 5.2-3 Simpler Design                               | 67 |

| The t-decoder                                      | 67 |

| The common compensator                             | 68 |

| Purpose-built address line                         | 69 |

| 5.3 Performance Compare                            | 70 |

| Chapter 6 Conclusions & Future work                | 72 |

| 6.1 Summary                                        | 72 |

| 6.2 Future Works                                   | 73 |

# **List of Figures**

| Figure 1.1: The connection of FEC in the communication system                  | 1     |

|--------------------------------------------------------------------------------|-------|

| Figure 1.2: The Constitution of Reed-Solomon Code                              | 2     |

| Figure 1.3: The classification of Reed-Solomon Codes in the FEC                | 3     |

| Figure 1.4: The characteristic chart of VLSI design orientation.               | 5     |

| Figure 2.1 : An example of multiplication in Finite Field                      | 12    |

| Figure 2.2: The Construction of a Codeword in Systematic Encoding              | 15    |

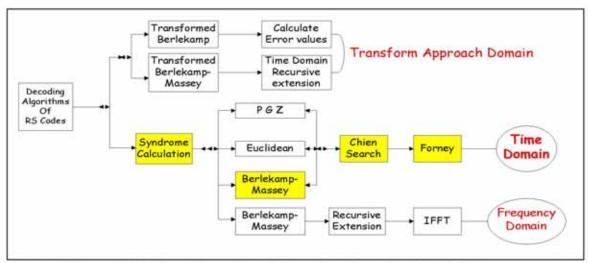

| Figure 2.3: The Categories of Decoding Algorithm in RS Codes                   | 16    |

| Figure 2.4: The LFSR Structure of Berlekamp-Massey algorithm                   | 26    |

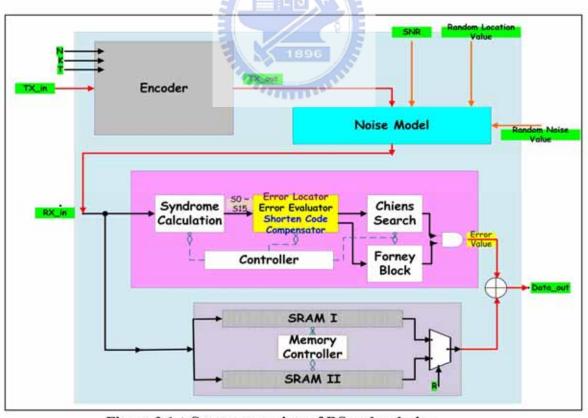

| Figure 3.1 : System overview of RS codec design                                |       |

| Figure 3.2: The two-stage pipeline                                             |       |

| Figure 3.3: The three-stage pipeline. E.S.                                     | 37    |

| Figure 3.4: The connection of 16 cells in the encoder or SC block              | 38    |

| Figure 3.5: The simpler "t-decoder" design.                                    | 38    |

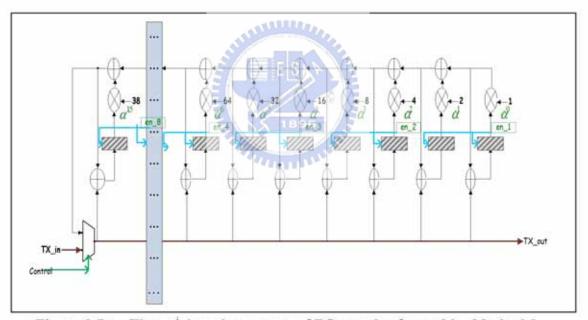

| Figure 3.6: The structure of RS encoder formed by Method 2.                    |       |

| Figure 3.7: The $\alpha^i$ -based structure of RS encoder formed by Method 3   | 40    |

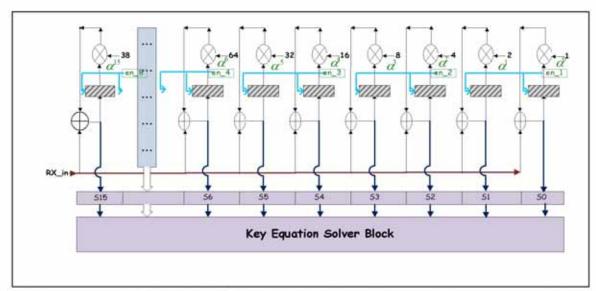

| Figure 3.8: Syndrome calculator block                                          | 42    |

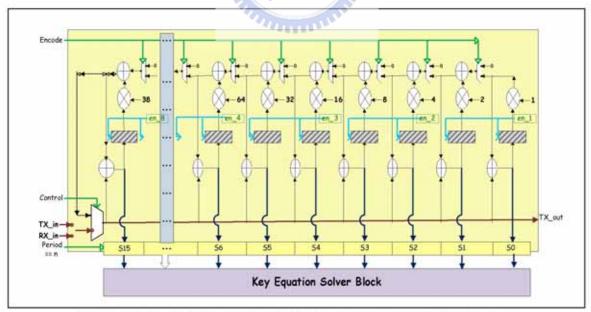

| Figure 3.9: Combined Multi-Mode Encoder & SC Architecture                      | 42    |

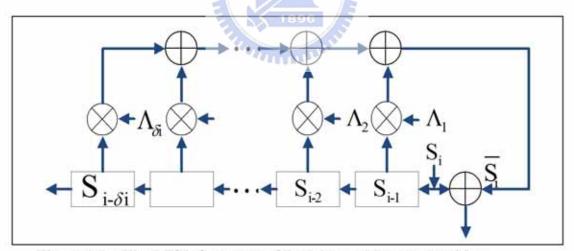

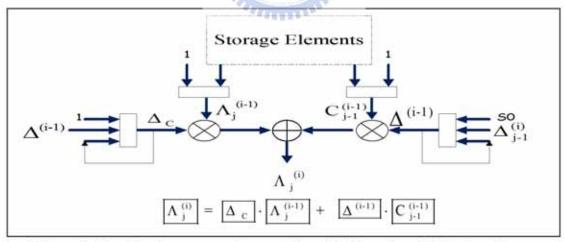

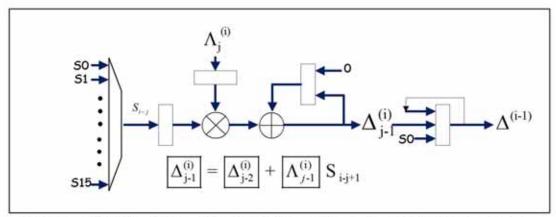

| Figure 3.10 : The Structure of computing $\Lambda(x)$ by using SiBM algorithm  | 43    |

| Figure 3.11: The decomposed architecture for computing i-th discrepancy        | 44    |

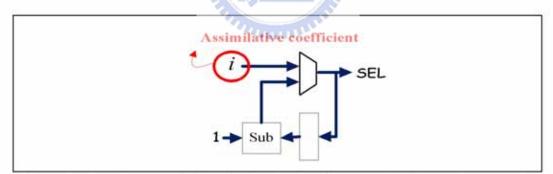

| Figure 3.12: The control circuit of selection line to select the syndrome valu | es 45 |

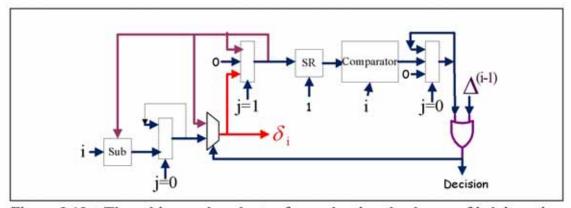

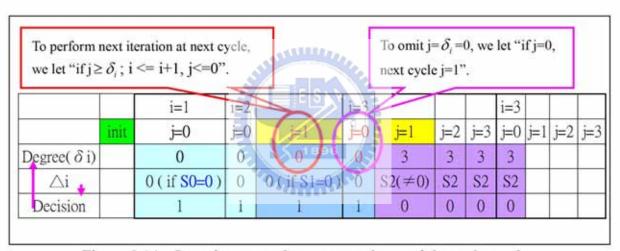

| Figure 3.13: The arbiter and evaluator for evaluating the degree of i-th iter  | ation |

|                                                                                | , 46  |

| Figure 3.14: Iteration control to prevent the special case hazard              |       |

| Figure 3.15: Dataflow controller and storage element design                    | 48    |

| Figure 3.16: The common compensator and its connection with whole KES          | block |

|                                                                                | 51    |

| Figure 3.17: The CSEE Block                                                    | 53    |

| Figure 4.1: Design Flow and verifications                                      | 55    |

| Figure 4.2: Parts of output file of bit-accurate C model.                      | 55    |

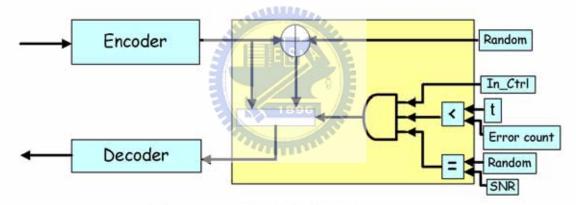

| Figure 4.3: The Noise Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

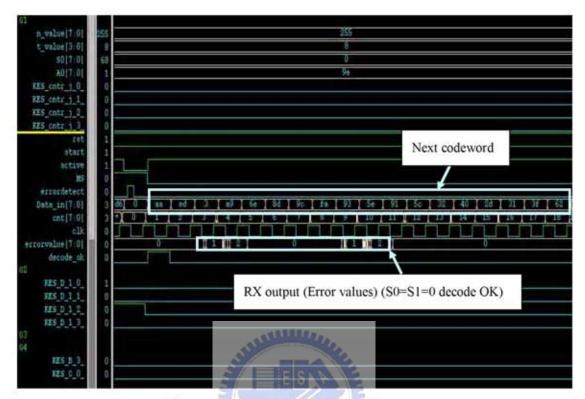

| Figure 4.4: Gate-level simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58  |

| Figure 4.5: The connection of FPGA Board, pattern generator, and logic analy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | zer |

| ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59  |

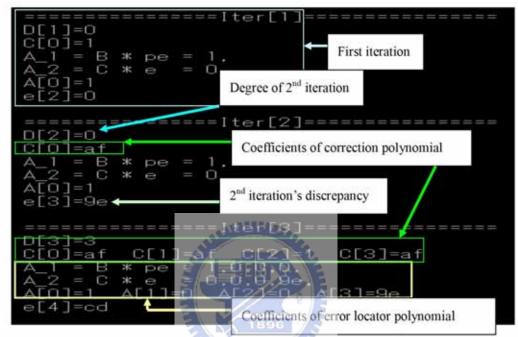

| Figure 4.6: One of the simulation results in the special-case simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

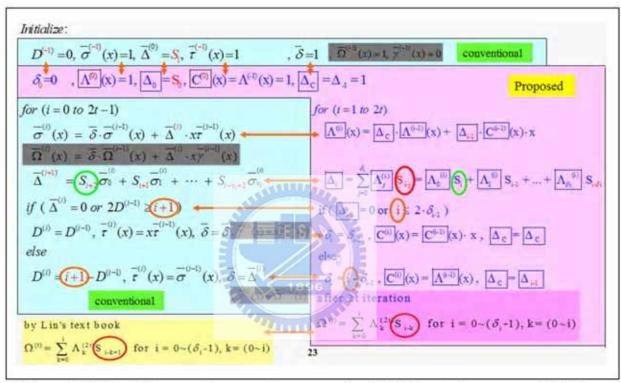

| Figure 5.1: The differences between the conventional iBMA and the proposed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| iBMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62  |

| Figure 5.2: The comparison between the proposed iBMA and the proposed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| SiBMA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63  |

| Figure 5.3: The comparison of the error-locators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64  |

| Figure 5.4: The comparison of the discrepancy calculator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64  |

| Figure 5.5: The comparison of the error-evaluators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65  |

| Figure 5.6: The comparison of the control circuits for syndrome selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66  |

| Figure 5.7: The comparison between the normal condition and the "Decision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Variation".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67  |

| Figure 5.8: The comparison of the t-decoders.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68  |

| Figure 5.9: The comparison between the conventional design and the common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   |

| compensators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69  |

| Figure 5.10: The comparison of the storage element with and without                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| purpose-built address line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69  |

| El Marian Committee of the Committee of |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Table 1.1: Some parameters list of specification with regard to RS codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Table 2.1: The construction of the GF(256) elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Table 2.2 : Iterative procedure for finding the error-location polynomial $\Lambda(x)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25  |

| Table 4. 1: The Synthesis Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59  |

| Table 4.2: The performance of each synthesized module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60  |

| Table 5.1: The comparison with publications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70  |

# Chapter 1

## Introduction

## 1.1 Background

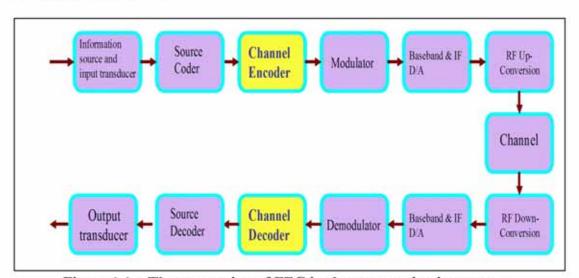

In the communication system and storage system, the integrity of data transmission is necessary. But the error probability increases after interference introduce. Consequently, the correctness of data transmission is reduced. So, many digital signaling applications in communication system and storage system employ Forward Error Correction (FEC). FEC is a technique in which redundant information is added to the signal to allow the receiver to detect and correct errors that may have occurred in transmission. Figure 1.1 shows the connection of FEC in the communication system.

Figure 1.1: The connection of FEC in the communication system

Many different types of codes have been devised for this purpose. Due to the well characteristic of error correction capability for both random errors and burst errors, Reed-Solomon codes [1] have been widespread used for error correction in various kinds of digital transmission and storage systems. It has been proved to be a good compromise between efficiency and complexity.

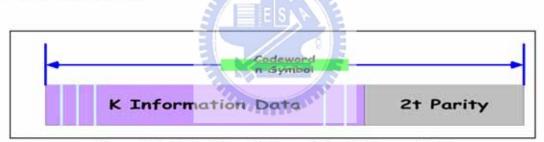

In general, the main categories of error correcting codes are block codes and convolution codes. Reed-Solomon codes are belonging to a block code, meaning the message to be transmitted is divided into separate blocks of data and each block has parity protection information added to it to form a self-contained codeword. It is also a systematic code, which means the encoding process does not vary the message symbols. The protection symbols are added as a separate part of the block. Figure 1.2 is a sketch map of this.

Figure 1.2: The Constitution of Reed-Solomon Code.

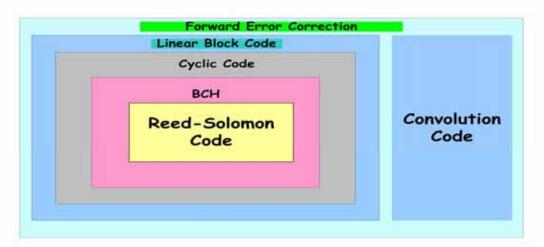

In Reed-Solomon codes, any two code-words operation produces another codeword. So, Reed-Solomon code is also a linear code. And because of cyclically shifting the symbols of a codeword produces another code-word, it is cyclic. The classification of Reed-Solomon Codes in the FEC is shown in Figure 1.3. Furthermore, it belongs to the family of Bose-Chaudhuri-Hocquenghem (BCH) codes [2, 3], but is distinguished by having multi-bit symbols. It makes the code particularly good at dealing with bursts of errors. In virtue of that although a symbol may have all its bits in error, this counts as only one symbol error in terms of the correction capacity of the code. It is the important factor in adopting RS code in many practical

applications such as digital audio and video [4], magnetic and optical recording [5,6], computer memory, cable modem[7], xDSL[8,9], wireless and satellite communications systems.

Figure 1.3: The classification of Reed-Solomon Codes in the FEC.

It provides different levels of protection by choosing different parameters for a code and affects the complexity of implementation. Therefore, a RS code can be expressed as (n, k) code, where n is the codeword length in symbols and k is the number of information symbols in the message.

In general,  $n \le 2^m - 1$ . Where m is the order of Galois Field.

If  $n < 2^m - 1$ , this is referred to as a **Shortened Code**. There are n - k parity symbols and t symbol errors can be corrected in a block,

where

$$t = (n-k)/2$$

...... for  $n-k$  even

or  $t = (n-k-1)/2$ ...... for  $n-k$  odd.

Modified RS codes are frequently used for providing different code rates and correcting capabilities. Shortening and puncturing is the major modification of RS codes. Ordinary, the standard error-and-erasure decoder is employed to decode the shortened and punctured RS codes. In this thesis, our design focus on the error-only decoder for the shorten code.

### 1.2 Motivation

As mentioned above, for burst errors and random errors, Reed-Solomon codes are popular to provide data integrity and exploited in numerous digital systems such as those for deep space, digital subscriber loop (cable modem and xDSL), gigabit (1000base-T) and 10G Ethernet (Fiber, Copper), digital audio and video broadcast (DAB/DVB), magnetic and optical recording (CD, DVD), computer memory (HDD), wireless as well as in satellite communications systems, and etc.

Table 1.1: Some parameters list of specification with regard to RS codes.

| Application         | Specification: (n, k, t) |               |  |  |  |

|---------------------|--------------------------|---------------|--|--|--|

| HDD                 | (72, 64, 4)              | (36, 32, 2)   |  |  |  |

| CD                  | (32, 28, 2)              | (28, 24, 2)   |  |  |  |

| DVD                 | (208, 192, 8)            | (182, 172, 5) |  |  |  |

| DVB<br>ITU J83(A,B) | (204, 1                  | 88, 8)        |  |  |  |

| STM-16<br>OC-192    | (255, 239, 8)            |               |  |  |  |

| CCSDS               | (15~255, n-16, 8)        |               |  |  |  |

| x-DSL & Cable modem | (~255, n-2t, t=1~8)      |               |  |  |  |

| WiMAX               | (~255, ~239, ~8)         |               |  |  |  |

The data processing topology in each application is based on different error property.

And because of the difference at processing topology, choosing different parameters such as the number of bit in a symbol, the number of symbol in a codeword and in a information data as well as in the redundant data for a code to provide different levels of protection is necessary. The constitution of parameter is numerous and each application has its own specification parameters. Table 1.1 shows a list of specification

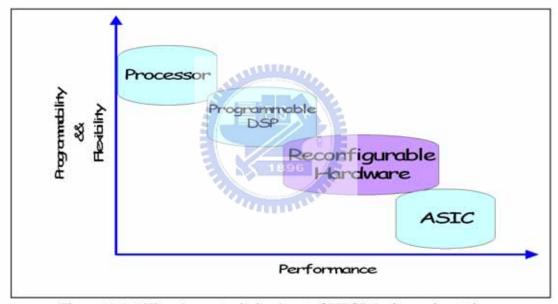

parameters with regard to Reed-Solomon codes.