# 國立交通大學

# 電機學院 IC 設計產業研發碩士班

# 碩士論文

## 應用於數位電視和 WIMAX 之低相位雜訊三角積分調變頻率合成器

مىلللارد

Low-Noise Delta-Sigma Frequency Synthesizers for DTV and WIMAX Applications

### 研究生:廖德文

指導教授:洪崇智 博士

中華民國 九十六年十二月

### 應用於數位電視和 WIMAX 之 低相位雜訊三角積分調變頻率合成器 Low-Noise Delta-Sigma Frequency Synthesizers for DTV and WIMAX Applications

| 研 究 生:廖德文 | Student : De-Wen Liao           |

|-----------|---------------------------------|

| 指導教授:洪崇智  | Advisor : Prof. Chung-Chih Hung |

# 國 立 交 通 大 學 電機學院 IC 設計產業研發碩士班 碩 士 論 文 A Thesis

Submitted to Department of College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R&D Master Program on IC Design

> December 2007 Hsinchu, Taiwan, Republic of China

中華民國九十六年十二月

### 應用於數位電視和WIMAX之

#### 低相位雜訊三角積分調變頻率合成器

學生:廖德文 指導教授:洪崇智

#### 國立交通大學電機學院產業研發碩士班

#### 摘 要

本論文提出低相位雜訊三角積分之分數型頻率合成器,兩種不同架構的分 數型頻率合成器被實現,這些電路皆應用於數位電視以及 WIMAX 行動通訊上。

在射頻系統上,頻率合成器的設計仍然是最具有挑戰性議題之一。因為它 必須要達到非常嚴格要求,例如:穩定時間(setting time)、相位雜訊、參考愧入 (reference feedthrough),又被稱作參考邊頻 (reference spur),...等。在設計 頻率合成器中,有幾個取捨(trade-off)會出現。首先,穩定時間長短主要取決於 迴路頻寬 (loop bandwidth)大小。同時因為考量迴路的穩定性,迴路頻寬會被 限制在大約 1/10 的參考頻率。接著,壓控振盪器的相位雜訊只有在小於迴路頻 寬時才會被回授的迴路所降低。最後,我們需要縮小迴路頻寬來降低參考邊頻。 為了解決這些取捨,我們設計出幾種新的架構採取電流匹配以及動態式電容取 樣,隨機充電等概念來降低參考邊頻的鎖相迴路。

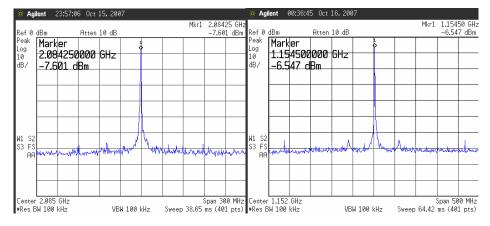

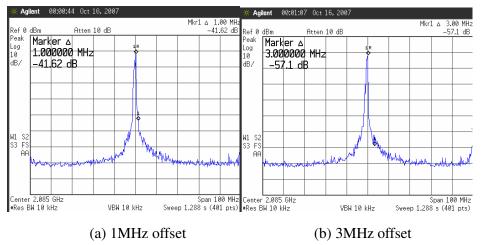

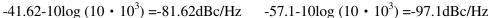

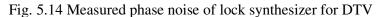

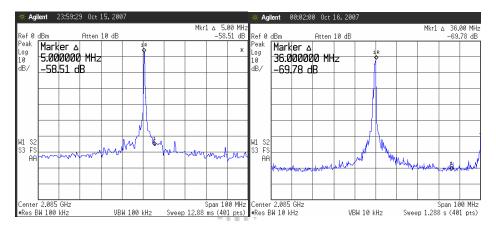

量測結果:再 DTV 系統下可調整輸出頻寬為 2110~870 兆赫茲,相位雜訊為 -81.62 分貝/赫茲 @1 赫茲,再 WIMAX 系統下可調整輸出頻寬為 2890~2100 兆赫茲,相位雜訊為-81.67 分貝/赫茲 @2.5 赫茲,寄生雜頻較主頻低 69.78 分 貝,49.49 分貝。

I

### Low-Noise Delta-Sigma Frequency Synthesizers for

### **DTV and WIMAX RF Applications**

Student : De-Wen Liao

Advisors : Dr. Chung-Chih Hung

Industrial Technology R&D Master Program of Electrical and Computer Engineering College National Chiao Tung University

# ABSTRACT

This thesis focuses on low-noise sigma-delta fractional-N synthesizers. Two fractional-N synthesizers are presented. These circuits are targeted for DTV and WIMAX applications.

Synthesizer design still remains one of the most challenge issues in RF system because it must meet very stringent requirements such as: setting time phase noise, reference feedthrough, etc. Several trade-offs exist in the synthesizer design. First, the settling time is largely determined by the loop bandwidth which is limited to approximately 1/10 of the reference frequency for the loop stability consideration. Second, the phase noise of the oscillator is reduced by the feedback loop only within the loop bandwidth. Finally, in order to suppress the reference spur, a small loop bandwidth is required. To solve all these trade-offs, we have proposed several new architectures adopting consists of current match, dynamically switched capacitors, and random charge to achieve low reference spur PLL.

The measurement results show that: the synthesizer output frequency for DTV system is tunable between 2110~870MHz, and phase noise is -81.62dBc/Hz @1-MHz offset. The output frequency for WIMAX system is tunable between 2890~2100MHz, and phase noise is -81.67dBc/Hz@2.5-MHz offset with spurious tones -69.78dBc, and -43.49dBc.

#### 誌 謝

隨著這份碩士論文的完成,兩年來在交大的求學生活也即將告一個段落,往 後迎接著我的,又是另一段嶄新的人生旅程。本論文得以順利完成,首先,要感 謝我的指導教授洪崇智老師在我兩年的研究生活中,對我的指導與照顧,並且在 研究主題上給予我寬廣的發展空間。而類比積體電路實驗室所提供完備的軟硬體 資源,讓我在短短兩年碩士班研究中,學習到如何開始設計類比積體電路,乃至 於量測電路,甚至單獨面對及思考問題的所在。此外要感謝<u>李育民</u>教授、<u>黃淑娟</u> 教授、<u>溫宏斌</u>教授撥冗擔任我的口試委員並提供寶貴意見,使得本論文更為完 整。也感謝國家晶片系統設計中心提供先進的半導體製程,讓我有機會將所設計 的電路加以實現並完成驗證。

另一方面,要感謝所有類比積體電路實驗室的成員兩年來的互相照顧與扶 持。首先,感謝博士班的學長<u>羅天佑、薛文弘、廖介偉、黃哲揚</u>以及已畢業的碩 士班學長<u>何俊達、黃琳家、蔡宗諺、林政翰、楊家泰和陳家敏</u>在研究上所給予我 的幫助與鼓勵,尤其是俊達學長,由於他平時不吝惜的賜教與量測晶片時給予的 幫助,使得我的論文研究得以順利完成。另外我要感謝<u>白逸維、林明澤、高正昇、</u> <u>邱建豪、吳國璽、黃旭佑和傳崇賢</u>等諸位同窗,透過平日與你們的切磋討論,使 我不論在課業上,或研究上都得到了不少收穫。尤其是電資710實驗室的同學們, 兩年來陪我一塊兒努力奮鬥,一起渡過同甘苦的日子,也因為你們,讓我的碩士 班生活更加多采多姿,增添許多快樂與充實的回憶。此外也感謝學弟們<u>林永洲</u>、 <u>郭智龍、夏竹緯、楊文霖,邱楓翔,黃介仁</u>的熱情支持,因為你們的加入,讓實 驗室注入一股新的活力與朝氣。

到這邊,特別要致上最深的感謝給我的父母及家人們,謝謝你們從小到大所 給予我的栽培、照顧與鼓勵,讓我得以無後顧之憂地完成學業,朝自己的理想邁 進,衷心感謝你們對我的付出。

最後,所有關心我、愛護我和曾經幫助過我的人,願我在未來的人生能有 一絲的榮耀歸予你們,謝謝你們。

> 廖德文 于 交通大學電資大樓 710 實驗室 2007.12.25

### Table of Contents

| Chapter | 1 Introduction                                                 | 1  |

|---------|----------------------------------------------------------------|----|

| 1.1     | Motivation                                                     | 1  |

| 1.2     | RF front-end overview                                          | 2  |

| 1.3     | Thesis Overview                                                | 4  |

| Chapter | 2 Fundamental of frequency synthesizers                        | 6  |

| 2.1     | Introduction to PLL                                            | 6  |

| 2.2     | General Consideration                                          | 8  |

| 2.2     | .1 Phase noise                                                 | 8  |

| 2.2     | .2 Spurs                                                       | 10 |

| 2.3     | Phase-Locked Loop (PLL) Fundamentals                           |    |

| 2.3     | .1 Phase Frequency Detector                                    | 11 |

| 2.3     | .2 Charge pump                                                 | 13 |

| 2.3     | 18 A                                                           | 15 |

| 2.3     | .4 Loop Filter                                                 | 16 |

| 2.3     | .5 Frequency Divider                                           | 19 |

| 2.4     | Noise Analysis of the PLL Synthesizer                          | 20 |

| 2.4     | .1 Input Noise Source                                          | 21 |

| 2.4     | .2 Noise of VCO                                                | 22 |

| Chapter | 3 Fractional-N PLL & Jitter and Phase noise in Ring Oscillator | 24 |

| 3.1     | The Fractional Mechanism                                       | 24 |

| 3.2     | The First Order Fractional-N Synthesizer                       | 26 |

| 3.3     | The Second Order Fractional-N Synthesizer                      |    |

| 3.4     | The Third Order Fractional-N Synthesizer                       | 29 |

| 3.4.1         | Delta-sigma modulators                                    |

|---------------|-----------------------------------------------------------|

| 3.4.2         | The Cascaded Modulator                                    |

| 3.4.3         | The Single-Loop DSM Modulator                             |

| 3.5 Oth       | er Types                                                  |

| 3.6 Exp       | pressions for Jitter and Phase noise in Ring Oscillator40 |

| 3.6.1         | Single-Ended CMOS Ring Oscillator41                       |

| 3.6.2         | Differential CMOS Ring Oscillators44                      |

| Chapter 4     | Spur-reduction Frequency Synthesizers for DTV and WIMAX   |

| applications. |                                                           |

|               | oduction                                                  |

| 4.2 Mo        | tivation47                                                |

| 4.2.1         | Tuning range                                              |

| 4.2.2         | Reference spur                                            |

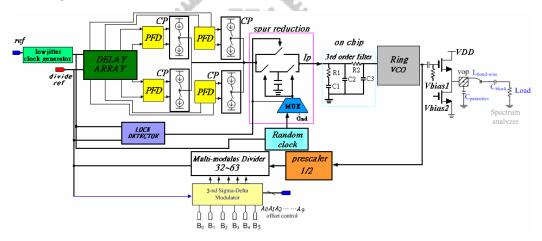

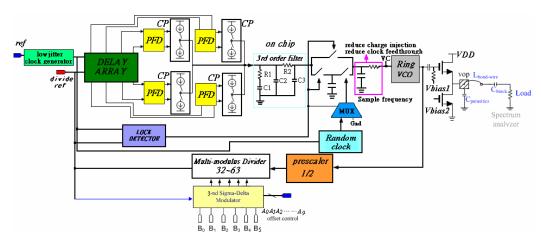

| 4.3 Pro       | posed System Architecture                                 |

| 4.3.1         | Synthesizer architecture                                  |

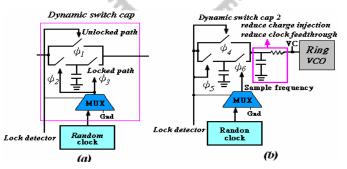

| 4.3.2         | Spur-reduction control                                    |

| 4.3.3         | Circuit analysis55                                        |

| 4.3.4         | Sampling switches                                         |

| 4.4 Bui       | lding Blocks60                                            |

| 4.4.1         | Low jitter clock generator, PFD, CP60                     |

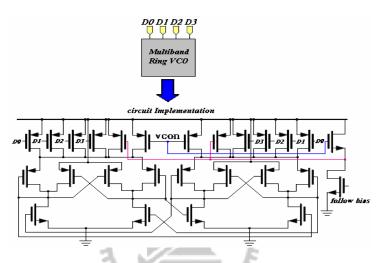

| 4.4.2         | Voltage control oscillator (Ring VCO)                     |

| 4.4.3         | Programmable Frequency Divider, Prescaler, Loop filter68  |

| 4.4.4         | Lock detector (LD), Random clock generator72              |

| 4.4.5         | Three-order Sigma-Delta Modulator74                       |

| 4.5 Fra       | ctional-N Frequency Synthesizer System78                  |

| Chapter  | 5 Experimental Results and Testing Setup |

|----------|------------------------------------------|

| 5.1      | Experimental Results                     |

| 5.2      | Test Setup                               |

| 5.3      | Measurement Results                      |

| 5.4      | Measured Summary                         |

| Chapter  | 6 Conclusions                            |

| 6.1      | Conclusions                              |

| Bibliogr | aphy90                                   |

# **List of Figures**

| Fig. 1.1 Block diagram of a general transceiver front-end                             | 3   |

|---------------------------------------------------------------------------------------|-----|

| Fig. 1.2 Double-Conversion tuners                                                     | 4   |

| Fig. 1.3 Double-Conversion system spectrums                                           | . 4 |

| Fig. 2.1 Typical frequency synthesizer architecture                                   | . 7 |

| Fig. 2.2 (a) Ideal; (b) Practical power spectrum of an oscillator                     | 8   |

| Fig. 2.3 (a) Receiver and (b) Transmitter                                             | 9   |

| Fig. 2.4 Frequency domain representation of spur                                      | 10  |

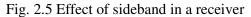

| Fig. 2.5 Effect of sideband in a receiver                                             | 10  |

| Fig. 2.6 (a) PFD block diagram (b) PFD state diagram (c) PFD timing diagram           | .11 |

| Fig. 2.7 (a) PFD implementation (b) PFD characteristic                                | .12 |

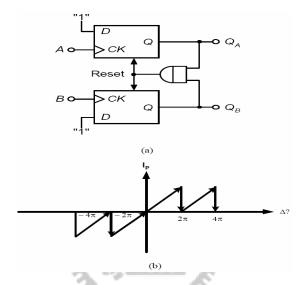

| Fig. 2.8 (a) Phase frequency detector (b) Dead zone in PFD                            | .13 |

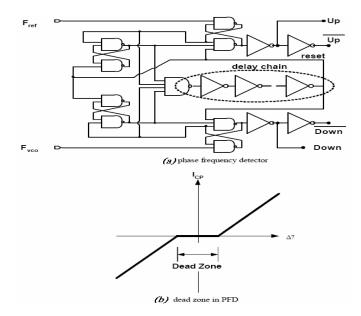

| Fig. 2.9 PFD with charge pump and the timing diagram                                  | .14 |

| Fig. 2.10 Addition of a zero to a charge pump                                         | .15 |

| Fig. 2.11 PLL-based frequency synthesizer linear model                                | 16  |

| Fig. 2.12 (a) Loop gain of simple PLL (b) addition of zero                            | 18  |

| Fig. 2.13 (a) 2 <sup>nd</sup> order loop filter (b) 3 <sup>rd</sup> order loop filter | 19  |

| Fig. 2.14 Periodic signal with jitter                                                 | 20  |

| Fig. 2.15 (a) PLL Input Phase Noise Model                                             | 21  |

| Fig. 2.15 (b) Bode plot normalized transfer function                                  | 21  |

| Fig. 2.16 (a) Noise transfer function of a PLL from VCO to output                     | .23 |

| Fig. 2.16 (b) Bode plot of the normalized transfer function                           | .23 |

| Fig. 2.17 Total output phase noise                                                    | 23  |

| Fig. 3.1 Periodic removal of a pulse from a periodic waveform                         | .24 |

| Fig. 3.2 (a) simple fractional-N synthesizer (b) use of divider in the loop           | .25 |

| Fig. 3.3 (a) Fractional-N synthesizer using a dual-modulus divider                    | .26 |

| Fig. 3.3 (b) Timing diagram                                                           | 26  |

| Fig. 3.4 Fractional-N synthesizer using a cycle swallower and an accumulator          | 27  |

| Fig. 3.5 (a) Cycle swallower circuit, (b) Its timing diagram                          | 27  |

| Fig. 3.6 Sawtooth phase error for the first order fractional-N synthesis              | 28  |

| Fig. 3.7 The analog phase interpolator                                                | 29  |

| Fig. 3.8 (a) 3-order MASH DSM (b) Its digital equivalent architecture30                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.9 A first-order DSM (a) block diagram, (b) its digital implementation32                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 3.10 Noise shaping in the first-order DSM33                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig. 3.11 The 2 <sup>nd</sup> –order MASH modulator                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fig. 3.12 The theoretical and simulated output spectrum for the MASH 1-1                                                                                                                                                                                                                                                                                                                                                                                                  |

| modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 3.13 The $2^{nd}$ -order single-loop DSM with multiple feedback coefficients37                                                                                                                                                                                                                                                                                                                                                                                       |

| Fig. 3.14 Timing diagram of a fractional-N frequency divider38                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 3.15(a) An example of fractional-N divider (b) digital phase accumulator40                                                                                                                                                                                                                                                                                                                                                                                           |

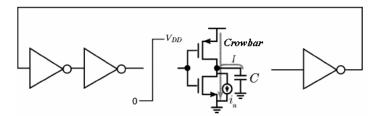

| Fig. 3.16 Capacitor and crowbar current in an inverter                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 3.17 Evolution of tail noise current45                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 3.18 The noise source in the differential buffer stage45                                                                                                                                                                                                                                                                                                                                                                                                             |

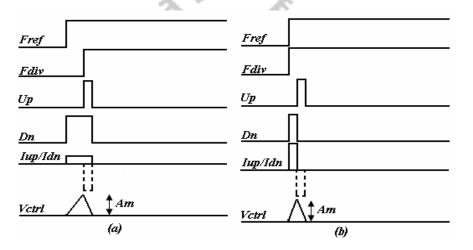

| Fig. 4.1 Spur generation concept (a) Charge pump currents mismatch (b) Up & Dn                                                                                                                                                                                                                                                                                                                                                                                            |

| signal timing mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

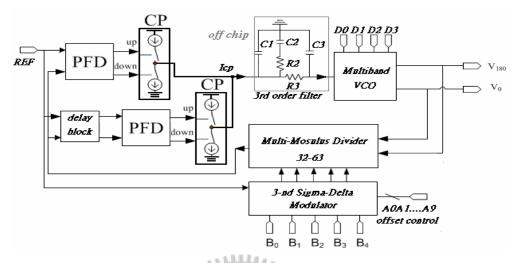

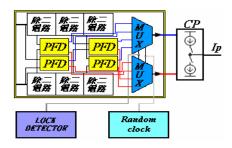

| Fig. 4.2 The architecture of DTV based on three-order $\Sigma \Delta$ modulator                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig. 4.3 The first architecture of WIMAX (mobile) based on Three-order $\Sigma\Delta$                                                                                                                                                                                                                                                                                                                                                                                     |

| modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 4.4 The second architecture of WIMAX (mobile) based on Three-order $\Sigma\Delta$                                                                                                                                                                                                                                                                                                                                                                                    |

| modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig. 4.5 The third architecture of WIMAX (mobile) based on Three-order $\Sigma \Delta$                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 4.5 The third architecture of WIMAX (mobile) based on Three-order $2\Delta$ modulator                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53                                                                                                                                                                                                                                                                                                                                                                                                           |

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53                                                                                                                                                                                                                                                                                                                                                  |

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54                                                                                                                                                                                                                                                                                                 |

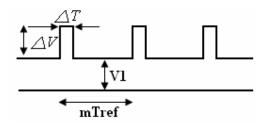

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55                                                                                                                                                                                                                                     |

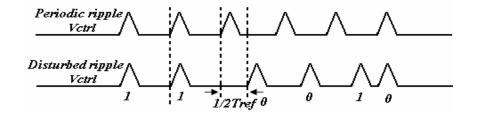

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55Fig. 4.10 Illustration of Random clock disturbance.56                                                                                                                                                                                |

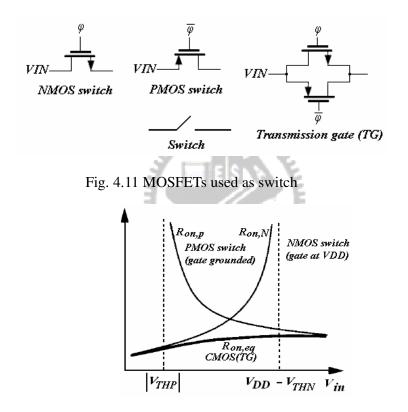

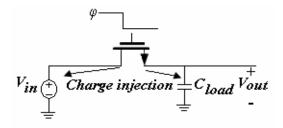

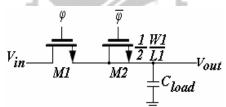

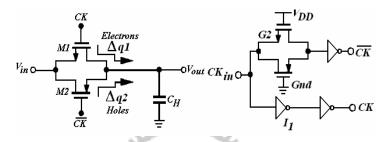

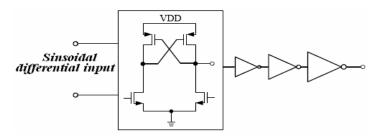

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55Fig. 4.10 Illustration of Random clock disturbance.56Fig. 4.11 MOSFETs used as switch.57                                                                                                                                             |

| modulator.52Fig. 4.6 Reduce $K_{\nu co}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55Fig. 4.10 Illustration of Random clock disturbance.56Fig. 4.11 MOSFETs used as switch.57Fig. 4.12 Small-signal on resistance of MOSFET switches.57                                                                                |

| modulator.52Fig. 4.6 Reduce $K_{\nu co}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55Fig. 4.10 Illustration of Random clock disturbance.56Fig. 4.11 MOSFETs used as switch.57Fig. 4.12 Small-signal on resistance of MOSFET switches.57Fig. 4.13 Simple configuration using an NMOS switches to how charge injection58 |

| modulator.52Fig. 4.6 Reduce $K_{vco}$ circuit implementation.53Fig. 4.7 The dynamic switch cap circuit implementation.53Fig. 4.8 Dynamic charge circuit implementation.54Fig. 4.9 Simplified model for disturbance on control line.55Fig. 4.10 Illustration of Random clock disturbance.56Fig. 4.11 MOSFETs used as switch.57Fig. 4.12 Small-signal on resistance of MOSFET switches.57Fig. 4.13 Simple configuration using an NMOS switches to how charge injection5859  |

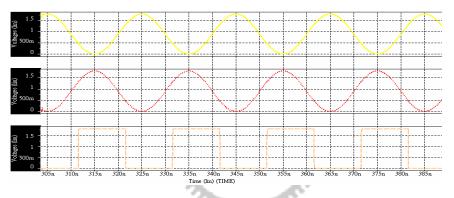

| Fig. 4.18 Low jitter clock generator simulation61                                    |

|--------------------------------------------------------------------------------------|

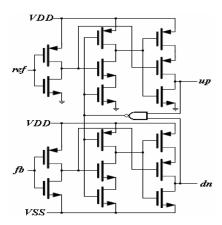

| Fig. 4.19 Phase frequency detector                                                   |

| Fig. 4.20 The time diagram of the PFD62                                              |

| Fig. 4.21 The charge pumps circuit and simulation63                                  |

| Fig. 4.22 Dead zone simulation of PFD with CP63                                      |

| Fig. 4.23 The output voltage range of charge pump64                                  |

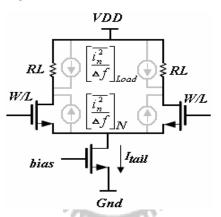

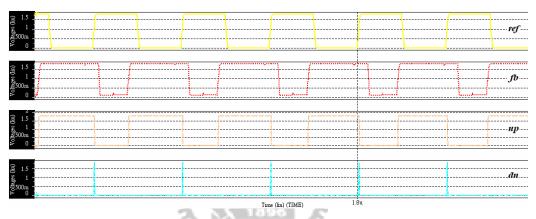

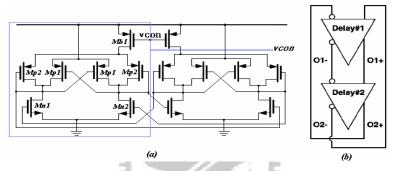

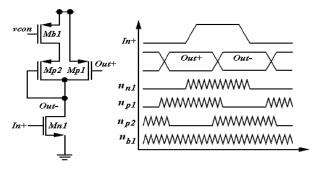

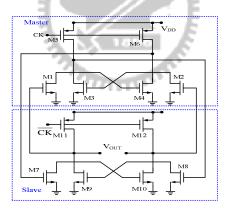

| Fig. 4.24 Circuit implementation of the propose (a) delay cell (b) ring oscillator64 |

| Fig. 4.25 Delay cell waveforms and thermal noise current65                           |

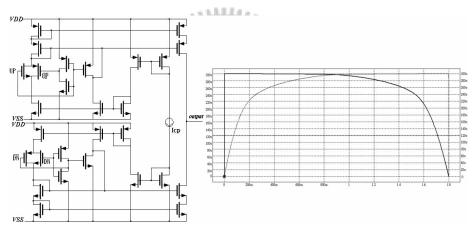

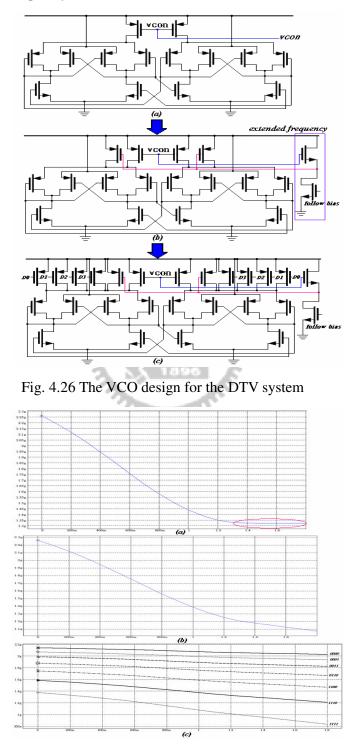

| Fig. 4.26 The VCO design for the DTV system                                          |

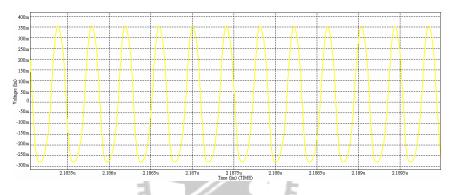

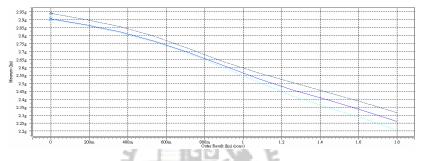

| Fig. 4.27 The VCO simulation for HSPICE                                              |

| Fig. 4.28 Phase noise of the VCO67                                                   |

| Fig. 4.29 The output swing with the PAD effect                                       |

| Fig. 4.30 The VCO tuning range (corner case: TT, FF, SS)68                           |

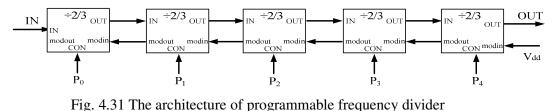

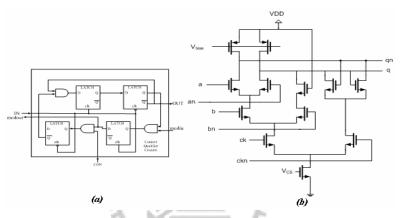

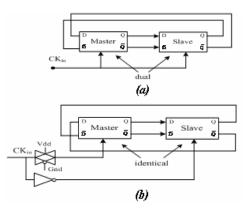

| Fig. 4.31 The architecture of programmable frequency divider                         |

| Fig. 4.32 (a)Functional blocks and logic implementation of a 2/3 divider cell (b)SCL |

| implementation of an AND gate combined with a latch function69                       |

| Fig. 4.33 Master-slave divider with (a) single clock (b) complementary clocks70      |

| Fig. 4.34 High speed, low voltage frequency divider70                                |

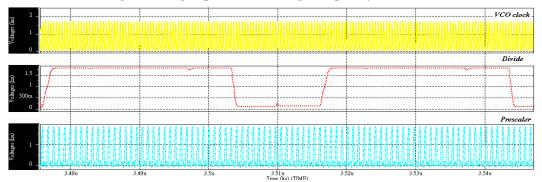

| Fig. 4.35 VCO, Prescaler and Programmable dividers simulation70                      |

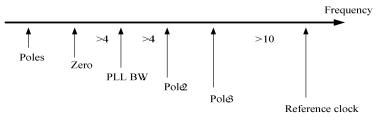

| Fig. 4.36 Relationship between zero, poles, reference and loop bandwidth71           |

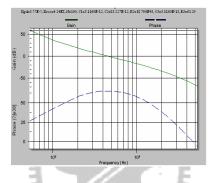

| Fig. 4.37 Bode plot of close loop PLL72                                              |

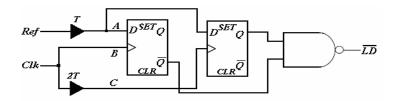

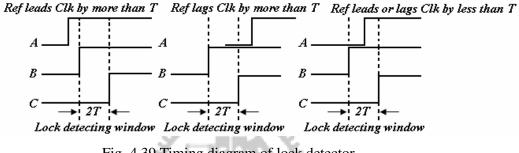

| Fig. 4.38 Lock detector                                                              |

| Fig. 4.39 Timing diagram of lock detector73                                          |

| Fig. 4.40 Timing diagram of Random clock generator73                                 |

| Fig. 4.41 Random clock generator simulation74                                        |

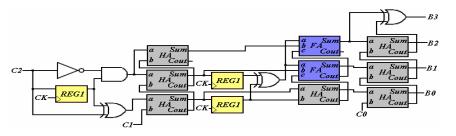

| Fig. 4.42 Pipelined $3^{rd}$ -order $\Sigma\Delta$ modulator                         |

| Fig. 4.43 Noise cancellation network of MASH 1-1-1 DSM75                             |

| Fig. 4.44 Realization of the noise cancellation network77                            |

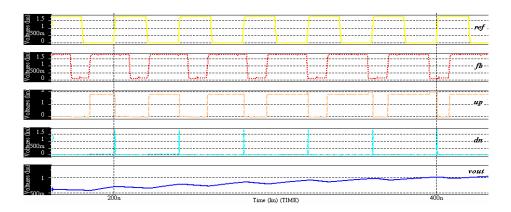

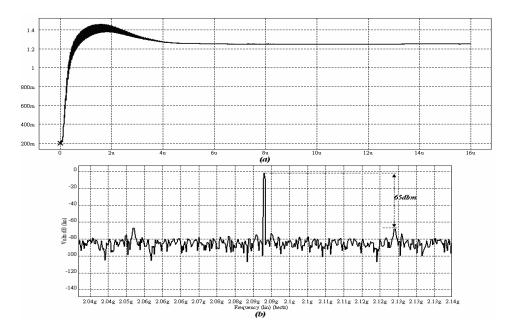

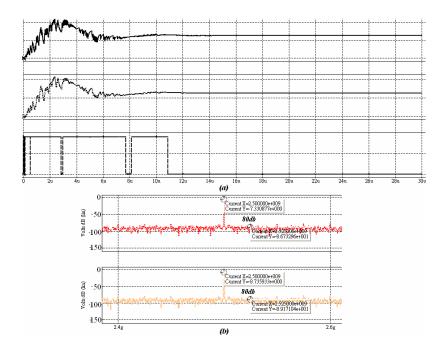

| Fig. 4.45 (a) VCO control voltage and (b) Out Spectrum when LO is 2.088GH78          |

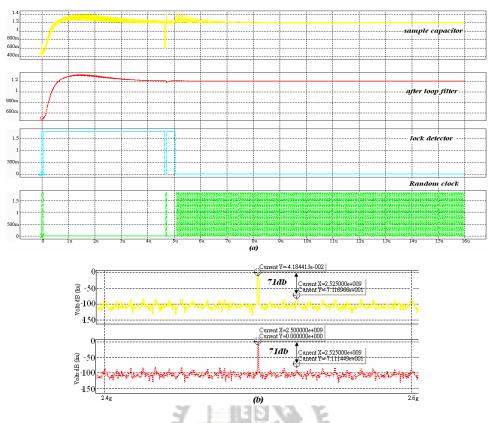

| Fig. 4.46 (a) VCO control voltage, sample capacitor, lock detector and random clock  |

| (b) Out Spectrum is 2.5GHz                                                           |

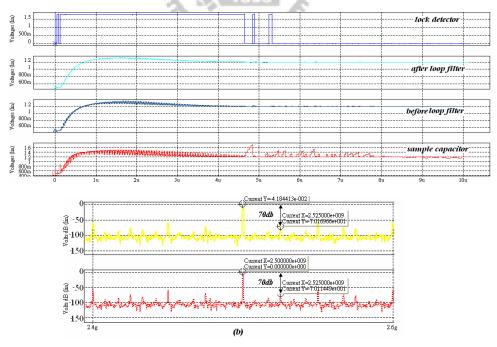

| Fig. 4.47 (a) VCO control voltage, sample capacitor, lock detector and random clock  |

| (b) Out Spectrum is 2.5GHz                                                           |

| Fig. 4.48 (a) VCO control voltage and lock detector (b) Out Spectrum is 2.5GHz | 80  |

|--------------------------------------------------------------------------------|-----|

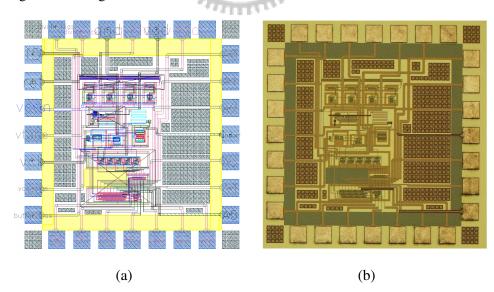

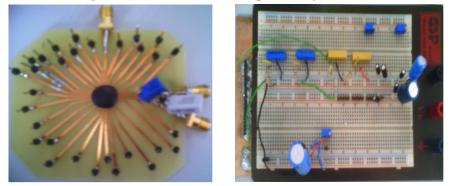

| Fig. 5.1 (a) Layout (b) Die photo                                              | .81 |

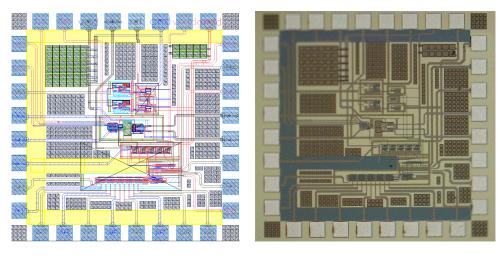

| Fig. 5.2 (a) Layout (b) Die photo                                              | 82  |

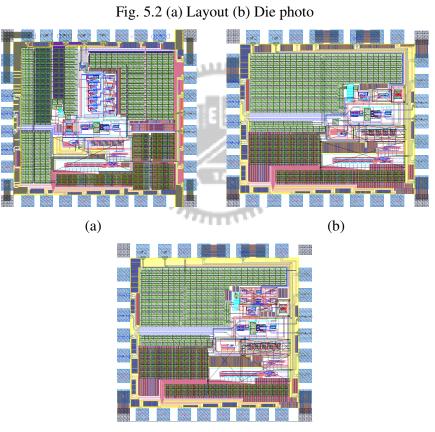

| Fig. 5.3 (a) Layout1 (b) Layout2 (c) Layout3                                   | 82  |

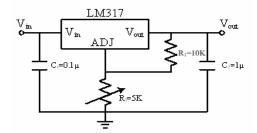

| Fig. 5.4 LM317 regulator                                                       | 83  |

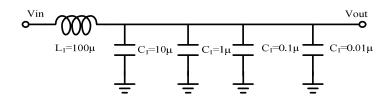

| Fig. 5.5 Bypass filter at the regulator output                                 | .84 |

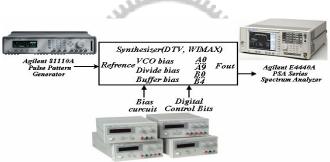

| Fig. 5.6 Measurement setup of the synthesizer                                  | 84  |

| Fig. 5.7 The testing PCB in the synthesizer                                    | 84  |

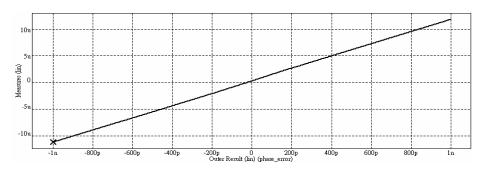

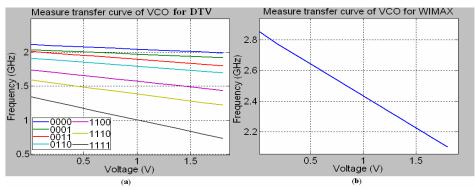

| Fig. 5.8 Measure VCO transfer curve                                            | 85  |

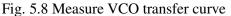

| Fig. 5.9 Measured output spectrum of WIMAX (mobile) synthesizer                | 85  |

| Fig. 5.10 Measured phase noise of lock synthesizer for WIMAX                   | 85  |

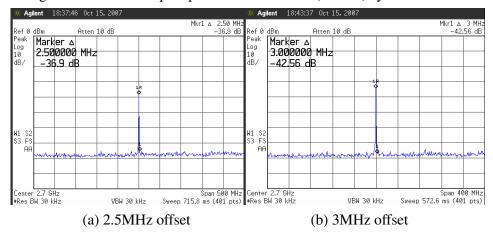

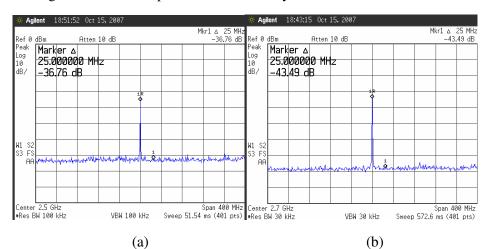

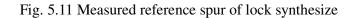

| Fig. 5.11 Measured reference spur of lock synthesize                           | 86  |

| Fig. 5.12 Measured output spectrum of divide in lock 2.5GHz                    | 86  |

| Fig. 5.13Measured output spectrum of DTV synthesize                            | 86  |

| Fig. 5.14 Measured phase noise of lock synthesizer for DTV                     | 87  |

| Fig. 5.15 Measured phase noise and reference spur of lock synthesizer for DTV  | 87  |

# **List of Tables**

| TABLE 4-1 Process corners simulation (DTV)          | 67 |

|-----------------------------------------------------|----|

| TABLE 4-2 Process corners simulation (DTV)          | 68 |

| TABLE 4-3 Process corners simulation (WIMAX mobile) | 68 |

| TABLE 4-4 Noise cancellation Network coding (A)     | 75 |

| TABLE 4-5 Noise cancellation Network coding (B)     | 76 |

| TABLE 4-6 Noise cancellation Network coding (C)     | 76 |

| TABLE 4-7 Noise cancellation Network coding (D)     | 77 |

| TABLE 4-8 Noise cancellation Network coding (E)     | 77 |

| TABLE 4-9 Fractional-N PLL performance summaries    | 80 |

| TABLE 5-1 Measure synthesizer performance summary   | 88 |

|                                                     |    |

### Introduction

#### **1.1 Motivation**

The system for fixed and portable reception of digital terrestrial television, known as digital television video (DTV), has been available for several years. Many countries such as America, Europe, Japan, have already advertised relative transmission standard and rules of application [1]-[4]. At the same time, Taiwan has also started the transition from analog to digital television.

By the rapid development and large demand of wireless communication, fully integrated monolithic radio transceivers are the most significant considerations for communication applications. The recent rapid growth of the wireless communication market inspires many people to research the concerned region with strong passion. Of such a many developments, enhanced operating frequency of CMOS technology encourages the designer to implement single-chip RF-to-baseband systems. One of the important design goals of portable wireless system is low power consumption for long battery life. CMOS technology satisfies the requirements of low power consumption, low cost, reduced size, and also a few GHz operating frequency in wireless systems.

Frequency synthesizer is an important topic of the RF front-end. As an example, for a direct-conversion receives to demodulate RF signal received from antenna, the

RF front-end amplified the signal by a low noise amplifier (LNA) first. And then the entire spectrum, both the wanted and unwanted signals, is translated to baseband by a mixer. In this step, a local oscillator (LO) is needed to down convert the RF signal. The oscillators used in RF transceivers are usually embedded in a synthesizer to achieve a precise definition of output phase and frequency. Synthesizer design still remains one of the most challenge issues in RF system because it must meet very stringent requirements such as: setting time phase noise, reference feedthrough (also called reference spur), etc. Several trade-offs exist in the design synthesizer. First, the settling time is largely determined by the loop bandwidth which is limited to approximately 1/10 of the reference frequency for the loop stability considerations. Second, the phase noise of the oscillator is reduced by the feedback loop only within the loop bandwidth. Finally, in order to suppress the reference spur, a small loop bandwidth is required. To solve all these trade-offs, we have proposed several new architectures adopting the current match . dynamic switch cap and random charge concept to achieve low reference spur PLL which their characteristics are introduced in chapter3 and 4.

#### 1.2 RF front-end overview

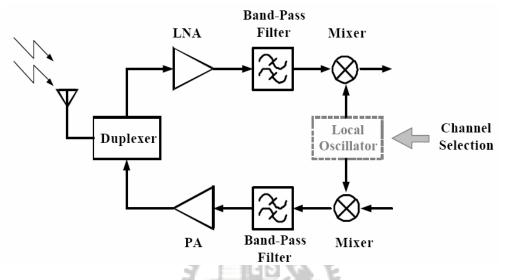

In typical RF front-end circuits, frequency synthesizer actions as a local oscillator (LO) for up/down conversion in communication transceivers. Fig. 1-1 shows a general block diagram of a transceiver. It contains a low-noise amplifier (LNA), a power amplifier (PA), mixers, and band-pass filters. In order not to distort the received signals, the excellent noise performance of frequency synthesizer is required. Besides, the switch time of circuit is also significant. The design of phase-locked loops (PLLs) must generally deal with a tight trade-off between the

setting time and the amplitude of the ripple on the oscillator control line. In conclusion, we can judge a synthesizer by following three parameters: phase noise, sideband interface (spurious tones), and locking time. Based on the above reason, we realize two sigma-delta fractional-N type synthesizers.

Fig. 1.1 Block diagram of a general transceiver front-end

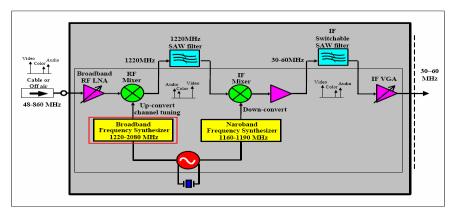

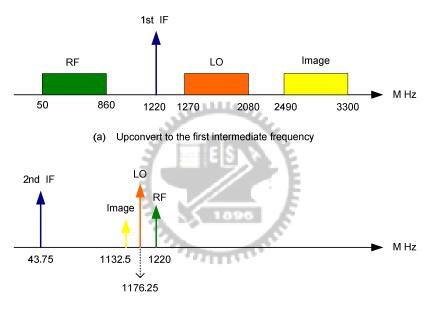

For the sake of reducing the demand for tracking filter, more and more tuners are designed by Double Conversion structure, composed of frequency synthesizers, mixers, and low noise amplifiers, as shown in Fig. 1.2. The first local oscillator (LO) is synthesized by a PLL and controlled by a microprocessor. The second LO is a fixed reference oscillator. This type of tuner converts the entire input band of 50-860MHz up to a fixed first intermediate frequency (IF), that is above the highest input frequency of interest, and selects the desired channel by the RF saw filter. This process rejects the image of the downconversion. Then, the selected channel is down converted to the second intermediate center at 43.75MHz and passes through the second IF saw filter. Finally, the output signal feeds the next stage to demodulate DTV (WIMAX) signal. The detailed spectrum is shown in Fig. 1.3.

Fig. 1.2 Double-Conversion tuners

(b) Downconvert to the second intermediate frequency

Fig. 1.3 Double-Conversion system spectrums

#### **1.3 Thesis Overview**

Chapter 2 will give basic ideas of phase-locked loops (PLLs) as well as some important characteristics in a frequency synthesizer. A design flow is described along with detailed parameter setting and architecture together with some examples is demonstrated.

Chapter 3 will present frequency synthesizer which is Fractional N synthesizer. At first we will discuss the motivation including several design issues, such as: jitter and Phase noise in Ring VCO Then, analysis and implementation of circuit are introduced in detail.

In chapter 4, A spur-reduction architecture will be proposed to further improve the spur reduction function. At first we will discuss the motivation including several design issues and several building block, such as: phase noise, reference spur .....Then, analysis and implementation of our circuit are introduced in detail.

In chapter 5 also; the experimental results will be presented in the end of this chapter.

Finally, chapter 6 will conclusion to this work is given. Suggestions for future works are recommended at the ending of this thesis.

## **Fundamental of frequency synthesizers**

#### **2.1 Introduction to PLL**

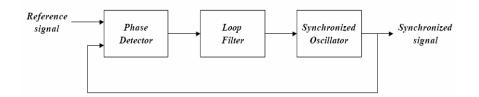

In general, the charge pump PLL contains five major building blocks which are phase/frequency detector charge pump, loop filter, voltage-controlled oscillator, and divide. By varying the dividing ratio of the divider, the PLL can synthesizer an output frequency which is a multiple of the input clock. Since the loop characteristics would be influenced by the dividing ratio, we need consider the loop stability carefully when we design the loop parameters. Fig 2.1 shows the topology of a typical frequency synthesizer. The oscillator generates a waveform whose fundamental oscillation frequency is controlled by the input voltage. When a divider is used, this oscillation frequency is divided by an integer number N. THE Phase of the resulting waveform is compared with a reference clock in a phase/frequency divider. Both up and down signals are generated to indicated which direction should the oscillation frequency be corrected. The error signal is low-passed filtered and finally fed a control voltage to the oscillator. The frequency division ratio N adjustable, several oscillation frequencies can be synthesized. Under condition of lock, two inputs of the phase detector have a constant phase relationship and thus equal frequency.

Fig. 2.1 Typical frequency synthesizer architecture The main applications of PLL are as follows:

1. Clock recovery: Some data streams, especially high-speed serial data streams, (such as the raw stream of data from the magnetic head of a disk drive) are sent without an accompanying clock. The receiver generates a clock from an approximate frequency reference, and then phase-aligns to the transitions in the data stream with a PLL. In order for this scheme to work, the data stream must have a transition frequently enough to correct any drift in the PLL's oscillator. Typically, some sort of redundant encoding is used; 8B10B is very common.

**2. Deskewing**: If a clock is sent in parallel with data, that clock can be used to sample the data. Because the clock must be received and amplified before it can drive the flip-flops which sample the data, there will be a finite, and process-, temperature-, and voltage-dependent delay between the detected clock edge and the received data window. This delay limits the frequency at which data can be sent. One way of eliminating this delay is to include a de-skew PLL on the receive side, so that the clock at each data flip-flop is phase-matched to the received clock.

**3.** Clock generation: Most electronic systems include processors of various sorts that operate at hundreds of megahertz. Typically, the clocks supplied to these processors come from clock generator PLLs, which multiply a lower-frequency reference clock (usually 50 or 100 MHz) up to the operating frequency of the processor. The multiplication factor can be quite large in cases where the operating frequency is multiple gigahertzes and the reference crystal is just tens or hundreds of

megahertz.

**4. Spread spectrum**: All electronic systems emit some unwanted radio frequency energy. Various regulatory agencies (such as the FCC in the United States) put limits on this emitted energy and any interference caused by it. The emitted noise generally appears at sharp spectral peaks (usually at the operating frequency of the device, and a few harmonics). A system designer can use a spread-spectrum PLL to reduce interference with high-Q receivers by spreading the energy over a larger portion of the spectrum. For example, by changing the operating frequency up and down by a small amount (about 1%), a device running at hundreds of megahertz can spread its interference evenly over a few megahertz of spectrum, which drastically reduces the amount of noise seen by FM receivers which have a bandwidth of tens of kilohertz.

#### 2.2 General Consideration

In additional to frequency accuracy and channel selection, two other aspects also influence the performance of a transceiver front-end: phase noise, and spurs.

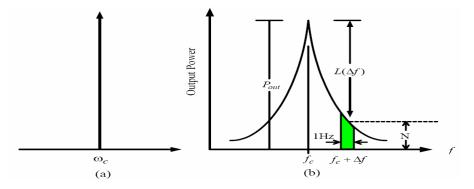

Fig. 2.2 (a) Ideal; (b) Practical power spectrum of an oscillator

#### 2.2.1 Phase Noise

Ideally, the output of the frequency synthesizer should be pure tones as shown in Fig. 2.2(a). However, due to the thermal noise of the resistors and transistors in the oscillator or some noise at the frequency tuning input of the oscillator, the phase of the oscillation will fluctuate. In frequency domain, the phase fluctuation forms a skirt of noise power around the carrier impulse as shown in Fig. 2.2(b). In order to quantify the phase noise, the noise power per unit bandwidth at an offset frequency  $(\triangle w)$  with respect to the carrier frequency  $(w_c)$  is compared with the carrier power, and this quantity is expressed in the unit of dBc/Hz. If the noise source is white, the phase noise in the frequency domain is proportional to  $1/\triangle f^2$ .

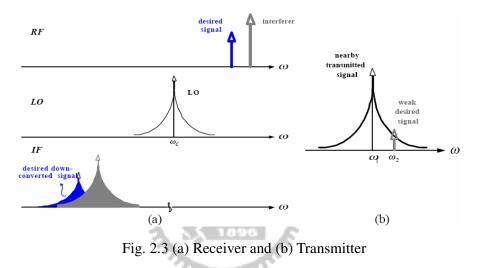

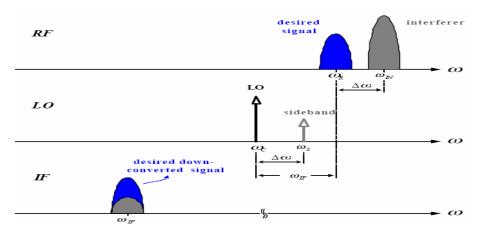

The effects of the phase noise in both the receiver and transmitter are shown in Fig. 2.3, which shows the receiver path. If there is a large interference signal near the small desired signal, both the desired signal and interference will be mixed down to the IF. In the mixing both signals will also have the same noise skirt as that of the impure LO signal because the down-conversions is actually a convolution in the frequency domain. Since the power of the interfering signal is generally large, the noise down-converted to the frequency of the desired signal can significantly degrade the signal-to-noise ratio (SNR) of the desired signals. The effect is called "reciprocal mixing." However, the effect in the transmit path is shown in Fig.2.3(b), where larger-power transmitted signals with substantial phase noise can

corrupt weak nearby signals. Therefore, the output spectrum of the LO must be

extremely sharp, and set of stringent phase-noise requirements must be satisfied in the wireless communication system.

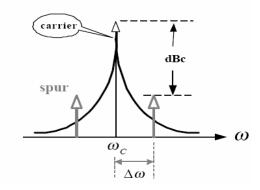

Fig. 2.4 Frequency domain representation of spur

#### 2.2.2 Spurs

Other than the phase noise due to the internal thermal noise and external noise, the oscillator can also be modulated by some noise of fixed frequency due to the switching of other circuits in the synthesizer. One of the main noise sources is the switching noise of the charge pump at the reference frequency. The input noise modulate the control voltage and hence the output frequency of the VCO. Two to will appear at the upper and lower sideband of the carrier as shown in Fig.2.4. The tones are called reference spurs and measured by the difference between the power the carrier and the spurs at some frequency offset ( $\triangle$ w) in the units of dBc.

Similar to the case of phase noise, as shown in Fig. 2.5, if there is a interference signal appearing at the frequency which reference spur also exist the desired signal and the interference will be mixed down to the IF, as degrade SNR of the desired one. In a zero-IF system, the down-converted interferer generation the dc offset and thus still affects the system SNR.

#### 2.3 Phase-Locked Loop (PLL) Fundamentals

When designing a PLL-based frequency synthesizer, it is very important to understand the behaviors of each functional block as well as the overall closed-loop behavior. The following discussion focuses on charge-pump PLLs, which is the most popular type of PLLs nowadays and is adopted in our work.

#### 2.3.1 Phase Frequency Detector (PFD)

Phase frequency can detector both phase and frequency difference between the reference signal and the output signal of the frequency divider. As shown in Fig. 2-6, if the frequency of A is greater than the frequency of B, then  $Q_A$  is high, but  $Q_B$  is still low. If the frequency of A and B are equal, then the circuit will check the phase difference between the two inputs, and generates a pulse equal to the phase difference at  $Q_A$  or  $Q_B$  (depends on which input has phase leading).

Fig. 2.6 (a) PFD block diagram (b) PFD state diagram (c) PFD timing diagram

Fig. 2-7(a), it shows a possible implementation of the above PFD. This circuit contains two reset table D-flip flops and a NAND gate. The input signals of A and B are as clock input and the input of two D-flip flops is always high. And we set the initial condition is  $Q_A=Q_B=0$ . If A is from 0 to 1, until B is from 0 to 1 and QB becomes high to make the two D-flip flops reset. And Fig. 2-7(b), shows the input-output characteristic of the PFD.

Fig. 2.7 (a) PFD implementation (b) PFD characteristic

Fig. 2-8(a) shows the PFD circuit. It is negative-trigger and has the same function as we discuss above. But it still has a drawback. When this type of PFD incorporated with charge pump circuit, it has a drawback that a dead zone exist, as shown in Fig. 2-8(b). If the reset signal is not delayed sufficiently, the output of charge pump will not change for small phase error, thus the dead zone translates to jitter in PLL and must be voided. In Fig. 2-8(a), the delay chain to increase delay of reset signal for eliminating dead zone.

Fig. 2.8 (a) Phase frequency detector (b) Dead zone in PFD

متللتي

#### 2.3.2 Charge pump

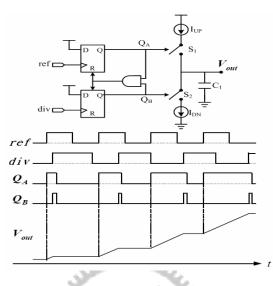

A PFD could not alone provide the exact voltage (or current) signal proportional to the phase difference at its inputs. A charge pump serves to convert the two digital output signals  $Q_A$  and  $Q_B$  of the PFD into charge flows whose quantity is proportional to the phase error. A passive filter then shape the output current signal of the charge pumps to suppress the useless messages buried in that signal.

A PFD together with a charge pump and a single capacitor  $C_1$  as the loop filter are shown in Figure 2.9, with the corresponding time-domain response shown as well. As a higher frequency than B or has the same frequency as B but with a leading phase, the charge pump sources a constant-valued current I<sub>1</sub> through switch  $S_1$  into the capacitor, and the output voltage increases steadily. Similarly, if the frequency of input A is lower or the phase is lagging, the output waveform will be a steadily downward one. What happens if the inputs are exactly the same? Careful examination shows that  $Q_A$  and  $Q_B$  will have pulses of short duration. In this case, if the currents of the two current sources are the same in quantity, as indicated in Figure 2.10, at the time that both  $S_1$  and  $S_2$  are on, the current sourced by  $I_1$  is exactly sunk by  $I_2$ . Thus no net current will flow through  $C_1$  and  $V_{out}$  remains unchanged as in the case when both  $S_1$  and  $S_2$  are off.

Fig. 2.9 PFD with charge pump and the timing diagram

The phase frequency detector and the charge pump can be together characterized as:

$$I_{pump} = I \frac{\phi_e}{2\pi}$$

(2.1)

Where  $I_{PUMP}$  is the output current of the charge pump,  $\phi_e = \phi_A \cdot \phi_B$  represents the phase error between the two PFD inputs and I=I1-I2 is the current value of the two current sources in the charge pump. This representation, however, is an approximate one. One should note that the charge pump is a discrete-time system, and it provides good approximation only when the loop bandwidth is much less than the input reference frequency.

The single-capacitor loop filter nevertheless has an infinite dc gain, which might unstablilize the close loop. To avoid instability, a resistor  $R_P$  in series with CP is added, which in effect adds a LHP (left-half-plane) zero to the overall open-loop transfer function. The transfer function of the resolution loop filter is:

$$F(s) = R_{P} + \frac{1}{sC_{P}}$$

(2.2)

Note that this representation indicates a conversion from an input current a output voltage, and thus is directly applicable in conjunction with Equation. (2.1).

Fig. 2.10 Addition of a zero to a charge pump

#### 2.3.3 Voltage-Controlled Oscillator

Many applications need that the oscillators be "tunable". The most popular circuit is the voltage-controlled oscillator, whose frequency is a linear function of its input control voltage. The transfer function is as follows:

$$\omega_{out} = \omega_0 + K_{VCO} V_{cont}$$

(2.3)

Here  $\omega_0$  is the free running frequency,  $K_{vco}$  is gain or sensitivity of the VCO, (usually in rad/s/V). Next, we want to derive the phase transfer function:

$$\int \omega_{out} = \omega_0 t + K_{VCO} \int V_{cont} dt \qquad (2.4)$$

Only the second term of the total phase is of interest. We call  $K_{VCO} \int_0^t V_{cont} dt$  as the "excess phase", denoted by  $\phi_{ex}$ . In fact, in the analysis of PLLs, we respect the VCO as a system whose input as the control voltage and output as the excess phase. If the system is LTI, then we get:

$$\phi_{ex} = K_{VCO} \int V_{cont} dt \qquad (2.5)$$

$$\frac{\phi_{ex}}{V_{cont}} = \frac{K_{VCO}}{s}$$

(2.6)

Therefore the VCO acts as an ideal integrator, providing a pole at s = 0 in the open loop transfer function in the PLL.

#### 2.3.4 Loop Filter

Fig. 2.11 PLL-based frequency synthesizer linear model

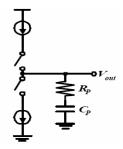

However, before further examining the loop filter, linear models of the PLL-based frequency synthesizer should be established. With proper characteristic of each function block, the close-loop behavior of frequency synthesizers can be analyzed. A linear model of a charge-pump PLL-based frequency synthesizer is shown in Fig. 2.11. Note that the input and output signals are phase (rad/s). Phase error  $\phi_e$  , the difference between the input phase  $\phi_{\rm in}$  and the feedback  $\phi_{\rm fb}$  , is extracted by the PFD, which is represented by a simple PLL in the linear model. The charge pumps (CP) then translate  $\phi_e$  into a current signal with a gain of  $I_P/2\pi$ , where  $I_P$  is the pump current. This current signal (A) flows into the passive filter  $(\Omega)$ , and is converted to voltage signal (V) at the control input of the VCO. The VCO generates an output signal whose frequency is related to the control input voltage with a gain of  $K_{VCO}$  (Hz/V). Since the phase signal rather than frequency signal is the variable in this linear model, the VCO block include a "1/s" term that integrates the frequency signal to derive the phase signal. The frequency divider in the feedback path is still a sample "1/ M" factor since division in frequency domain has the same effect in phase domain. Hence, the open-loop transfer function can be represented as:

$$G(s) = \frac{I_{P}}{2\pi} \cdot F(s) \cdot \frac{2\pi K_{VCO}}{s} \cdot \frac{1}{M}$$

(2.7)

$$G(s) = \frac{I_P \cdot K_{VCO}(1 + s \cdot R_P C_P)}{s^2 \cdot M \cdot C_P} = \frac{I_P \cdot K_{VCO} \cdot R_P}{M} \cdot \frac{s + w_z}{s^2}$$

$$(2.8)$$

$$where w_z = \frac{1}{R_P C_P}$$

The loop bandwidth K, defined as the unity gain frequency of the open-loop transfer function, can be found assuming that K is much greater than  $w_{z:}$

$$G(s) = \frac{I_P \cdot K_V C O \cdot R_P}{M} \cdot \frac{s + w_z}{s^2} \approx \frac{I_P \cdot K_V C O \cdot R_P}{M} \cdot \frac{1}{s} = 1$$

$$\Rightarrow K \approx \frac{I_P \cdot K_V C O \cdot R_P}{M}$$

(2.9)

Thus the open-loop transfer function can be rewritten as:

$$G(s) = K \cdot \frac{s + w_z}{s^2}$$

(2.10)

The simplest LPF is to connect a capacitor to the control voltage. The open-loop transfer function is derived as follows:

$$\frac{V_{out}}{\Delta \phi}(s) = \frac{I_p}{2 \pi C_p} \frac{1}{s}$$

(2.11)

$$\frac{\phi_{out}}{\phi_{out}}(s)\Big|_{open} = \frac{I_p}{2\pi C_p} \frac{K_{vco}}{s^2}$$

(2.12)

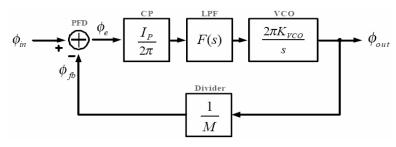

Since the loop gain has two poles at the origin, this topology is called a "type II" PLL. It is unstable because the loop gain has two poles at the origin. As illustrated in Fig. 2.12(a), each integrator provides constant 90° phase shift. Thus the system will oscillate at the unit-gain frequency. So, we have to add a zero to increase phase margin.

We can thus add a resistor in series with the original capacitor. The open-loop transfer function is derived as follows:

$$\frac{V_{out}}{\Delta \phi}(s) = \frac{I_p}{2\pi} \left( R_p + \frac{1}{sC_p} \right)$$

(2.13)

$$\frac{\phi_{out}}{\phi_{out}}(s)\Big|_{open} = \frac{I_p}{2\pi} \left(R_p + \frac{1}{sC_p}\right) \frac{K_{vco}}{s}$$

(2.14)

As shown in Fig. 2.12(b), the phase margin will increase because of the zero  $1/(R_pC_p)$  and the system will not oscillate at the unit-gain frequency. However, a severe problem occurred in such PLLs. Due to the resistor in series with capacitor, each time a current is injected into the loop filter and then produces large voltage jump. It makes ripples of control voltage of VCO and degrades the purity of the output frequency spectrum.

Fig. 2.12 (a) Loop gain of simple PLL (b) addition of zero

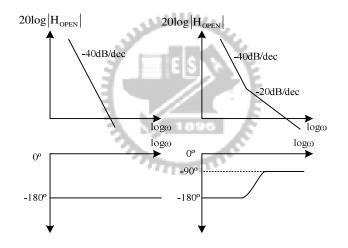

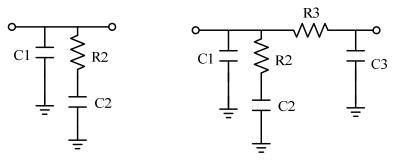

We can ease this effect by adding a second capacitor in parallel with  $R_p$  and  $C_p$ . The loop filter is now of 2<sup>nd</sup> order and the open loop transfer function of PLL now is of third-order and has stability problem, as shown in Fig. 2.13 (a). But if we make  $C_2$  is about one-fifth to one-tenth of  $C_p$ , the open-loop transfer function is near the second-order and would be stable.

$$F(s) = K_{h} \frac{s + w_{2}}{s\left(\frac{s}{w_{1}} + 1\right)}$$

(2.15)

where

$$K_{h} = \frac{C_{P}R_{p}}{C_{P} + C_{2}}$$

, and  $\omega_{2} = \frac{1}{C_{P}R_{p}}, \omega_{1} = \frac{C_{2} + C_{P}}{C_{2}C_{P}R_{p}}$

Moreover, current switching in the charge pump at the reference frequency  $f_{ref}$  would cause unwanted sidebands at the frequency spectrum of VCO. We can add additional LPF to suppress the spur that is  $f_{ref}$  offset from the carrier frequency, as shown in Fig. 2.13 (b). The loop filter transfer function is

$$F(s) = K_{h} \frac{s + w_{2}}{s\left(\frac{s}{w_{1}} + 1\right)\left(\frac{s}{w_{3}} + 1\right)}$$

(2.16)

where

$$K_{h} = \frac{C_{2}R_{2}}{C_{1} + C_{2}}$$

, and  $\omega_{2} = \frac{1}{C_{2}R_{2}}$ ,  $\omega_{1} = \frac{C_{1} + C_{2}}{C_{1}C_{2}R_{2}}$

$\omega_{3} = \frac{1}{C_{3}R_{3}}$

The additional pole must be lower than the reference frequency in order to significantly attenuate the spurs. However, it must be at least five times higher than the loop bandwidth, or the loop will almost assuredly become unstable.

Fig. 2.13 (a) 2<sup>nd</sup> order loop filter (b) 3<sup>rd</sup> order loop filter

#### 2.3.5 Frequency Divider

Frequency dividers are used to synthesize a high frequency LO from a precise low frequency crystal oscillator. The output frequency  $f_{div}$  equals the input frequency  $f_{in}$  divided by an integer number. From this information we could derive a model for the divider in the phase domain.

The phase  $\theta_{in}$  of the input signal is given by

$$\boldsymbol{\theta}_{in}(t) = 2\pi f_{in}t + \boldsymbol{\theta}_p \sin 2\pi f_m t \qquad (2.17)$$

And the instantaneous frequency of the input signal is:

$$f_{inst}(t) = \frac{1}{2\pi} \frac{d\theta_{in}(t)}{dt} = f_{in} + \theta_p f_m \cos 2\pi f_m t \qquad (2.18)$$

$$f_{div} = \frac{f_{inst}}{N} = \frac{f_{in}}{N} + \frac{\theta_p f_m \cos 2\pi f_m t}{N}$$

(2.19)

And the phase of the output signal can now be found as:

$$\theta_{div}(t) = \int 2\pi f_{div}(t) dt$$

=  $2\pi \frac{f_{in}}{N}t + \frac{\theta_p}{N}\sin 2\pi f_m t = \frac{\theta_{in}(t)}{N}$  (2.20)

### 2.4 Noise Analysis of the PLL Synthesizer

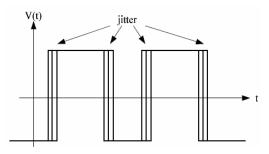

The job of any frequency synthesizer is to generate a spectrally pure output signal. An ideal periodic output in the frequency domain has only an impulse at the fundamental frequency and perhaps some other impulse energy at DC and harmonic. In the actual oscillator implementation, the zero crossings of the periodic wave vary with time as shown in Fig. 2.14. This varying of the zero crossings is known as time domain jitter.

Fig. 2.14 Periodic signal with jitter

A PLL-based frequency synthesizer suffers from introduced at input or

generate by the other building blocks. It is important to learn how different noise sources affect the noise performance of the output signal. The sources of noise may be classified into two types: (1) the noise at input, and (2) the noise of VCO.

#### 2.4.1 Input Noise Source

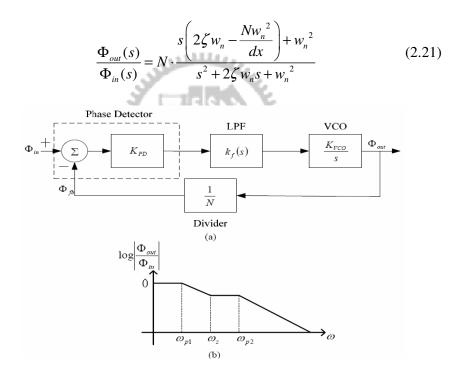

An input reference signal with phase noise can be modeled in the PLL as shown in Fig. 2.15(a) [5].

The input noise,  $\Phi_{in}$ , is treated as an input signal and the same PLL transfer function for the input noise transfer function. The input phase noise transfer function is plotted in Fig. 2.15(b).

Fig. 2.15 (a) PLL Input Phase Noise Model (b) Bode plot normalized transfer function

The input phase is shaped by the low-pass characteristic of the second-order PLL. In order to reduce the phase noise in the output signal due to the input phase noise it is desired to make the PLL bandwidth as narrow as possible. Notice that the input noise is amplifier by a factor of N. If input noise is a concern, the lowest possible value of N should be used. Usually in frequency synthesizer design the

input phase noise is not a concern because the reference signal generally comes from a low phase noise crystal oscillator.

#### 2.4.2 Noise of VCO

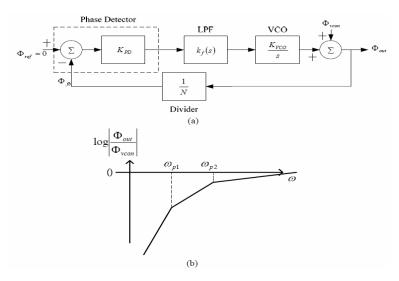

The phase noise of the VCO can be modeled as Fig. 2.16(a) [5]. The VCO phase noise,  $V_{CON}$ , is treated as an input signal and following transfer function is plotted in Fig. 2.16(b).

$$\frac{\Phi_{out}(s)}{\Phi_{vcon}(s)} = \frac{s^2 + \frac{s W_n^2 N}{K_{PD} K_{VCO}}}{s^2 + 2\xi \cdot \omega_n s + \omega_n^2}$$

(2.22)

The VCO phase noise is shaped by a high-pass characteristic by the second-order PLL. In order to reduce the phase noise in the output signal due to the VCO phase noise it is desirable to make the PLL bandwidth as wide as possible. Here a tradeoff regarding loop bandwidth position and its effect on input phase noise contribution and VCO phase noise contribution is observed. The optimum loop bandwidth depends on the application. It is optimal to have a narrow loop bandwidth for input noise performance.

Narrow band loops aid in the cases where the PLL is operating with a noisy reference signal. It is optimal to have a wide loop bandwidth for VCO noise performance. Usually the dominant source of noise is the VCO in fully integrated frequency synthesizer design [6].

The VCO phase noise is caused by such things as the upconverted *1/f* noise from the transistor used to design the VCO, noise in the control path, and cycle-to cycle fluctuations in the power supply[7][8]. With the VCO contributing significant phase noise it is optimal to make the loop bandwidth as wide as possible.

Fig. 2.16 (a) Noise transfer function of a PLL from VCO to output (b) Bode plot of the normalized transfer function

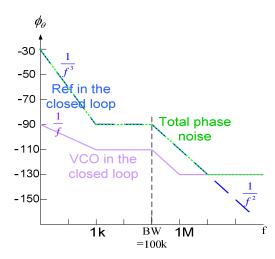

The total phase noise can be derived by adding the above two eventual phase noises, as shown in Fig. 2.17. It is obviously that when the frequencies nears carrier, the REF in the closed loop dominate the total phase noise. Otherwise, the VCO dominates. If we want to suppress the phase noise of REF, we can decrease the BW. However, it will raise the phase noise of VCO. On the contrary, increasing the BW will suppress the phase noise of VCO but raise the phase noise of Ref. It is a trade off. How we decide the best BW is important.

Fig. 2.17 Total output phase noise

## **Fractional-N PLL**

## 3.1 The Fractional Mechanism

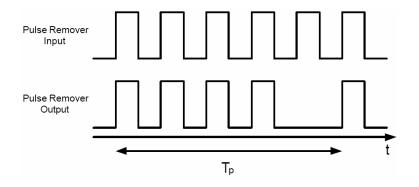

Before studying the fractional architecture, we make an observation. Suppose, as shown in Fig. 3.1, a pulse is removed every  $T_P$  seconds from a periodic signal x(t) that has a frequency fl. The resulting waveform, y(t) then exhibits  $fl \cdot T_P$ -1 pulses every  $T_P$  seconds, i.e., y(t) has an "average" frequency equal to fl-1/ $T_P$ . This method can be used to vary the average frequency of a signal by small steps. We should note, however, that f(t) is not a strictly periodic signal. The idea of removing pulses nevertheless useful in fine-step frequency synthesis.

Fig. 3.1 Periodic removal of a pulse from a periodic waveform

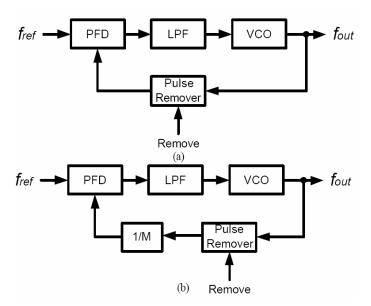

Fig. 3.2(a) shows simple fractional-N architecture. In addition to the PFD, LPF, and VCO, the loop incorporates a pulse remover, a circuit that blocks one input pulse upon assertion of the remove command. Since under locked condition the two

frequencies presented to the phase detector must be equal, the average output frequency of the pulse remover equals  $f_{ref}$ , and hence  $f_{out}=f_{ref}+1/\text{TP}$ , where T<sub>P</sub> is the periodic with which the remove command is applied. Note that  $f_{out}$  can vary by a fraction of  $f_{ref}$  because the frequency  $f_p=1/\text{T}_P$  can be derived from  $f_{ref}$  by simply division. Provided by a crystal oscillator,  $f_{ref}$  is typical limited to a few tents of megahertz. Thus, as shown in Fig. 3.2(b), a fractional-N synthesizer incorporates a divider in the feedback to generate high output frequencies.

Fig. 3.2 (a) simple fractional-N synthesizer (b) use of divider in the loop

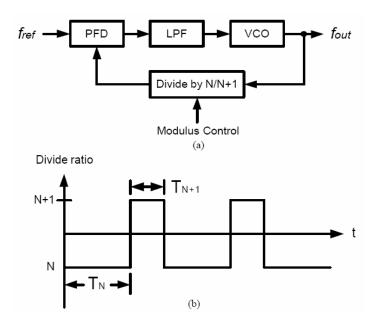

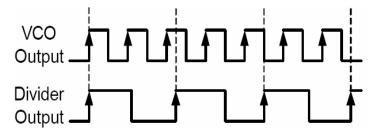

While the original fractional-N topology was based on the pulse remover concept [9], modern implementations of this architecture operate on a somewhat different principle. Depicted in Fig. 3.3, such a synthesizer replaces the pulse remover and the divider of Fig. 3.2 (b) with a dual-modulus prescaler. If the prescaler divides by N for  $T_N$  output pulses (of the VCO) and by N+1 for  $T_{N+1}$ output pulses, shown in Fig. 3.3 (b), then the equivalent divide ratio is shown as

$$\begin{split} f_{vco,avg} &= \frac{1}{(T_N + T_{N+1})} \bigg[ T_N \cdot N \cdot f_{ref} + T_{N+1} \cdot (N+1) \cdot f_{ref} \bigg] \\ &= \bigg[ N + T_{N+1} / (T_N + T_{N+1}) \bigg] \cdot f_{ref} \\ &= (N \cdot f) \cdot f_{ref} \end{split} \tag{3.1}$$

This value can vary between N and N+1 in fine steps by proper choice of A and B. The resulting modulus is sometimes written as N.f, where the dot denotes a decimal point and N and f represent the integer and fractional parts of the modulus.

Fig. 3.3 (a) Fractional-N synthesizer using a dual-modulus divider,

(b)Timing diagram

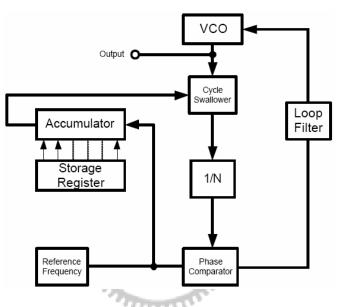

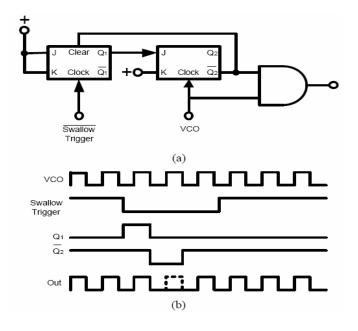

## 3.2 The First Order Fractional-N Synthesizer

Fig. 3.4 shows the fractional-N PLL [10] which the accumulator and the cycle swallower become part of the circuit. The operation principle of this structure is the same as the one described in Fig. 3.3(b). Fig. 3.5 shows the detail circuits and timing diagram of the cycle swallower. To operate, a chain of VCO pulses serves as the clock for the flip-flop. A swallow trigger signal is illustrated generally as being asynchronous with the VCO pulses. However, flip-flop will trigger on the negative

edge of swallow trigger and output a  $Q_1$  pulse to flip-flop. When the next negative edge of VCO signal appears at the clock of flip-flop, the  $Q_2$  output goes negative. This output resets flip-flop and also provides an "off" input to AND gate. Thus, the next VCO pulse will not appear at the output of AND gate; that is, has been swallowed. The negative edge of pulse again triggers flip-flop allowing the subsequent pulses of the VCO signal to pass through AND gate.

Fig. 3.4 Fractional-N synthesizer using a cycle swallower and an accumulator

Fig. 3.5 (a) Cycle swallower circuit, (b) Its timing diagram

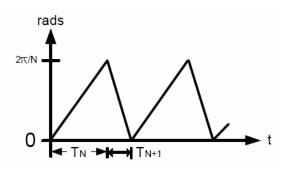

From Fig. 3.3(b), this periodic modification of the divider modulus gives rise to a sawtooth phase error (Fig. 3.6). If unfiltered, the phase error causes severe spurious tones-fractional spurs at all multiples of the offset frequency ( $.f \times f_{ref}$ ).

Fig. 3.6 Sawtooth phase error for the first order fractional-N synthesis

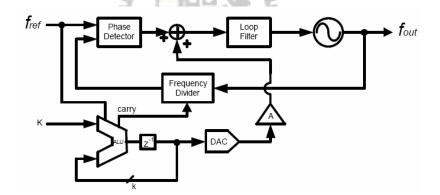

## 3.3 The Second Order Fractional-N Synthesizer

The fractional spurs in the above-mentioned averaging fractional-N synthesis are a serious problem. An important can be achieved by analog compensation of the phase error [11, 12, 13]. The output of the phase register of the digital accumulator is a measure for the phase error. The phase register is a kind of "bookkeeping system" that tracks the phase advancement of the VCO for every reference cycle. Due to the loop integration the actual phase detector output becomes an analog sawtooth waveform which is mentioned in Fig.3.7.Using a DAC (Digital-to-Analog) the staircase output of the phase register can be converted to an analog sawtooth current, scaled by A (Fig. 3.7) to match the phase error. By summing the phase detector output and the DAC output on the loop filter capacitors, the AC component is in the ideal case removed from the phase error. The VCO output is now only driven by the wanted DC phase error, canceling all fractional spurs in the output spectrum.

However, this method has several disadvantages. First of all, the maximum

amplitude of the phase error depends on  $f_{ref}$ , such that the DAC output amplitude must be variable, while its input is constant. Secondly, the sampling frequency of the DAC can be rather high. To have fast setting (large loop bandwidth), the  $f_{ref}$  can easily be some tens of MHz. The sampling frequency of the DAC must be at least  $2 \times f_{ref}$ , for a full Nyquist DAC, to be able to compensate spurs up to the reference frequency. To have a spurious suppression of at least -70dB, required in most telecommunication system, the accuracy of the DAC must be around 8 bits [14]. This occupies a larger chip area and dissipates the power consumption. Thirdly, due to matching issues, the accuracy of the cancellation is limited, requiring external adjustment and calibration. Therefore, the analog compensation method is not a viable solution for all integration of frequency synthesizers for wireless communication systems in CMOS technology.

Fig. 3.7 The analog phase interpolator

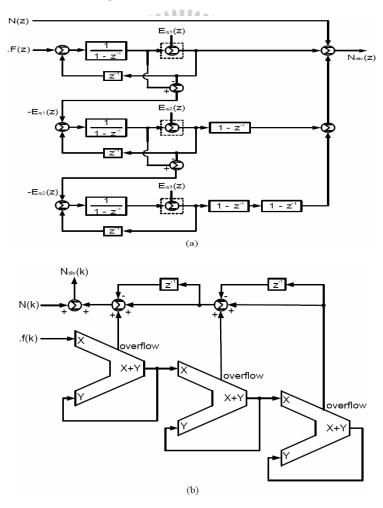

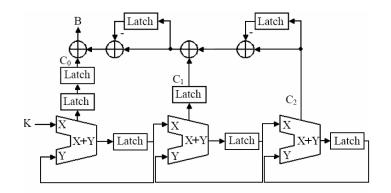

## 3.4 The Third Order Fractional-N Synthesizer

The next significant evolutionary step for fractional-N synthesizer will be an all-digital implementation, known as *delta-sigma modulator (DSM)*, eliminating spurious digitally and allow good phase noise performance by digitally noise-shaping techniques, as shown in Fig. 3.8 [15]. The DSM architecture used in this paper terms as a Multistage Noise Shaping (MASH) which is cascaded by three

first-order modulator to ensure the stability. It is assumed random to model each 1-bit quantizes as a unity gain element with added quantization noise. N.F is the desired rational divide ratio and  $N_{div}$  (k) is the actual sequence presented to the integer divider. The transfer function is

$$Ndiv(z) = N_f(z) + (1 - z^{-1})^3 \times E_{q3}(z)$$

(3.2)

In a locked PLL,

$$f_{out} = N_{div} \times f_{ref}$$

$$F_{out}(z) = N_{.}F(z) \times f_{ref} + E_{q3}(z)(1 - z^{-1})^{3} \times f_{ref}$$

(3.3)

Where the first term is the desired frequency and the second term represents frequency noise due to delta-sigma modulation.

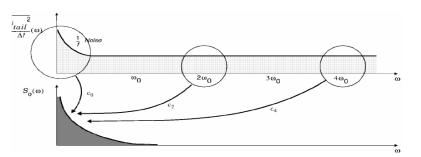

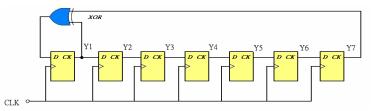

Fig. 3.8 (a) 3-order MASH DSM (b) Its digital equivalent architecture

By converting to the frequency domain and generating to any number of modulators, the power spectral (PSD) which is considered with small offset ranges compared to the reference frequency is [15].

$$S_E(f) \approx \frac{(2\pi)^2}{12f_{ref}} \left[ \frac{2\pi f}{f_{ref}} \right]^{2(m-1)} rad^2 / Hz$$

(3.4)

The system in Fig. 3.8 can be simplified when it is recognized that an accumulator is a compact realization of the delta-sigma modulator as shown in Fig. 3.8 (b). This architecture leads to the all digital implementation easily. Regardless of the advantages of low phase noise, low reference feedthrough spurs, fast tuning speed, and small step size for this architecture, fractional spurs is a design issue to overcome. In addition, when the DSM is fed with a DC input, the quantized signal bounces between two levels and may be periodic. The structure of such quantization is known as pattern noise, or idle tones. Since this is the desired architecture for the fractional-N synthesizer in this thesis, we will consider this problem and figure out how to solve these problems?

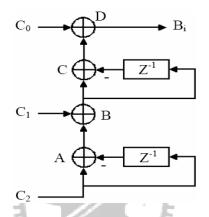

### 3.4.1 Delta-sigma modulators

DSMs are basically divided into two types: *single-stage* and *cascaded*. Digital DSMs, unlike their analog counterparts, don't have any non-idealities, and when the modulator is stable, there is no overload problem. Cascaded digital modulators won't suffer from mismatches and noise leakage from front stages, and multi-bit quantizer won't suffer from any nonlinearity, which doesn't exit digital modulator at all.

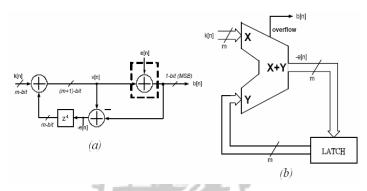

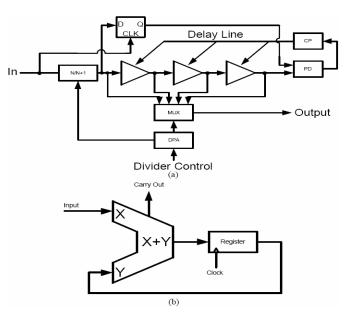

To understand the function of the DSM, one should know the building block: the first-order DSM or the accumulator. A block diagram of the first-order DSM with the error-feedback topology is shown in Fig. 3.9(a), where the quantizer is modeled as an additive white noise source e[n]. The signal-flow graph for this modulator in its digital implementations is illustrated in Fig. 3.9(b), where the m-bit input signal K[n] is summed with the m-bit register content to produce the (m+1)-bit quantizer input signal v[n]. The 1-bit quantization process is accomplished by simply taking the most significant bit (MSB) of v[n]. The residual m-bit signal, which represents the negative of the quantization error signal, is then stored in the m-bit register to be summed with the input signal at the next clock cycle. The accumulator overflow and the accumulator result correspond to the 1-bit quantizer output and the negative of the quantization error at any time, respectively.

Fig. 3.9: A first-order DSM (a) block diagram, (b) its digital implementation The transfer function of the first-order DSM is

$$B(z) = K(z) + (1 - z^{-1})E(z)$$

(3.5)

Thus the power spectral density is

$$S_B(f) = S_K(f) + \left[2\sin\left(\frac{\pi f}{f_s}\right)\right]^2 S_E(f)$$

(3.6)

Where  $f_s$  is the sampling frequency or the reference frequency,  $f_{ref}$ , for the synthesizer. Note that 1-bit quantizer is assumed to have uniform quantization error and the power is spread over a bandwidth of  $f_{ref}$ . Consequently, the power spectral density (PSD) of quantization error is 1/ (12  $f_{ref}$ ). Note that the second term of Eq. 3.7 is the PSD introduced by the quantization noise. Generally, where m is the order of the DSM.

$$S_{f}(f) = \frac{1}{12f_{ref}} \left[ 2\sin\left(\frac{\pi f}{f_{ref}}\right) \right]^{2m}$$

(3.7)

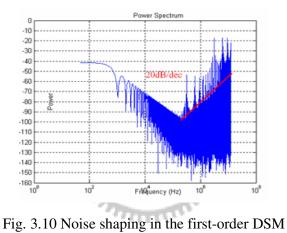

To illustrate the noise shaping action of the DSM, one can apply a sinusoid with amplitude A, frequency  $f_o$  to the DSM input. Fig. 3.2 shows the PSD of the first-order DSM. The high frequency band shows the 20dB/dec noise shaping. Note that there exists many spurs around the signal which will effect the noise requirement targeted in many wireless system. Thus, the first DSM is not suitable to the fractional-N synthesis.

$2^{nd}$  and 3-order DSMs are practically used for fractional-N synthesizers.  $4^{th}$  or even higher order modulators are rarely used because it's difficult to suppress the phase noise at higher frequencies by limited order of loop filter. We will study the second-order cascaded and single-loop DSM in the next two sections.

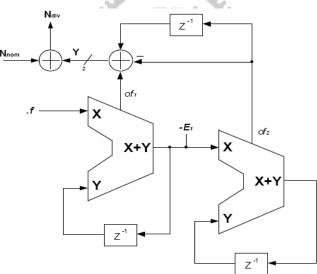

### 3.4.2 The Cascaded Modulator

The cascaded 1-1 or MASH (multi-stage noise-shaping) DSM modulator is shown in Fig. 3.11. The MASH modulator consists of a cascaded of first-order modulators, whose quantization error  $-E_i$  is the input to the next modulator. By summing the filtered versions of the first-order outputs, the quantization error of the first modulator is cancelled. Since the DSM modulator in fractional-N PLLs is an all digital implementation, the cancellation is perfect. The output of the modulator with perfect cancellation is:

$$Y = .f + (1 - z^{-1})E_1 + \left[-E_1 + (1 - z^{-1})E_2\right] (1 - z^{-1})$$

= .f + (1 - z^{-1})^2 E\_2 (3.8)

Thus,

$$N_{div} = N_{.}f + (1 - z^{-1})^{2} E_{2}$$

(3.9)

The equations expose the most important quality of a MASH modulator, i.e. its unconditional stability for any modulator order, because of its first order nature. Another advantage is the integration of the MASH modulator in plain CMOS technology, since only adders and register are needed to implement the noise shaping function.

Fig. 3.11 The 2<sup>nd</sup> –order MASH modulator

In the implementation of Fig. 3.11, the output is a 2-bit word with a mean value, fractional number *.f.* With  $N_{norm}$  added, the nominal frequency could be tuned for the purpose of targeted frequency band. Note that to increase the output dynamic range of the modulator to accommodate more division moduli, multiple MSBs can be taken as outputs of the first-order modulators instead of the single bit output, *of<sub>1</sub>*[16].

To obtain the theoretical PSD in the locked PLL, using Eq. (3.10)

$$F_{out}(z) = N \cdot f(z) f_{ref} + (1 - z^{-1}) f_{ref} E_2(z)$$

(3.10)

Applying the PSD of  $E_2=1/(12f_{ref})$  and knowing that the second term of Eq. (3.11) is the frequency fluctuations of  $F_{out}(z)$ ,

$$S_{fE}(z) = \left| (1 - z^{-1})^2 f_{ref} \right|^2 (1/12 f_{ref})$$

=  $\left| 1 - z^{-1} \right|^4 (f_{ref}/12)$  (3.11)

We want phase fluctuations, not frequency fluctuation.

$$\phi(t) = \int w(t) dt = 2\pi \int f_E dt$$

(3.12)

Employing a simple rectangular integration to represent  $\int dt$  in the z-domain,

$$\Phi(z) = \frac{T_s w(z)}{1 - z^{-1}} = \frac{2 \pi T_s F_E(z)}{1 - z^{-1}}$$

(3.13)

Where  $T_s = 1/f_{ref}$  is the sample period. With Eq. (3.12) and Eq. (3.13), we obtain

$$S_{\Phi}(z) = \frac{(2\pi)^{2}}{\left|1 - z^{-1}\right|^{2} f_{ref}^{2}} \cdot \frac{\left|1 - z^{-1}\right|^{4} f_{ref}}{12}$$

$$= \frac{(2\pi)^{2}}{12 f_{ref}} \left|1 - z^{-1}\right|^{2} rad^{2} / Hz$$

(3.14)

Converting to the frequency domain and generalizing to any number of modulator sections,

$$S_{E}(f) = \frac{(2\pi)^{2}}{12f_{ref}} \left[ 2\sin\left(\frac{\pi f}{f_{ref}}\right) \right]^{2(m-1)} rad^{2} / Hz \qquad (3.15)$$

We can simplify the above expression by taking advantage of the assumption that the offset range is small compared to the reference frequency.

$$S_{E}(f) \approx \frac{(2\pi)^{2}}{12f_{ref}} \left[ \frac{2\pi f}{f_{ref}} \right]^{2(m-1)} rad^{2} / Hz$$

(3.16)

Note that this is the derivation of Eq. (3.4).

In the frequency domain, the intensive use of modulus dynamic range translates

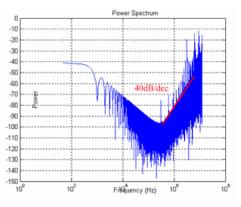

in substantial levels of high frequency. This is reflected in the noise transfer function (NTF) of the MASH modulator, which is  $(1-z^{-1})^2$  (see Eq. (3.10)). Fig. 3.12 shows the simulated output spectrum for this MASH 1-1 modulator. Compared to the Eq. (3.8), it provides the 40Db per decade for high frequency noise shaping.

Fig. 3.12 The theoretical and simulated output spectrum for the MASH 1-1

#### modulator

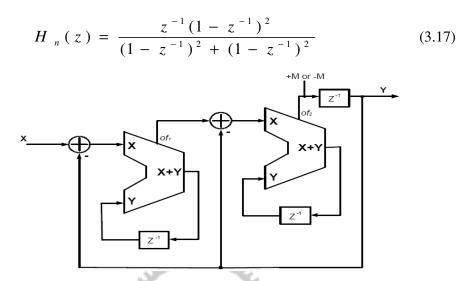

## 3.4.3 The Single-Loop DSM Modulator