### 國立交通大學

電子工程學系 電子研究所碩士班

### 碩士論文

利用高介電長數 HfA10 之元素含量做為阻擋層 應用在非揮發性記憶體上之研究

Study on High-k Gate dielectric Hf<sub>1-x</sub>Al<sub>x</sub>O for Blocking layer of SONOS Non-Volatile Memory

# 研究生:顧春瑀

指導教授: 雷添福 博士

中華民國 九十七年八月

# 利用高介電長數 HfAlO 之元素含量做為阻擋層應用在非揮發性記憶體上之研究

### Study on High-k Gate dieletric Hf<sub>1-x</sub>Al<sub>x</sub>O for Blocking layer

### of SONOS Non-Volatile Memory

College of Electrical Engineering & Computer Science

**National Chiao Tung University**

In Partial Fulfillment of the Requirements

For the Degree of

**Master of Science**

in

Electronic Engineering August 2008 Hsinchu, Taiwan, Republic of China

中華民國九十七年八月

利用高介電長數 HfA10 之元素含量做為阻擋層

### 應用在非揮發性記憶體上之研究

學生:顧春瑀 指導教授:雷添福 博士

#### 國立交通大學

工程學

所碩士班

研究

在本論文的第二章中,我們討論不同成分的 Hf1-xA1x0 在經過不同溫度的退火 處理所產生的變化。我們利用有系統的方法來萃取我們所需要的最好的條件。我 們期望在記憶體在寫入與抹除操作時扮演重要的角色,而沒有過大的漏電流存 在。

摘要

在本論文的第三章中,我們提出一個利用高介電係數 HfA10 還有氧化鋁作為 阻擋層的 SONOS 非揮發性記憶體。雖然氧化鋁一直是一個做為阻擋層的很好的材 料,但是由於他的 k 值不夠高,所以寫入以及抹除的速度不是非常明顯的快速。 所以我們增加一些 Hf 的材質進入氧化鋁裡面,以期望能提高 k 值。從上面的第 二章的一些資料中,我們萃取出最好的條件做為我們的阻擋層。並且測量記憶體 的電性,將 HfA10 以及氧化鋁互相比較。

# Study on High-k Gate dieletric Hf<sub>1-x</sub>Al<sub>x</sub>O for Blocking layer of SONOS Non-Volatile Memory

Student: Bobby Ku Advisor: Dr. Tan-Fu Lei

Department of Electronics Engineering &

### Institute of Electronics

National Chiao Tung University

ABSTRACT

In chapter 2, we discuss the dependence of different Hf<sub>1\*</sub>Al<sub>\*</sub>O component dielectric on the different annealing temperatures. We used a systematic methodology to extract the best result for our blocking layer of SONOS-type memories. We expect the high-k blocking layer can play a key role in program/erase speed without large leakage current.

In chapter 3, we purpose the SONOS-type nonvolatile memory with high-k HfA10 and A1<sub>2</sub>O<sub>3</sub> blocking layer. Although A1<sub>2</sub>O<sub>3</sub> is a good material for blocking layer of SONOS memory, the program/erase speed is not obvious faster attributed to the k is not high enough. So we add the Hf into A1<sub>2</sub>O<sub>3</sub> for our blocking layer in order to increase the k. From the data in chapter 2, we use the best condition for our blocking layer. We also measure the memory characteristic to compare A1<sub>2</sub>O<sub>3</sub> and HfA10.

### 致謝

首先要向我的指導教授雷添福老師致上最大的謝意,因為在老師的關心指導 還有尊尊教誨下,我的論文才得以完成。由於老師採取信任的態度,讓學生自由 的發揮創意做實驗,在報告進度時提供了寶貴的意見,讓我這兩天過得非常充 實,學到許多實用的東西。

再來,我想謝謝鄭兆欽學長跟楊紹明學長,在我一開始進入研究所的時候他 們非常照顧我,也帶我做實驗。另外,我最感謝的是張家文學長,在我實驗進度 落後的時候拉我一把,並且還指導我很多東西,讓我能夠順利的畢業;還有黃博, 在我遇到問題的時候他都盡量幫我解決。也要謝謝一起做實驗的李旭恆、正妹 凱、show、土豆、簡嘉宏還有張嘉文!!沒有他們的大力幫助我的進度可能落後 又落後了;還要大力的感謝正愷兄,在我最後口試以及量測上提供寶貴的建議。 也要謝謝實驗室其他的學長:搞笑的小P學長、很忙的羅大學長,還有冠良,都 在最後的時候提供我一些口試的意見;也祝福你們實驗順利。還有一些已經畢業 的學長:志仰、伯儀、余博、哲倫,很感謝你們辛苦的照顧我。

另外,也要謝謝 samo 哥、砲政哥哥、洋A、猛男、綺哥、小黛哥、沈佑書、 黃義涵、暴走以及翁啓祥在修課的時候給了我很大的幫助,還要感謝宣凱、效喻、 弘森、欣哲以及孝瑜幫我做 ALD,還有可愛的乾妹雨蓁以及曉萱都幫我很多。

最後,我要感謝我母親,這幾年辛苦她了,還有我姊姊,這段時間沒有他們 的全力支持,我是不會走到這一步的;最後最後,也謝謝這段時間陪我的筱君, 在我最艱苦的時候陪伴我走過!!!謝謝你們。

III

| Abstract (Chinese)                                               | I    |

|------------------------------------------------------------------|------|

| Abstract (English)                                               | II   |

| Acknowledge                                                      | III  |

| Contents                                                         | IV   |

| Table & Figure Captions                                          | VI   |

| Chapter 1 Introduction                                           | 1    |

| 1-1 Overview of Flash Memory                                     | 1    |

| 1-2 Motivation                                                   | 4    |

|                                                                  | 6    |

| Chapter 2 Physical and Electrical properties of MIS Capacitors U | sing |

| MOCVD Hf <sub>1-x</sub> Al <sub>x</sub> O Dieletrics             | 11   |

|                                                                  | 11   |

| 2-2 Experimental.                                                | 13   |

| 2-3 Results and Discussion                                       |      |

| 2-3-1 C-V Characteristics                                        | 14   |

| 2-3-2 I-V Characteristics                                        |      |

| 2-3-3 CET Characteristics                                        |      |

# Contents

| 2-4 Summary                                                                 | 16 |

|-----------------------------------------------------------------------------|----|

| Chapter 3 Characteristics of SONOS-type Memory with High-<br>Blocking Layer |    |

| 3-1 Introduction                                                            | 32 |

| 3-2 Experimental                                                            |    |

| 3-3 Results and Discussion                                                  |    |

| 3-3-1 Ig-Vg curves and Memory Window                                        | 34 |

| 3-3-2 Program and Erase Speed                                               | 35 |

| 3-3-3 Data Retention Characteristic                                         |    |

| 3-3-4 Disturbance Measurement                                               | 36 |

| 3-4 Summary                                                                 | 37 |

|                                                                             | 56 |

| Reference 1896                                                              | 58 |

| Chapter 1                                                                   | 58 |

| Chapter 2                                                                   | 63 |

| Chapter 3                                                                   | 65 |

# **Figure Captions**

| Chapter 1                                                                               |

|-----------------------------------------------------------------------------------------|

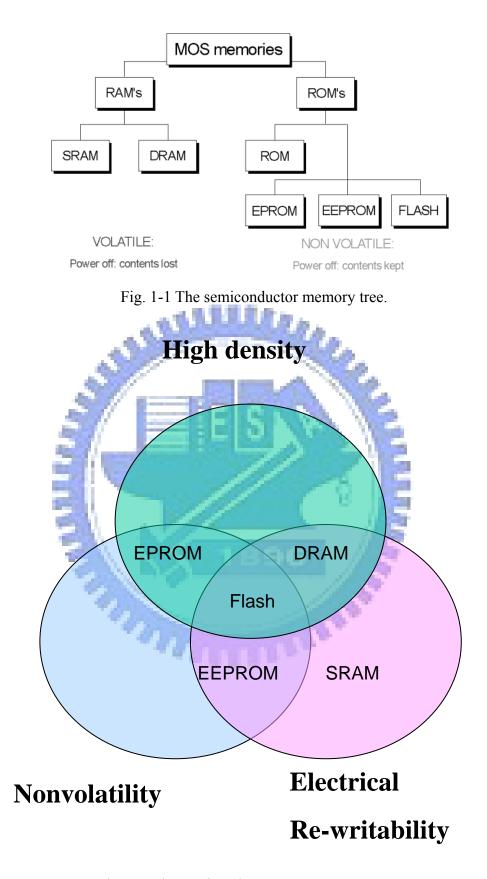

| Fig. 1-1: The semiconductor memory tree7                                                |

| Fig. 1-2: The semiconductor memory7                                                     |

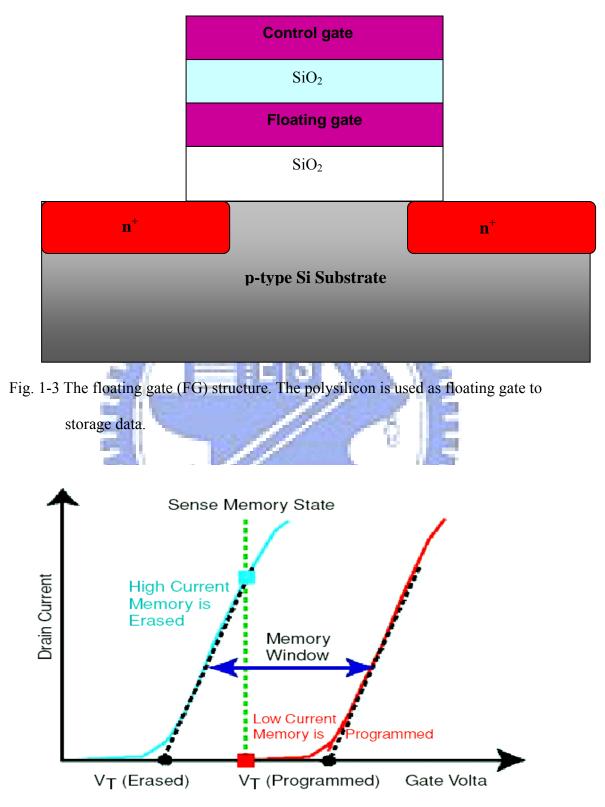

| Fig. 1-3: The floating gate (FG) structure. The polysilicon is used as floating gate to |

| storage data8                                                                           |

| Fig. 1-4: Current-voltage characteristic of a memory device in the erased and           |

| programmed state, showing the V <sub>th</sub> shift and the memory window               |

| Fig. 1-5: The conventional SONOS memory structure. Silicon nitride is used as           |

| charge trapping layer9                                                                  |

| Fig. 1-6: The band diagram of nitride- based SONOS memory9                              |

| Fig. 1-7: The calculated gate leakage for low standby power (LSTP) application          |

| [1.21]                                                                                  |

Chapter 2

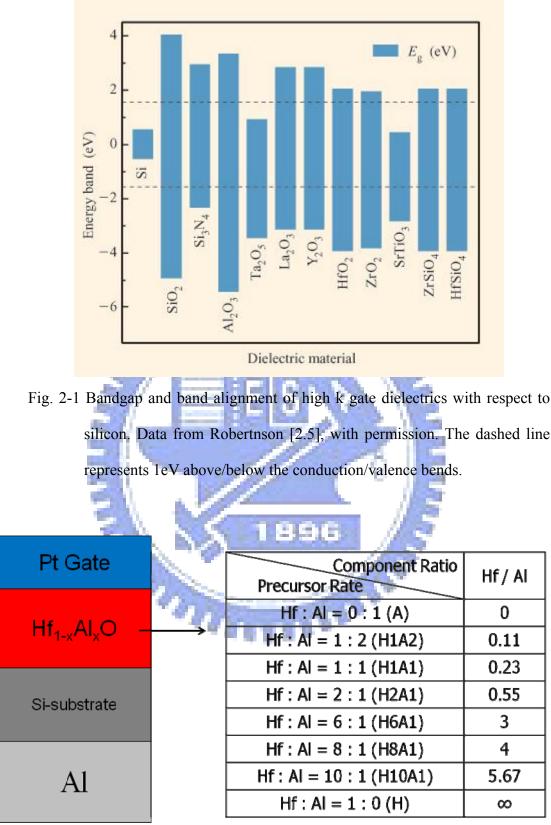

Fig. 2-1: Bandgap and band alignment of high k gate dielectrics with respect to

silicon......17

Fig. 2-2: The process flow of the Hf<sub>1-x</sub>Al<sub>x</sub>O MOS capacitors.....17

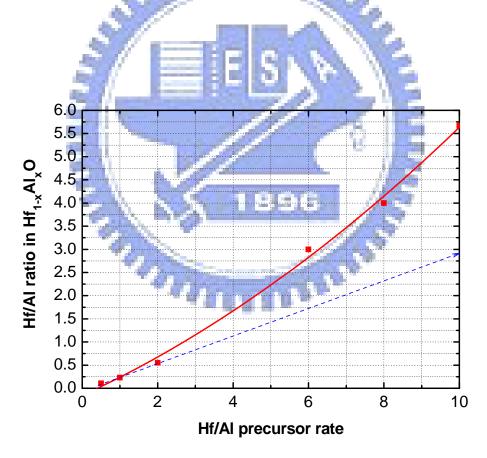

Fig. 2-3: The relationship between Hf/Al precursor rate and Hf/Al ratio in

| $Hf_{1-x}Al_xO$                                                                        |

|----------------------------------------------------------------------------------------|

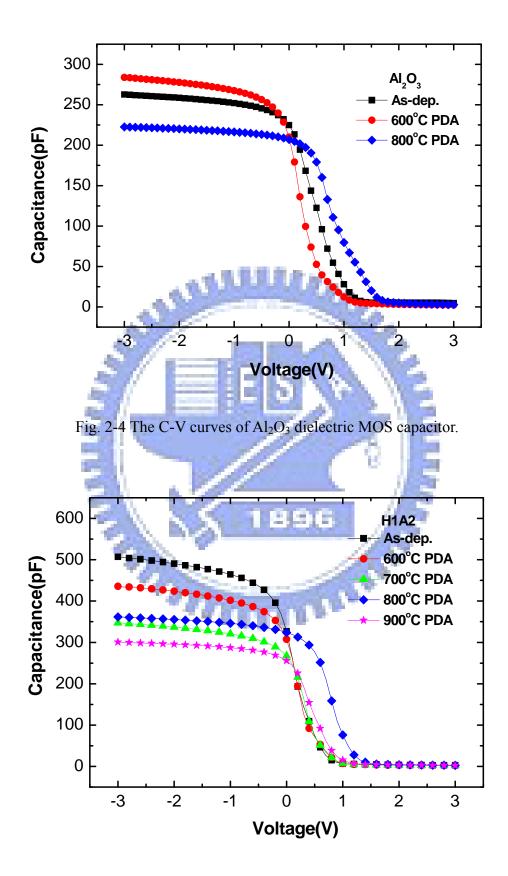

| Fig. 2-4: The C-V curves of Al <sub>2</sub> O <sub>3</sub> dielectric MOS capacitor19  |

| Fig. 2-5: The C-V curves of H1A2 (Hf/Al = 0.11) dielectric MOS capacitor19             |

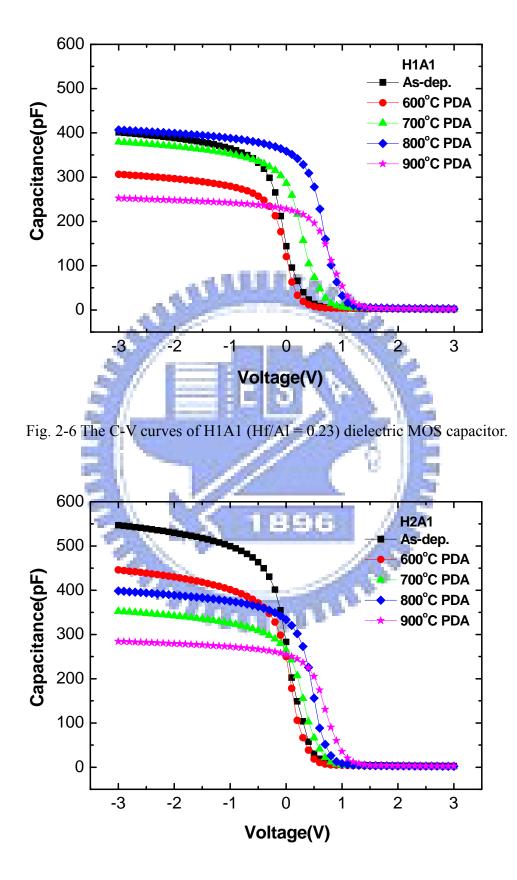

| Fig. 2-6: The C-V curves of H1A1 (Hf/Al = 0.23) dielectric MOS capacitor20             |

| Fig. 2-7: The C-V curves of H2A1 (Hf/Al = 0.55) dielectric MOS capacitor20             |

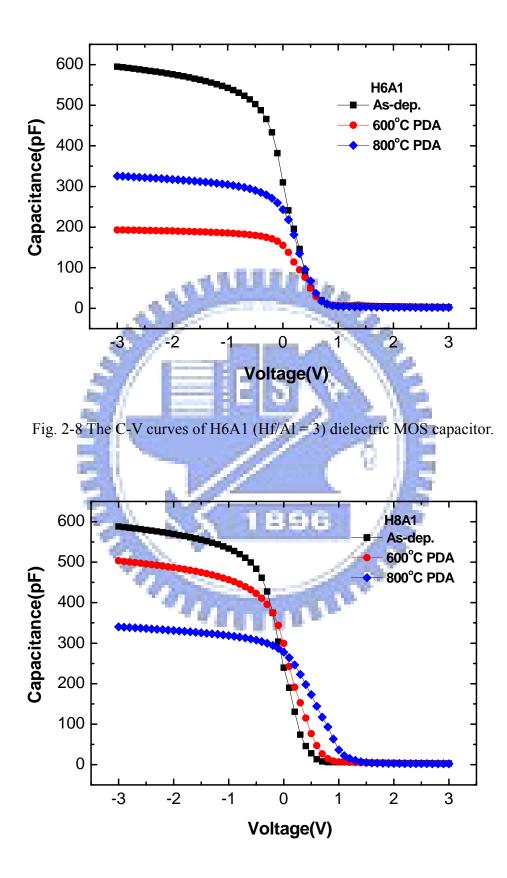

| Fig. 2-8: The C-V curves of H6A1 (Hf/Al = 3) dielectric MOS capacitor21                |

| Fig. 2-9: The C-V curves of H8A1 (Hf/Al = 4) dielectric MOS capacitor21                |

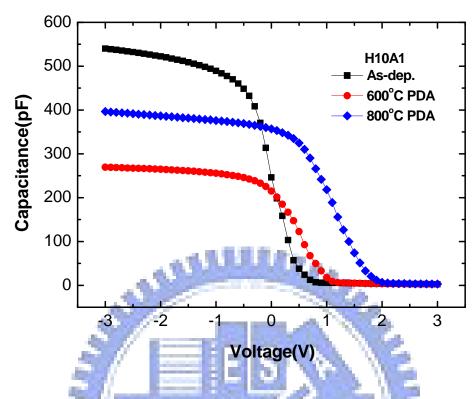

| Fig. 2-10: The C-V curves of H10A1 (Hf/Al = 5.67) dielectric MOS capacitor22           |

| Fig. 2-11: The C-V curves of HfO <sub>2</sub> dielectric MOS capacitor22               |

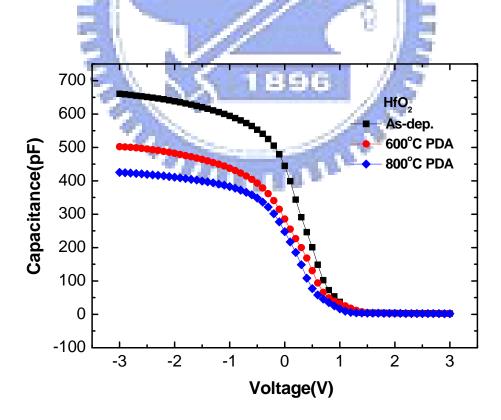

| Fig. 2-12: The I-V curves of Al <sub>2</sub> O <sub>3</sub> dielectric MOS capacitor23 |

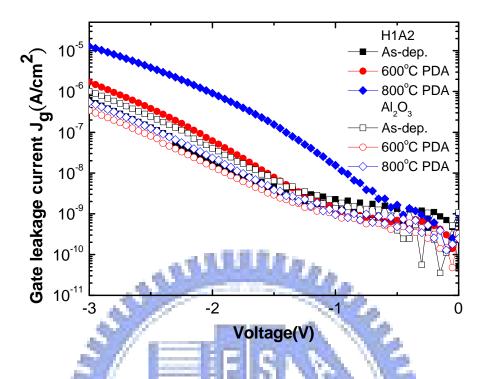

| Fig. 2-13: The I-V curves of H1A2 (Hf/Al = 0.11) dielectric MOS capacitor23            |

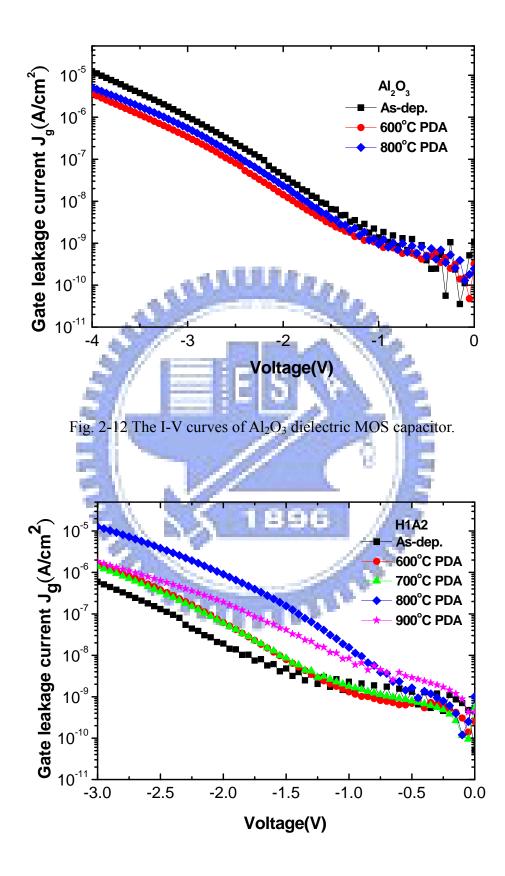

| Fig. 2-14: The I-V curves of H1A1 (Hf/Al = 0.23) dielectric MOS capacitor24            |

| Fig. 2-15: The I-V curves of H2A1 (Hf/Al = 0.55) dielectric MOS capacitor24            |

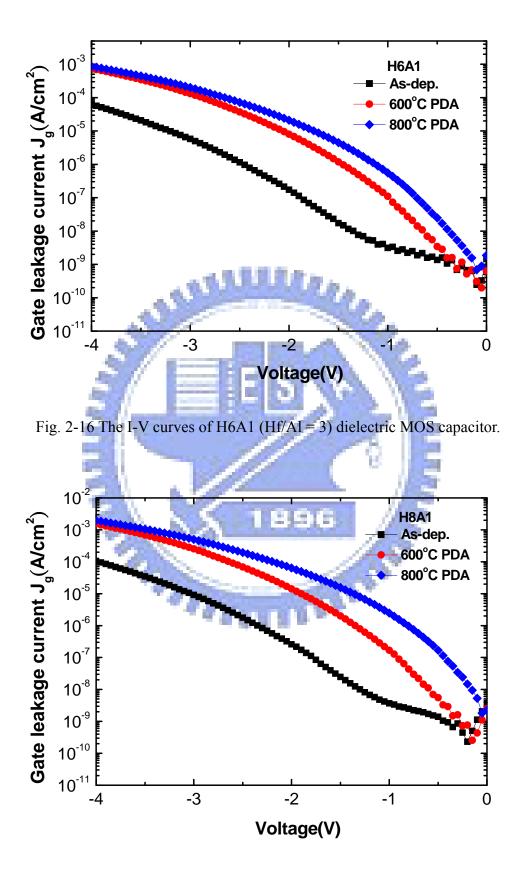

| Fig. 2-16: The I-V curves of H6A1 (Hf/Al = 3) dielectric MOS capacitor25               |

| Fig. 2-17: The I-V curves of H8A1 (Hf/Al = 4) dielectric MOS capacitor25               |

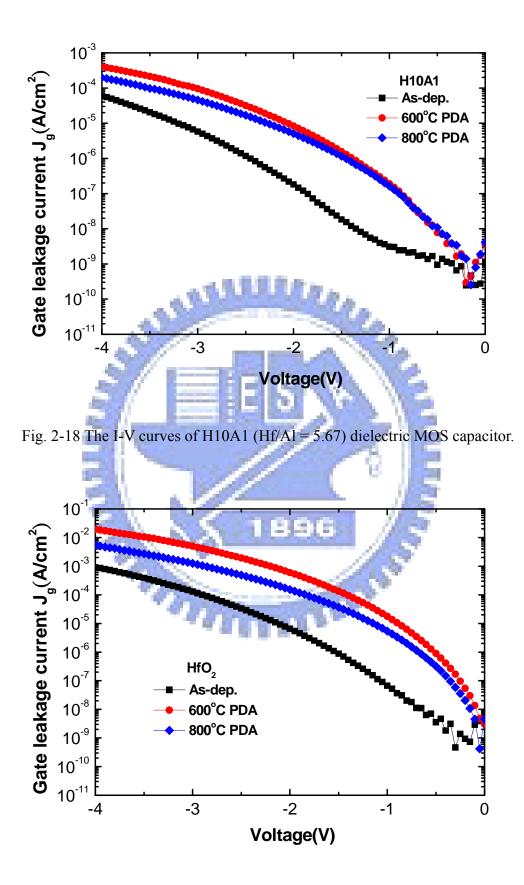

| Fig. 2-18: The I-V curves of H10A1 (Hf/Al = 5.67) dielectric MOS capacitor26           |

| Fig. 2-19: The I-V curves of HfO <sub>2</sub> dielectric MOS capacitor26               |

| Fig. 2-20: The gate leakage current comparison between H1A2 and $Al_2O_3$ with the     |

| same condition (As-dep., 600°C PDA and 800°C PDA)27                                    |

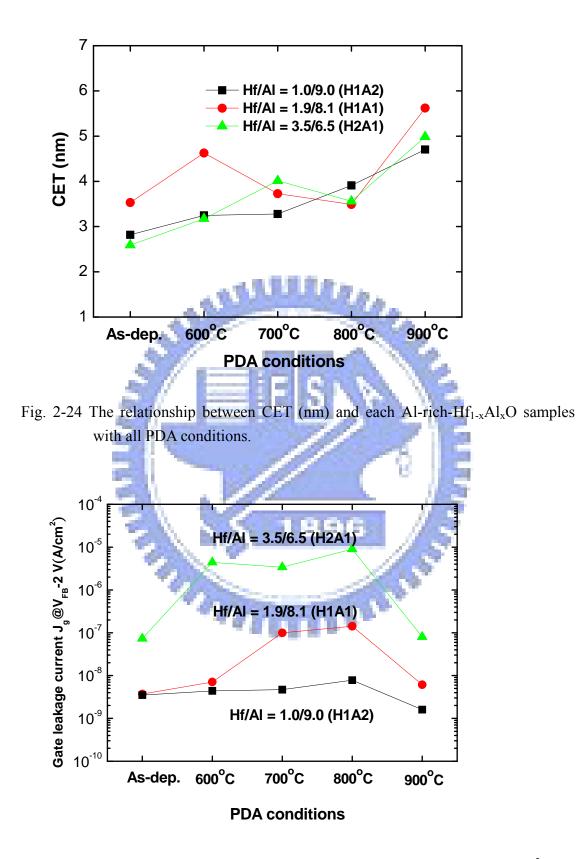

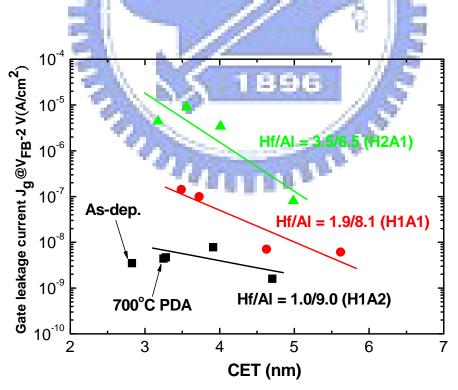

Fig. 2-21: The relationship between interfacial state density D<sub>it</sub> and PDA Fig. 2-22: The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and Fig. 2-23: The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and Fig. 2-24: The relationship between CET (nm) and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions..... Fig. 2-25: The relationship between the gate leakage current  $J_g @V_{fb}-2V(A/cm^2)$  and Fig. 2-26: The relationship between the gate leakage current  $J_g@V_{fb}-1.5V(A/cm^2)$  and Fig. 2-27: The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and

Chapter 3

Fig. 3-2: The relationship between gate leakage current  $J_g$  (A/cm<sup>2</sup>) and gate electric

| field V <sub>g</sub> /EOT (MV/cm)41                                                                   |

|-------------------------------------------------------------------------------------------------------|

| Fig. 3-3: The $I_d$ - $V_g$ curves of the $Al_2O_3$ blocking layer flash memory in the fresh,         |

| programmed, and erased state at different conditions                                                  |

| Fig. 3-4: The $I_d$ - $V_g$ curves of the HfAlO blocking layer flash memory in the fresh,             |

| programmed, and erased state at different conditions                                                  |

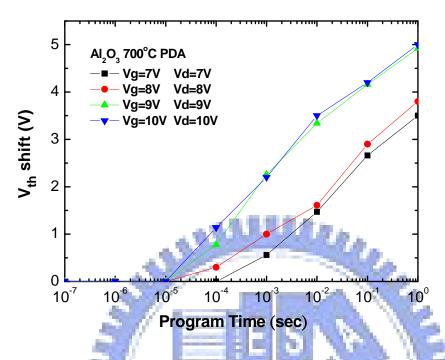

| Fig. 3-5: The program speed curves of SONOS-type memory with $Al_2O_3$ (700°C PDA)                    |

| blocking layer. (CHEI mechanism)43                                                                    |

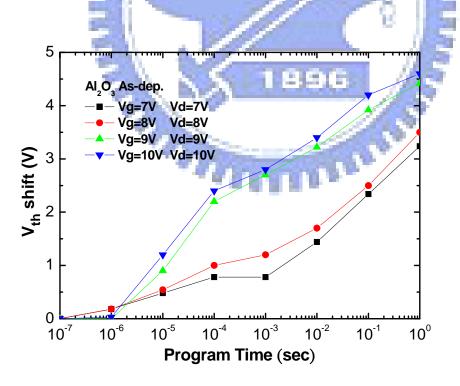

| Fig. 3-6: The program speed curves of SONOS-type memory with Al <sub>2</sub> O <sub>3</sub> (As-dep.) |

| blocking layer. (CHEI mechanism)43                                                                    |

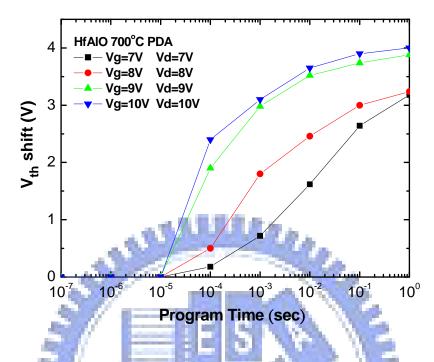

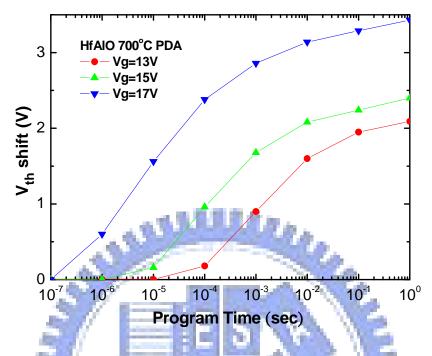

| Fig. 3-7: The program speed curves of SONOS-type memory with HfAlO (700°C                             |

| PDA) blocking layer. (CHEI mechanism)44                                                               |

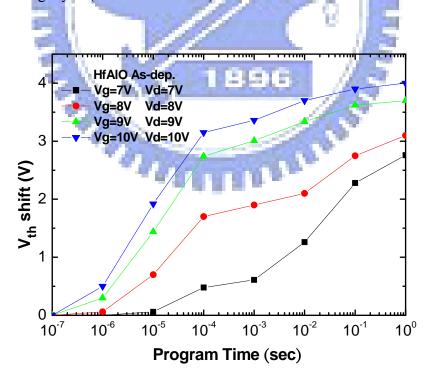

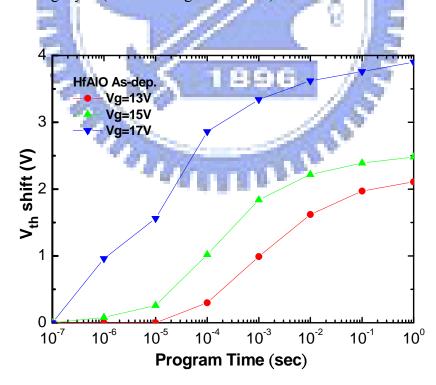

| Fig. 3-8: The program speed curves of SONOS-type memory with HfAlO (As-dep.)                          |

| blocking layer. (CHEI mechanism)44                                                                    |

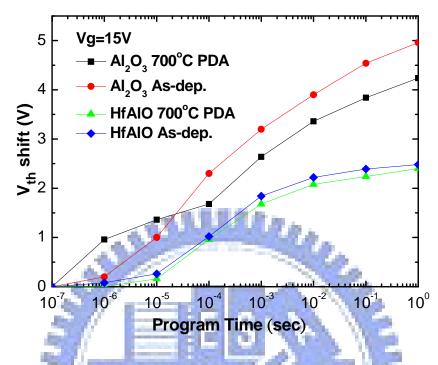

| Fig. 3-9: The comparison program speed curves of SONOS-type memory with $Al_2O_3$                     |

| and HfAlO (700°C PDA) blocking layer. (CHEI mechanism)45                                              |

| Fig. 3-10: The comparison program speed curves of SONOS-type memory with $Al_2O_3$                    |

| and HfAlO (As-dep.) blocking layer. (CHEI mechanism)45                                                |

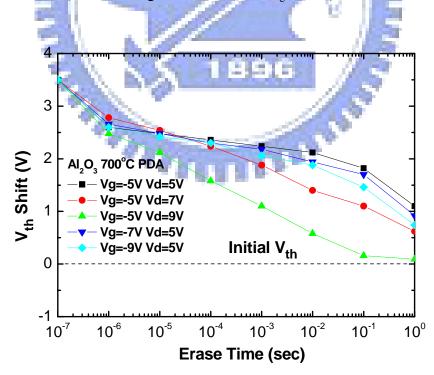

| Fig. 3-11: The program speed curves of SONOS-type memory with $Al_2O_3$ (700°C                        |

| PDA) blocking layer. (FN tunneling mechanism)46                                                       |

| Fig. 3-12: The program speed curves of SONOS-type memory with $Al_2O_3$ (As-dep.)                     |

# blocking layer. (FN tunneling mechanism)......46

Fig. 3-13: The program speed curves of SONOS-type memory with HfAlO (700°C PDA) blocking layer. (FN tunneling mechanism)......47 Fig. 3-14: The program speed curves of SONOS-type memory with HfAlO (As-dep.) blocking layer. (FN tunneling mechanism)......47 Fig. 3-15: The comparison program speed curves of SONOS-type memory with all devices. (FN tunneling mechanism with  $V_g = 15V$ ).....48 Fig. 3-16: The erase speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (700°C PDA) Fig. 3-17: The erase speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (As-dep.) blocking layer. (Band To Band Hot Hole mechanism)......49 Fig. 3-18: The erase speed curves of SONOS-type memory with HfAlO (700°C PDA) Fig. 3-19: The erase speed curves of SONOS-type memory with HfAlO (As-dep.) blocking layer. (Band To Band Hot Hole mechanism)......50 Fig. 3-20: The comparison program speed curves of SONOS-type memory with all (Band To Band Hot Hole mechanism with  $V_g$ =-5V devices. Fig. 3-21: The retention characteristic of SONOS-type flash memory with Al<sub>2</sub>O<sub>3</sub>

Fig. 3-22: The retention characteristics of SONOS-type flash memory with HfAlO

| (As-dep. and 700°C PDA) blocking layer at 25°C |  |

|------------------------------------------------|--|

|------------------------------------------------|--|

Fig. 3-23: The charge loss rate characteristics of SONOS-type flash memory with all

| devices at 25 | °C | .52 | 2 |

|---------------|----|-----|---|

|---------------|----|-----|---|

Fig. 3-24: The gate disturbance characteristics of SONOS-type flash memory with

Al<sub>2</sub>O<sub>3</sub> (As-dep. and 700°C PDA) blocking layer. (Erase State)......52

- Fig. 3-25: The gate disturbance characteristics of SONOS-type flash memory with

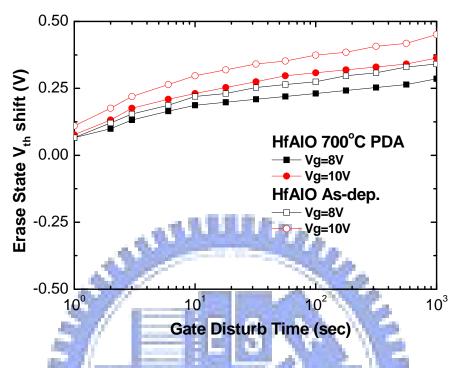

- HfAlO (As-dep. and 700°C PDA) blocking layer. (Erase State)......53

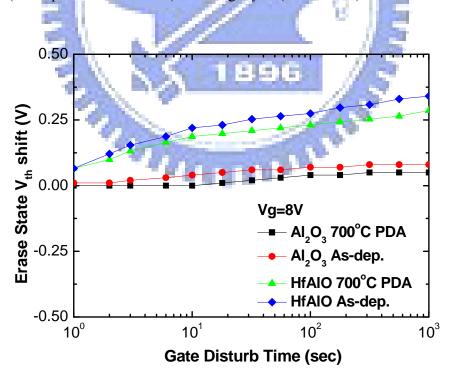

- Fig. 3-26: The gate disturbance characteristics of SONOS-type flash memory with all

- Fig. 3-27: The gate disturbance characteristics of SONOS-type flash memory with

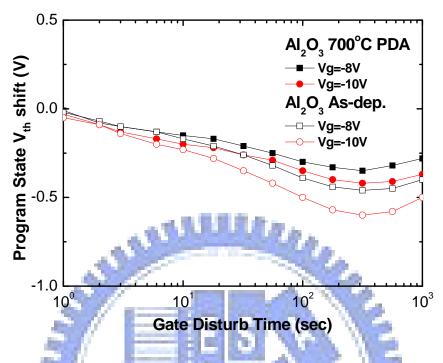

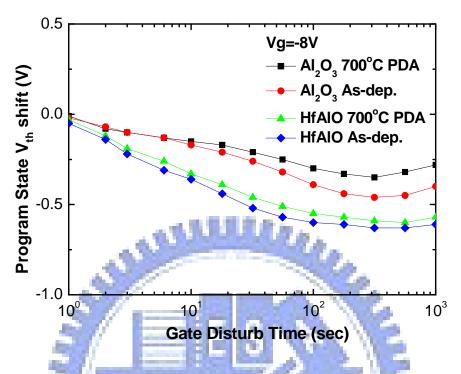

- $Al_2O_3$  (As-dep. and 700°C PDA) blocking layer. (Program State).......54

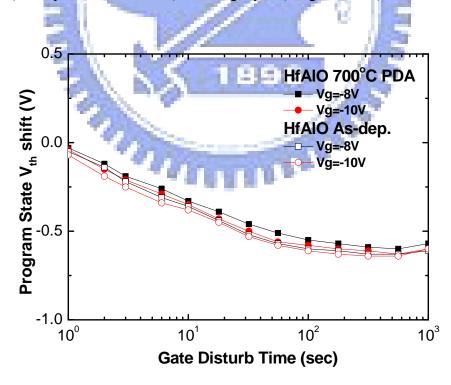

- Fig. 3-28: The gate disturbance characteristics of SONOS-type flash memory with HfAlO (As-dep. and 700°C PDA) blocking layer. (Program State).......54

- Fig. 3-30: The read disturbance characteristics of SONOS-type flash memory with all

# **Table Captions**

| Chapter 1 |  |  |

|-----------|--|--|

|           |  |  |

Table 1-1: Scaling parameters for 2001 ITRS......10

Chapter 2

Table 2-1: Selected material and electrical properties of high-*k* gate dielectrics......16

Table 2-2: Split table for MIS Capacitors using MOCVD Hf<sub>1-x</sub>Al<sub>x</sub>O Dielectric......18

Table 2-3: The characteristics of Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O dielectrics capacitors......31

# Chapter 1 Introduction

### **1-1 Overview of Flash Memory**

Semiconductor memory is an indispensable component of modern electronic system. It is used in personal computers, cellular phones, digital cameras, smart-media, networks, automotive systems, global positioning systems.

The memories based on complementary metal-oxide-semiconductor (CMOS) technology can be divided into two main categories by whether the storage data can be affected by the power supply as depicted in Fig. 1-1: —The volatile memory: like SRAM and DRAM .

SRAM memory can retain the stored information as long as the power is on, drawing very little current. However, the information will be lost when the power is turned off, so SRAM is not a nonvolatile memory.

A Dynamic Random Access Memory (DRAM) cell consists of one transistor and one capacitor. Compared to flash memory, DRAM has much faster program/read speed with very low operating voltage, while flash memory needs 1us to 1ms programming time and high programming voltage. Unfortunately, DRAM is a volatile memory.

—The non-volatile memory: this kind memory will keep the storage data even if the power supply is off, like electrically programmable read only memory (EPROM), electrically erasable programmable read only memory (EEPROM), and the flash memory. Fig. 1-2 shows the semiconductor memory.

The most explosive growth field of the semiconductor memory is the Flash

memory. The advantages of Flash memory are that it can be electrically written more than 100K times with byte programming and sector erasing and with the smallest cell size (one transistor cell) [1.1]-[1.2]. The Flash memory cell is used floating gate (FG) structure as illustrated in Fig. 1-3.

S. M. Sze and D. Kahng, invented the first floating-gate (FG) nonvolatile semiconductor memory in 1967 [1.3]. The conventional FG memory (in Fig. 1-3) used polysilicon as a charge storage layer surrounded by the dielectric [1.1]. Fig. 1-4 shows a typical current versus gate voltage characteristic of an erased FG memory and its Vt shift when the FG memory is programmed. The memory-state for the device can be determined by measuring the current in the MOSFET when a control gate bias is applied within the memory window.

The FG structure can achieve high densities, good program/erase speed and good reliability for Flash memory application. However, the FG memory has several drawbacks. Firstly, the Flash memory needs thick tunnel oxide (8~10nm) to provide superior retention and endurance characteristics, but it also causes higher operation voltage, slow P/E speed, and poor scalability issues. Secondly, because the polysilicon floating-gate is conductive, the total charges stored in floating-gate will be easily leaked directly through the tunnel oxide when the tunnel oxide is damaged during P/E cycles [1.4]. In order to improve the write/erase speed of a floating-gate device, the thickness of the tunnel oxide must be reduced. The tunnel oxide must be less than 25Å in order to achieve 100 ns write/erase time for a reasonable programming voltage (<10 V). Unfortunately, the retention time will be too short. Stress- induced leakage current (SILC) will further degrade the retention time.

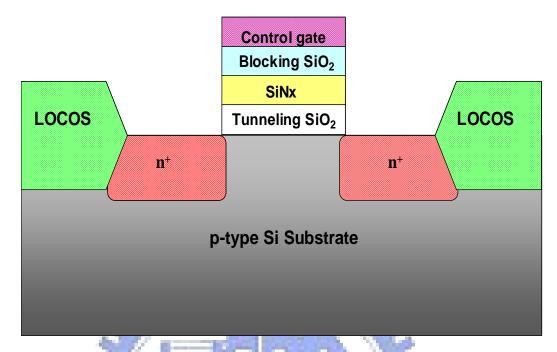

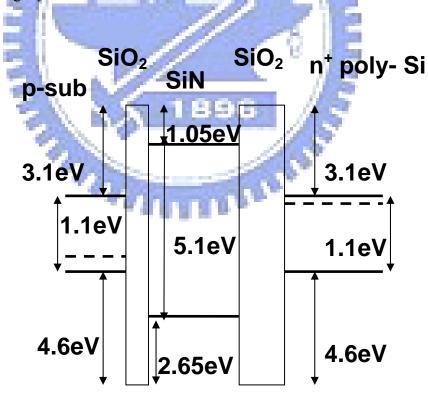

The floating gate memory requires thick tunnel oxide to prevent charge loss through the defect. In order to solve the scaling issue of FG memory, the poly Si-Oxide-Nitride-Oxdie-Silicon (SONOS) memory has been studied recently [1.4]. SONOS memory has better charge retention than floating gate memory when floating gate tunneling oxide is below 10nm due to its isolated deep-level traps. Hence, a leakage path in the tunneling oxide will not cause the discharge of the memory cell [1.4]. The structure of SONOS memory is shown in Fig. 1-5. The SONOS memory uses silicon nitride as charge trapping layer, and the band diagram is shown in Fig. 1-6. The conduction band offset between silicon substrate and nitride is 2.05eV. When we apply a positive voltage on the gate, the band will bend downward as illustrated in Fig. 1-6 [1.5]. The electrons in the Si-sub conduction band will tunnel through the tunneling oxide and a portion of nitride to be trapped in the charge trapping layer.

In order to improve program/erase (P/E) speed, the tunnel oxide thickness should be scaled to maximize the Fowler–Nordheim tunneling probability. However, to avoid the degradation of retention characteristics by tunneling leakage through ultrathin tunnel oxide, the optimization of the tunnel oxide thickness is necessary [1.7]. The optimization of the blocking layer is also necessary to avoid electron tunneling through the blocking oxide during the erase condition, which in turn causes an undererased problem [1.6, 1.8]. Since the high-k dielectric exhibits a significantly lower leakage current density for the relatively thinner effective oxide thickness, we can increase both the thickness and the electric field for the tunnel oxide at the same operating voltage. Therefore, a SONOS-type flash device with high-k dielectrics for a blocking layer provides a faster P/E speed and longer data retention time [1.9].

Besides, continued device scaling requires the continued reduction of the gate dielectric thickness. This requirement arises from two different considerations: controlling the short-channel effect and achieving a high current drive by keeping the amount of charge induced in the channel large as the power-supply voltage decreases. In both cases, to a first approximation, it is the electrical thickness that is important. The electrical thickness at inversion is determined by the series combination of three

capacitances in the gate stack: the depletion capacitance of the gate electrode, the capacitance of the gate dielectric, and the capacitance of the inversion layer in the silicon. On the other hand, the direct tunneling current through the gate dielectric grows exponentially with decreasing physical thickness of the gate dielectric [1.10]. This tunneling current has a direct impact on the standby power of the chip and puts a lower limit on unabated reduction of the physical thickness of the gate dielectric. It is likely that tunneling currents arising from silicon dioxides (SiO<sub>2</sub>) thinner than 0.8 nm cannot be tolerated, even for high-performance systems [1.11]. Solutions that reduce the gate tunneling current and gate capacitance degradation due to polysilicon depletion are explored through introduction of new materials; high-dielectric-constant gate dielectrics.

### **1-2 Motivation**

Today the key dielectrics such as SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> are widely used in the modern silicon devices. Aggressive scaling of CMOS devices and design of DRAM stimulates the investigation of alternative to  $SiO_2$  and  $Si_3N_4$  high dielectric constant (high-k) dielectrics, such as Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, etc. [1.12, 1.13]. Since 1990 nonvolatile semiconductor memory (NVSM) has been the technology driver of the semiconductor industry [1.14]. At the present time a floating gate FLASH EEPROM dominates in the NVSM market. The floating gate type of FLASH EEPROM is impossible to scale down to beyond 0.18 µm due to the difficulty in scaling the tunnel oxide [1.15]. However, for design of terabit EEPROM memory array it is necessary to the channel length of 30-40 use nm. On contrary, а silicon-oxide-nitride-oxide-silicon (SONOS) EEPROM potentially can be scaled up to this size [1.16, 1.17]. Recently SONOS with thick bottom oxide was proposed, where write/erase (W/E) is produced due to hot electron/hole injection in nitride [1.18, 1.19]. Also there were attempts to use SONOS as DRAM devices [1.20].

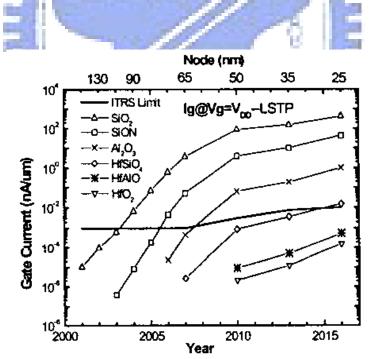

From [1.21], Fig. 1-7 shows that SiO<sub>2</sub> will approach the scaling limits (Table 1-1, 2001 ITRS) in 2003 due to its high gate leakage, High-k (HfO<sub>2</sub>, HfAlO and Al<sub>2</sub>O<sub>3</sub>) can extend the CMOS technology scaling for long-term solutions. Beside, SiO<sub>2</sub> is usually applied as a top oxide in a conventional SONOS. Since SiO<sub>2</sub> has low dielectric constant  $\varepsilon$ =3.9 in comparison with Si<sub>3</sub>N<sub>4</sub> ( $\varepsilon$ =7.5) the electric field in top oxide is about two time larger, than in nitride. Therefore, for scaled SONOS device with comparable thickness of nitride and SiO<sub>2</sub> top oxide, a remarkable part of applied voltage drops on the top oxide during W/E programming. Replacing SiO<sub>2</sub> by high-*k* dielectric can decrease this undesirable voltage drop and, consequently, the total applied voltage [1.22, 1.23, 1.24]. Moreover, because of an electric field in high-*k* dielectric much less than one in SiO<sub>2</sub>, one can expect that parasitic carrier injection [1.25] through top oxide should be suppressed in SONOS with high-*k* dielectric as a top layer. These suppositions were supported by experiment with SONOS with Al<sub>2</sub>O<sub>3</sub> as a blocking oxide [1.23] and by preliminary simulations of W/E process in SONOS with Al<sub>2</sub>O<sub>3</sub> and ZrO2 as a top oxide [1.24].

The goal of this paper is more detail investigation on the characteristics of SONOS type memory with high-*k* dielectrics instead of conventional SONOS with SiO<sub>2</sub> as a top blocking dielectric. This also includes the description of the physical and electrical properties of metal-insulator-metal capacitors, which play a great role of our n-channel SONOS type memory. As example we considered Al<sub>2</sub>O<sub>3</sub> ( $\epsilon$ =9), HfAlO ( $\epsilon$ =9~25) and HfO<sub>2</sub> ( $\epsilon$ =25) as mostly studied high-*k* dielectrics.

### **1-3 Thesis Organization**

In this thesis, we study the performance of the SONOS-type memory device with high-k dielectric as blocking layer using MOCVD.

In Chapter 1, we introduce the background of the flash memory and explain why SONOS-type memory with high-k blocking layer.

In Chapter 2, we fabricate metal-insulator-metal capacitors using MOCVD HfAlO dielectric, measuring C-V and I-V. And then we discuss the physical and electrical properties in order to extract the excellent result to fabricate n-channel SONOS type memories device.

In Chapter 3, we fabricate n-channel SONOS type memories using HfAlO for blocking layer. And then we discuss the advantages and weak points of them.

At the end of this thesis, we make a conclusion in Chapter 4.

Fig. 1-2 The semiconductor memory.

Fig. 1-4 Current-voltage characteristic of a memory device in the erased and programmed state, showing the  $V_{th}$  shift and the memory window.

Fig. 1-5 The conventional SONOS memory structure. Silicon nitride is used as charge trapping layer.

Fig. 1-6 The band diagram of nitride- based SONOS memory.

| Year                   | 2003    | 2004    | 2005    | 2006    | 2007    | 2010    | 2013    | 2016    |

|------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Node(nm)               | 107     | 90      | 80      | 70      | 65      | 50      | 35      | 25      |

| EOT(HP)                | 1.1~1.6 | 0.9~1.4 | 0.8~.13 | 0.7~1.2 | 0.6~1.1 | 0.5~0.8 | 0.4~0.6 | 0.4~0.5 |

| EOT(LSTP)              | 2.0~2.4 | 1.8~2.2 | 1.6~2.0 | 1.4~1.8 | 1.2~1.6 | 0.9~1.3 | 0.8~1.2 | 0.7~1.1 |

| V <sub>DD</sub> (HP)   | 1.0     | 1.0     | 0.9     | 0.9     | 0.7     | 0.8     | 0.8     | 0.6     |

| V <sub>DD</sub> (LSTP) | 1.2     | 1.2     | 1.2     | 1.2     | 1.1     | 1.0     | 0.9     | 0.9     |

| I <sub>g</sub> (HP)    | 70      | 100     | 300     | 700     | 1000    | 3000    | 7000    | 10000   |

| Ig(LSTP)               | 0.001   | 0.001   | 0.001   | 0.001   | 0.001   | 0.003   | 0.007   | 0.01    |

Table 1-1 Scaling parameters for 2001 ITRS. The Node is shown as the MPU 1/2Pitch in nm. The EOT (nm), operating voltage VDD(V) and gate leakageIg(nA/um) are listed for both high performance(HP) and low stand-bypower(LSTP) CMOS technology.

Fig. 1-7 The calculated gate leakage for low standby power (LSTP) application. Here, an average value of the proposed maximum and minimum EOT from Table 1-1 is used for each generation. Al<sub>2</sub>O<sub>3</sub> mole fraction is 30% for HfAlO and Si<sub>3</sub>N<sub>4</sub> mole fraction 40% for optimized SiON [1.21].

# Chapter 2

# Physical and Electrical properties of MIS Capacitors Using MOCVD Hf<sub>1-x</sub>Al<sub>x</sub>O Dieletrics

### **2-1 Introduction**

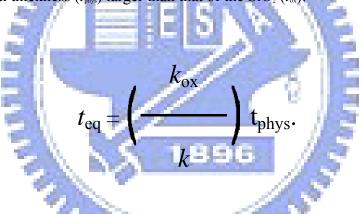

A gate dielectric with a dielectric constant (*k*) substantially higher than that of  $SiO_2(k_{ex})$  will achieve a smaller equivalent electrical thickness ( $t_{eq}$ ) than the SiO<sub>2</sub>, even with a physical thickness ( $t_{phys}$ ) larger than that of the SiO<sub>2</sub> ( $t_{ex}$ ):

Replacing the SiO<sub>2</sub> with a material having a different dielectric constant is not as simple as it may seem. The material bulk and interface properties must be comparable to those of SiO<sub>2</sub>, which are remarkably good. Basic material properties such as thermodynamic stability with respect to silicon, stability under thermal conditions relevant to microelectronic fabrication, low diffusion coefficients, and thermal expansion match are some critical examples. In addition, interface traps of the order of a few  $10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> and bulk traps of the order of a few  $10^{10}$  cm<sup>-2</sup> are common among SiO2 and the closely related oxynitrides [2.1, 2.2]. Charge trapping and reliability for the gate dielectrics are particularly important considerations.

Thermal stability with respect to silicon is an important consideration, since high-temperature anneals are generally employed to activate dopants in the source/drain as well as the polysilicon gate. Although many binary and ternary oxides are predicted to be thermally stable with respect to silicon [2.3], recent research on high-dielectric-constant gate insulators have focused primarily on binary metal oxides such as Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, and Gd<sub>2</sub>O<sub>3</sub> and their silicates [2.4, 2.5]. Table 2-1 compares the properties of the common high-k gate dielectrics reported in the literature. The dielectric constant of these materials generally ranges from 10 to 40, which is about a factor of 3 to 10 higher than SiO2. The benefits of using a very-high-dielectric-constant material to simply replace SiO2 for the same electrical thickness are limited because of the presence of two-dimensional electric fringing fields from the drain through the physically thicker gate dielectric [2.6, 2.7]. The drain fringing field lowers the source-to-channel potential barrier and lowers the threshold voltage in a way similar to the well-known drain-induced barrier lowering (DIBL), in which the drain field modulates the source-to-channel potential barrier via coupling through the silicon substrate. The use of higher-k-materials must therefore be combined with a concurrent reduction of the electrical thickness.

A large silicon-to-insulator energy barrier height is desirable because the gate direct-tunneling current is exponentially dependent on the (square root of the) barrier height [2.8]. In addition, hot-carrier emission into the gate insulator is also related to the same barrier height [2.9]. The high-k material should therefore not only have a large bandgap, but also have a band alignment which results in a large barrier height. Figure 2-1 illustrates the bandgap and band alignment for several high-k gate dielectrics calculated by Robertson [2.5]. Most high-k materials that have other desirable properties do have relatively low band offsets and small bandgaps. Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) is probably the only material that has a bandgap and band

alignment similar to those SiO<sub>2</sub>.

In this work, we discuss the electrical characteristic of gate dielectric with different ratio of  $HfO_2$  and  $Al_2O_3$  at different annealing temperature. Under these assumptions, we found a systematic method to extract the excellent result. We expect that the excellent result can play a key role in blocking layer on SONOS type memory.

### **2-2 Experimental**

Figure 2-2 schematically depicts the process flow of the proposed MIS capacitors. The fabrication process of the  $Hf_{1-x}Al_xO$  dielectric MOS capacitors were started on p-type, 5-10  $\Omega$  cm, (100) 150mm silicon substrates which had been RCA clean before deposition. Then, we deposited the  $Hf_{1-x}Al_xO$  by Metal Organic Chemical Vapor Deposition (MOCVD). In order to observe the effect of RTA conditions on mos capaciter properties, we varied the RTA temperature after the  $Hf_{1-x}Al_xO$  deposition. The samples went through oxide RTA treatment in N2 ambient at various temperatures (As-department, 600°C, 700°C, 800°C, 900°C, as shown in Table 2-2) for 1min. After that, Pt is used for the top capacitor by sputtering method with pure Pt target. Finally Al is used for the bottom capacitor by thermal coater method with pure Al target.

At the first time, we changed the different Hf : Al precursor rate, such as Hf : Al = 2:1 (H2A1), Hf : Al = 1:1 (H1A1), and Hf : Al = 1:2 (H1A2). In order to know the Hf/Al ratio in the dielectric Hf<sub>1-x</sub>Al<sub>x</sub>O, we analyzed by XPS method. And then, we discovered that the Hf/Al ratio in the dielectric Hf<sub>1-x</sub>Al<sub>x</sub>O at the H2A1 precursor rate is 0.55, H1A1 is 0.23, and H1A2 is 0.11 (All of them are Al-rich). So we predicted that H6A1 may be 1 (The blue dash line in Fig. 2-3, and the three points in Fig.2-3 are H2A1, H1A1, and H2A1). Therefore we tried the H6A1, H8A1, H10A1, and also  $H(HfO_2)$  and  $A(Al_2O_3)$  at the second time in order to know the characteristics of Hf-rich and  $Al_2O_3$ . The red line in Fig. 2-3 shows that the actual relationship between Hf/Al precursor rate and Hf/Al ratio in  $Hf_{1-x}Al_xO$  which is not the same with our prediction.

### 2-3 Results and Discussion

In this section, the physical and electrical characteristics of MOS capacitors using MOCVD HfAlO dielectric were discussed.

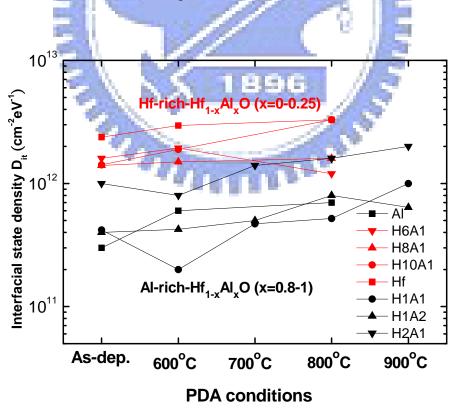

#### 2-3-1 C-V Characteristic

Fig. 2-4~2-11 show the relationship between the sweep voltage and capacitance for  $Hf_{1-x}Al_xO$  MOS Capacitors. We have several conditions for  $Hf_{1-x}Al_xO$  MOS capacitors. Then we measure C-V curves, and use a systematic methodology to extract the accurate flat band voltage of  $Hf_{1-x}Al_xO$  MOS capacitors for interfacial state density (Fig. 2-21).We found that the higher PDA temperature, the thicker dielectric, the higher interface density, therefore the capacitance decreases. We also found that the H1A2 C-V curves are better than others.

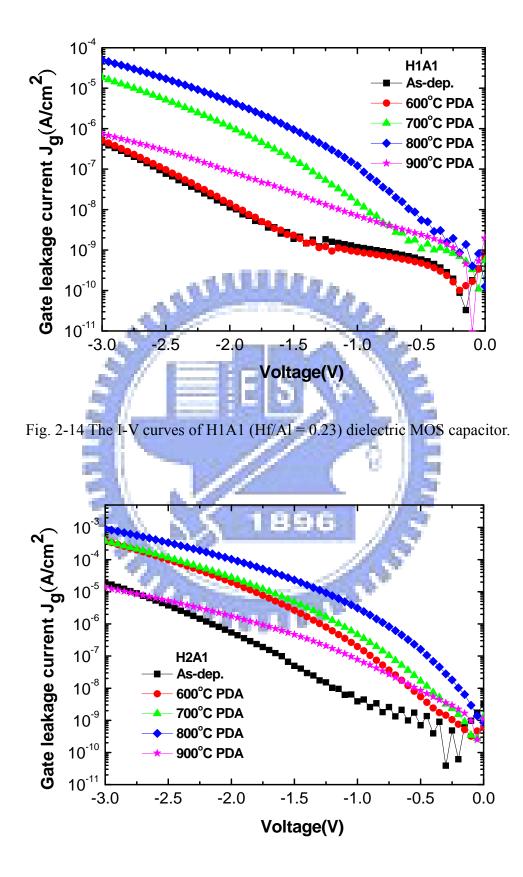

#### 2-3-2 I-V Characteristic

We also measure I-V curves, such as Fig. 2-12~2-19 illustrate. We found that the more Hf component the more leakage current, and higher PDA temperature the higher gate leakage current. This is because that more Hf component more grain boundaries. Fig. 2-20 shows that the gate leakage current comparison between H1A2 and Al<sub>2</sub>O<sub>3</sub> sample with the same condition (As-dep., 600°C PDA and 800°C PDA). We found

that they are almost the same.

#### **2-3-3 CET Characteristic**

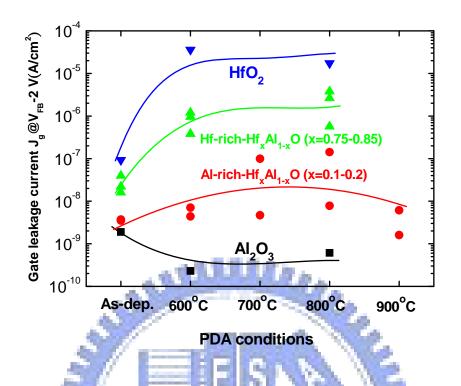

From the C-V illustrations (Fig. 2-4~2-11), we not only can calculate the V<sub>fb</sub> for each sample, but also the CET for each sample. So we plot the Fig. 2-22 which shows the relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and each sample for all conditions. We discovered that the more Hf component the higher gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$ , this is because that the more Hf component the more grain boundaries. The Fig. 2-23 shows the relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and the CET for each samples with all PDA conditions. We found that the Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O capacitors are better than Hf-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O ones in the relationship between gate leakage current and CET.

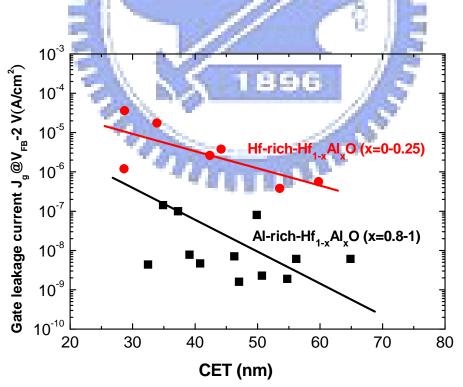

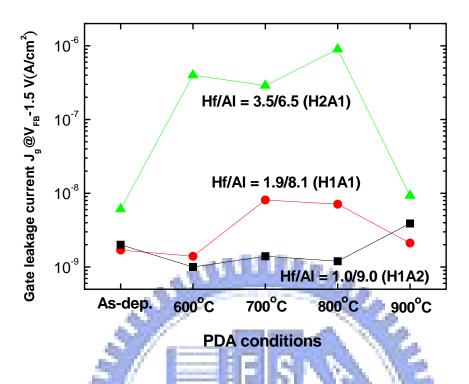

From the two pictures (Fig. 2-22 and 2-23), we extract the Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O capacitors are better, so we discuss the Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O characteristics especially. Fig.2-24 shows the relationship between CET (nm) and each Al-rich samples with all PDA conditions, Fig. 2-25 shows the relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions, and Fig. 2-26 shows the relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions, and Fig. 2-26 shows the relationship between the gate leakage current  $J_g@V_{fb}-1.5V(A/cm^2)$  and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions. From Fig. 2-24 and Fig. 2-25, we can combine them to the Fig. 2-27 which shows that the relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and the CET for each samples with all PDA conditions. We can obviously find the two samples H1A2 (As-dep.) and H1A2 (700°C PDA) with the lowest CET and the lowest gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  from Fig. 2-27, so we decided the four conditions (H1A2 As-dep., H1A2 700°C PDA, Al<sub>2</sub>O<sub>3</sub> As-dep., and Al<sub>2</sub>O<sub>3</sub> 700°C PDA) are our the best blocking layer for SONOS-type memory in next chapter. We cast the characteristics of

Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O dielectrics capacitors in Table 2-3.

## 2-4 Summary

In this chapter, we observed that Al-rich  $Hf_{1-x}Al_xO$  dielectric capacitors have lower interfacial state density, lower gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$ and  $J_g@V_{fb}-1.5V(A/cm^2)$ , and lower CET than Hf-rich ones at the same condition. Therefore we optimized the condition for the SONOS-type memory blocking layer. According to our data, we choose A (Al<sub>2</sub>O<sub>3</sub>: As-dep. and 700°C PDA) and H1A2 (HfAlO: As-dep. and 700°C PDA) for our blocking layer of SONOS-type memory.

|                                | S/ E       | EES          |             | 2                   |

|--------------------------------|------------|--------------|-------------|---------------------|

|                                | Dielectric |              | Conduction  | Thermal stability   |

| Dielectric                     | constant   | Bandgap (eV) | band offset | w.r.t. silicon      |

|                                | (bulk)     |              | (eV)        | (MEIS data)         |

| SiO <sub>2</sub>               | 3.9        | 9            | 3.5         | >1050°C             |

| Si <sub>3</sub> N <sub>4</sub> | 2 7        | 5.3 8 9      | 2.4         | >1050°C             |

| Al <sub>2</sub> O <sub>3</sub> | ~10        | 8.8          | 2,8         | ~1000°C             |

|                                | 122        |              | C. C. C.    | Not                 |

| Ta <sub>2</sub> O <sub>5</sub> | 25         | 4.4          | 0.36        | thermodynamically   |

|                                |            |              |             | stable with silicon |

| Y <sub>2</sub> O <sub>3</sub>  | ~15        | 6            | 2.3         | Silicate formation  |

| HfO <sub>2</sub>               | ~20        | 6            | 1.5         | ~950°C              |

| ZrO <sub>2</sub>               | ~23        | 5.8          | 1.4         | ~900°C              |

Table 2-1 Selected material and electrical properties of high-k gate dielectrics.Data compiled from Robertson [2.5], Gusev et al. [2.4], Hubbard and Schlom [2.3], and other sources.

Fig. 2-2 The process flow of the Hf<sub>1-x</sub>Al<sub>x</sub>O MOS capacitors. On the right: the different flow rates and the dielectric Hf/Al component ratio analyzed by XPS method.

| Sample<br>Split Condition | Н | H10A1 | H8A1 | H6A1 | H2A1 | H1A1 | H1A2 | Α |

|---------------------------|---|-------|------|------|------|------|------|---|

| As-dep.                   |   |       |      |      |      |      |      |   |

| 600°C PDA                 | • | •     | •    | •    | •    | •    | •    | • |

| 700°C PDA                 |   |       |      |      |      |      |      |   |

| 800°C PDA                 | ٠ | •     | •    | •    | •    | ٠    | •    | • |

| 900°C PDA                 |   | - 15  | 112  | 800  | *    | *    | *    | * |

Table 2-2 Split table for MIS Capacitors using MOCVD Hf<sub>1-x</sub>Al<sub>x</sub>O Dielectric.

Fig. 2-3 The relationship between Hf/Al precursor rate and Hf/Al ratio in  $Hf_{1-x}Al_xO$ .

Fig. 2-5 The C-V curves of H1A2 (Hf/Al = 0.11) dielectric MOS capacitor.

Fig. 2-7 The C-V curves of H2A1 (Hf/Al = 0.55) dielectric MOS capacitor.

Fig. 2-9 The C-V curves of H8A1 (Hf/Al = 4) dielectric MOS capacitor.

Fig. 2-10 The C-V curves of H10A1 (Hf/A1 = 5.67) dielectric MOS capacitor.

Fig. 2-11 The C-V curves of HfO<sub>2</sub> dielectric MOS capacitor.

Fig. 2-13 The I-V curves of H1A2 (Hf/Al = 0.11) dielectric MOS capacitor.

Fig. 2-15 The I-V curves of H2A1 (Hf/Al = 0.55) dielectric MOS capacitor.

Fig. 2-17 The I-V curves of H8A1 (Hf/Al = 4) dielectric MOS capacitor.

Fig. 2-19 The I-V curves of HfO<sub>2</sub> dielectric MOS capacitor.

Fig. 2-20 The gate leakage current comparison between H1A2 and Al<sub>2</sub>O<sub>3</sub> with the same condition (As-dep., 600°C PDA and 800°C PDA).

Fig. 2-21 The relationship between interfacial state density D<sub>it</sub> and PDA conditions.

Fig. 2-22 The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and each sample for all conditions.

Fig. 2-23 The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and the CET for each samples with all PDA conditions.

Fig. 2-25 The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions.

Fig. 2-26 The relationship between the gate leakage current  $J_g@V_{fb}-1.5V(A/cm^2)$  and each Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O samples with all PDA conditions.

Fig. 2-27 The relationship between the gate leakage current  $J_g@V_{fb}-2V(A/cm^2)$  and the CET for each samples with all PDA conditions.

| Properties<br>Sample         | EOT(A) | V <sub>fb</sub> (V) | D <sub>it</sub> (cm <sup>-2</sup> eV <sup>1</sup> ) | $J_g @V_{fb} - 2V(A/cm^2)$   | J <sub>g</sub> @V <sub>fb</sub> -1.5V<br>(A/cm <sup>2</sup> ) |

|------------------------------|--------|---------------------|-----------------------------------------------------|------------------------------|---------------------------------------------------------------|

| Al2O3(As-dep.)               | 44.8   | 0.89                | 1.3x10 <sup>11</sup>                                | 1.9x10 <sup>-9</sup>         | 6.3x10 <sup>-10</sup>                                         |

| H1A2(As-dep.)                | 28.2   | 0.6                 | 4x10 <sup>11</sup>                                  | 3.5x10 <sup>-9</sup>         | 10 <sup>-9</sup>                                              |

| H1A2(700 <sup>°</sup> C PDA) | 32.8   | 0.64                | 5x10 <sup>11</sup>                                  | <b>3.7</b> ×10 <sup>-9</sup> | 1.4x10 <sup>-9</sup>                                          |

| H1A1(As-dep.)                | 35.3   | 0.3                 | 4.2x10 <sup>12</sup>                                | 3.7x10 <sup>-9</sup>         | 1.7x10 <sup>-9</sup>                                          |

| H1A1(700°C PDA)              | 37.3   | 0.62                | 4.7x10 <sup>12</sup>                                | 10-7                         | 8.1x10 <sup>-9</sup>                                          |

| H2A1(As-dep.)                | 35.9   | 0.44                | 10 <sup>12</sup>                                    | 7.3x10 <sup>-8</sup>         | 6.1x10 <sup>-9</sup>                                          |

| H2A1(700 <sup>°</sup> C PDA) | 40.1   | 0.59                | 1.4x10 <sup>12</sup>                                | 3.4x10 <sup>-6</sup>         | 1.4x10 <sup>-9</sup>                                          |

Table 2-3 The characteristics of Al-rich-Hf<sub>1-x</sub>Al<sub>x</sub>O dielectrics capacitors.

# Characteristics of SONOS-type Memory with High-k Hf<sub>1-x</sub>Al<sub>x</sub>O Blocking Layer

### **3-1 Introduction**

Poly-Si/Oxide/Nitride/Oxide–Silicon (SONOS)-type structure memories, which include nitride and nanocrystal memories, have recently attracted much attention for their application in the next-generation nonvolatile memories [3.1-3.10]. Alternatively, conventional floating gate Flash memories adopt the multilevel-cell concept to increase its density based on the same process technology [3.11-3.14]. In recent years, change ONO processing technology and choice trapping layer material have been study to improve the cell data retention. Such as high-k, silicon, germanium, and metal nanocrystals may by used to provide charge storage for nonvolatile memories.

Tremendous efforts have been focused on the development of high-density, low-cost, and nonvolatile solid-state storage devices for the applications of portable electronic devices, such as MP3 players, mobile phones, and digital cameras [3.15, 3.16]. Among the many kinds of nonvolatile memories, floating-gate flash memory has received a great amount of interest because its density has increased almost 2-fold a year for several years [3.15-3.17]. For further increases in device density, the tunnel oxide thickness should be scaled down, but even a single defect can discharge the stored memory charge owing to the conductive nature of the floating polycrystalline silicon (poly-Si) gate electrode in floating gate devices [3.18]. Therefore, silicon–oxide–nitride–oxide–silicon (SONOS) devices have received increasing interest recently owing to their better endurance, smaller cell/chip size, and lower power consumption than the floating gate devices [3.18, 3.19]. However, charge retention and erase speed remain the major challenges to overcome in order for SONOS devices to replace floating-gate devices. Recently, Lee et al. reported that improved erase performance and endurance characteristics can be achieved by

replacing SiO2 and poly-Si as high-k dielectric,  $Al_2O_3$  for blocking oxide material, respectively [3.20]. Data retention characteristics, however, still must be improved because a small memory window is expected after a long retention.

In this work, we fabricate a high performance nonvolatile memory with a high-k material for blocking layer. The blocking layer material is Hf<sub>1-x</sub>Al<sub>x</sub>O. This high-k material is used to replace the blocking layer in the SOHOS structure. These material provide high thermal stability and good electrical properties, therefore it can maintain the good electrical characteristic in the fabrication process. The faster operation speed can be improved, and programming efficiency can be improved. The application of high-k materials can further reduce the operation voltage and potentially can help memory device scaling. It has good characteristics in terms of considerably high speed program/erase, large memory windows, good retention time, good endurance, good disturbance, and good retention.

2

### **3-2 Experimental**

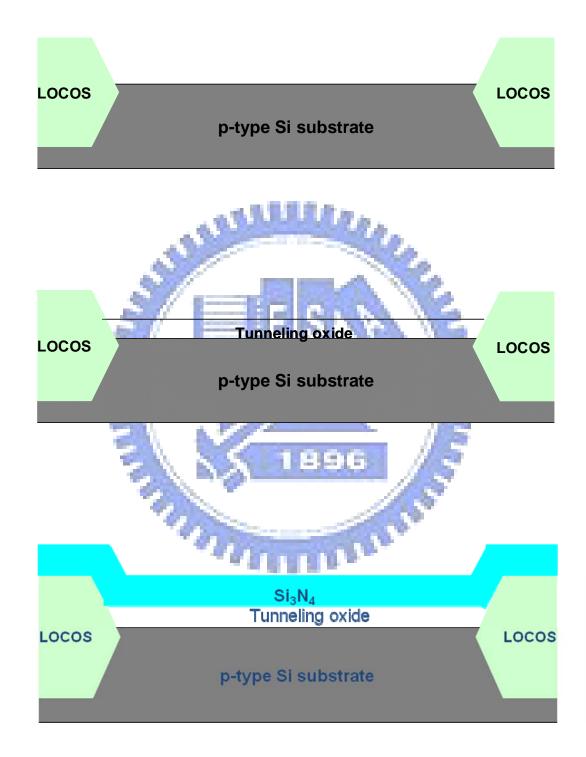

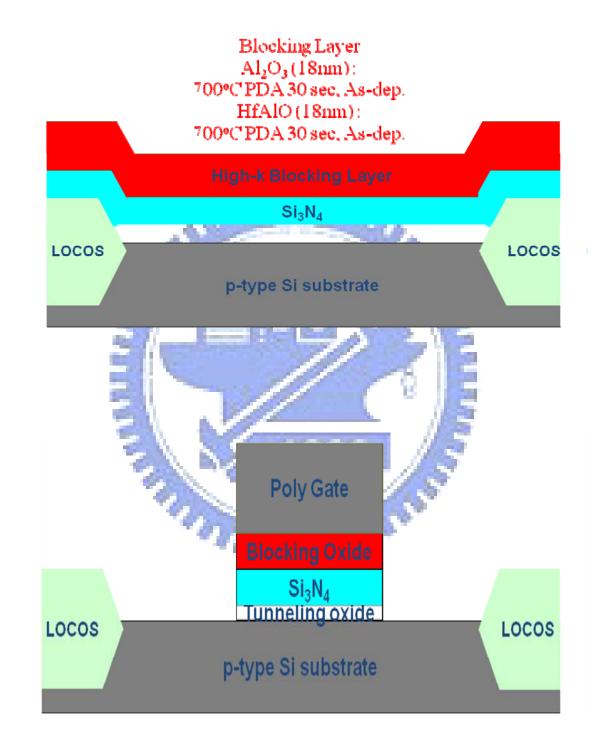

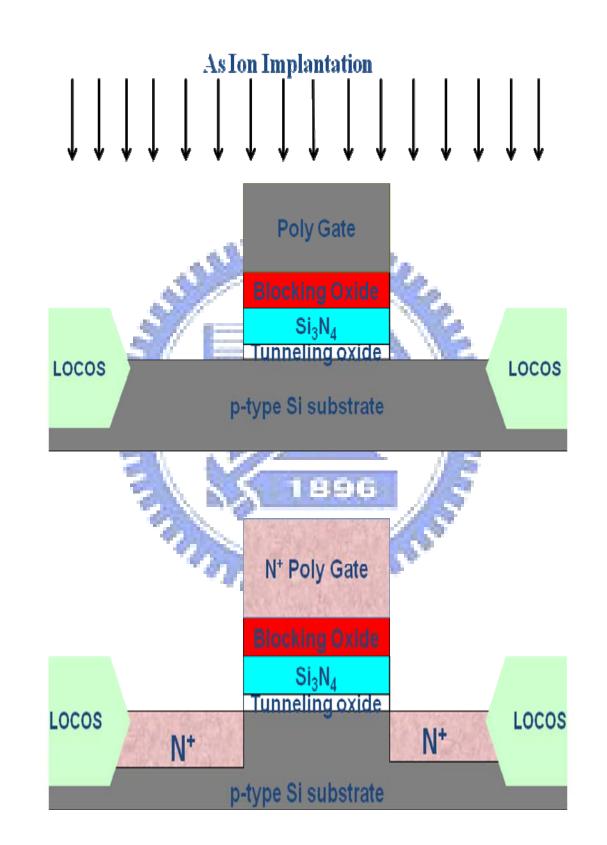

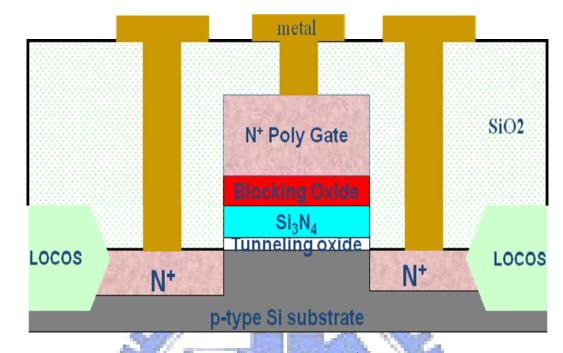

In Chapter 2, we decided two materials for our blocking layer which are Hf<sub>0.1</sub>Al<sub>0.9</sub>O(In this chapter, we call it as HfAlO) and Al<sub>2</sub>O<sub>3</sub>, and two RTA conditions (As-dep. and 700°C). Figure 3-1 schematically depicts the process flow of the proposed SONOS flash memory. The fabrication process of the memory devices with blocking layer HfAlO and Al<sub>2</sub>O<sub>3</sub> involved was started with the LOCOS isolation process on p-type, 5-10  $\Omega$  cm, (100) 150mm silicon substrates. First, a 4 nm thick tunnel oxide was thermally grown at 1000<sup>o</sup>C in vertical furnace system. The trapping layer of Si<sub>3</sub>N<sub>4</sub> layer was deposited by Low Pressure Chemical Vapor Deposition (LPCVD). Blocking oxide of HfAlO about 21 nm thick and Al<sub>2</sub>O<sub>3</sub> about 18nm were then deposited by Metal Organic Chemical Vapor Deposition (MOCVD). After that, two of the samples (one is HfAlO, another is Al<sub>2</sub>O<sub>3</sub>) went through RTA treatment in N<sub>2</sub> ambient at 700<sup>o</sup>C for 30sec. And then, a 200 nm thick poly-silicon was deposited to serve as the gate electrode by Low Pressure Chemical Vapor Deposition (LPCVD). Then, gate electrode was patterned. For NMOSFET ,the source/drain and gate were doped by self-aligned As ion implantation at the dosage and energy of  $5 \times 10^{15}$  ions/cm<sup>-2</sup> and 25 KeV, then the substrate contact was patterned and the sub-contact was implanted with BF<sub>2</sub> at the dosage and energy of  $5 \times 10^{15}$

ions/cm<sup>-2</sup> and 40 KeV. After these implantations, for NMOSFET the dopants were activated at 900<sup>o</sup>C for 30 sec. The rest of the subsequent standard CMOS procedures were complete for fabricating the poly Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) memory devices.

#### **3-3 Results and Discussion**

In this section, the electrical characteristics of poly gate SONOS-type memory with HfAlO and Al<sub>2</sub>O<sub>3</sub> for blocking layer were discussed.

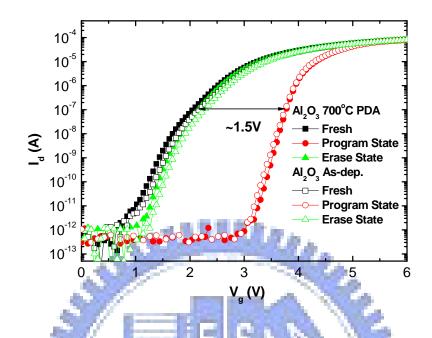

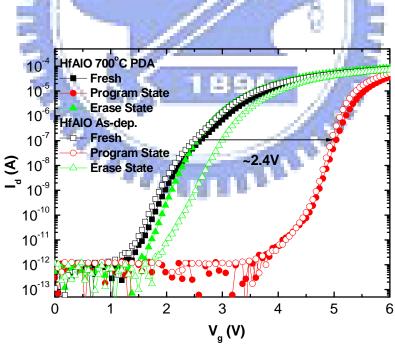

#### 3-3-1 Ig-Vg Curves and Memory Window

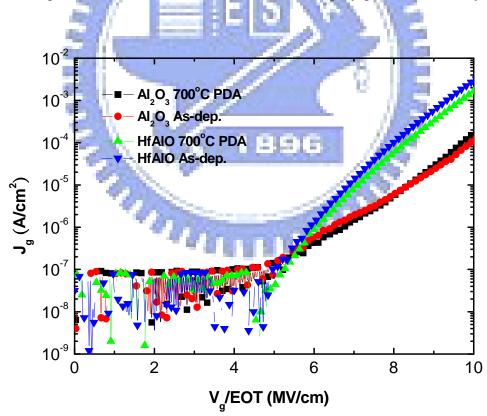

Fig. 3-2 shows that relationship between gate leakage current J<sub>g</sub> (A/cm<sup>2</sup>) and gate electric field Vg/EOT (MV/cm). We observed the HfAlO blocking layer memories have higher gate leakage current  $J_{e}$  than  $Al_2O_3$  ones at high electric field ( $V_g$ /EOT >8 MV/cm), this is probably because the HfAlO blocking layer memories have more grain boundaries and lower conduction band gap than Al<sub>2</sub>O<sub>3</sub> ones. Because of Hf crystalline temperature lower than Al<sub>2</sub>O<sub>3</sub>, the grain boundaries may generate after high PDA temperature. The leakage may pass through these grain boundaries. Another because that HfAlO blocking layer memories have lower band gap than Al<sub>2</sub>O<sub>3</sub> ones, the electrons may tunnel easily through the gap to gate. Fig. 3-3 and Fig. 3-4 show the Id-Vg curves of the Al<sub>2</sub>O<sub>3</sub> and HfAlO blocking layer memories under program and erase operations. We use channel hot electron injection (CHEI) to program and band to band hot hole to erase (BTBHH). All the program condition are  $V_g = 8V$ ,  $V_d = 8V$  with 10 m-sec stress, and the erase condition are  $V_g$ = -9V,  $V_d$ = 9V with 0.1 sec stress. The  $V_{th}$  of Al<sub>2</sub>O<sub>3</sub> blocking layer after programming shift about 1.5V from the original fresh state, and the HfAlO ones are about 2.4V. After erasing, the  $V_{th}$  shift almost the same as program state-fresh. So the memory windows are about 1.5V (Al<sub>2</sub>O<sub>3</sub>) and 2.4V (HfAlO). We also observed that the higher gate leakage current the larger memory window, just like HfAlO ones.

#### **3-3-2 Program and Erase Speed**

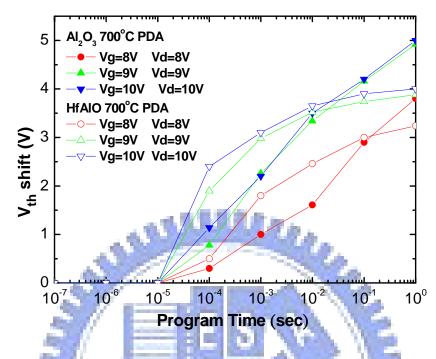

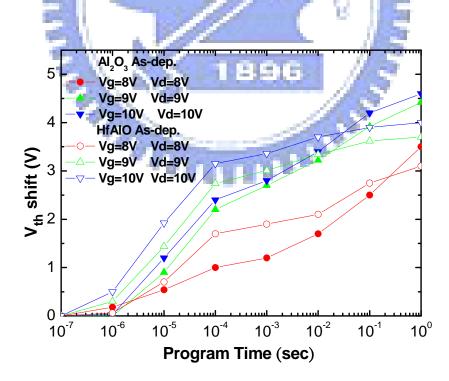

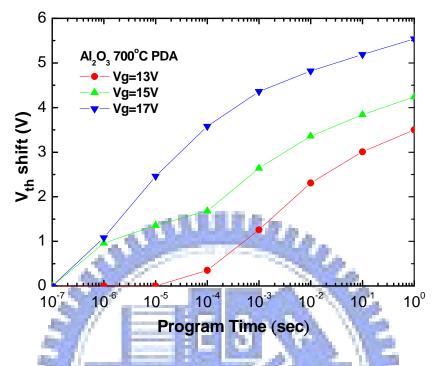

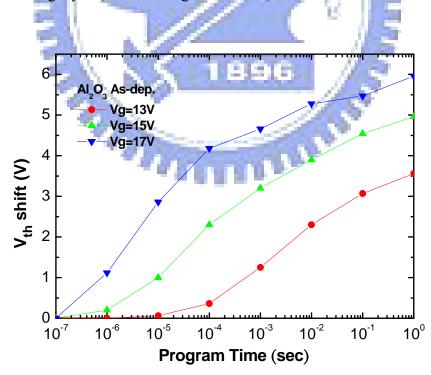

For the SONOS-type flash memory with high-k Al<sub>2</sub>O<sub>3</sub> and HfAlO blocking layer, the program speed are shown in Fig. 3-5~3-8 and Fig. 3-10~3-13. First, we use channel hot electron injection (CHEI) to program all samples and show four different stress conditions:  $V_g = 7V$ ,  $V_d = 7V$ ;  $V_g = 8V$ ,  $V_d = 8V$ ;  $V_g = 9V$ ,  $V_d = 9V$ ;  $V_g = 10V$ ,  $V_d = 10V$  in Fig. 3-5~3-8. We can obviously observe the line of Al<sub>2</sub>O<sub>3</sub> and HfAlO (700°C PDA) are not going up about 10<sup>-5</sup> and 10<sup>-6</sup> sec, this is because that the higher PDA temperature ones generate interfacial state to hold memory programming. We also compare the CHEI program speed at the same PDA conditions, as shown in Fig. 3-9 and Fig. 3-10. We found that SONOS-type memories with HfAlO blocking layer program faster than Al<sub>2</sub>O<sub>3</sub> ones about < 1 m-sec, but Al<sub>2</sub>O<sub>3</sub> ones faster than HfAlO ones about > 1 m-sec. This is because that HfAlO ones have higher k than Al<sub>2</sub>O<sub>3</sub> ones, the program speed is faster about < 1 m-sec; but the HfAlO blocking layer memories have more grain boundaries and lower conduction band gap than Al<sub>2</sub>O<sub>3</sub> ones, these maybe generate gate leakage current. And then, we use FN tunneling to program all samples and show three different stress conditions:  $V_g = 13V$ ,  $V_g = 15V$  and  $V_g = 17V$  in Fig. 3-11~3-14. We also fixed the gate voltage  $V_g = 15V$  to compare all devices in Fig. 3-15. We observed that program speed of the SONOS-type memory with HfAlO blocking layer are not faster than Al<sub>2</sub>O<sub>3</sub> ones. This is probably because the lower valance band gap and more grain boundaries of HfAlO ones, the FN program speed of Al<sub>2</sub>O<sub>3</sub> ones are more efficacious.

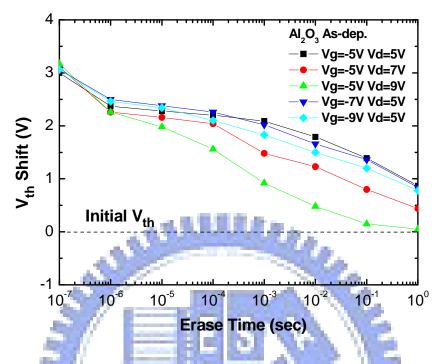

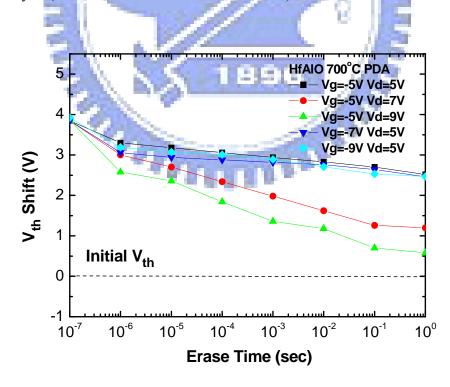

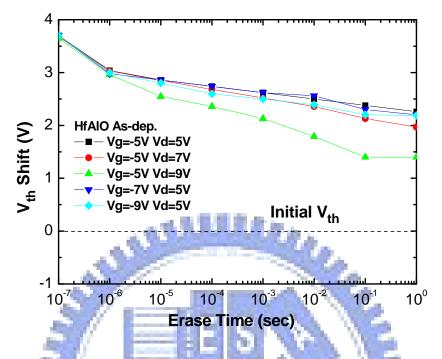

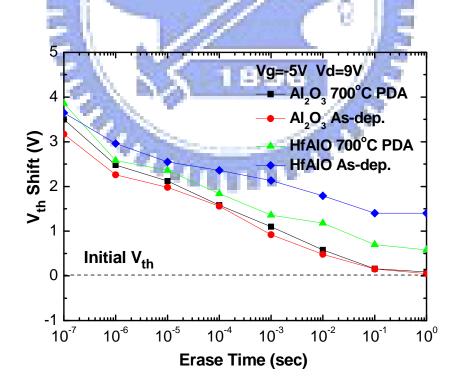

The erase speed of SONOS-type flash memory with high-k Al<sub>2</sub>O<sub>3</sub> and HfAlO blocking layer are shown in Fig. 3-16~3.19. We use band to band hot hole (BTBHH) to erase all devices and show five different stress conditions:  $V_g$ = -5V,  $V_d$ = 5V;  $V_g$ = -5V,  $V_d$ = 7V;  $V_g$ = -5V,  $V_d$ = 8V;  $V_g$ = 10V,  $V_d$ = 10V. We found the more  $V_d$  erase voltage degree the better erase efficacy, it seems larger  $V_g$  voltage degree does not work. We also fixed the stress condition ( $V_g$ = -5V,  $V_d$ = 9V) to compare all devices in Fig. 3-20. We observed the HfAlO ones are more difficult to erase to initial state, this is because electron back tunneling occur.

#### **3-3-3 Data Retention Characteristic**

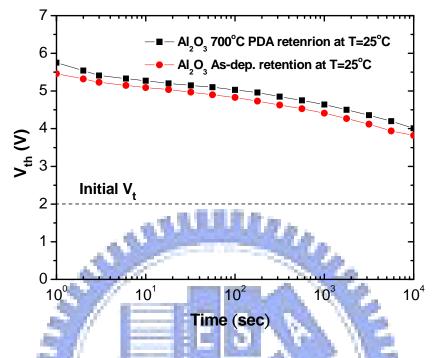

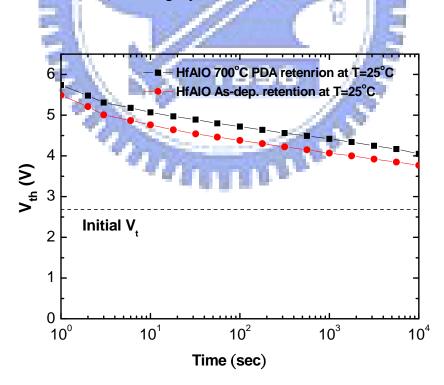

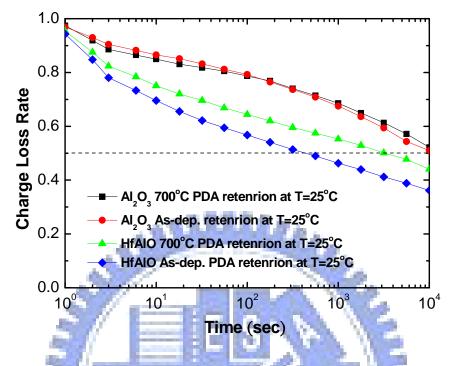

Fig. 3-21 and 3-22 are the data retention characteristic of SONOS memory with HfAlO and Al<sub>2</sub>O<sub>3</sub> blocking layer measured at 25°C. We can observed that these data are not the same with our predict results, so we plot the illustration for charge loss rate in order to analyze clearly what as shown in Fig. 3-23. We can observe that the HfAlO ones loss charge more than 50% after  $10^4$  sec stress. Although it seems that the data characteristics of Al<sub>2</sub>O<sub>3</sub> ones are better than HfAlO ones, the data characteristics of Al<sub>2</sub>O<sub>3</sub> ones are still not very good. This is probably because that the valance band gap of Al2O3 is lower than SiO2 to induce leakage current.

#### **3-3-4 Disturbance Measurement**

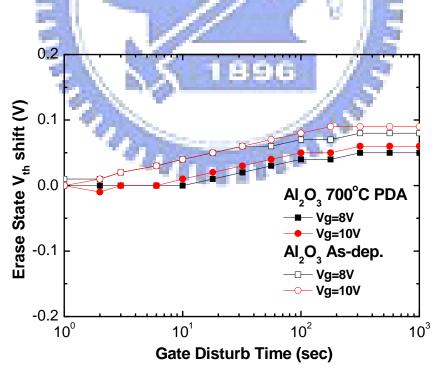

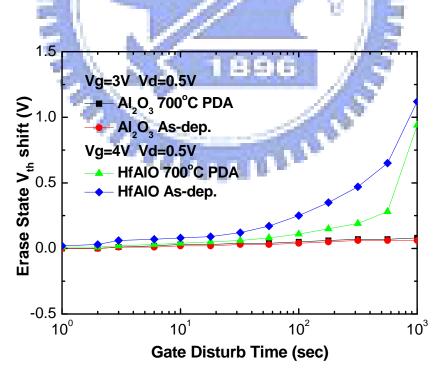

Fig. 3-24 and 3-25 show the gate disturbance measurement of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> and HfAlO blocking layer for two stress conditions:  $V_g$ = 8V and  $V_g$ = 10V with  $V_d = V_s = V_b = 0V$  at erase state for  $10^3$  sec stress. The applied gate voltage will attract electrons in the substrate tunneling to the SiN<sub>x</sub> layer by FN tunneling mechanism and result into V<sub>th</sub> increase. We can obviously found that the devices after 700°C PDA perform good characteristic than As-dep. ones. That is probably because that the 700°C PDA temperature condition make the blocking layer thicker than As-dep. ones. Fig. 3-26 shows the comparison of gate disturbance of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> and HfAlO blocking layer for one stress condition:  $V_g = 8V$  with  $V_d = V_s = V_b = 0V$  at erase state for  $10^3$  sec stress. We found the data characteristics of  $Al_2O_3$  ones are better than HfAlO ones. This is because the valance band gap of HfAlO is lower than Al<sub>2</sub>O<sub>3</sub> ones. We also measure the gate disturbance at program state, as shown in Fig. 3-27 and 3-28. The measurement conditions are  $V_g$ = -8V and  $V_g$ = -10V with  $V_d$ =V<sub>s</sub>=V<sub>b</sub>=0V at erase state for  $10^3$  sec stress. We can find that phenomenon of electron back tunneling occur after  $10^3$ sec stress. Fig. 3-29 shows the comparison of gate disturbance of SONOS-type memory with  $Al_2O_3$  and HfAlO blocking layer for one stress condition:  $V_g$ = -8V with  $V_d = V_s = V_b = 0V$  at program state for  $10^3$  sec stress. We can observe there are more grain boundaries in the SONOS-type memory with HfAlO blocking layer than Al<sub>2</sub>O<sub>3</sub> ones, so the disturbance is not better than  $Al_2O_3$ . Fig. 3-30 shows read disturbance measurement of the SONOS-type memories with HfAlO and Al<sub>2</sub>O<sub>3</sub> blocking layer. We applied two stress conditions:  $V_g$ = 3V,  $V_d$ = 0.5V to Al<sub>2</sub>O<sub>3</sub> ones and  $V_g$ = 4V  $V_d$ = 0.5V to HfAlO ones for 10<sup>3</sup> sec. The read disturbance data of HfAlO are not better than Al<sub>2</sub>O<sub>3</sub>.

# **3-4 Summary**

In this chapter, we propose the SONOS-type memories with high-k HfAlO and Al<sub>2</sub>O<sub>3</sub> blocking layer. We have shown the electric curves, like Jg-Vg/EOT, Id-Vg, program/erase speed with different mechanism, charge retention, charge loss rate, gate disturbance with program and erase state, and read disturbance. We compare the qualities of the SONOS-type memories with high-k HfAlO and Al<sub>2</sub>O<sub>3</sub> blocking layer, and discuss the factors about them.

Fig. 3-1 The process flow and the cross-section of the  $n^+$  poly gate flash memory.

Fig. 3-2 The relationship between gate leakage current  $J_g$  (A/cm<sup>2</sup>) and gate electric field  $V_g$ /EOT (MV/cm).

Fig. 3-3 The  $I_d$ -V<sub>g</sub> curves of the  $Al_2O_3$  blocking layer flash memory in the fresh, programmed, and erased state at different conditions. The memory windows are about 1.5V.

Fig. 3-4 The I<sub>d</sub>-V<sub>g</sub> curves of the HfAlO blocking layer flash memory in the fresh, programmed, and erased state at different conditions. The memory windows are about 2.4V.

Fig. 3-5 The program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (700°C PDA) blocking layer. (CHEI mechanism)

Fig. 3-6 The program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (As-dep.) blocking layer. (CHEI mechanism)

Fig. 3-7 The program speed curves of SONOS-type memory with HfAlO (700°C PDA) blocking layer. (CHEI mechanism)

Fig. 3-8 The program speed curves of SONOS-type memory with HfAlO (As-dep.) blocking layer. (CHEI mechanism)

Fig. 3-9 The comparison program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> and HfAlO (700°C PDA) blocking layer. (CHEI mechanism)

Fig. 3-10 The comparison program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> and HfAlO (As-dep.) blocking layer. (CHEI mechanism)

Fig. 3-11 The program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (700°C PDA) blocking layer. (FN tunneling mechanism)

Fig. 3-12 The program speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (As-dep.) blocking layer. (FN tunneling mechanism)

Fig. 3-13 The program speed curves of SONOS-type memory with HfAlO (700°C PDA) blocking layer. (FN tunneling mechanism)

Fig. 3-14 The program speed curves of SONOS-type memory with HfAlO (As-dep.) blocking layer. (FN tunneling mechanism)

Fig. 3-15 The comparison program speed curves of SONOS-type memory with all devices. (FN tunneling mechanism with  $V_g = 15V$ )

Fig. 3-16 The erase speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (700°C PDA) blocking layer. (Band To Band Hot Hole mechanism)

Fig. 3-17 The erase speed curves of SONOS-type memory with Al<sub>2</sub>O<sub>3</sub> (As-dep.) blocking layer. (Band To Band Hot Hole mechanism)

Fig. 3-18 The erase speed curves of SONOS-type memory with HfAlO (700°C PDA) blocking layer. (Band To Band Hot Hole mechanism)

Fig. 3-19 The erase speed curves of SONOS-type memory with HfAlO (As-dep.) blocking layer. (Band To Band Hot Hole mechanism)

Fig. 3-20 The comparison program speed curves of SONOS-type memory with all devices. (Band To Band Hot Hole mechanism with  $V_g$ =-5V  $V_d$ =9V)

Fig. 3-21 The retention characteristic of SONOS-type flash memory with Al<sub>2</sub>O<sub>3</sub> (As-dep. and 700°C PDA) blocking layer at 25°C.

Fig. 3-22 The retention characteristics of SONOS-type flash memory with HfAlO (As-dep. and 700°C PDA) blocking layer at 25°C.

Fig. 3-23 The charge loss rate characteristics of SONOS-type flash memory with all devices at 25°C.

Fig. 3-24 The gate disturbance characteristics of SONOS-type flash memory with Al<sub>2</sub>O<sub>3</sub> (As-dep. and 700°C PDA) blocking layer. (Erase State)

Fig. 3-25 The gate disturbance characteristics of SONOS-type flash memory with HfAlO (As-dep. and 700°C PDA) blocking layer. (Erase State)

Fig. 3-26 The gate disturbance characteristics of SONOS-type flash memory with all samples. (Erase State)

Fig. 3-27 The gate disturbance characteristics of SONOS-type flash memory with Al<sub>2</sub>O<sub>3</sub> (As-dep. and 700°C PDA) blocking layer. (Program State)

Fig. 3-28 The gate disturbance characteristics of SONOS-type flash memory with HfAlO (As-dep. and 700°C PDA) blocking layer. (Program State)

Fig. 3-29 The gate disturbance characteristics of SONOS-type flash memory with all samples. (Program State)

Fig. 3-30 The read disturbance characteristics of SONOS-type flash memory with all samples. (Program State)

# Conclusions

The thesis of "Study on High-k Gate dieletric  $Hf_{1-x}Al_xO$  for Blocking layer of SONOS Non-Volatile Memory" was proposed. The results of each chapter are summarized as below.

In chapter 2, we discuss the dependence of different  $Hf_{1-x}Al_xO$  component dielectric on the different annealing temperatures. We used a systematic methodology to extract the best assumption for our SONOS-type memory. We found Al-rich  $Hf_{1-x}Al_xO$  dielectric have lower interface density, lower gate leakage current, and lower CET than Hf-rich at the same condition. We also found the H1A2 (Hf : Al = 0.11) sample has the lowest leakage current and CET in Al-rich  $Hf_{1-x}Al_xO$ , and the leakage current as low as  $Al_2O_3$  at low PDA conditions.

In chapter 3, we replace conventional blocking layer with HfAlO and Al<sub>2</sub>O<sub>3</sub> dielectric on SONOS-type memories. We have shown the electric curves, just like Ig-Vg, Id-Vg, program speed with different mechanism, erase speed, charge loss rate and disturbances. We demonstrate program efficiency of HfAlO blocking layer are better than Al<sub>2</sub>O<sub>3</sub> ones about < 1 m-sec. But program efficiency of Al<sub>2</sub>O<sub>3</sub> blocking layer are better than HfAlO ones about > 1 m-sec, because of large leakage current. The EBT phenomenon occurs to erasing and gate disturb with program state. All the retention characteristic data are not good, because of large leakage current occurred by lower band gap.

In order to overcome the retention, large leakage current and electron back tunneling issue, we propose some assumption:

- Using lower band gap for trapping layer (such as Si) in order to reduce the gate leakage current.

- 2. Using nanocrystal for trapping layer in order to improve the retention issue.

- 3. Using metal gate for larger work function in order to reduce EBT.

- Using tri-blocking layer (such as oxide/high-k/oxide) may improve the retention issue.

# Reference

### **Chapter 1**

- [1.1] Y. King, "Thin Dielectric Technology and Memory Devices", Ph.D dissertation, Univ. of California, Berkeley, CA 1999.

- [1.2] A.J. Walker et al, " 3D TFT-SONOS Memory Cell for Ultra-High Density File Storage Applications", 2003 Symposium on VLSI Technology.

- [1.3] S.M. Sze, "Physics of Semiconductor Devices, 2<sup>nd</sup> Edition", John Wiley & Sons.

- B. D. Salvo, C. Gerardi, R. V. Schaijk, S. A. Lombardo, D. Corso, C. Plantamura, T. Serafino, G. Ammendola, M. V. Duuren, P. Goarin, W. Y. Mei, K. V. D. Jeugd, H. Baron, M. Gély, P. Mur, and S. Deleonibus, *IEEE Trans. Device and Materials Reliability*, 4, 377 (2004).

[1.5] Y.-N. Tan, W.-K. Chim, B. J. Cho, and W.-K. Choi, *IEEE Trans. Electron Devices*, 51, 1143 (2004).

[1.6] J. Bu and M. H. White, *Solid-State Electron*. 45, 113 (2001).

- [1.7] M. L. French, C. Chen, H. Sathianathan, and M. H. White, *IEEE Trans.Compon.*, Packag. Manuf. Technol., Part A 17, 390 (1994).

- [1.8] F. R. Libsch and M. H. White, Solid-State Electron. 33, 105 (1990).

- [1.9] C. Lee, S. Hur, Y. Shin, J. Choi, D. Park, and K. Kim, *Proceedings of the*

Conference on Sol. State Dev. Mat. 162 (2002).

- [1.10] S.-H. Lo, D. Buchanan, Y. Taur, and W. Wang, "Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of Ultra-Thin-Oxide nMOSFETs," *IEEE Electron Device Lett.* 18, 209–211 (1997).

- [1.11] D. Frank, R. Dennard, E. Nowak, P. Solomon, Y. Taur, and H.-S. Wong,

"Device Scaling Limits of Si MOSFETs and Their Application Dependencies," *Proc. IEEE* 89, 259–288 (2001).

- [1.12] G.D. Wilk, R.M. Wallace and J.M. Anthony, High-*k* dielectrics: current status and materials properties considerations. *J. Appl. Phys.* **89** (2001), pp.

- [1.13] E.P. Gusev, E. Cartier, D.A. Buchanan, M. Gribelyuk, M. Copel, H. Okorn-Schmodt *et al.*, Ultrathin high-*k* metal oxides on silicon: processing, characterization and integration issues. *Microelectron. Eng.* **59** (2001), pp. 341–349.

- [1.14] S.M. Sze, Evolution of nonvolatile semiconductor memory: from floating-gate to single-electron memory cell. In: S. Luryi, J. Xu and A. Zaslavsky, Editors, *Future trends in microelectronics*, John Wiley & Sons (1999).

- [1.15] I. Fujiwara, H. Aozasa, A. Nakamura and Y. Hayashi, 0.13 μm MONOS single transistor memory cell with separated source lines. *Pros. IEDM* 98 955 (1998), pp. 36.7.1–36.7.4.

- [1.16] S. Minami and Y. Kamigaki, A novel MONOS nonvolatile memory device ensuring 10-year data retention after 10<sup>7</sup> erase/write cycles. *IEEE Trans. Electron Dev.* **40** (1993), pp. 2011–2017.

- [1.17] J. Bu and M.H. White, Design considerations in scaled SONOS nonvolatile memory devices. *Solid State Electron.* 45 (2001), pp. 113–117.

- K.T. Chang, W.M. Chen, C. Swift, J.M. Higman, W.M. Paulson and K.M. Chang, A new SONOS memory using source-side injection for programming.

*IEEE Electron Dev. Lett.* **19** (1998), pp. 253–255.

- [1.19] I. Bloom, P. Pavan and B. Eitan, NROM—a new non-volatile memory technology: from device to product. *Microelectron. Eng.* 59 (2001), pp. 213–223.

[1.20] H.C. Wann and C. Hu, High-endurance ultra-thin tunnel oxide in MONOS

device structure for dynamic memory application. *IEEE Electron Dev. Lett.* **16** (1995), pp. 491–493.

- [1.21] Y.T. Hou,M.F. Li,H.Y. Yu,Y. Jin and D.-L. Kwong, Quantum tunneling and scalability of HfO<sub>2</sub> and HfAlO gate stacks. *IEEE Electron Dev. Meeting IEDM* (2002), pp. 731–734.

- [1.22] Gritsenko VA, Nasyrov KA. Transport and defects in advanced gate

dielectrics. Abstract of Conference "Nano and Giga Challenges in Microelectronics", September 10–13, 2002, Moscow, Russia. p. 131

- [1.23] Lee C, Hur S, Shin Y, Choi J, Park D, Kim K. A novell structure SiO<sub>2</sub>/SiN/ High-k dielectrics, Al<sub>2</sub>O<sub>3</sub> for SONOS type flash memory. Abstract of the 2002 International Conference on Solid State Devices and Materials, 2002, Nagoya, Japan. p. 162

- [1.24] Gritsenko VA, Nasyrov KA, Novikov YuN. A new low voltage fast SONOS memory with High-K dielectrics. Abstract of the 12th Workshop on dielectrics in microelectronics, November 18–29, 2002, Grenoble, France. p. 179.

- [1.25] Gritsenko VA, Nasyrov KA, Novikov YuN. Unpublished.

- [1.26] V. A. Gritsenko, K. A. Nasyrov, Yu. N. Novikov, A. L. Aseev, S. Y. Yoon, Jo-Won Lee, E. -H. Lee and C. W. Kim, A new low voltage fast SONOS memory with high-k dielectric, *Solid-State Electronics* 47 (2003), pp. 1651-1656

- [2.1] D. A. Buchanan, "Scaling the Gate Dielectric: Materials, Integration, and Reliability," *IBM J. Res. & Dev.* 43, 245–264 (1999).

- [2.2] E. P. Gusev, H.-C. Lu, E. L. Garfunkel, T. Gustafsson, and M. L. Green,

"Growth and Characterization of Ultrathin Nitrided Silicon Dioxide Films,"

IBM J. Res. & Dev. 43, 265–286 (1999)

- [2.3] K. Hubbard and D. Schlom, "Thermodynamic Stability of Binary Oxides in Contact with Silicon," J. Mater. Res. 11, 2757 (1996).

- [2.4] E. Gusev, E. Cartier, D. Buchanan, M. Gribelyuk, M. Copel, H.

Okorn-Schmidt, and C. D'Emic, "Ultra High-k Metal Oxides on Silicon: Processing, Characterization, and Integration Issues," *Proceedings of the Conference on Insulating Films on Semiconductors (INFOS)*, 2001.

- [2.5] J. Robertson, "Band Offsets of Wide-Band-Gap Oxides and Implications for Future Electronic Devices," J. Vac. Sci. Technol. B 18, 1785–1791 (2000).

- [2.6] D. Frank, R. Dennard, E. Nowak, P. Solomon, Y. Taur, and H.-S. Wong,

"Device Scaling Limits of Si MOSFETs and Their Application Dependencies," *Proc. IEEE* **89**, 259–288 (2001).

- [2.7] D. Frank and H.-S. P. Wong, "Analysis of the Design Space Available for High-k Gate Dielectric in Nanoscale MOSFETs," *Proceedings of the IEEE Silicon Nanoelectronics Workshop*, 2000, pp. 47–48.

- [2.8] S. M. Sze, *Physics of Semiconductor Devices*, Wiley, New York, 1981

m

[2.9] T. Ning, C. Osburn, and H. Yu, "Emission Probability of Hot Electrons from Silicon into Silicon Dioxide," J. Appl. Phys. 48, 286 (1977).

11111

- [3.1] Marvin H. White, Yang (Larry) Yang, Ansha Purwar, Margaret L. French, "A Low Voltage SONOS Nonvolatile Semiconductor Memory Technology ", *IEEE transactions on components, packaging, and manufacturing technology*—PART A, VOL. 20, NO. 2, JUNE 1997.

- [3.2] Shin-ichi Minami and Yoshiaki Kamigaki, "A Novel MONOS Nonvolatile Memory Device Ensuring 10-Year Data Retention after 107 Erase/Write Cycles ", *IEEE Transactions on Electron Devices*, VOL. 40, NO. 11, NOVEMBER 1993.

[3.3] C. C.-H. Hsu et al., *Exf. Ah. SSDM*, Tsukuba, p. 140.1992.

- [3.4] T. Ohnakado et al., in *IEDM Tech. Dig.*, p. 279.1995.

- [3.5] Jao-Hsian Shiue et. al. "A study of interface trap generation by Fowler-Nordheim and Substrate-hot-carrier stresses for 4-nm thick gate oxides," in IEEE transactions on electron devices, vol. 46, NO.8, August 1999.

- [3.6] O. Takahiro, T. Hiroshi, K. Hayashi, and M. D. K. Kaisha, "Non-volatile semiconductor memory device capable of high speed programming/erasure, U.S. patent no. 5818761,", Oct. 6, 1998.

- [3.7] D. P. Shum *et al.*, "A novel band-to-band tunneling induced convergence mechanism for low current, high density Flash EEPROM applications," in *IEDM Tech. Dig.*, 1994, pp. 41–44.

- [3.8] C.-Y. Hu. *et al.*, "Substrate-current-induced hot electron (SCIHE) injection: A new convergence scheme for Flash memory," in *IEDM Tech. Dig.*, 1995, pp. 283–287.

- [3.9] T. S. Chen, K. H. Wu, H. Chung, and C. H. Kao, "performance improvement of SONOS memory by bandgap engineer of charge-trapping layer", *IEEE Electron. Device Lett.*, vol.25, no.4, pp. 205-207, Apr. 2002.

- [3.10] Marvin H. White, Yang (Larry) Yang, Ansha Purwar, Margaret L. French, "

A Low Voltage SONOS Nonvolatile Semiconductor Memory Technology ",

*IEEE transactions on components, packaging, and manufacturing*

technology—PART A, VOL. 20, NO. 2, JUNE 1997.

- [3.11] T. Sugizaki, M. Kohayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, "Novel Multi-bit SONOS Type Flash Memory Using a Highk Charge Trapping Layer", Symposium on VLSI Technology Digest of Technical Papers 2003.

- [3.12] Marvin H. White, Dennis A. Adams, James R. Murray, Stephen Wrazien, Yijie (Sandy) Zhao, Yu (Richard) Wang, Bilal Khan, Wayne Miller, Rajiv Mehrotra1, "Characterization of Scaled SONOS EEPROM Memory Devices for Space and Military Systems", *IEEE* 2004.

- [3.13] G. D. Wilk, R. M. Wallace, J. M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations ", *Applied Physics Review*, vol.89, no.10,pp.5243-5275, May 2001.

- [3.14] T. Ohnakado *et al.*, "Novel electron injection method using band-to-band tunneling induced hot electron (BBHE) for Flash memory with a p-channel cell," *IEDM Tech. Dig.*, pp. 279–282, 1995.

- [3.15] C.-G. Hwang: Proc. IEEE 91 (2003) 1765.

- [3.16] K. Kim, J. H. Choi, J. Choi and H.-S. Jeong: VLSI Technology (VLSITSA-Tech), 2005, p. 88.

- [3.17] J.-H. Park, S.-H. Hur, J.-H. Lee, J.-T. Park, J.-S. Sel, J.-W. Kim, S.-B. Song,

J.-Y. Lee, J.-H. Lee, S.-J. Son, Y.-S. Kim, M.-C. Park, S.-J. Chai, J.-D. Choi,

U.-I. Chung, J.-T. Moon, K.-T. Kim, K. Kim and B.-I. Ryu: IEDM Tech.

Dig., 2004, p. 873.

- [3.18] M. H. White, D. A. Adams and J. Bu: IEEE Circuits Devices 16 (2000).

- [3.19] S.-I. Minami and Y. Kamigaki: IEEE Trans. Electron Devices 40 (1993) 2011.

- [3.20] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park and K. Kim: IEDM Tech. Dig., 2003, p. 26.5.1.

# 簡歷

- 姓名: 顧春瑀

- 性 別: 男

- 出生日期: 中華民國七十一年二月十一日

- 籍 貫: 安徽省 懷遠縣

- 地 址: 桃園縣桃園市豐林里 11 鄰三和街 74 巷 2 弄 3 號

- 學 歴: 國立臺灣大學 地理環境資源學系

(民國95年6月)

國立交通大學 電子研究所固態組 碩士班

(民國97年8月)

論文題目: 利用高介電長數 HFAIO 之元素含量做為阻擋層應用在非揮發性

Study on High-k Gate dieletric Hf1-xA1xO for Blocking layer of SONOS

Non-Volatile Memory

記憶體上之研究

電子郵件: springrain@mail2000.com.tw