## 國立交通大學

## 電子工程學系電子研究所

碩 士 論 文

應用於無線近身網路之嵌入式晶體振盪器

An Embedded Crystal Oscillator for Wireless Body Area Network Applications

研究生: 黃上賓

指導教授:李鎮宜博士

中華民國九十七年八月

#### 應用於無線近身網路之嵌入式晶體振盪器

#### **An Embedded Crystal Oscillator for**

#### **Wireless Body Area Network Applications**

研究生: 黃上賓 Student: Shang-Bin Huang

指導教授: 李鎮宜博士 Advisor: Dr. Chen-Yi Lee

Submitted to Department of Electronics Engineering & Institute Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of Requirements

for the Degree of Master

in

**Electronics Engineering**

August 2008

Hsinchu, Taiwan, Republic of China

中華民國 九十七 年 八 月

#### 應用於無線近身網路之嵌入式晶體振盪器

研 究 生: 黃上賓 指導教授: 李鎮宜教授 國立交通大學電子工程學系電子研究所

#### 摘要

在本篇論文裡,我們介紹一個應用於無線近身網路的嵌入式晶體振盪器和基頻低功率設計流程,來降低整個系統的功率消耗和面積使用。

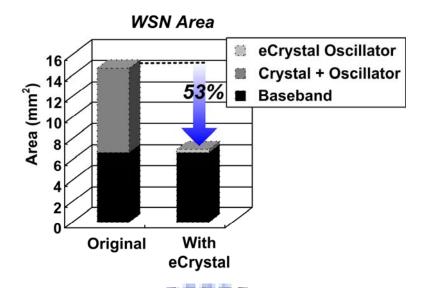

近年來,健康照護的系統應用於無緣近身網路愈來愈受到人們的重視,尤其是針對人體生醫訊號的偵測。在這樣的應用中,可以從配戴在身上的無線感測器對人體訊號做長時間的偵測,並以無線的方式將資料傳送給整合在手機或個人數位助理的接收端。基於這樣的一個應用,極低的功率消耗跟高度整合的面積會是系統不可或缺的需求。我們使用了低功率的設計流程來降低整個基類的功率消耗,儘管整個基類的功率消耗已經非常低。但從整個系統來看,我們可以發現功率消耗主要由晶片外部的一些元件佔非常大的部份,像是石英晶體與其搭配使用的振盪器。不僅如此,這些晶片外部的元件同樣佔據了相當大的面積使用,對整個系統造成額外的負擔,於是嵌入式晶體振盪器[1]被提出來取代這些晶片外部所使用元件。嵌入式晶體振盪器是藉由互補金氧半導體製程的方式,將晶體振盪器整合進單一晶片中,如此一來可以大大地降低系統的製造成本、面積及功率消耗。在本篇論文我們對整個嵌入式晶體振盪器的行為做一個詳盡的關述,並分析頻率校準的設計,最後建立了一個嵌入式晶體振盪器的原型來驗證這樣的行為。藉由使用嵌入式晶體振盪器以及基頻的低功率設計流程,整個系統將可以降低 73%的功率消耗和 53%的面積使用。

## An Embedded Crystal Oscillator for Wireless Body Area Network Applications

Student: Shang-Bin Huang Advisor: Chen-Yi Lee Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University

#### Abstract

In this thesis we propose an Embedded Crystal (eCrystal) oscillator and baseband low power design flow for Wireless Body Area Network (WBAN) applications to assure the overall system power and area reduction.

In the recent years, people have attached great importance to healthcare monitoring system for WBAN applications. There are multiple wireless sensor nodes (WSNs) placed on the human body for long-time monitoring. The WSNs transmit data wirelessly to a central processing node (CPN) integrated into mobile phones or personal digital assistants (PDAs). Ultra-low power and tiny integrated area are the features required in such applications. A low power design flow comprising Multiple Supply Voltage (MSV) and power gating is used to reduce baseband power consumption. However, the overall system power is dominated by some off-chip components, e.g. quartz crystal and oscillator. Besides, these external components also occupy very large system area. Therefore, an eCrystal oscillator [1] has been proposed to replace these external components, and this can largely reduce manufacturing cost, system area, and power consumption. We elaborate and analyze the frequency error calibration of eCrystal oscillator and establish the prototype platform to verify the system behavior with eCrystal oscillator. By the use of eCrystal oscillator and baseband low power design flow, the system will have 73% power reduction and 53% area reduction.

#### 誌謝

在 Si2 實驗室的碩士班研究過程中,讓我學到了非常多的東西。其中要感謝我的指導教授李鎮宜博士,他提供了非常完善的研究環境與資源,使我們能夠從系統的各個層面來發展及實現研究的方向。還有要感謝實驗室的鍾菁哲學長、游瑞元學長,在碩士班裡給我的關心與指導,也要感謝實驗室的同學及學弟妹們:余建螢、陳燦文、陳俊廷、郭冠麟、宋偉豪、馬曉涵,他們在我困惑時經常地提供意見與幫助。另外還要感謝我的家庭給予的關心與鼓勵。在大家的支持下,我才能順利地完成碩士學業,最後感謝口試

#### **CONTENTS**

## **CONTENTS**

| $P_{\Delta}$ | GF |

|--------------|----|

| IA           | UL |

| Chapter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

| 1-1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  |

| 1-2 Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5  |

| Chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6  |

| Low Power Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  |

| 2-1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

| 2-1-1 Multiple Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  |

| 2-1-2 Power Gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7  |

| 2-2 Low Power Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

| 2-3 Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 |

| The state of the s |    |

| The state of the s | 13 |

| - 100 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16 |

| Appropriate the property of th |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20 |

| Analysis of Embedded Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |

| 3-1 System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 |

| 3-2 System Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

| 3-3 Frequency Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24 |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

| Emulation of Embedded Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4-1 Building Block Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 4-1-1 Transmitter Node and Remote Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 4-1-2 Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4-1-3 Frequency Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4-1-4 A/D and D/A Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

#### **CONTENTS**

| 4-2 Case Studies                              | 39 |

|-----------------------------------------------|----|

| 4-2-1 Frequency Shift Keying Applications     | 39 |

| 4-2-2 Wireless Body Area Network Applications | 43 |

| Chapter 5                                     | 50 |

| Conclusions and Future Work                   | 50 |

| 5-1 Conclusions                               | 50 |

| 5-2 Future Work                               | 50 |

| References                                    | 52 |

| Appendix                                      | 54 |

| Appendix                                      | 54 |

## LIST OF FIGURES

*PAGE*

| Figure 1-1: Target operation scenario for WBAN applications                                                                                                                  | 2  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: The Quartz crystal used in a wireless electrocardiogram (ECG) patch (source:                                                                                     |    |

| IMEC)                                                                                                                                                                        | 3  |

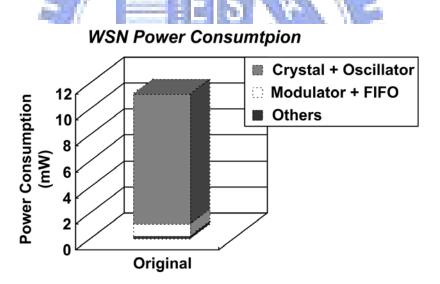

| Figure 1-3: The power consumption of WSN                                                                                                                                     | 4  |

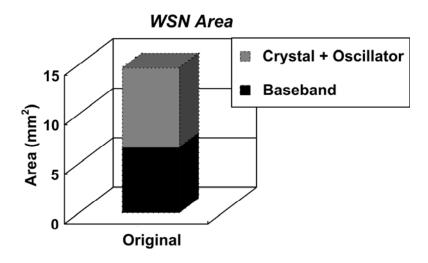

| Figure 1-4: The area of WSN                                                                                                                                                  | 5  |

| Figure 2-1: Footer and Header fine-grain power gating implementation in NAND gate                                                                                            | 8  |

| Figure 2-2: Header coarse-grain power gating implementations                                                                                                                 | 8  |

| Figure 2-3: Ring style sleep transistor implementations                                                                                                                      | 9  |

| Figure 2-4: Column style power gating implementations                                                                                                                        | 9  |

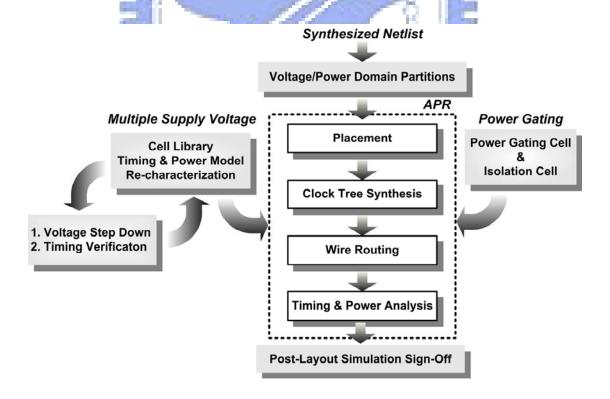

| Figure 2-5: The low power design flow for baseband chip implementation                                                                                                       | 10 |

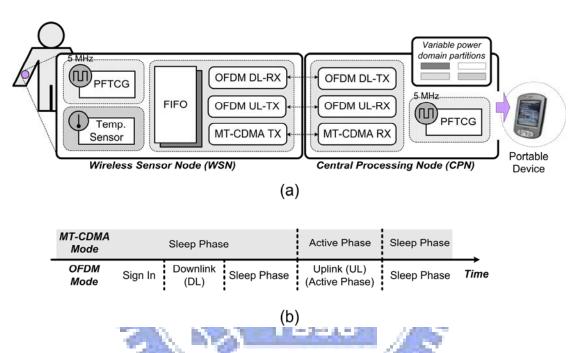

| Figure 2-6: The dual-mode baseband transceiver with (a) abstract view of functional block and (b) behavior time line                                                         |    |

| Figure 2-7: The transceiver block diagram with power domain planning (a) wireless sensor node (WSN); (b) central processing node (CPN); (c) power management cell; (d) power | r  |

| management control sequence                                                                                                                                                  | 12 |

| Figure 2-8: The coarse-grain and column style power gating applied in this work                                                                                              | 13 |

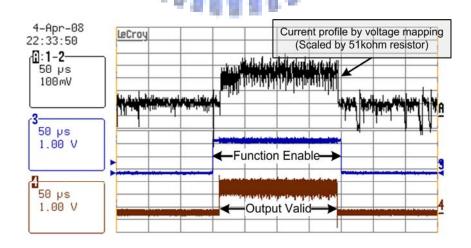

| Figure 2-9: Current profile between sleep and active state                                                                                                                   | 17 |

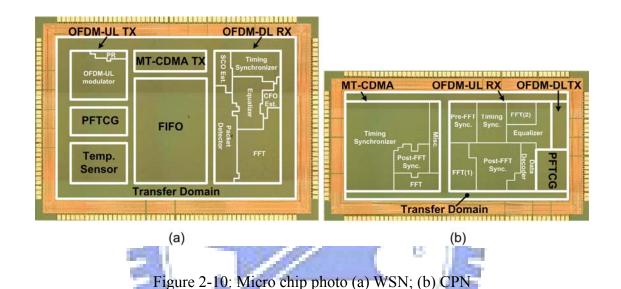

| Figure 2-10: Micro chip photo (a) WSN; (b) CPN                                                                                                                               | 18 |

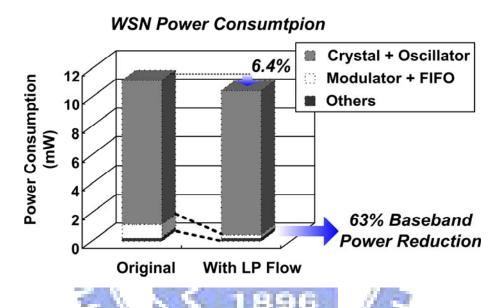

| Figure 2-11: The power consumption of WSN with low power design flow                                                                                                         | 19 |

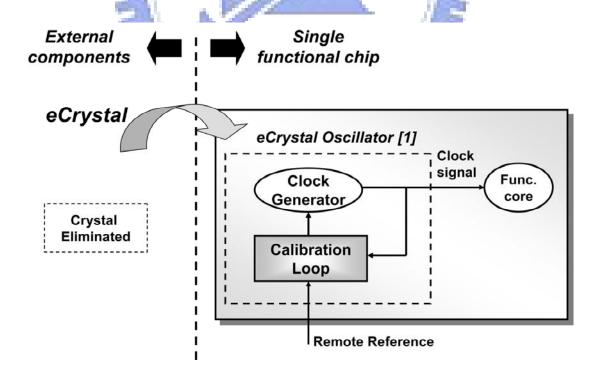

| Figure 3-1: The concept of eCrystal oscillator                                                                                                                               | 20 |

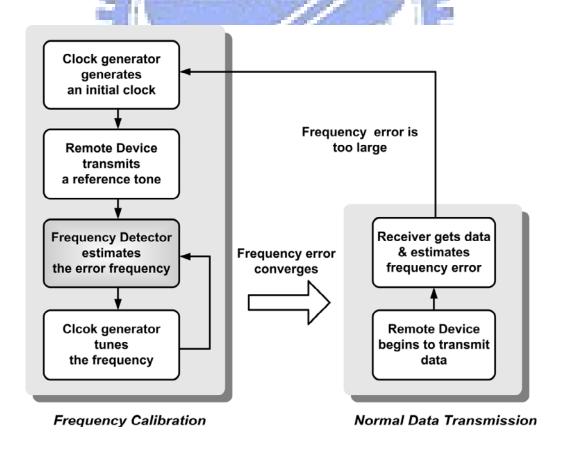

| Figure 3-2: The operation flow of eCrystal system.                                                                                                                           | 21 |

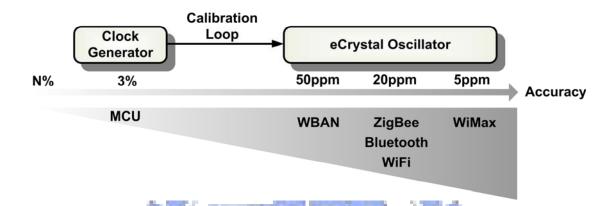

| Figure 3-3: The accuracy of eCrystal oscillator for possible different applications                                                                                          | 22 |

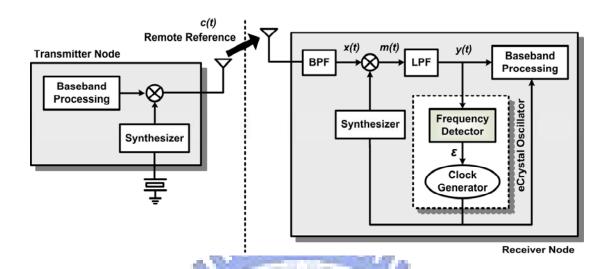

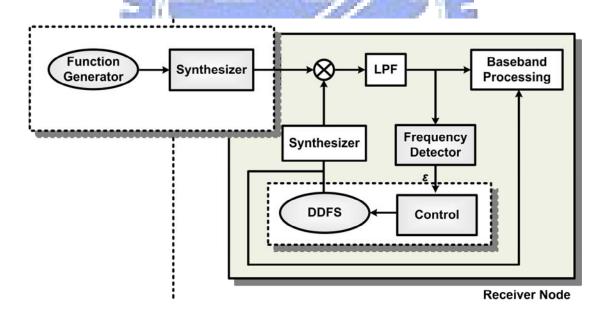

| Figure 3-4: Block diagram of the eCrsytal oscillator system                                                                                                                  | 23 |

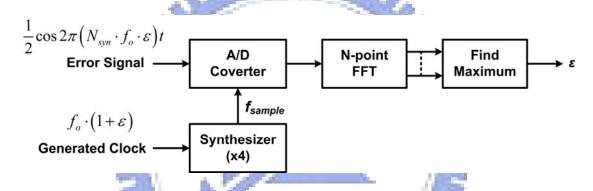

| Figure 3-5: The FFT-based frequency detector                                                                                                                                 | 25 |

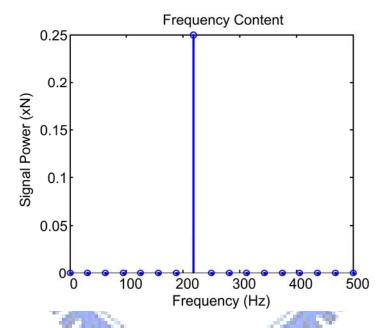

| Figure 3-6: The signal power of the best-case FFT detection                                                                                                                  | 26 |

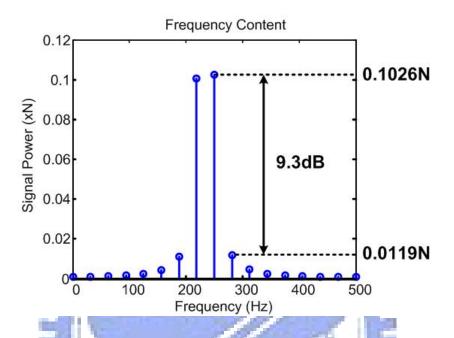

| Figure 3-7: The signal power of the worst-case FFT detection                                                                                                                 | 27 |

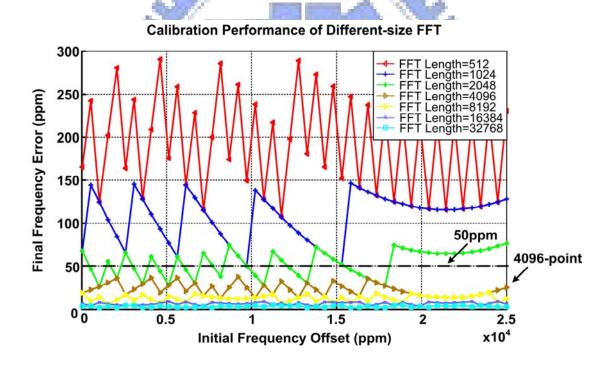

| Figure 3-8: The calibration performance of different-size FFT                                                                                                                | 28 |

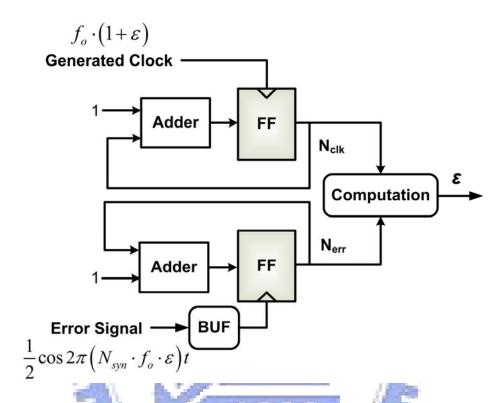

| Figure 3-9: The architecture of counter-based frequency detector                                                                                                             | 29 |

#### LIST OF FIGURES

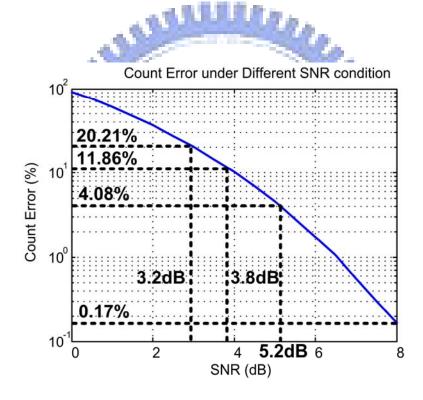

| Figure 3-10: The counting error under different SNR conditions                                                   | . 32 |

|------------------------------------------------------------------------------------------------------------------|------|

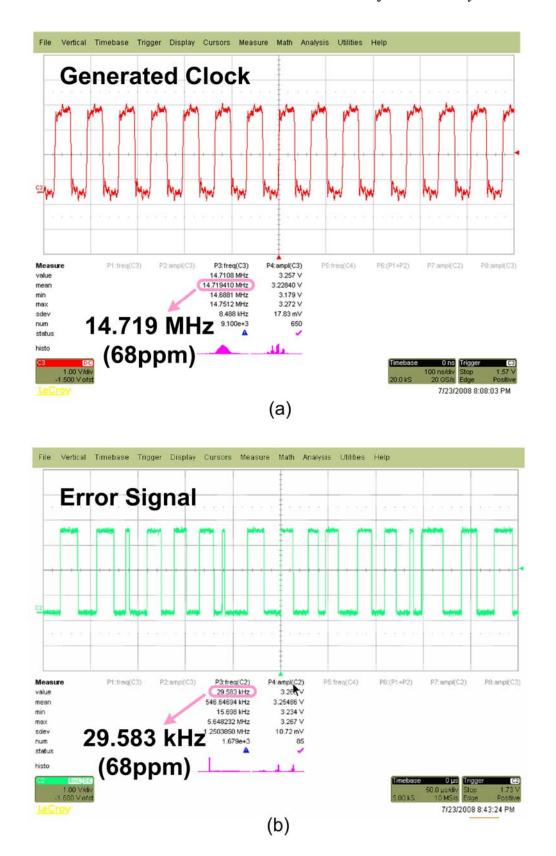

| Figure 4-1: Block diagram of the eCrystal emulation platform                                                     | . 35 |

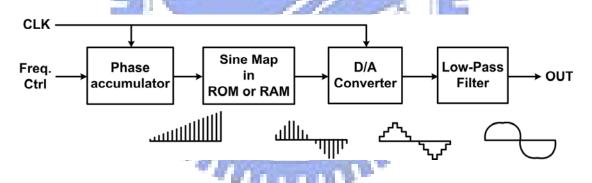

| Figure 4-2: Block diagram of the DDFS                                                                            | . 36 |

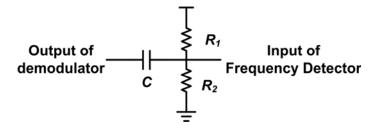

| Figure 4-3: The analog-to-digital bias circuit.                                                                  | . 38 |

| Figure 4-4: The eCrystal oscillator prototype for FSK applications                                               | . 40 |

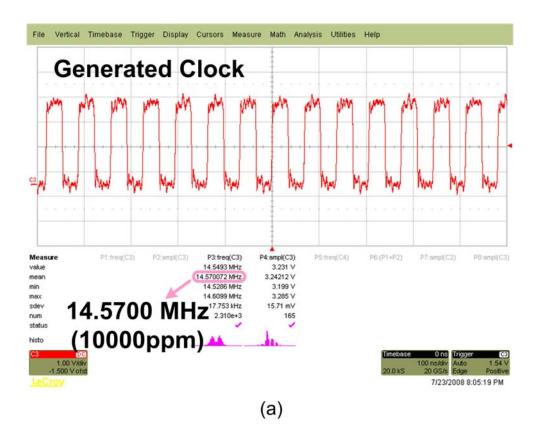

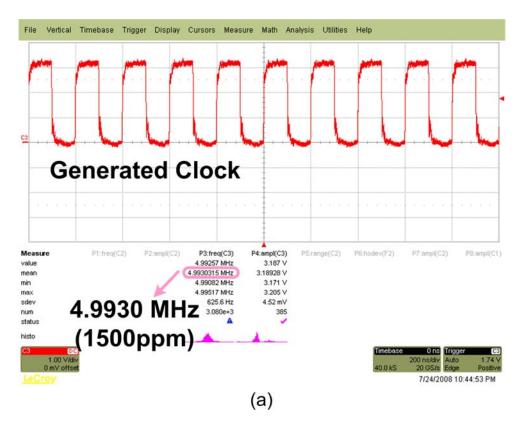

| Figure 4-5: The initial case of eCrystal oscillator for FSK applications (a) Generated Clock Error Signal        |      |

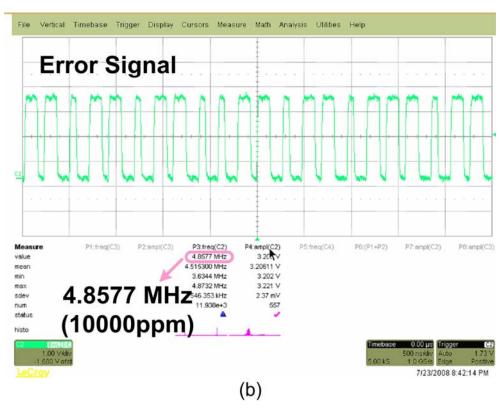

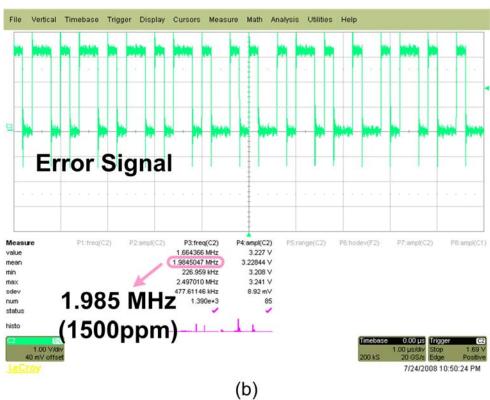

| Figure 4-6: The final results of eCrystal oscillator for FSK applications (a) Generated Clock (b) Error Signal   |      |

| Figure 4-7: The eCrystal oscillator prototype for WBAN applications                                              | . 44 |

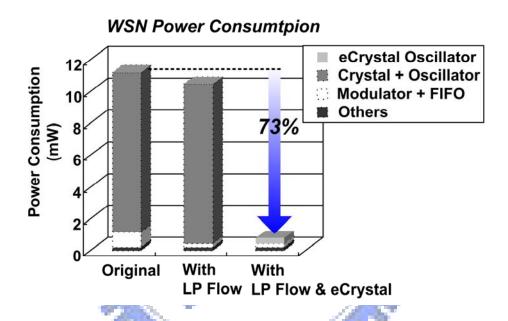

| Figure 4-8: The initial case of eCrystal oscillator for WBAN applications (a) Generated Cl (b) Error Signal      |      |

| Figure 4-9: The final results of eCrystal oscillator for WBAN applications (a) Generated Clock; (b) Error Signal | . 46 |

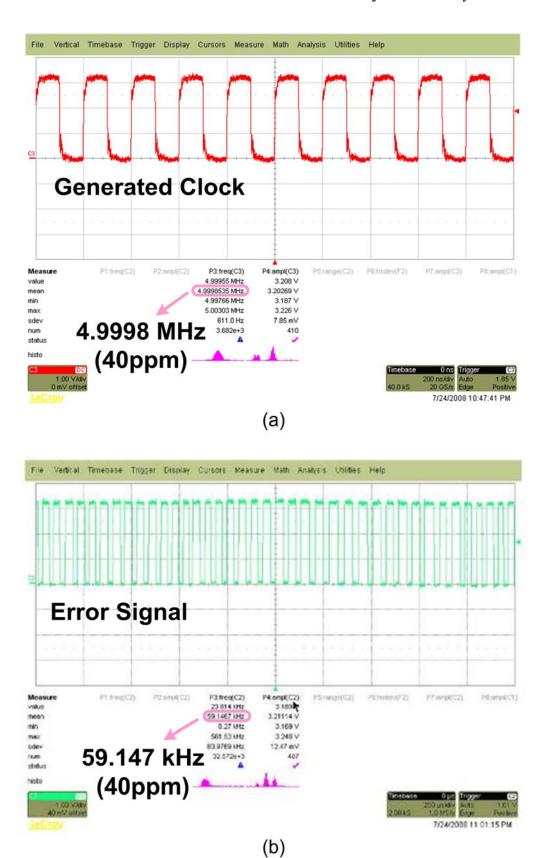

| oscillator                                                                                                       | . 48 |

| Figure 4-11: The area of WSN with low power design flow and eCrystal oscillator                                  | . 49 |

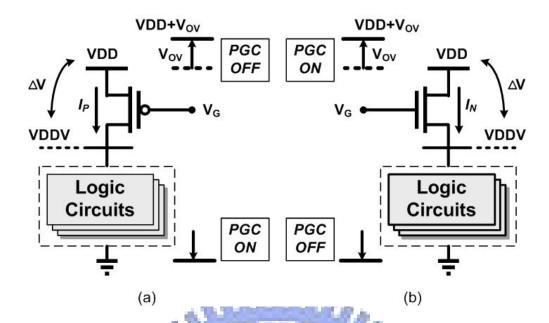

| Figure A-1: Power gating cell operation mechanism (a) PMOS header; (b) NMOS header                               | . 55 |

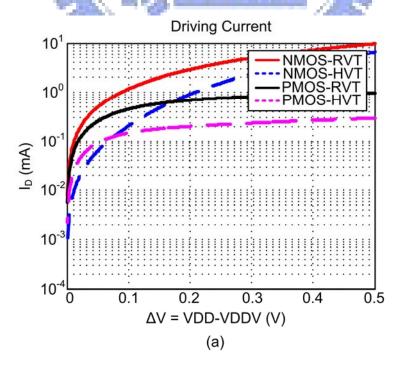

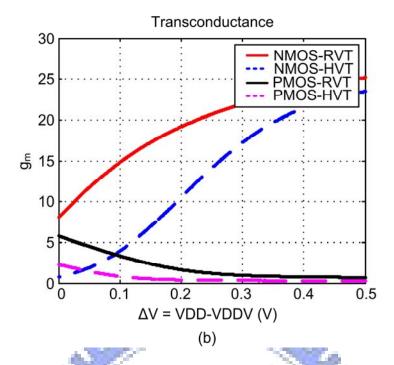

| Figure A-2: NMOS: $V_D(0.5V) + V_G(0.9V)$ and PMOS $V_S(0.5V) + V_G(0V)$ (a) driving currer (b) transconductance |      |

| Figure A-3: Testing circuit                                                                                      | . 59 |

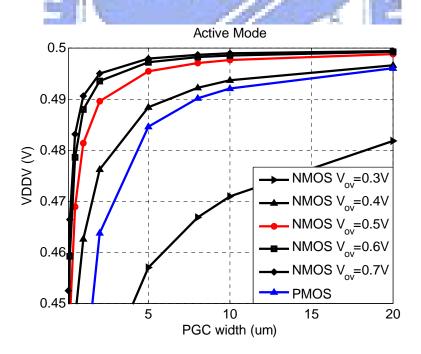

| Figure A-4: VDDV pulled by PGC in the active state                                                               | . 60 |

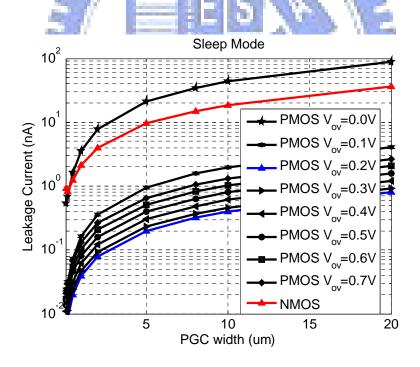

| Figure A-5: Leakage current in the sleep state                                                                   | . 61 |

#### LIST OF TABLES

## LIST OF TABLES

| $D_{I}$ |            | T  |

|---------|------------|----|

| PA      | <b>(</b> 7 | r, |

| Table 1-1: The power consumption, area, and cost of the quartz crystal [2]           | 3       |

|--------------------------------------------------------------------------------------|---------|

| Table 2-1: Chip core power in WSN and CPN chipset                                    | 17      |

| Table 2-2: Chip Summary                                                              | 18      |

| Table 3-1: The specification of eCrystal oscillator                                  | 22      |

| Table 3-2: The counting error requirement when different number of detection/calibra | tion is |

| applied                                                                              | 32      |

| Table 3-2: Comparisons of FFT-based and counter-based frequency detector             | 34      |

| Table 4-1: The emulation results of eCrystal oscillator for WBAN applications        |         |

| Table 4-2: The power consumption and area of eCrystal oscillator [13]                | 48      |

## Chapter 1

#### Introduction

#### 1-1 Motivation

With the increase of the world's elderly population and modern work pressure, the population of various cardiovascular and other chronic diseases increases rapidly, and the age decreases year by year. In medical institutions, many sensors of physiological monitoring equipments were placed in patients and transmit signals to display devices by electric wires. Except testers feel uncomfortable by those wires, it is more dangerous to cause wires peeling when they shift beds or turn the bodies over. Besides, many physiological signals demand long-term and continuous monitoring. Therefore, the wireless transmission of physiological is more and more important for medical staff and patients.

1896

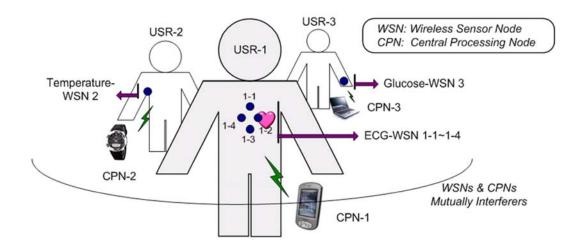

In the Wireless Body Area Network (WBAN) applications, the goal of ubiquitous healthcare monitoring is to extend the physiological monitoring from the closed in-hospital environment to any open roaming spaces. The target operation scenario is illustrated in Figure 1-1, there are multiple wireless sensor nodes (WSNs) placed on the human body. Each WSN can perform physiological data sensing and processing, and transmit the data wirelessly to a central processing node (CPN) which may be integrated into a mobile phone or a personal digital assistant (PDA).

1

Figure 1-1: Target operation scenario for WBAN applications

To achieve this ubiquitous healthcare monitoring in the WBAN applications, the system must provide highly reliable signal exchanges between the WSNs and CPN so that doctors will not make mistakes when estimating the patients' condition. In addition to the reliability issue, the system, especially the WSN, is required to have ultra-low power (µW-level) with highly integrated tiny area. Smaller size not only reduces the manufacturing cost but also provide the convenience and portability. And the physiological signals usually need long-term and continuous monitoring to observe if there is something abnormal. Also, the working energy will be provided by the batteries with limited energy. Therefore, ultra-low power consumption is required for this system.

Figure 1-2 shows the quartz crystal used in a wireless electrocardiogram (ECG) patch. The quartz crystal plays an important role in the existing system to provide a reference clock, and usually needs extra passive components or a silicon oscillator pad to generate the reference clock frequency. This configuration has large overhead on power consumption (mW-level), area occupation, and manufacturing cost, as shown in Table 1-1 [2].

Figure 1-2: The Quartz crystal used in a wireless electrocardiogram (ECG) patch

(source: IMEC)

Table 1-1: The power consumption, area, and cost of the quartz crystal [2]

| Power       | In-crystal | 1μW~200μW                             |

|-------------|------------|---------------------------------------|

| consumption | Oscillator | 1mW~50mW (active) 10μW~50μW (standby) |

| Area        | SMD        | 3.2mm x 2.5mm x 0.5mm                 |

| Alea        | DIP        | 11.5mm x 4.7mm x 3.5mm                |

| C           | ost        | US\$0.15~2                            |

Figure 1-3 and Figure 1-4 show the power consumption and area of the WSN, exclusive the analog-to-digital converter (ADC). Except the baseband power consumption, the use of quartz crystal and oscillator occupy very large part of the WSN. Therefore, we apply low power design flow to achieve μW-level baseband power consumption. However, the off-chip components consume much more power and dominate the overall system power consumption. As a result, an Embedded Crystal (eCrystal) oscillator [1] has been proposed to replace these external

components, which includes quartz crystal, oscillator, resistors, and capacitors, by a tunable process, voltage, and temperature (PVT) tolerance clock generator [3] with frequency error calibration. The clock generator is designed with limited initial frequency offset, say 3%, under any process, voltage, and temperature (PVT) variations, and the calibration loop provides a clock mismatch recovery to improve fine-tuning frequency error. With the eCrystal oscillator which can be integrated in standard CMOS process, the external components can be eliminated, and this results in large system area and manufacturing cost reduction. In this thesis the hardware design and system behavior of the eCrystal oscillator will be discussed and analyzed. And the prototype platform is established to verify the behavior of the eCrystal oscillator.

Figure 1-3: The power consumption of WSN

4

Figure 1-4: The area of WSN

#### 1-2 Organization

In this thesis, we use the baseband low power design design flow and eCrystal oscillator to reduce overall system power consumption and area usage. In the following chapters, the detailed design process and principle will be presented clearly.

In Chapter 2, the low power design flow applied for baseband chip implementation is presented.

In Chapter 3, the system behavior of eCrystal oscillator is described, and the architecture of frequency error calibration to improve fine-tuning frequency error is discussed and formulated.

In Chapter 4, the emulation design of building blocks in the eCrystal oscillator is discussed, and two prototypes for WBAN and FSK applications are demonstrated.

Finally, in Chapter 5, we summarize the conclusions and present the future work.

## Chapter 2

## Low Power Design Flow

In this chapter the low power techniques including Multiple Supply Voltage (MSV) and power gating will be introduced and applied to the low power design flow for baseband chip implementation.

#### 2-1 Background

#### 2-1-1 Multiple Supply Voltage

Multiple Supply Voltage (MSV), which is also called Voltage Island [4], is an effective power reduction technique, which operates different blocks at different voltages.

In previous generations, large functional blocks were not integrated in the single chip, so that the supply voltage of each block could be made independently. As advance of process technology, the chip capacity is increasing; therefore, more and more functional units will be integrated into the single chip, which is called System-on-Chip (SoC). These different functional blocks on the chip may have different performance requirements; hence MSV is used to lower down the voltage level of each block while maintaining the performance requirements.

To implement MSV on a system, the power domain partition should be defined in the front end, and created during the floor-planning stage of physical design for the following placement and optimization. In the MSV implementation, every signal that crosses different power domains requires a level shifter to convert one voltage level to another. Although level shifting from a higher-voltage power domain to a lower one is usually optional, level shifting from a lower-voltage power domain to a higher one is necessary. Besides, the size of level shifter should be chosen carefully to ensure the signal integrity when crossing different power domains.

#### 2-1-2 Power Gating

Power gating comes from Multi-threshold CMOS (MTCMOS) technique [5-6], which is very effective for reducing leakage current in the sleep state. The concept of MTCMOS is to use both high- $V_T$  and low- $V_T$  devices on a chip. High- $V_T$  devices can be used for leakage current reduction while low- $V_T$  devices can be used for higher performance requirement. Furthermore, MTCMOS involves using high- $V_T$  transistors to gate power supplies of a low- $V_T$  logic circuit. When the high- $V_T$  transistors are turned on, the low- $V_T$  logic block is connected to power supplies and goes to active state. When the low- $V_T$  logic circuit enters the sleep state, the high- $V_T$  transistors are turned off for leakage current reduction.

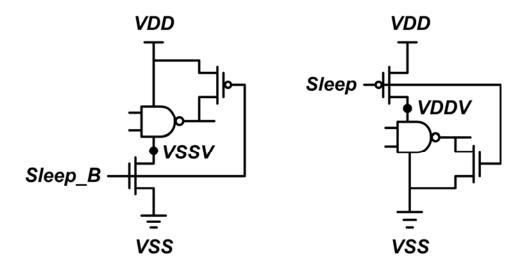

From another point of view, using MTCMOS technique in every standard cell is also called fine-grain or cell-based power gating implementation [7], as shown in Figure 2-1. The advantage of the fine-grain power gating implementation is that the virtual power rails are short and hidden in the cell. However, the power switches which are added in every standard cell result in significant area overhead. Moreover, the normal standard cells provided by library vendors and ASIC foundries can not be used. What's more important issue is that the built-in power switch is subject to PVT variation, which results in added IR-drop variation, or performance variation, in the cell.

Figure 2-1: Footer and Header fine-grain power gating implementation in NAND gate

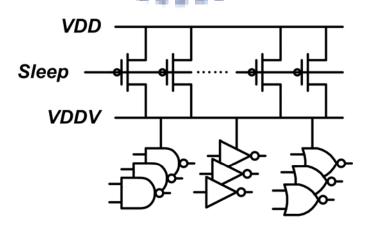

On the other hand, in the coarse-grain or distributed power gating implementation [7], which is shown in Figure 2-2, the power switches are connected between the real power rail and the virtual power rail networks. The main advantage of the coarse-grain power gating implementation is that all power switches can share charge/discharge current. Consequently, it is less sensitive to PVT variation and also less IR-drop variation compared with the fine-grain power gating implementation. Moreover, the area overhead is significantly smaller due to the charge sharing among the power switches.

Figure 2-2: Header coarse-grain power gating implementations

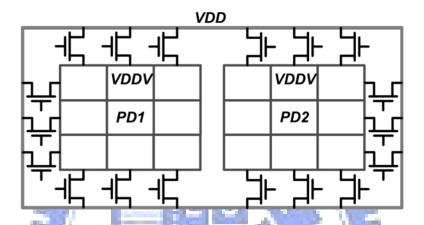

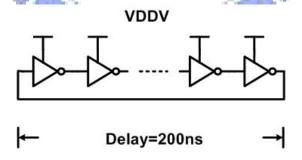

In addition to fine/coarse-grain power gating, the ring/column style is also an important issue for power gating implementation. The ring style power network shown in Figure 2-3 has less complexity on Auto Place and Route (APR) flow but worse IR-drop performance because the real power line is far from the center of the power domain.

Figure 2-3: Ring style sleep transistor implementations

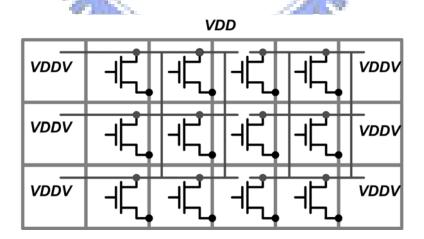

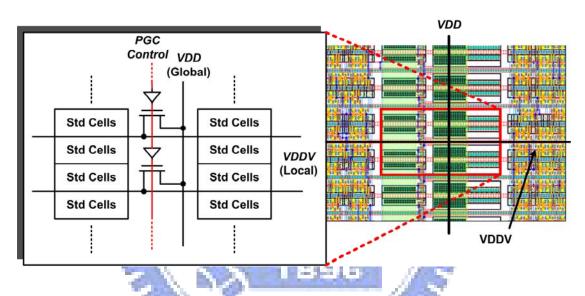

On the other hand, the column style power network shown in Figure 2-4 has better IR-drop performance but is more complex on APR flow.

Figure 2-4: Column style power gating implementations

#### 2-2 Low Power Design Flow

Based on the typical cell-based design flow, the low power techniques including MSV and power gating are added to achieve low power design, as shown in Figure 2-5. Before the APR, the voltage/power domain partitions must be defined first to apply MSV and power gating. To apply voltage-scaling approach in MSV technique, the timing and power models of cell libraries provided from the foundries should be re-characterized. And every time the supply voltage is stepped-down, the timing of standard cell must be verified to assure the functionality. In the power gating technique, the power gating cell (PGC) is added to turn ON/OFF the power domain and the isolation cell is used to isolate the power domain during the sleep state. After the APR flow, the post-layout simulation is performed to sign-off the overall low power design.

Figure 2-5: The low power design flow for baseband chip implementation

#### 2-3 Implementations

The 0.5V 7Mbps baseband transceiver chipset, consists of WSN and CPN, is designed for WBAN applications. The system block diagram and behavior time-line are illustrated in Figure 2-6. The baseband processor provides both MT-CDMA and OFDM modes for different data rate requirements.

Figure 2-6: The dual-mode baseband transceiver with (a) abstract view of functional blocks and (b) behavior time line

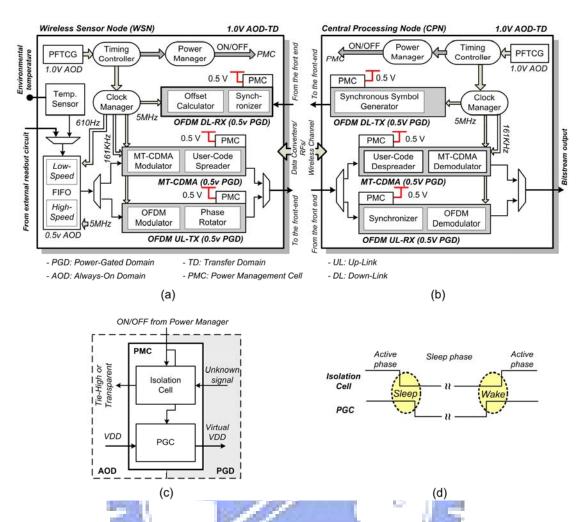

The low power design flow, including MSV and power gating, is applied for this baseband chip implementation to reduce both dynamic and static power consumptions, as illustrated in Figure 2-7.

Figure 2-7: The transceiver block diagram with power domain planning (a) wireless sensor node (WSN); (b) central processing node (CPN); (c) power management cell; (d) power management control sequence

# 2-3-1 Voltage/Power Domain Partitions

This system is partitioned into 12 power domains, which are designed with different supply voltages to reduce total power consumption. In this baseband transceiver chipset, the main functional blocks are operated at 0.5V according to the required performance and achievable functionality. Except for the main functional blocks, there are several special functional blocks, Phase and Frequency Tunable Clock Generator (PFTCG) and Temperature Sensor (TS), which are designed at 1.0V. Moreover, a transfer-domain (TD) including the control units is defined and operated

at 1.0V to be an interface between the functional blocks and I/O pads.

#### 2-3-2 Power Gating Implementation

Considering the large area overhead and higher PVT sensitivity of fine-grain power gating and larger IR-drop of ring style power gating, the coarse-grain and column style power gating implementation is applied in this work, as shown in Figure 2-8.

Figure 2-8: The coarse-grain and column style power gating applied in this work

Moreover, there are different characteristics for different types of power switches. For example, PMOS transistor is less leaky than NMOS transistor of a same size, while NMOS transistor has higher drive current than PMOS transistor of a same size and hence small area overhead [7]. And this comparison will be discussed in the Appendix.

#### 2-3-3 Power Gating and Isolation Timing Control