# 國立交通大學

## 電子工程學系 電子研究所碩士班

## 碩士論文

WiMAX通道編碼技術與

數位訊號處理器實現之探討

E 5

Study in WiMAX Channel Coding Techniques and Associated Digital Signal Processor Implementation

研究生:陳佳楓

指導教授:林大衛 博士

中華民國九十七年六月

### WiMAX 通道編碼技術與

### 數位訊號處理器實現之探討

# Study in WiMAX Channel Coding Techniques and Associated Digital Signal Processor Implementation

研究生: 陳佳楓

Student: Jia-Fong Chen

指導教授:林大衛 博士

Advisor: Dr. David W. Lin

Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Master of Science in

Electronics Engineering June 2008 Hsinchu, Taiwan, Republic of China

中華民國九十七年六月

### WiMAX 通道編碼技術與

### 數位信號處理器實現之探討

研究生:陳佳楓

指導教授:林大衛 博士

### 國立交通大學

電子工程學系 電子研究所碩士班

#### 摘要

### a shiller.

IEEE 802.16e 無線通訊標準中,於系統的傳送端訂定了前向誤差改正編碼的機制,藉此減低通訊頻道中雜訊失真的影響。通道編碼是本論文的重點。

本篇論文前半部份重點在於,研究 IEEE 802.16e OFDMA 所訂定的迴旋編碼(咬 尾)系統並且實現在德州儀器公司所發展數位訊號處理器(DSP) TMS320C6416上的維 特比解碼協處理器(VCP)並針對咬尾編碼的特性,中斷服務常式(ISR)以及增強型直接 記憶體存取(EDMA)進行研究。此外我們也利用 3L Diamond 的 EDMA 進行 VCP 在多 個 DSP 運算處理的應用。在論文中,我們利用 C 語言所模擬的迴旋碼在加成性白色 高斯通道下和利用 VCP 應用於迴旋碼進行效能及速度上的比較。在效能錯誤率上, 受限於實點數及 VCP 輸入位元數的硬體條件下,若以相同條件比較而言,兩者的效 能是接近的。而在速度方面,經過在 DSP 平台上最佳化我們的程式後,分別於 CCS 模 擬器和 3L 測量上,迴旋編碼的編碼器部份,可以到每秒 16,667K 和 3,764K 位元的處 理速度,而在 VCP 方面解碼器的部份可以達到每秒 7,897K 和 2,997K 位元的處理速 度,C 語言模擬方面則可以達到每秒 805K 和 632K 位元的處理速度。簡而說之,若 以解碼器觀點而言,VCP 提升了速度為 9.8 和 4.7 倍,分別針對 CCS 模擬器和 3L Diamond 測量而得到數據。

本論文後半部份重點,研究 IEEE 802.16e OFDMA 所訂定的渦輪迴旋碼(CTC)系統並且實現在數位訊號處理器。闡明渦輪迴旋碼的雙二位元循環遞迴系統迴旋(duo-binary CRSC)編碼與最大對數事後機率(max-log MAP)解碼演算法。我們利用 C 語言驗證系統演算法上的正確性,並在加成性白色高斯通道下模擬了各種調變。接著在 TI C6416 DSP 平台實現,於 3L Diamond 測量上方面,編碼器部份可以到每秒 8,223 位元的處理速度,而解碼器的部份僅可以達到每秒 30K 位元的處理速度。之後我們對於解碼器做了一些最佳化的改善,使解碼器的速度增進約 10 倍,進而可以達到每秒 300K 位元的處理速度。

# Study in WiMAX Channel Coding Techniques and Associated Digital Signal Processor Implementation

Student: Jia-Fong Chen

Advisor: Dr. David W. Lin

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

### Abstract

## and the second

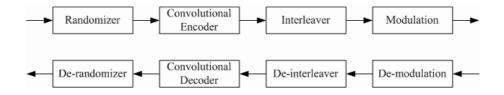

In the IEEE 802.16e wireless communication standard, a *f*orward *e*rror *c*orrection (FEC) mechanism is presented at the transmitter side to reduce the noisy channel effect. The focus is on the channel coding.

The focus of the fist part of this thesis is the research of the convolutional code (CC) with tail biting defined in IEEE 802.16e OFDMA standard and implement the project on Viterbi-decoder coprocessor (VCP) of the Texas Instruments (TI)'s TMS320C6416T digital signal processor (DSP) and also sturdy for tail-biting encoding property, interrupt service routine (ISR) and enhanced direct memory access (EDMA). Besides, we also employ the EDMA under 3L Diamond real-time operating system (RTOS) for the VCP applications of multi-DSP operation. We compare CC in AWGN channel on the C program to CC on the VCP applications for BER performance and processing rate. In BER performance, the simulation is limited to the hardware fixed-point and VCP branch metric input bit numbers; however, if we utilize the same condition to compare them, we can find their performance are close. In processing rate, after optimizing the programs on the DSP platform, encoder can achieve two data processing rates of 16,667 Kbps and 3,764 Kbps, the VCP decoder can achieve two processing rates of 7,897 Kbps and 2,997 Kbps and the C program decoder can achieve two processing rates of 805 Kbps and 632 Kbps, respectively on the C6416 CCS simulator and 3L Diamond. In short, we utilize the CCS and 3L to measure, finding decoding processing rate can be improve significantly about 9.8 and 4.7 times, respectively.

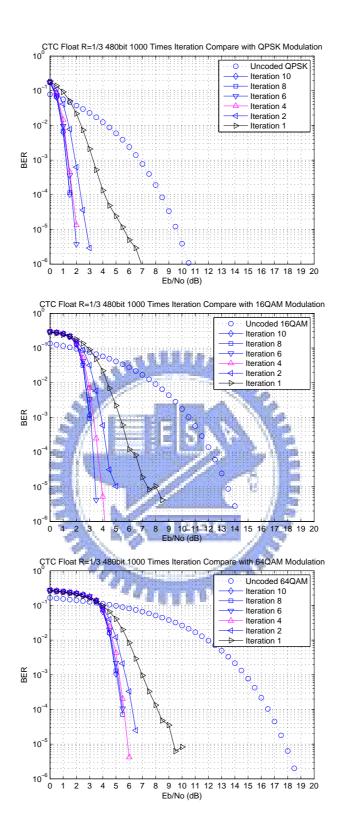

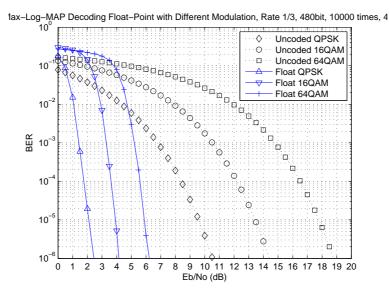

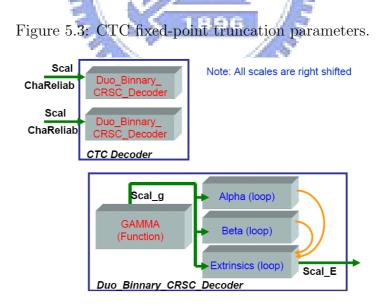

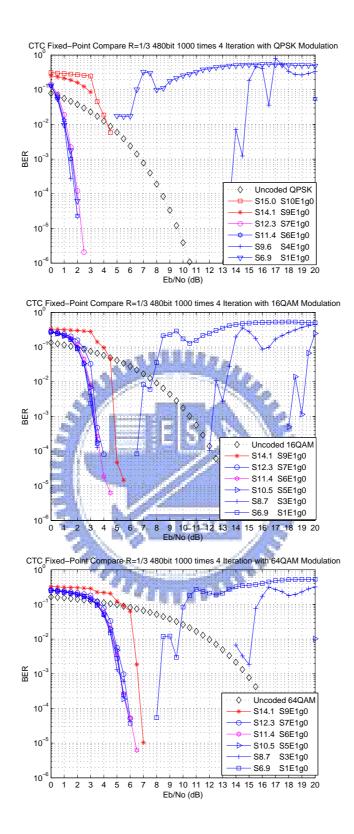

The focus of second part is the research of the convolutional turbo code (CTC) defined in IEEE 802.16e OFDMA and implement on the C6416 DSP. We explain the duo-binary circular recursive systematic convolutional encoding (duo-binary CRSC) and the max-log MAP decoding algorithm. We employ the C program to insure the correctness of our algorithm and simulate the CTC for different modulation in AWGN; then, we implement on TI C6416 DSP. The encoder can achieve a data processing rate of 8,223 Kbps and the decoder can achieve a processing rate of 30 Kbps on the 3L. Then we utilize some optimized techniques to improve the decoder's speed, which is approximately 10 times speeded up in decoding rate. Therefore, the decoder can achieve a further data processing rate of 300 Kbps.

## 誌謝

本篇論文的完成, 誠摯地感謝我的指導老師林大衛博士, 從踏入交通大學電 子所開始, 多虧老師的循循善誘, 不但給予我在課業、研究上的幫助, 使我學到 了分析問題及解決問題的能力。同時老師樂觀的生活態度也影響了我, 讓我更有 勇氣面對各種困難。在此, 僅向老師及老師的家人致上最高的感謝之意。

另外要感謝的,是實驗室的洪崑健學長和吳俊榮學長。謝謝你們熱心有耐性 地幫我解決了許多通訊方面相關的疑問。也要感謝 3L Diamond Engineer Peter Robertson,謝謝你不嫌棄我的英文,透過不斷往來的英文書信,仍然很熱心很 積極的幫我解決一些 3L EDMA 的問題。另外還要感謝「數位信號處理平台在嵌 入式系統的應用」一書作者,交大電信所畢業的盧怡仁學長,學長已經畢業學校 很多年,因緣巧合和學長搭上了線,感謝您幫我釐清一些 DSP 問題的觀念。

感謝通訊電子與訊號處理實驗室(Commlab),提供了充足的軟硬體資源,讓 我在研究中不虞匱乏。感謝94級柏昇、順成兩位學長的指導,以及95級昀澤、 光中、婉清、奕安、威年、尚諭、衛川、紹唐等實驗室成員,平日和我一起唸書, 一起討論,也一起打混,讓我的研究生涯充滿歡樂又有所成長。期待大家畢業之 後都能有不錯的發展。

最後,要感謝的是我的家人,他們的支持讓我能夠心無旁騖的從事研究工作。 謝謝所有幫助過我、陪我走過這一段歲月的師長、同儕與家人。謝謝!

誌於 2008.6 故鄉風城 交大

佳楓

# Contents

| 1        | Intr | oducti | on                                                                         | 1  |

|----------|------|--------|----------------------------------------------------------------------------|----|

|          | 1.1  | Scope  | of the Work                                                                | 1  |

|          | 1.2  | Organ  | ization of This Thesis                                                     | 3  |

| <b>2</b> | Ove  | rview  | of CC and CTCs in IEEE 802.16e OFDMA                                       | 4  |

|          | 2.1  | Tail-B | iting Convolutional Code Specifications [1]                                | 4  |

|          |      | 2.1.1  | Randomizer [1]                                                             | 5  |

|          |      | 2.1.2  | Convolutional Encoder [1]                                                  | 7  |

|          |      | 2.1.3  | Interleaver [1]                                                            | 10 |

|          |      | 2.1.4  | Modulation $[1]$                                                           | 11 |

|          | 2.2  | Decod  | ing of CC                                                                  | 11 |

|          |      | 2.2.1  | Demodulation for Bit-Interleaved Coded Modulation $[9]$                    | 12 |

|          | 2.3  | Convo  | lutional Turbo Codes Specifications [1]                                    | 16 |

|          |      | 2.3.1  | CTC Encoder in IEEE 802.16e OFDMA [1] $\ldots \ldots \ldots \ldots \ldots$ | 17 |

|          |      | 2.3.2  | CTC Interleaver $[1]$                                                      | 20 |

|          |      | 2.3.3  | CTC Tail-Biting [1], [10]                                                  | 20 |

|   |     | 2.3.4  | Subpacket Generation (Channel Interleaver or Interleaver and Punc-                         |    |

|---|-----|--------|--------------------------------------------------------------------------------------------|----|

|   |     |        | turing) [1] $\ldots$                                                                       | 23 |

|   | 2.4 | Decod  | ling of CTC                                                                                | 29 |

|   |     | 2.4.1  | The Turbo Decoding Algorithm [11]                                                          | 29 |

|   |     | 2.4.2  | Decoding Rule for CRSC Codes with Non-binary Trellis [14] $\ldots$                         | 31 |

|   |     | 2.4.3  | Simplified Max-Log-MAP Algorithm for Double-Binary CTC $\left[14\right]~$                  | 33 |

| 3 | DSI | P Impl | lementation Environment                                                                    | 37 |

|   | 3.1 | The D  | SP Baseboard                                                                               | 37 |

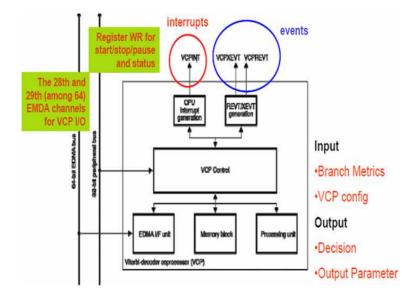

|   | 3.2 | The V  | iterbi-Decoder Coprocessor (VCP) [19]                                                      | 38 |

|   |     | 3.2.1  | Overview of VCP [19], [21], [22]                                                           | 38 |

|   |     | 3.2.2  | VCP Inputs (Brach Metrics and VCP Input Configuration) [19], [22]                          | 43 |

|   |     | 3.2.3  | VCP Output (Decisions) [19]                                                                | 46 |

|   |     | 3.2.4  | Sliding Windows Processing [19]                                                            | 48 |

|   | 3.3 | VCP ]  | Programming [19], [21]                                                                     | 49 |

|   |     | 3.3.1  | Prepare Input Configuration, Initialize Input Buffers, and Allocate                        |    |

|   |     |        | Output Buffers [21]                                                                        | 51 |

|   |     | 3.3.2  | EDMA Resource [19] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 52 |

|   |     | 3.3.3  | VCP Procedure [21]                                                                         | 52 |

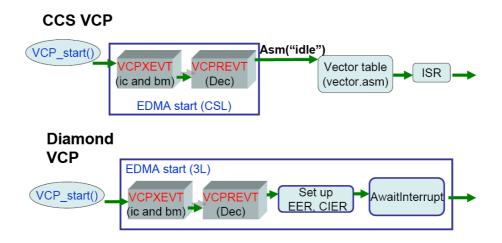

|   | 3.4 | EDM    | A under the Code Composer Studio (CCS) [23]                                                | 54 |

|   |     | 3.4.1  | EDMA Control Registers [23]                                                                | 55 |

|   |     | 3.4.2  | Parameter RAM (PaRAM) [23]                                                                 | 58 |

|   |                                               | 3.4.3                                                                                               | EDMA Transfer Parameter Entry [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60                                                                                 |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|   |                                               | 3.4.4                                                                                               | Initiating an EDMA Transfer [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                 |

|   |                                               | 3.4.5                                                                                               | Linking EDMA Transfers [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                                 |

|   |                                               | 3.4.6                                                                                               | EDMA Interrupt Generation [23], [24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62                                                                                 |

|   | 3.5                                           | EDMA                                                                                                | A under the 3L Diamond Real-Time Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                 |

|   |                                               | 3.5.1                                                                                               | Introduction to 3L Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                                 |

|   |                                               | 3.5.2                                                                                               | SC6xEDMA [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                                 |

|   |                                               | 3.5.3                                                                                               | EDMA Channel Availability [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                 |

|   |                                               | 3.5.4                                                                                               | SC6xEDMAChannel Functions [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                 |

| 4 | DSI                                           | P Impl                                                                                              | ementation of Convolutional Encoder and Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                                                                                 |

|   |                                               |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

|   | 4.1                                           | VCP ]                                                                                               | Parameter Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                 |

|   | 4.1                                           | VCP 1<br>4.1.1                                                                                      | Parameter Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70<br>71                                                                           |

|   | 4.1                                           |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

|   | 4.1                                           | 4.1.1                                                                                               | Generator Polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                                                                                 |

|   | <ul><li>4.1</li><li>4.2</li></ul>             | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li></ul>                                                 | Generator Polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>71                                                                           |

|   |                                               | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li><li>Codin</li></ul>                                   | Generator Polynomials    Image: | 71<br>71<br>72                                                                     |

|   | 4.2                                           | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li><li>Codin</li><li>Comp</li></ul>                      | Generator Polynomials   EDMA Setting   Tail-Biting   Gain Analysis [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71<br>71<br>72<br>73                                                               |

| 5 | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | <ul> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>Codin</li> <li>Comp</li> <li>VCP 0</li> </ul> | Generator Polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> </ul>             |

| 5 | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | 4.1.1<br>4.1.2<br>4.1.3<br>Codin<br>Comp<br>VCP 0                                                   | Generator Polynomials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>84</li> </ul> |

|     | 5.2.1 | Speed Performance of the DSP Code                                               | 97  |

|-----|-------|---------------------------------------------------------------------------------|-----|

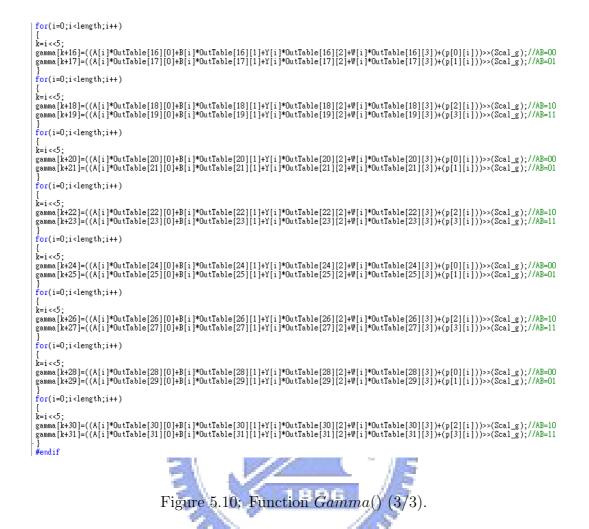

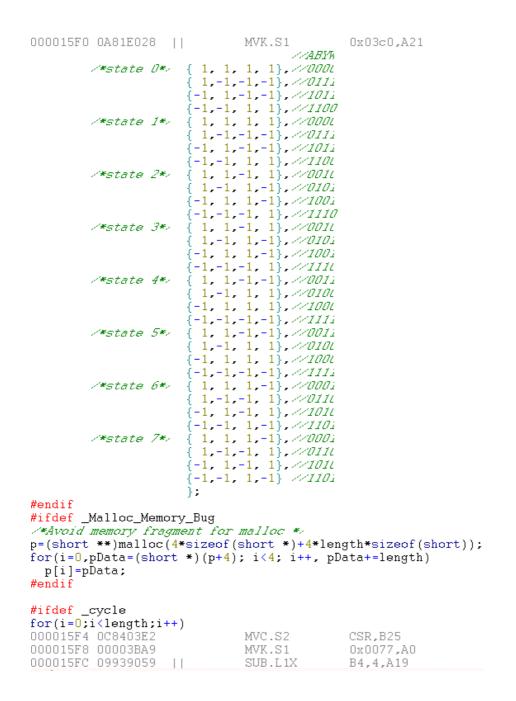

|     | 5.2.2 | Improving CTC Decoding Speed                                                    | 101 |

| 5.3 | Comp  | arison of Speed of Current Codes                                                | 113 |

|     | 5.3.1 | The Views of Block Decoder for Processing Rate                                  | 113 |

|     | 5.3.2 | Comparison of Tail-Biting CC and CTC for Adders and Multipliers .               | 114 |

|     | 5.3.3 | Comparison of Decoder Speed for Tail-Biting CC, CTC, and LDPC $% \mathcal{C}$ . | 116 |

## 6 Conclusion and Future Work

## Bibliography

120

118

# List of Figures

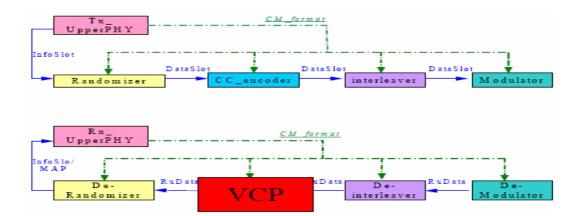

| 2.1  | Structure of convolutional coding in transmitter (top path) and decoding in |    |

|------|-----------------------------------------------------------------------------|----|

|      | receiver (bottom path)                                                      | 5  |

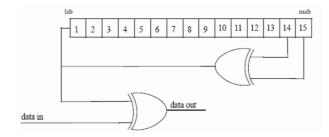

| 2.2  | PRBS for data randomization (from [1]).                                     | 7  |

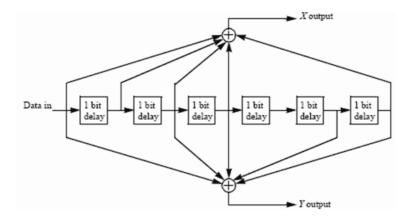

| 2.3  | Convolutional encoder of rate $1/2$ (from [1])                              | 8  |

| 2.4  | The second permutation of interleaver.                                      | 11 |

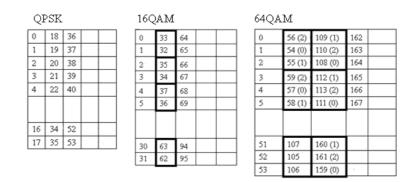

| 2.5  | QPSK, 16-QAM, and 64-QAM constellations (from [1]).                         | 12 |

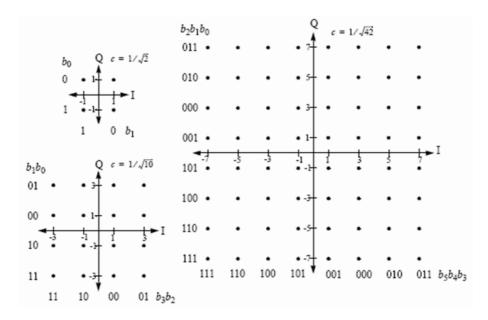

| 2.6  | Metric partitions of the 16-QAM constellation (from [9])                    | 15 |

| 2.7  | CTCs coding block diagram (from [1]).                                       | 16 |

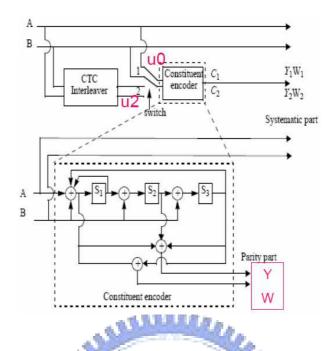

| 2.8  | CTC encoder (modified from [1])                                             | 18 |

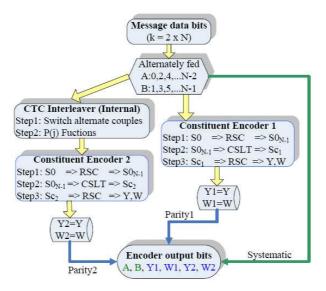

| 2.9  | CTC rate 1/3 encoder flow chart                                             | 19 |

| 2.10 | CTC encoding slot concatenation for different rate (modified from [1])      | 20 |

| 2.11 | CTC channel coding per modulation (modified from $[1]$ )                    | 21 |

| 2.12 | CTC interleaver in two steps (modified from $[1]$ )                         | 22 |

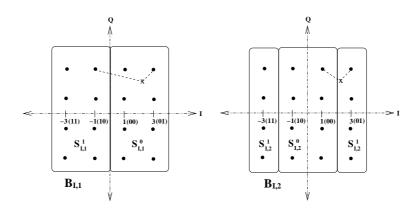

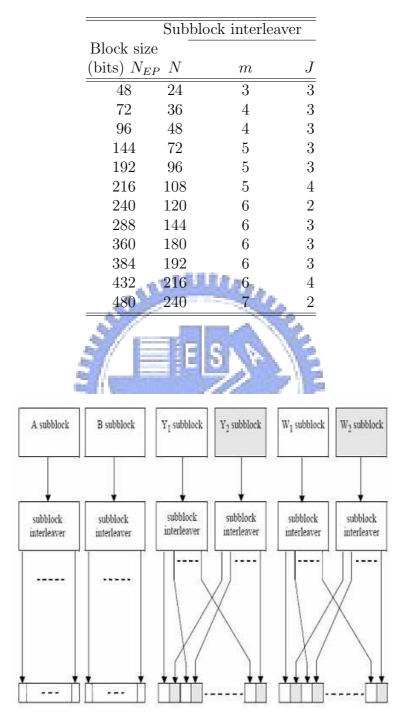

| 2.13 | Block diagram of CTC channel interleaving scheme (from $[1]$ )              | 26 |

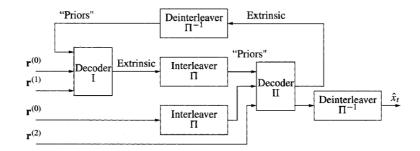

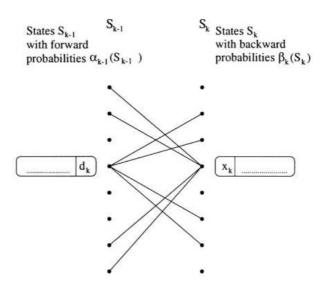

| 2.14 | Block diagram of a turbo decoder (from [11]).                               | 29 |

| CTC trellis structure of duo-binary convolutional code with feedback encoder       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (from [14])                                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

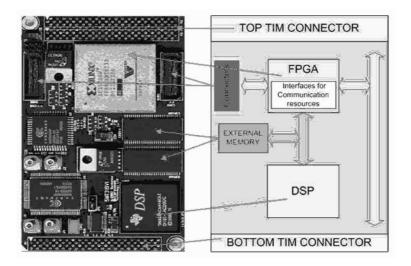

| Sundance's SMT395 module (from $[18]$ )                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCP block diagram (modified from $[19]$ )                                          | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

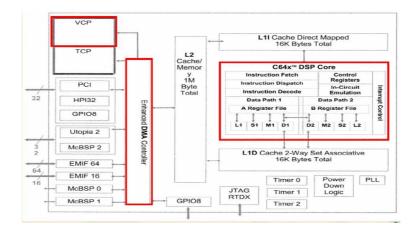

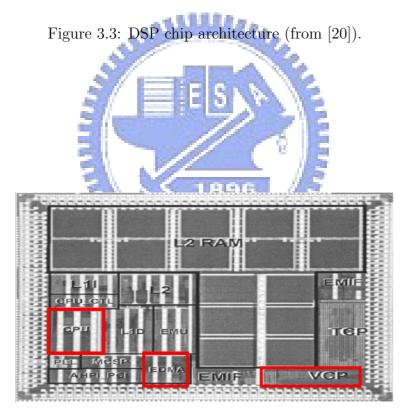

| DSP chip architecture (from $[20]$ )                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DSP chip die (from [20])                                                           | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

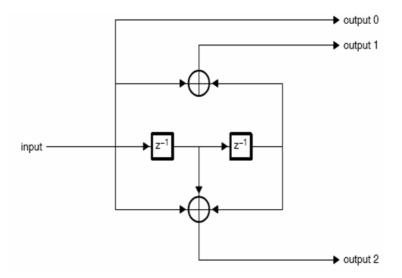

| Convolutional encoder example, where $K = 3$ , $R = 1/3$ , $G0 = (100)_8$ , $G1 =$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $(101)_8, G2 = (111)_8 $ (from [19])                                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

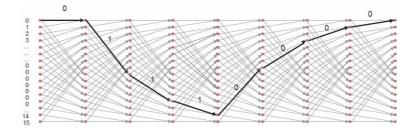

| Convolutional code trellis example (from [19])                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Example of survivor path and associated decoded sequence (from $[21]$ )            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

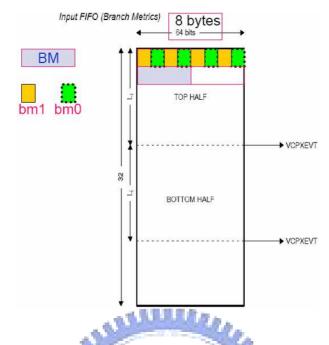

| VCP input FIFO (modified from [19]).                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCP registers (modified from [19]).                                                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

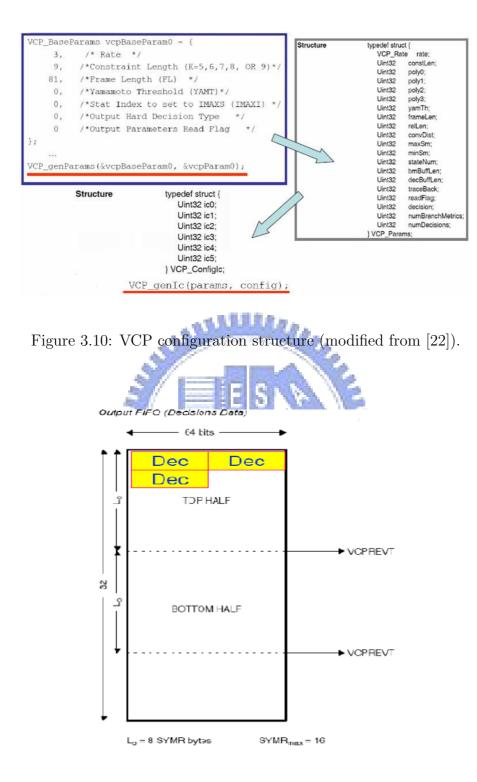

| VCP configuration structure (modified from [22]).                                  | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

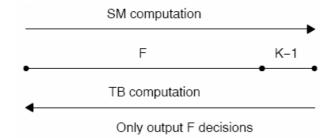

| VCP output FIFO (modified from [19]).                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCP tailed traceback mode (from [19])                                              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCP frame, reliability, and convergence length limitations(modified from [19]).    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCP EDMA parameters structure (from [19])                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EDMA control (from [23])                                                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

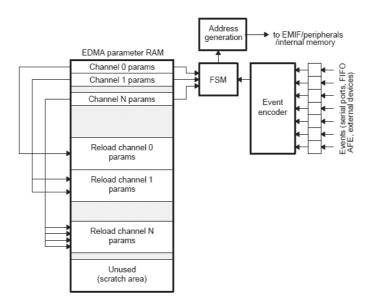

| EDMA parameter RAM contents (modified from [23]).                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EDMA channel parameters (from [23])                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Example of linked EDMA transfers (from [23]).                                      | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                    | (from [14]).Sundance's SMT395 module (from [18]).VCP block diagram (modified from [19]).DSP chip architecture (from [20]).DSP chip die (from [20]).Convolutional encoder example, where $K = 3$ , $R = 1/3$ , $G0 = (100)_8$ , $G1 = (101)_8$ , $G2 = (111)_8$ (from [19]).Convolutional code trellis example (from [19]).Convolutional code trellis example (from [19]).Example of survivor path and associated decoded sequence (from [21]).VCP registers (modified from [19]).VCP registers (modified from [19]).VCP configuration structure (modified from [22]).VCP tailed traceback mode (from [19]).VCP tailed traceback mode (from [19]).VCP frame, reliability, and convergence length limitations(modified from [19]).VCP EDMA parameters structure (from [19]).EDMA control (from [23]).EDMA channel parameters (from [23]). |

| 4.1  | CC encoding and decoding with VCP.                                                 | 71 |

|------|------------------------------------------------------------------------------------|----|

| 4.2  | VCP parameter setting (modified from [21])                                         | 72 |

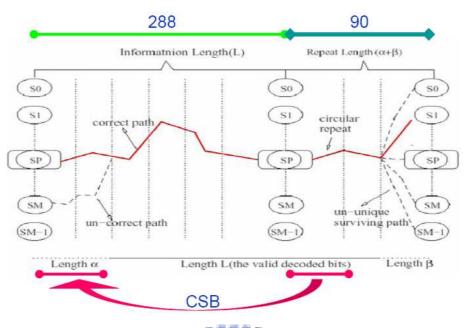

| 4.3  | Tail-biting CC decoding employing (modified from [3])                              | 73 |

| 4.4  | VCP decoding performance in AWGN with different BM truncation precisions           |    |

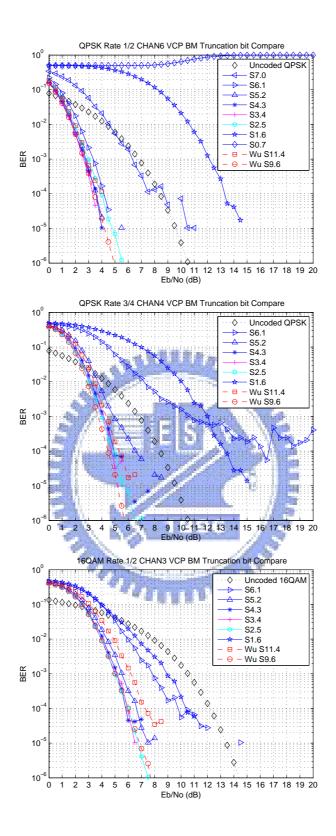

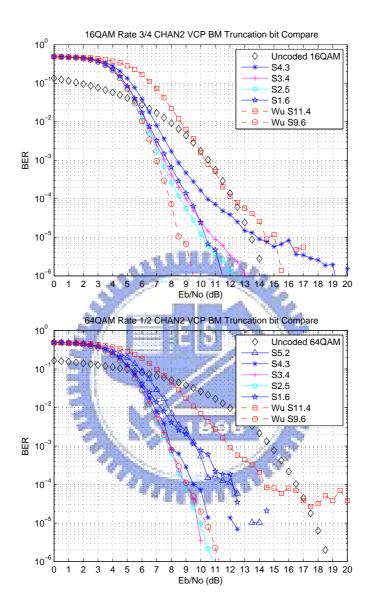

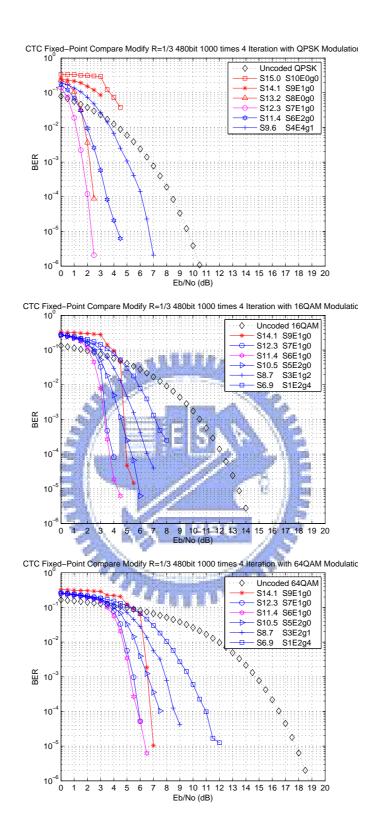

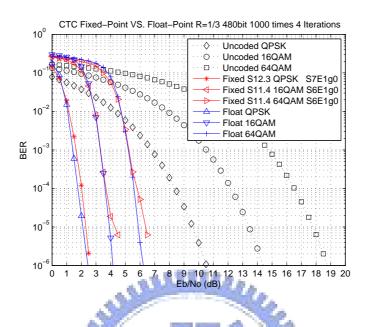

|      | (1/3)                                                                              | 78 |

| 4.5  | VCP decoding performance in AWGN with different BM truncation precisions           |    |

|      | (2/3)                                                                              | 79 |

| 4.6  | VCP decoding performance in AWGN with different BM truncation precisions           |    |

|      | $(3/3).  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 80 |

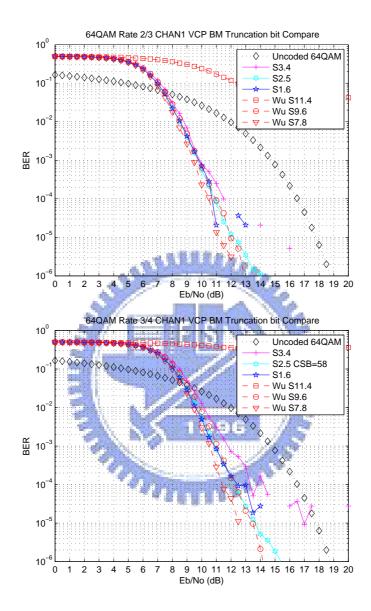

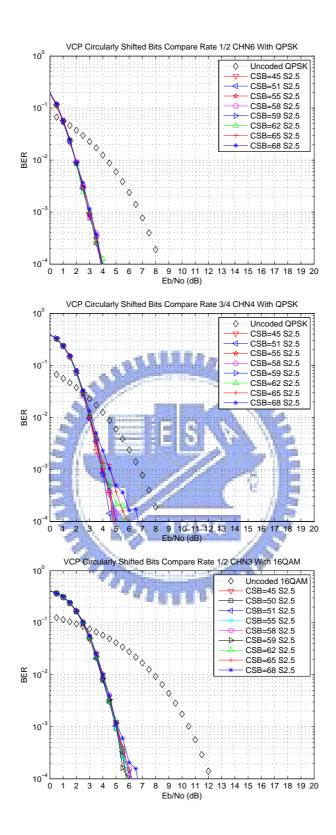

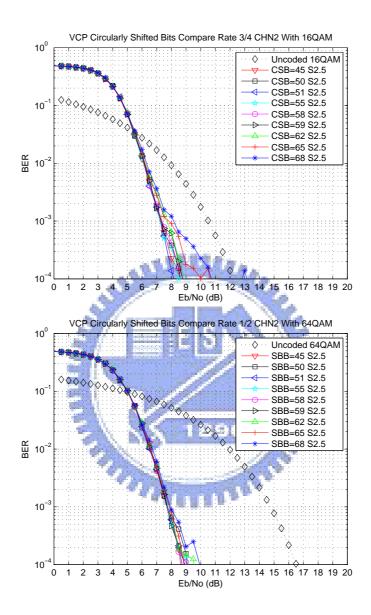

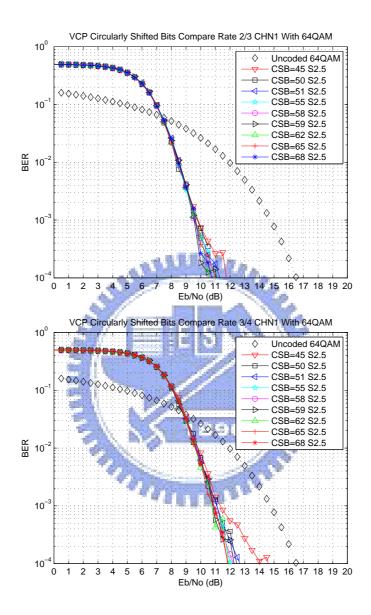

| 4.7  | Effect of CSB values in VCP-based decoding in AWGN at different coding-            |    |

|      | modulation settings $(1/3)$                                                        | 81 |

| 4.8  | Effect of CSB values in VCP-based decoding in AWGN at different coding-            |    |