# 國立交通大學

電子工程學系 電子研究所碩士班

## 碩士論文

應用於低溫多晶矽製程下和差類比數位轉換器 電路設計與實現

## Design and Realization of Delta-Sigma A/D Converter in LTPS Technology

研究生: 蔡佳琪 (Chia-Chi Tsai) 指導教授: 柯明道教授 (Prof. Ming-Dou Ker)

中華民國九十八年三月

# 應用於低溫多晶矽製程下和差類比數位轉換器 電路設計與實現

# Design and Realization of Delta-sigma A/D Converter in LTPS Technology

研究生:蔡佳琪

Student: Chia-Chi Tsai

指導教授:柯明道教授

Advisor: Prof. Ming-Dou Ker

國立交通大學

電子工程學系 電子研究所

碩士論文

A Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao-Tung University in Partial Fulfillment of the Requirements for the Degree of Master in Electronics Engineering March 2009 Hsin-Chu, Taiwan

中華民國九十八年三月

### 應用於低溫多晶矽製程下

### 和差類比數位轉換器電路設計與實現

學生:蔡佳琪

指導教授:柯明道教授

### 國立交通大學 電子工程學系電子研究所碩士班

### **ABSTRACT (CHINESE)**

低溫複晶矽 (low temperature polycrystalline silicon, LTPS) 薄膜電晶體 (thin-film transistors, TFTs) 已被視為一種材料廣泛地研究於可攜帶式系統產品 中,例如數位相機、行動電話、個人數位助理 (PDA) 、筆記型電腦等,這是由 於低溫複晶矽薄膜電晶體的電子遷移率約是傳統非晶矽 (amorphous silicon) 薄 膜電晶體的一百倍大。此外,低溫複晶矽技術可藉由將驅動電路整合於顯示器之 周邊區域來達到輕薄、巧小且高解析度的顯示器。這樣的技術也將越來越適合於 系統面板 (System-on-Panel, SOP) 應用之實現。

隨著系統面板的發展,各式輸入顯示技術 (input display technology) 被整合 於其中,包含了記錄文字、影像或是照片的掃描器 (scanner),偵測手指或是筆 跡的觸控式面板 (touch panel)等,這些新穎的應用不管對於個人或是企業都可 以帶來很大的便利性。另外,面板溫度對液晶顯示器薄膜電晶體影響顯著,因此 為了提升系統可靠度,溫度補償電路也廣泛的被討論。無論是在觸控式面板設計 抑或是溫度補償電路等,其中都包含了感測電路 (sensing circuit)。類比至數位 轉換器就是一種被廣泛地應用在感測電路後端,將感測到的類比訊號轉換為數位 訊號進而驅動其它數位訊號處理器 (DSP) 的電路。因此,隨著輸入顯示技術的 發展以及溫度補償電路的不可或缺性,面板上類比至數位轉換器的整合是非常值 得被研究與探討。 在本篇論文之中,首次提出了設計於玻璃基板上之和差類比至數位轉換電路 並且已經在三微米低溫複晶矽薄膜電晶體製程下成功被驗證。相較於其它類比至 數位轉換器 (flash ADC, pipeline ADC),此電路可藉由負迴授機制以操作速度換 取較高的解析度,同時佔用較小的面積。此類比至數位轉換器操作在十伏特的操 作電壓之下,前端和差調變器 (delta-sigma modulator) 將類比輸入訊號轉換成連 續性的位元流 (bit stream),再經由降頻濾波器 (decimation filter) 轉換為八位元 之數位訊號。此新提出的類比至數位轉換器電路未來將可以被整合在面板上,帶 來更便利性的應用。

## Design and Realization of Delta-Sigma A/D Converter in LTPS Technology

Student: Chia-Chi Tsai

Advisor: Prof. Ming-Dou Ker

Department of Electronics Engineering & Institute of Electronics College of Electrical and Computer Engineering National Chiao-Tung University

### ABSTRACT (ENGLISH)

# Low temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) have been widely investigated as a material for portable systems, such as digital camera, mobile phone, personal digital assistants (PDAs), notebook, and so on, because the electron mobility of LTPS TFTs is about 100 times larger than that of the conventional amorphous silicon TFTs. Furthermore, LTPS technology can achieve slim, compact, and high-resolution display by integrating the driving circuits on peripheral area of display. This technology will also become more suitable for realization of System-on-Panel (SOP) applications.

SOP displays are value-added displays with various functional circuits, and the input display technology creates opportunities for new applications like a scanner for recording of text or images for on-line shops and touch-sensing circuits for detecting the position of finger or pen. Besides, optical characteristics of TFT-LCDs are significantly dependent on panel temperature. For wide usage in thermally harsh environments, LCD should use a robust temperature compensation system to enhance

reliability and maintain performance. Sensing circuits are indispensable to these novel applications. The technique of forming an optical sensor using LTPS TFT fabrication process is developed to incorporate these new functions in the display without any additional circuit behind the display.

A/D converters (ADC) are widely used in the interface between analog sensing circuits and digital processing circuits to convert the analog sensor signals to a digital signal and then processed by some digital circuits or FPGA. For the above reason, integration of ADC on the glass substrate is my focus in this thesis.

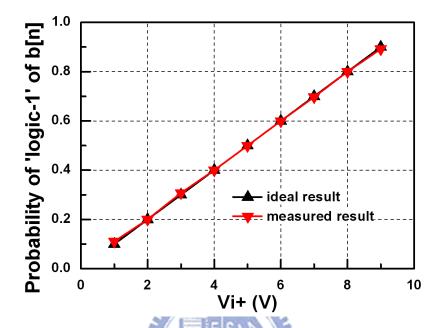

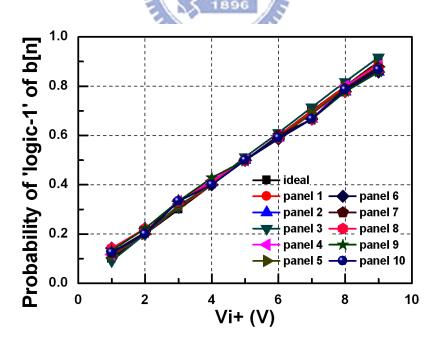

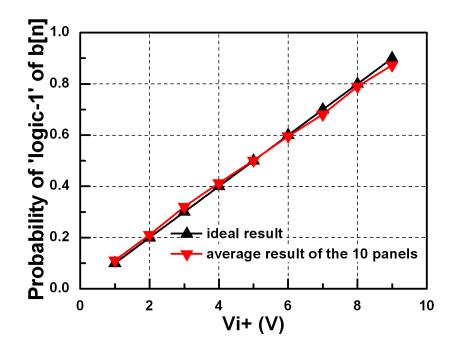

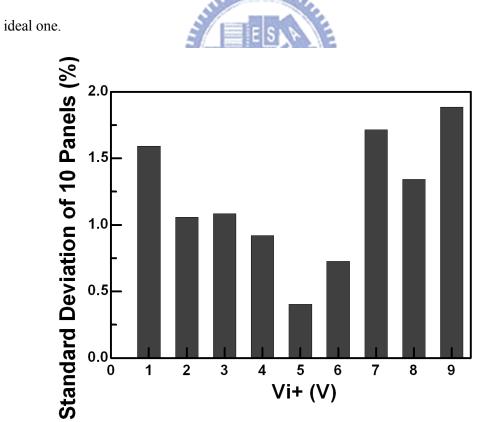

In this thesis, a delta-sigma ADC designed and implemented with the TFTs on glass substrate has been proposed, and successfully verified in a 3-µm LTPS process. From the experimental results, the probability in the bit stream of the digital output from the delta-sigma modulator is correctly fit in the analog input voltage ratio. Such a bit stream can be converted into 8-bit digital code successfully under the operation voltage of 10V with TFTs on the glass substrate. The proposed delta-sigma ADC can be further used to achieve the precise analog circuits for SOP applications, which enables the analog circuits to be integrated in the active matrix LCD (AMLCD) panels.

### ACKNOWLEDGEMENTS

### 致謝

在這兩年的碩士生涯當中,首先我要感謝的是我的指導教授 柯明道老師。 老師在接了義守大學副校長職位之後變得越來越忙碌,卻總是不辭辛苦的南北兩 地奔波,在每個星期一晚上回到新竹跟同學們開會,即使開會開到半夜十二點、 一點,老師卻仍精神奕奕,一點也看不出疲態,但想必是非常辛苦的吧!

而在我的研究過程中,我要特別感謝「友達光電股份有限公司」給予我們研 究群許多下線機會,讓我們有機會對我們的電路做一個很好的驗證。另外,我最 要感謝的是服務於其中的鯉魚學長。鯉魚學長在兩年前畢業於柯明道教授研究 群,之後便投入了友達光電。鯉魚學長不僅在研究上非常認真、知識非常富足, 他更是一個非常願意給予學弟妹幫助與指導的學長。尤其是在每次要下線之前, 即使學長手頭有非常多的工作,他仍願意為我們撥出時間做 DRC 及 LVS 驗證,每 次一忙下來可能就是一個上午,但他卻連一杯飲料都不希望給我們請,真的讓我 們大家都非常非常的感謝。

我還要感謝的是吳介琮老師研究群的金毛學長以及愛莉絲學長,謝謝你們對 於我研究以及量測的指導。對於這個研究題目我可以說是從無到有,常常碰壁。 謝謝你們對於不是同指導教授的我可以這麼不厭其煩的提點,每當我有一個問題 出現的時候,學長們卻總是舉一反三,幫助我建立更完整的概念。

此外,我要感謝的是「奈米與晶片系統實驗室」的學長姐及學弟妹們,在各 方面給予我協助,讓我可以順利完成我的畢業論文。

接著謝謝天天在我煩躁的時候讓我沒事踢踢他的椅子卻從不生氣、謝謝小州 哥在我小咪生不出來的時候半小時搞定同時為了我的破英文煩惱不已、謝謝小昀 昀提供美肌相機讓女孩們出遊總是拍拍拍的很開心還帶來了可愛的便便鼠、謝謝 世範在咪停的時候陪我聊天聊地聊是非、謝謝北鴨每次都提供好吃的甜點還親自 送來、謝謝吃吃跟狗達代替了北鴨跟我們可以多陪小州哥一年,謝謝實驗室的大 家,一起研究,一起玩樂,豐富了碩士班期間的生活。

另外,我要謝謝我的室友們,謝謝嚕嚕每天晚上陪我聊天聊到不用睡覺偶爾 還可以吃到親手做的美味早餐、謝謝南西口試前貼心的給我小卡片讓我更有信 心、謝謝青玉週末大家都不在的時候煮飯給我吃填飽我的肚子、謝謝蔣灣在下雨 天時都貼心的找我讓我搭便車,謝謝妳們讓我的外宿生涯每天開開心心。

最後,我最是要感謝的是我的父親蔡德根先生、哥哥蔡政偉以及我的男友陳 鞏鞏。我的父親對我們的愛是不可言喻的,他可以粗衣節食卻希望給我們好的生 活,他忙碌到生病卻不希望我們替他擔心,現在我畢業了,希望可以跟哥哥一起 努力,讓父親可以無憂無慮的生活。而男友不論開心或是難過,總是站在我的身 邊支持著我,走過好多好多個年頭,希望未來我們依然可以相互支持、開開心心 的走下去。 要感謝的人太多了,若有遺漏,在此一併謝過。本論文撰寫時已力求嚴謹, 然謬誤之處在所難免,尚祈各位讀者不吝惜賜予寶貴意見,使本論文能更加完善。

蔡 佳 琪僅誌於竹塹交大民國九十八年三月

## CONTENTS

| ABSTRACT (CHINESE) i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTRACT (ENGLISH)iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CONTENTS vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TABLE CAPTIONS ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FIGURE CAPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>Chapter 1</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Introduction1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.1 Motivation       1         1.1.1 LCD Industry and LTPS Technology [1], [2]       1         1.1.2 The table state of the s |

| 1.1.2 The Advantages of the System-on-Panel LTPS TFT-LCD Displays [4],      [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.1.3 Future Applications of "Input Display" [7]7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.1.4 Thermal Influence on LCDs [8], [9], [10]11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.1.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2 Background Knowledge of Thin-Film Transistors Liquid Crystal Displays.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2.1 Brief Introduction of Liquid Crystal Displays [11], [12]13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.2.2 Liquid Crystal Display Module Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.3 Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>Chapter 2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fundamentals and Realization of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| First-order Delta-sigma Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1.1 Nyquist-rate and Oversampled Converter [18]18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1.2 Fundamentals of the First-order Delta-sigma Modulator [16], [18]19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2 Circuits Implementation on Glass Substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.2.1 Design of Fully-differential Folded-cascode Operational Amplifier24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2.2 Design of 1-bit Quantizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

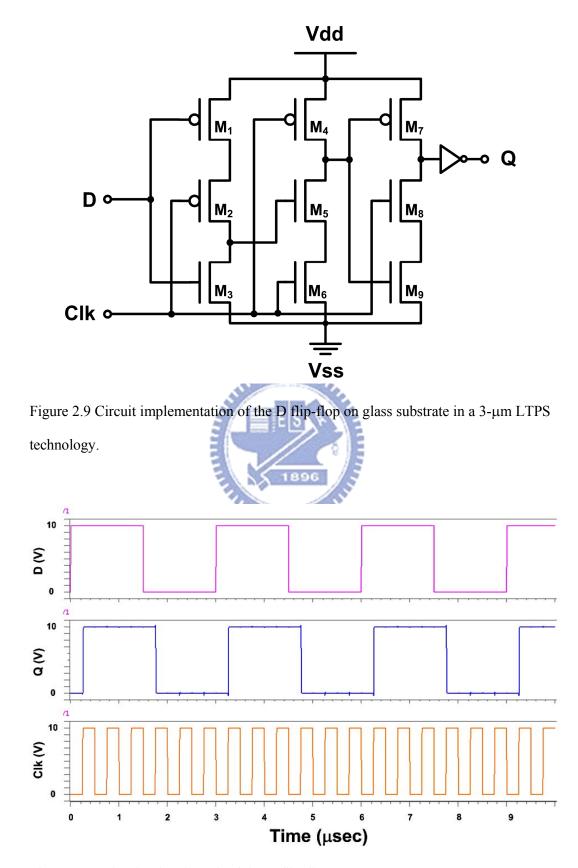

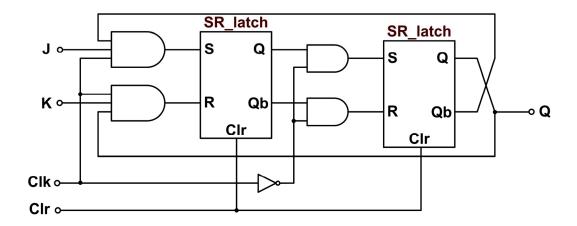

| 2.2.3 Design of D Flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Chapter 3                                      |    |

|------------------------------------------------|----|

| Decimation Filter for First-order              |    |

| Delta-sigma Modulator                          |    |

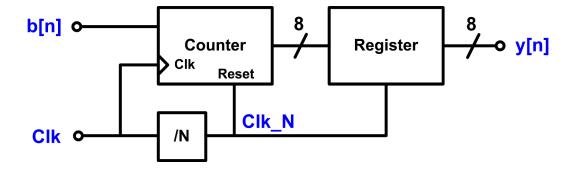

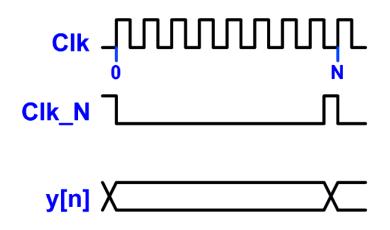

| 3.1 Introduction                               |    |

| 3.2 Circuits Implementation on Glass Substrate |    |

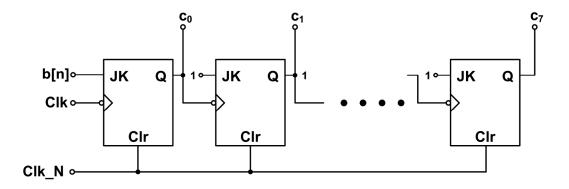

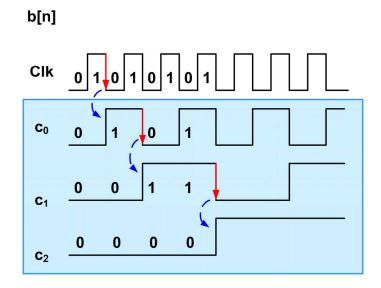

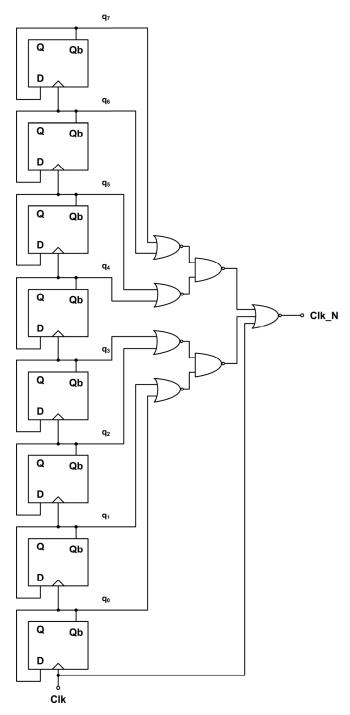

| 3.2.1 Design of the Counter                    |    |

| 3.2.2 Design of the Register                   |    |

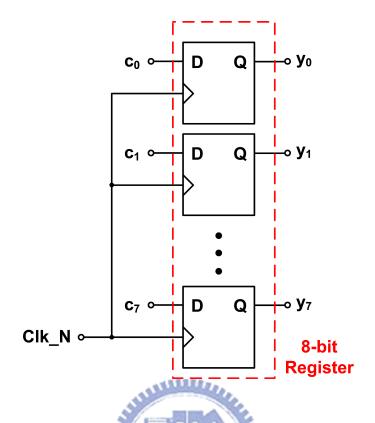

| 3.2.3 Design of the Divider                    | 43 |

| 3.2.4 Summary                                  | 45 |

| 3.3 Summary                                    | 46 |

| Chapter 4                                      | 47 |

|                                                             | ······································ |

|-------------------------------------------------------------|----------------------------------------|

| Measured Results of the First-order Delta-sigma A/D Convert | ter47                                  |

| 4.1 Layout Considerations                                   | 47                                     |

| 4.2 Measured Results                                        |                                        |

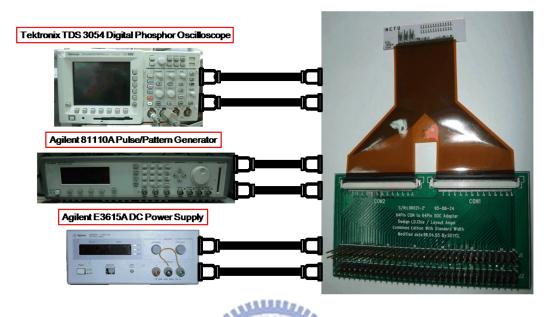

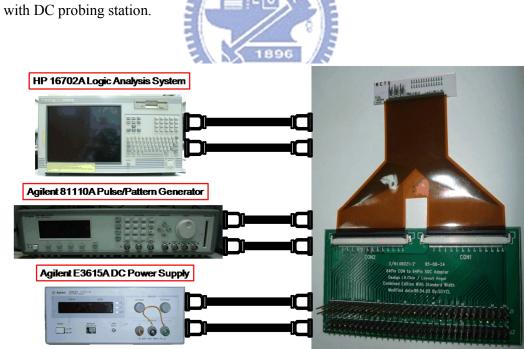

| 4.2.1 Measurement Setup                                     | 49                                     |

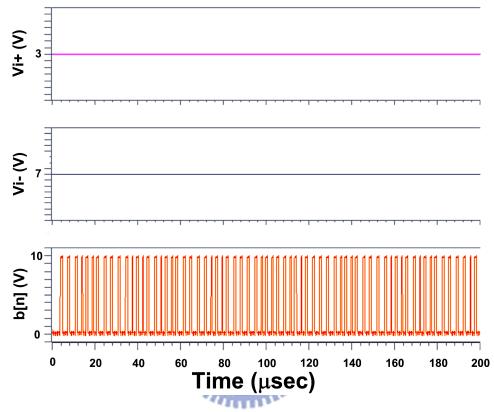

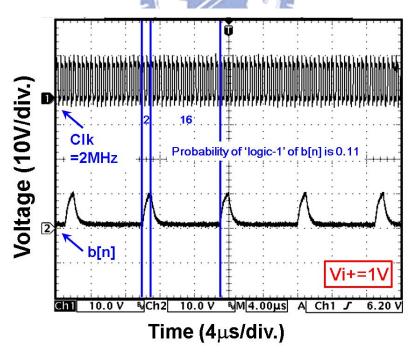

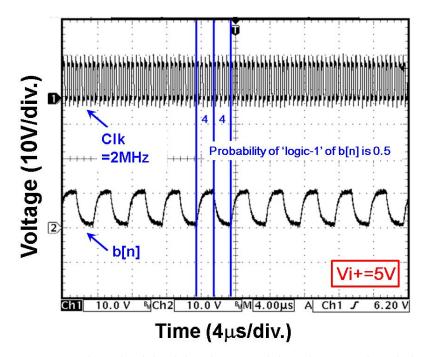

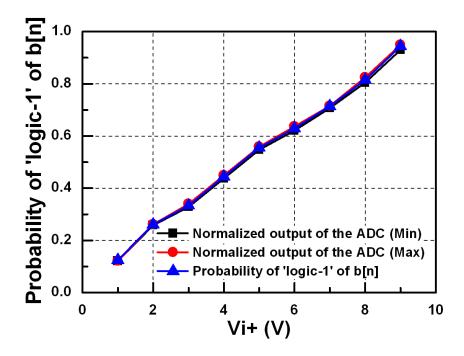

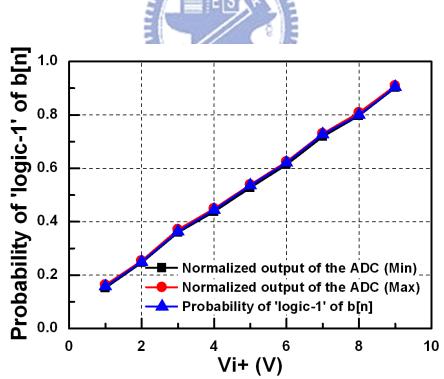

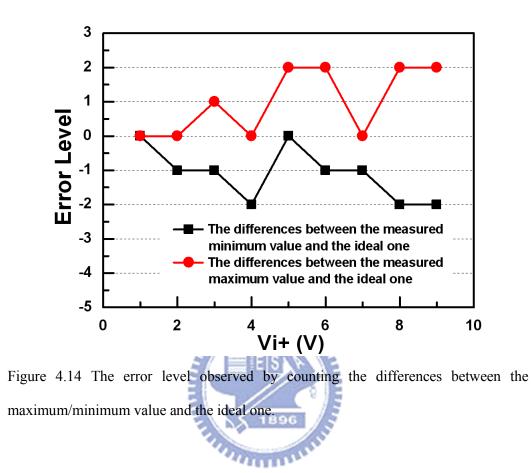

| 4.2.2 Measured Results of the Delta-sigma Modulator         | 51                                     |

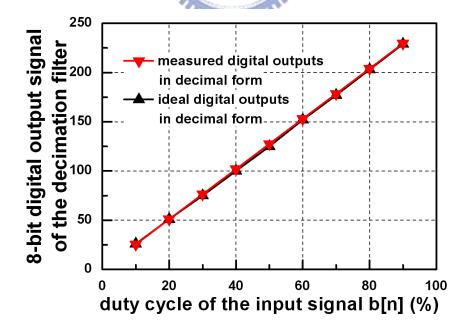

| 4.2.3 Measured Results of the Decimation Filter             | 55                                     |

| 4.2.4 Measured Results of the Delta-sigma A/D Converter     | 56                                     |

| 4.2.5 Summary                                               | 59                                     |

|                                                             |                                        |

| Chapter 5                    | 60 |

|------------------------------|----|

| Conclusions and Future Works | 60 |

| 5.1 Conclusions              | 60 |

| 5.2 Future Works             | 60 |

| REFERENCES       |    |

|------------------|----|

| VITA             | 64 |

| PUBLICATION LIST |    |

## **TABLE CAPTIONS**

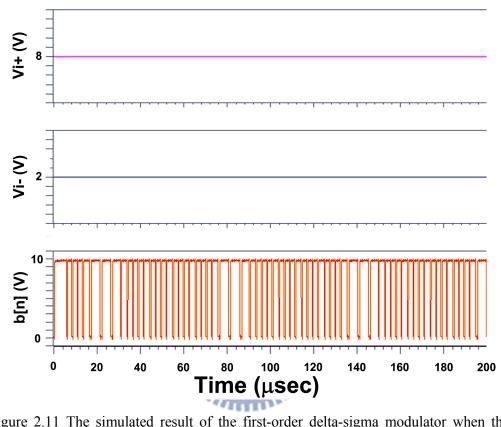

| Table 2.1 The operation of delta-sigma modulator with an input signal $x[n]$ of 6V23    |

|-----------------------------------------------------------------------------------------|

| Table 2.2 The probability of 'logic-1' in one period is calculated and listed as Vi+ is |

| 8V                                                                                      |

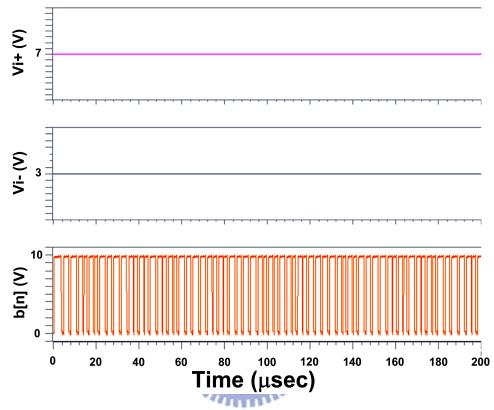

| Table 2.3 The probability of 'logic-1' in one period is calculated and listed as Vi+ is |

| 7V                                                                                      |

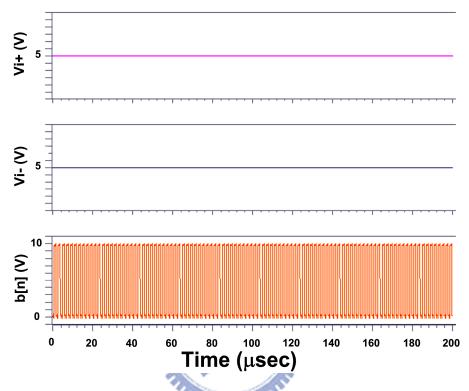

| Table 2.4 The probability of 'logic-1' in one period is calculated and listed as Vi+ is |

| 5V                                                                                      |

| Table 2.5 The probability of 'logic-1' in one period is calculated and listed as Vi+ is |

| 3V                                                                                      |

| Table 3.1 The truth table of the JK Flip-flop.    40                                    |

## **FIGURE CAPTIONS**

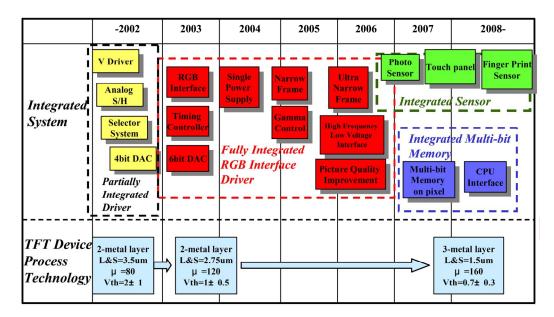

| Figure 1.1 System integration roadmap of LTPS TFT-LCD                                         |

|-----------------------------------------------------------------------------------------------|

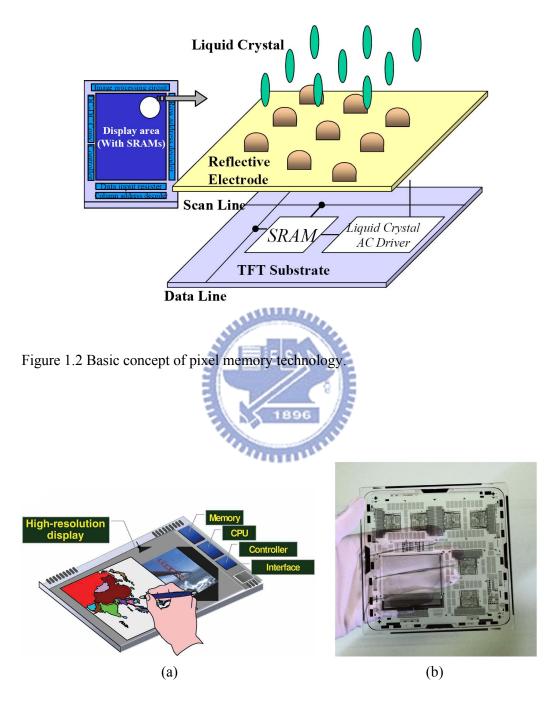

| Figure 1.2 Basic concept of pixel memory technology                                           |

| Figure 1.3 (a) The schematic illustration of the "sheet computer" concept and (b) a           |

| CPU with an instruction set of 1-4 bytes and an 8-bit data bus on glass substrate4            |

| Figure 1.4 The roadmap of LTPS technologies leading toward the realization of sheet           |

| computers                                                                                     |

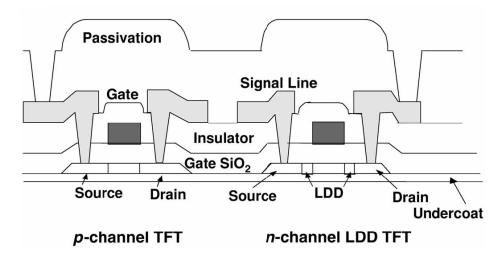

| Figure 1.5 Schematic cross-section view of the structure of a LTPS complementary              |

| metal oxide semiconductor (CMOS). LDD = lightly doped drain                                   |

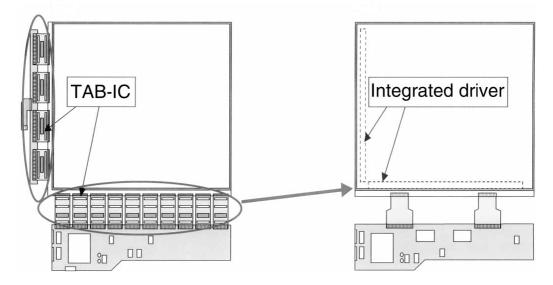

| Figure 1.6 Comparison of (a) an amorphous silicon TFT-LCD module and (b) a                    |

| low-temperature polycrystalline silicon TFT-LCD module                                        |

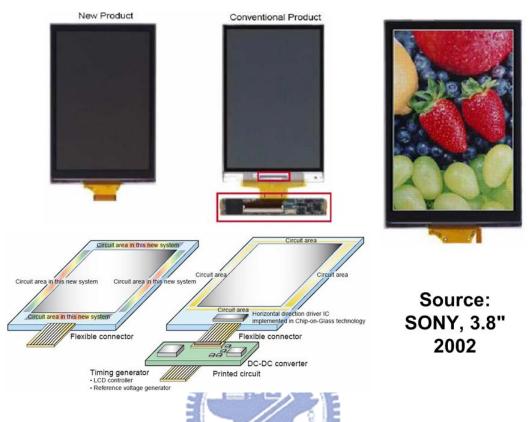

| Figure 1.7 The comparison of new SOP technology product and conventional product.             |

| The new 3.8" SOP LTPS TFT-LCD panel has been manufactured by SONY corp. in                    |

| 2002.7Figure 1.8 Future applications of "Input Display"                                       |

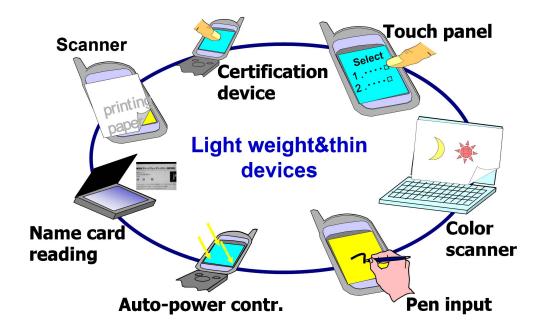

| Figure 1.8 Future applications of "Input Display"                                             |

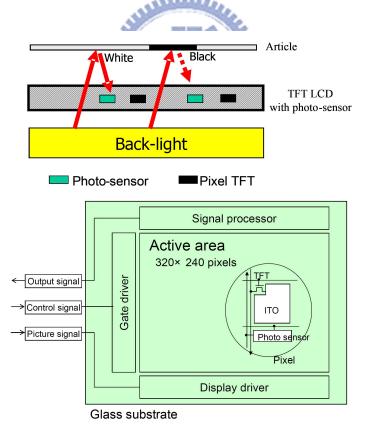

| Figure 1.9 The principle and structure of the photo-sensing display                           |

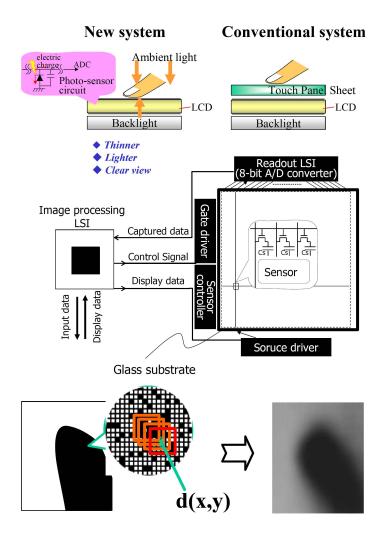

| Figure 1.10 The system architecture and image-capturing finger of the new touch               |

| panel                                                                                         |

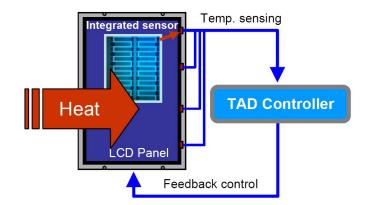

| Figure 1.11 TAD (Thermally adaptive driving) integrated thermal sensor system                 |

| architecture                                                                                  |

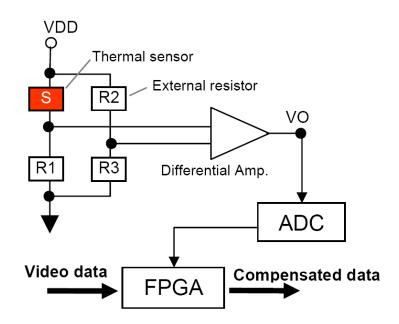

| Figure 1.12 The temperature readout circuit consists of an external full bridge circuit       |

| and a differential amplifier                                                                  |

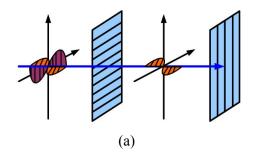

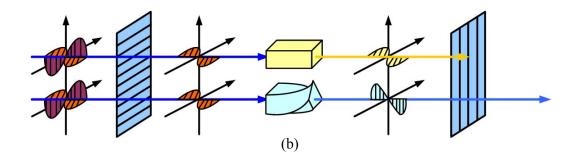

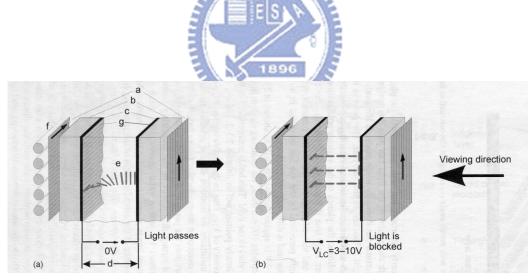

| Figure 1.13 (a) A couple of polarizers with 90° phase error. (b) A couple of polarizers       |

| with liquid crystals14                                                                        |

| Figure 1.14 The structure of a TN-LCD (a) while light is passing, and (b) while light         |

| is blocked. a: polarizer; b: glass substrate; c: transparent electrode; g: orientation layer; |

| e: liquid crystal; f: illumination15                                                          |

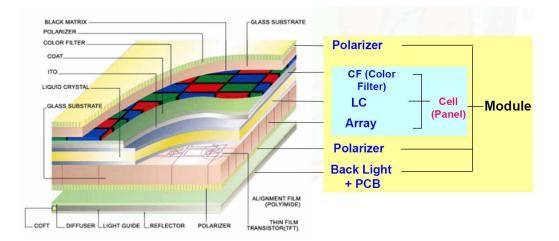

| Figure 1.15 The cross section structure of TFT-LCD panel                                      |

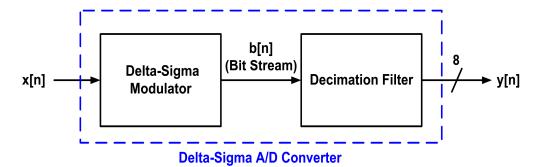

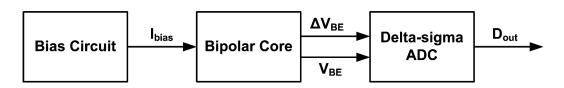

| Figure 2.1 Basic circuit diagram of Delta-sigma ADC consists of delta-sigma                   |

| modulator and decimation filter                                                               |

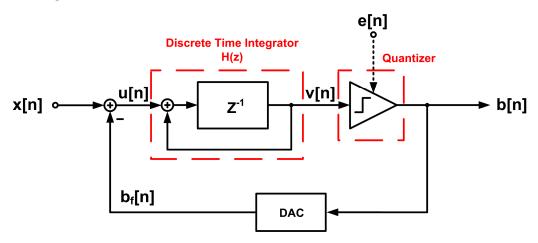

| Figure 2.2 Block diagram of delta-sigma modulator20                                           |

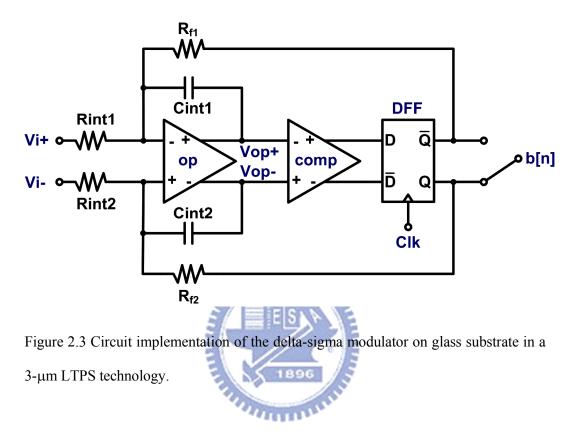

| Figure 2.3 Circuit implementation of the delta-sigma modulator on glass substrate in a        |

| 3-µm LTPS technology24                                                                        |

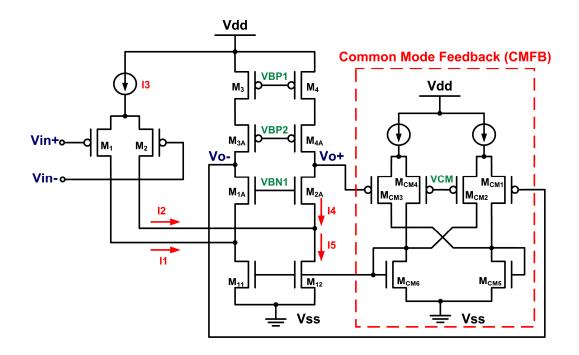

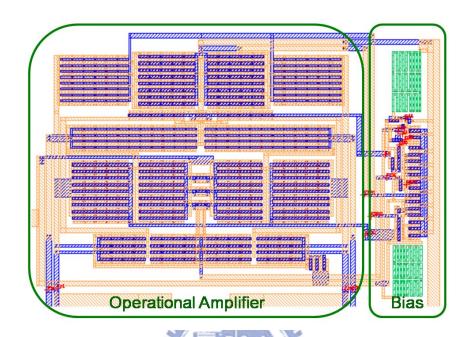

| Figure 2.4 Circuit implementation of the fully-differential folded-cascode operational        |

| amplifier on glass substrate in a 3-µm LTPS technology26                                      |

| Figure 2.5 The simulated frequency response of the fully differential operational             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

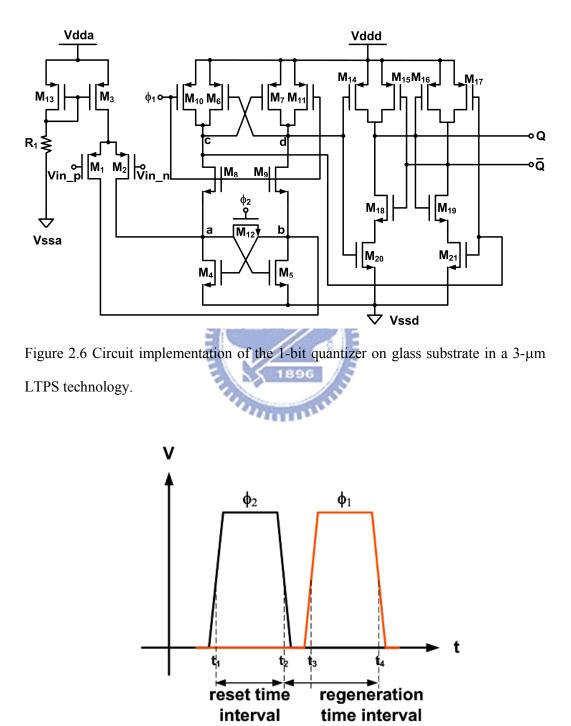

| Figure 2.6 Circuit implementation of the 1-bit quantizer on glass substrate in a 3-µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ì                                                                                                                                 |

| LTPS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                                                                |

| Figure 2.7 Time relation between $\phi_1$ and $\phi_2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                                                                |

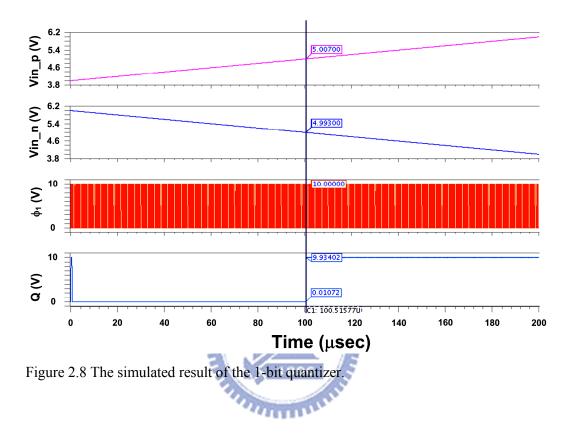

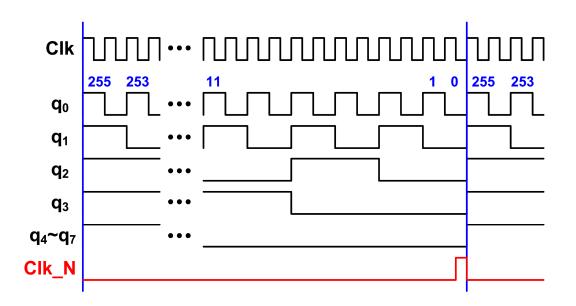

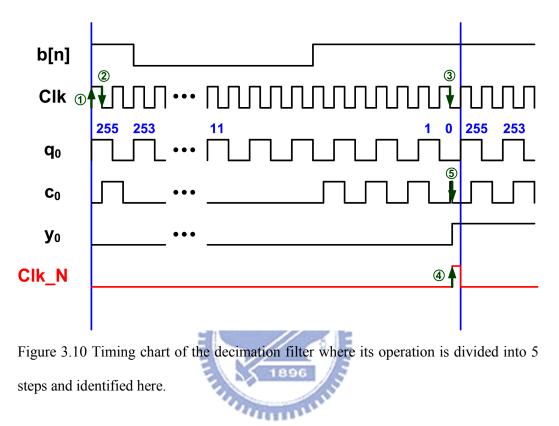

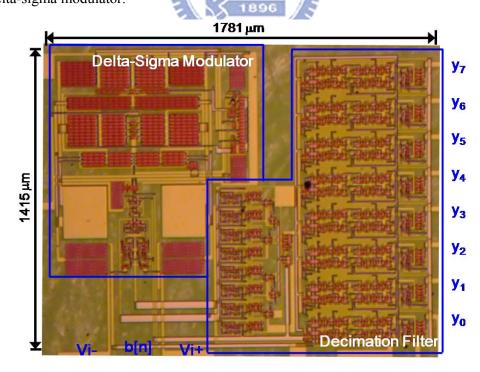

| Figure 2.8 The simulated result of the 1-bit quantizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                |