國 立 交 通 大 學

電 信 工 程 學 系

碩 士 論 文

WDM 全光環型網路之插入式存取協定設計

An Insertion Access Protocol for WDM All-optical

Unidirectional Ring Network

研 究 生：陳恭立

指 導 教 授：田伯隆 博 士

中 華 民 國 九 十 七 年 六 月

# WDM 全光環型網路之插入式存取協定設計

## An Insertion Access Protocol for WDM All-optical Unidirectional Ring Network

研究 生：陳恭立

Student : Kung-Li Chen

指 導 教 授：田 伯 隆 博 士

Advisor : Dr. Po-Lung Tien

國 立 交 通 大 學

電 信 工 程 學 系

Submitted to Department of Communication Engineering

College of Electrical and Computer Engineer

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master of Science

in Communication Engineering

June 2008

Hsinchu, Taiwan, Republic of China

中 華 民 國 九 十 七 年 六 月

# WDM 全光環型網路之插入式存取協定設計

學生：陳恭立

指導教授：田伯隆 博士

國立交通大學電信工程學系碩士班

## 摘要

在這篇論文裡我們主要針對都會型環狀單向光纖網路提出一個適宜的 MAC protocol，且此光纖網路可達成全光的目的，亦即 packet 從 source 端傳送至 destination 端中間的過程均以光的方式承載而不需經過光電的轉換。而我們設計這個 protocol 的目的是希望能達到在網路頻寬使用上的公平性以及在環狀拓樸的限制下達到最大的 network throughput。

此 protocol 的想法主要來自於針對 twin bus 光纖網路所設計之 ACCI protocol 且此 protocol 之特色為具有全分散式控制的架構。關於頻寬存取的機制上當 channel 為 idle 時為隨機存取而若當 channel 為 busy 時則採取控制存取的方式。

在本論文中將會對此 protocol 有清楚的描述且我們亦會對我們模擬所得的結果進行分析。並且由模擬的結果我們將會證明此 protocol 確實可以有效克服於此單一環狀光纖網路中所可能存在的公平性議題。

# An Insertion Access Protocol for WDM All-optical Unidirectional Ring Network

Student: Kung-Li Chen

Advisor : Dr. Po-Lung Tien

Department of Communication Engineering

National Chiao Tung University

## ABSTRACT

In this article, we proposed a MAC protocol for an Metro all-optical WDM unidirectional ring network where packets remain in optical domain from source to destination. The main targets which have been considered in the design of this protocol consist in the achievement of a highly fair access to the network resources and a network throughput performance close to the maximum values allowed in the adopted ring topology.

This protocol is based on the concepts of the ACCI protocol which is designed for a twin bus optical network and is characterized by a fully distributed control mechanism. Meanwhile, the access mechanism of proposed protocol is based on a random access if channel is idle and a controlled access if channel is busy.

A detailed description of the access protocol and results of simulation will be given in the text. It will be proven that the issue of fairness arising from unidirectional optical ring network will be circumvented.

## 誌 謝

本篇論文得以如期完成，首先感謝我的指導教授田伯隆老師在這一年多來於研究過程中細心的指導。在與老師討論的過程中，使我學會了解決問題應有的態度以及方法，幫助我在光纖網路的研究領域中建立信心且獲益良多。

感謝實驗室學長啟賢在研究上的細心解答以及生活上的扶持與關照，另外也謝謝學弟禕達、偉民以及逸曼平時在研究課題上的討論。最後謹以此論文獻給始終在背後默默支持我的父母以及所有關心我的人。

# 目 錄

|           |                                                                 |      |

|-----------|-----------------------------------------------------------------|------|

| 中文摘要      | .....                                                           | i    |

| 英文摘要      | .....                                                           | ii   |

| 誌謝        | .....                                                           | iii  |

| 目錄        | .....                                                           | iv   |

| 圖目錄       | .....                                                           | v    |

| 表目錄       | .....                                                           | viii |

| Chapter 1 | Introduction.....                                               | 1    |

| Chapter 2 | Background.....                                                 | 4    |

| 2.1       | The ACCI access protocol.....                                   | 4    |

| 2.1-1     | Introduction of ACCI protocol.....                              | 4    |

| 2.1-2     | Basic concepts of ACCI protocol.....                            | 5    |

| 2.1-3     | Cell format of ACCI protocol .....                              | 7    |

| 2.1-4     | Access procedure of ACCI protocol .....                         | 9    |

| 2.1-5     | Overload control of ACCI protocol .....                         | 15   |

| 2.2       | The RPR fairness algorithm.....                                 | 17   |

| 2.3       | Individual Wavelength Switching and Photonic Slot Routing ..... | 23   |

| Chapter 3 | Proposed Protocol.....                                          | 28   |

| 3.1       | Network architecture and format of Photonic Slot.....           | 28   |

| 3.2       | Proposed protocol for IWS .....                                 | 31   |

| 3.2-1     | Basic concepts .....                                            | 31   |

| 3.2-2     | Node architecture and removal mechanism .....                   | 33   |

| 3.2-3     | Access procedure of proposed protocol for IWS.....              | 35   |

| 3.3       | Proposed protocol for PSS.....                                  | 42   |

| 3.3-1     | Basic concepts .....                                            | 42   |

| 3.3-2     | Node architecture and removal mechanism .....                   | 44   |

| 3.3-3     | Access procedure of proposed protocol for PSS .....             | 46   |

| Chapter 4 | Simulation Results and Performance Analysis .....               | 55   |

| 4.1       | Network parameters and traffic model .....                      | 55   |

| 4.2       | Simulation results for IWS.....                                 | 60   |

| 4.3       | Simulation results for PSS.....                                 | 70   |

| Chapter 5 | Conclusions and Future Works.....                               | 77   |

| Reference | .....                                                           | 78   |

## 圖 目 錄

|             |                                                  |    |

|-------------|--------------------------------------------------|----|

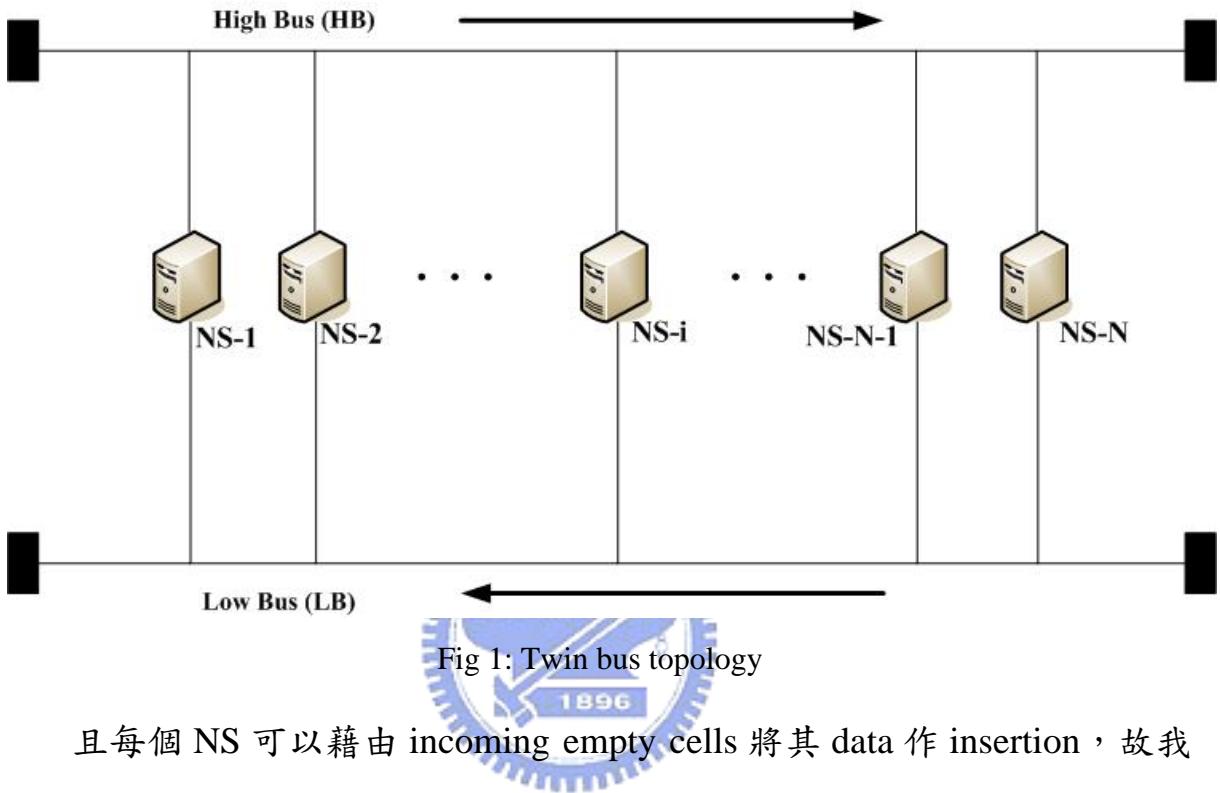

| Figure 1    | Twin bus topology.....                           | 6  |

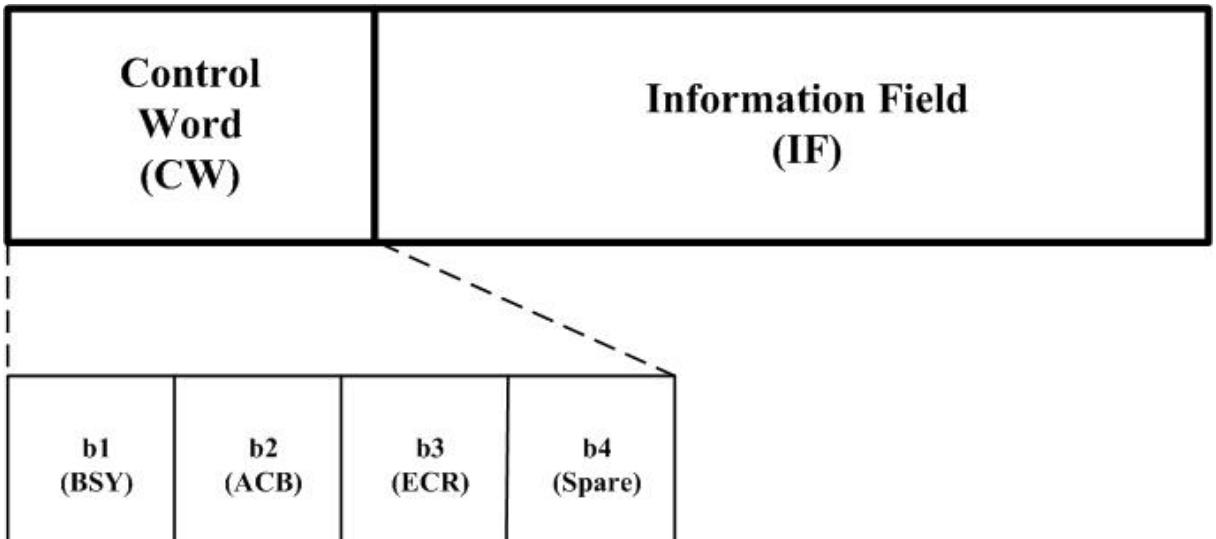

| Figure 2    | Cell format of ACCI protocol.....                | 8  |

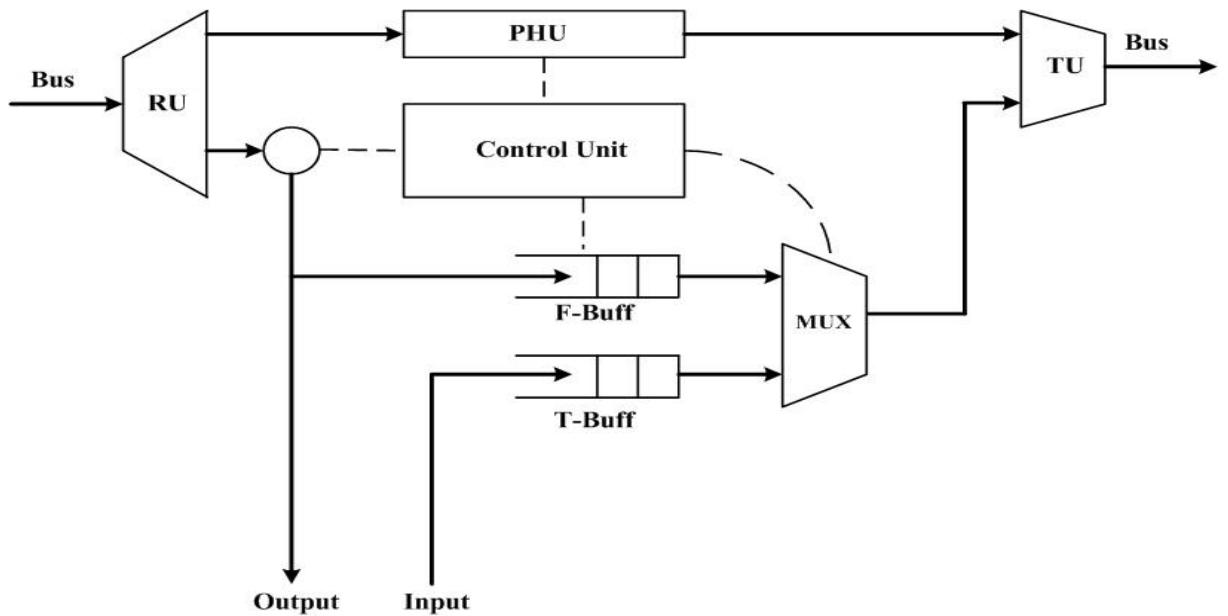

| Figure 3    | NS-bus interface of ACCI protocol.....           | 10 |

| Figure 4-1  | Transmitting step of case (i) .....              | 11 |

| Figure 4-2  | Transmitting step of case (ii) .....             | 12 |

| Figure 4-3  | Transmitting step of case (iii) .....            | 13 |

| Figure 4-4  | Transmitting step of case (iv) .....             | 13 |

| Figure 4-5  | Transmitting step of case (v) .....              | 14 |

| Figure 4-6  | Transmitting step of case (vi) .....             | 15 |

| Figure 5    | Architecture of RPR station.....                 | 18 |

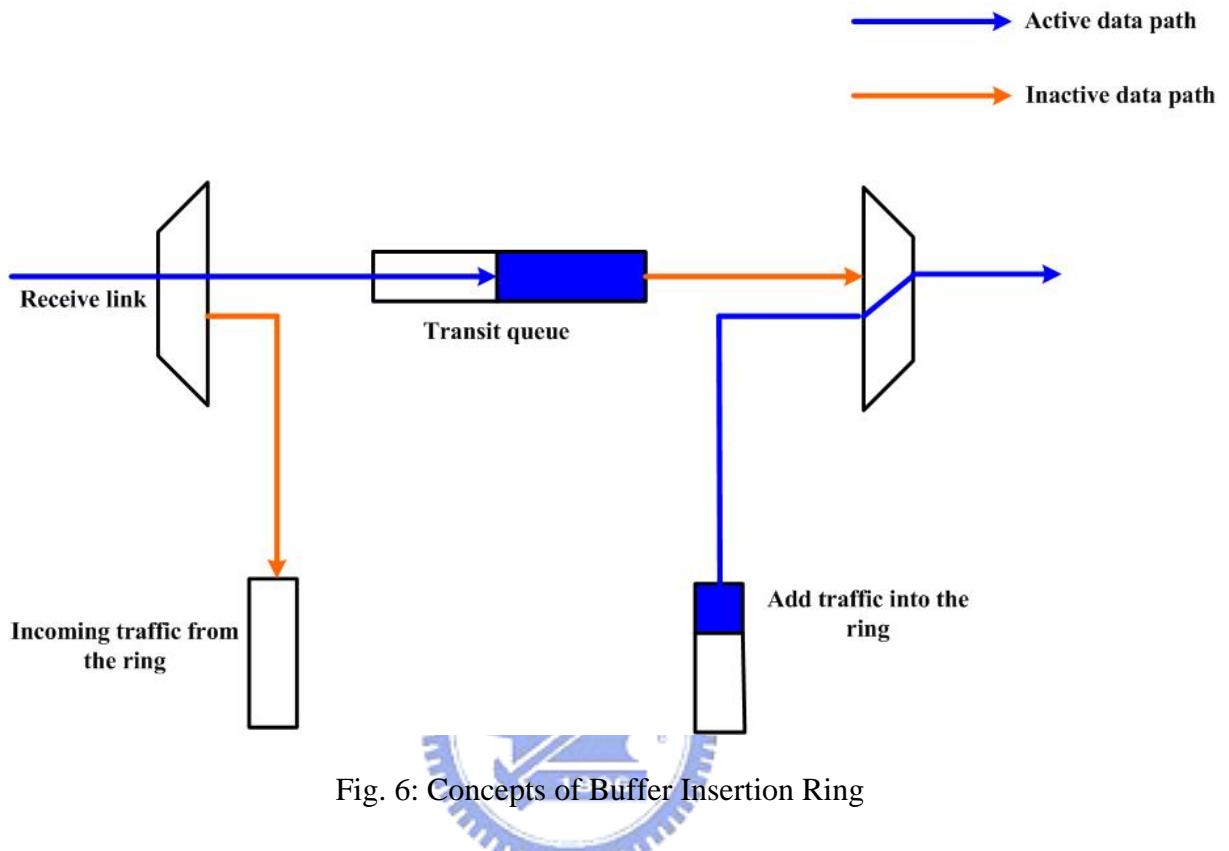

| Figure 6    | Concepts of Buffer Insertion Ring.....           | 19 |

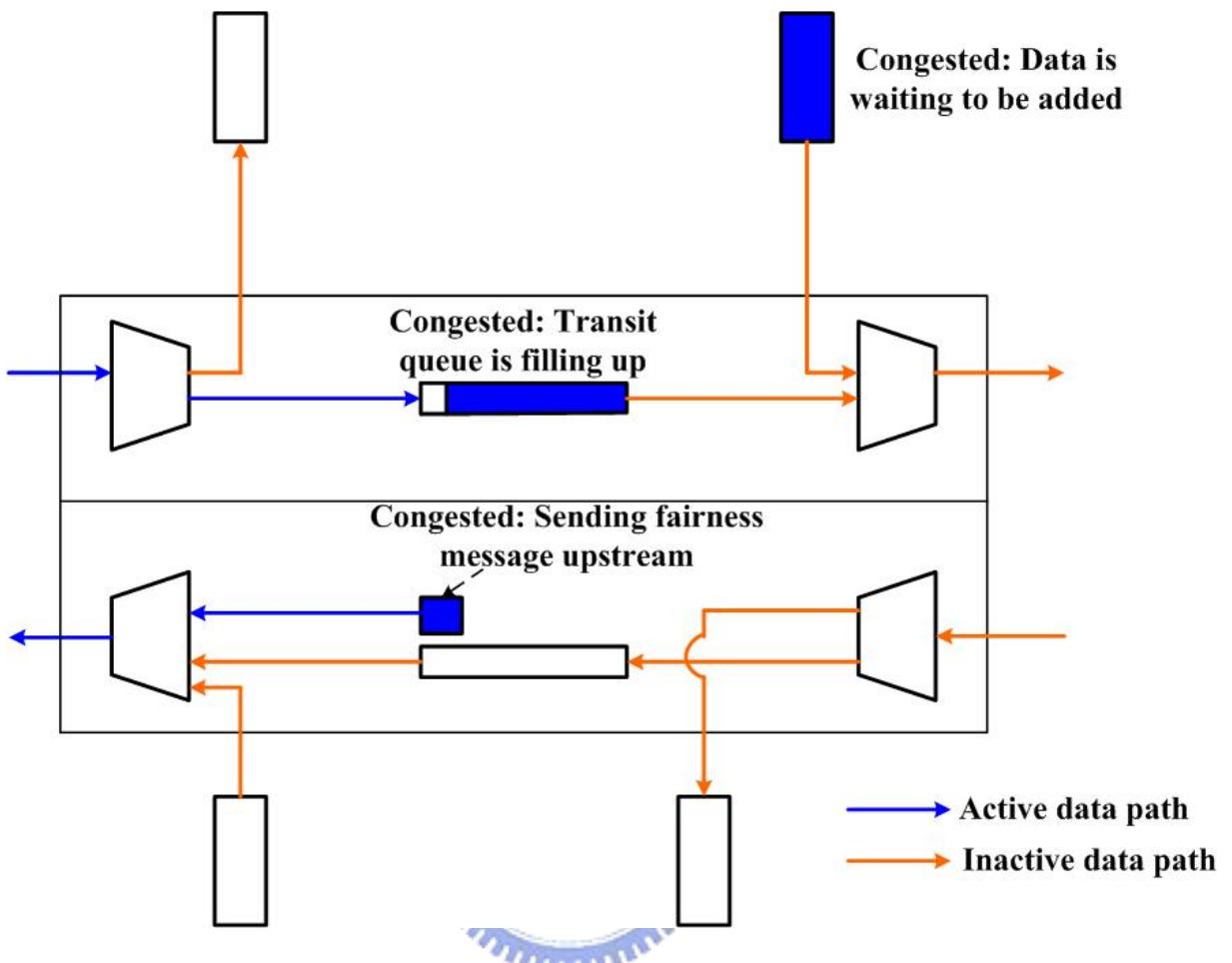

| Figure 7    | When a station becomes congested.....            | 20 |

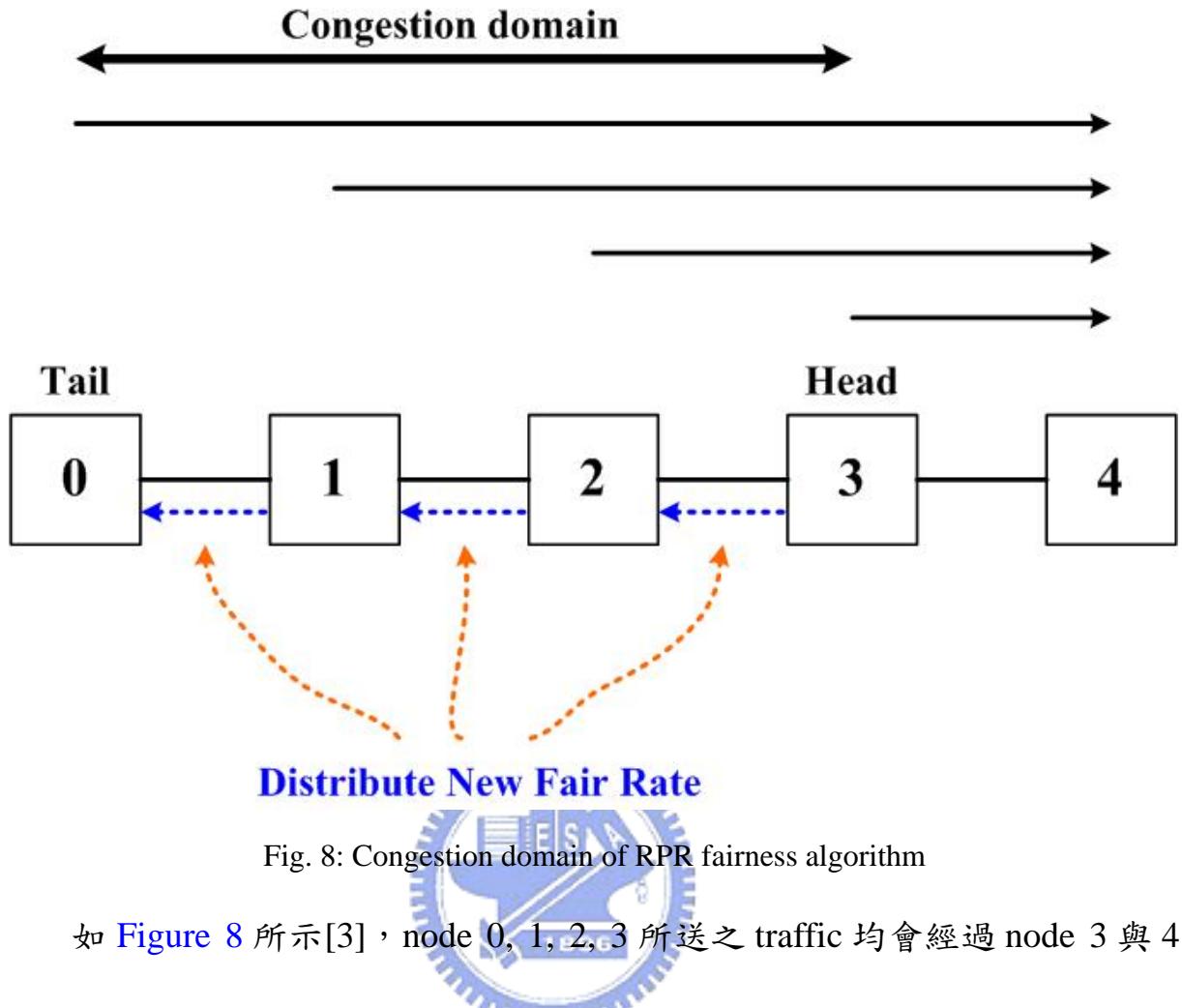

| Figure 8    | Congestion domain of RPR fairness algorithm..... | 21 |

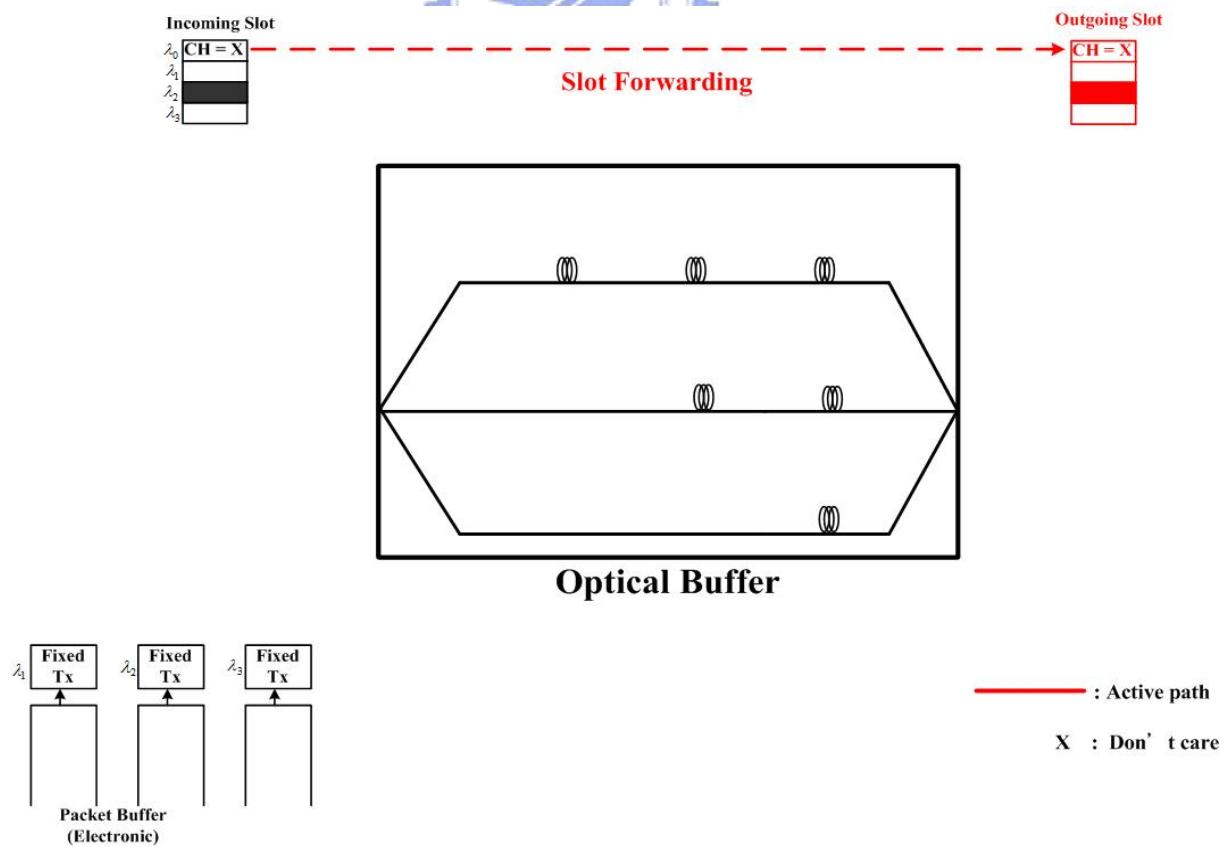

| Figure 9    | Spatial Reuse of IWS node.....                   | 24 |

| Figure 10   | Destination constrain of PSR.....                | 25 |

| Figure 11   | PSS (removal of destination constrain) .....     | 26 |

| Figure 12   | Network architecture.....                        | 28 |

| Figure 13   | Format of Photonic Slot.....                     | 30 |

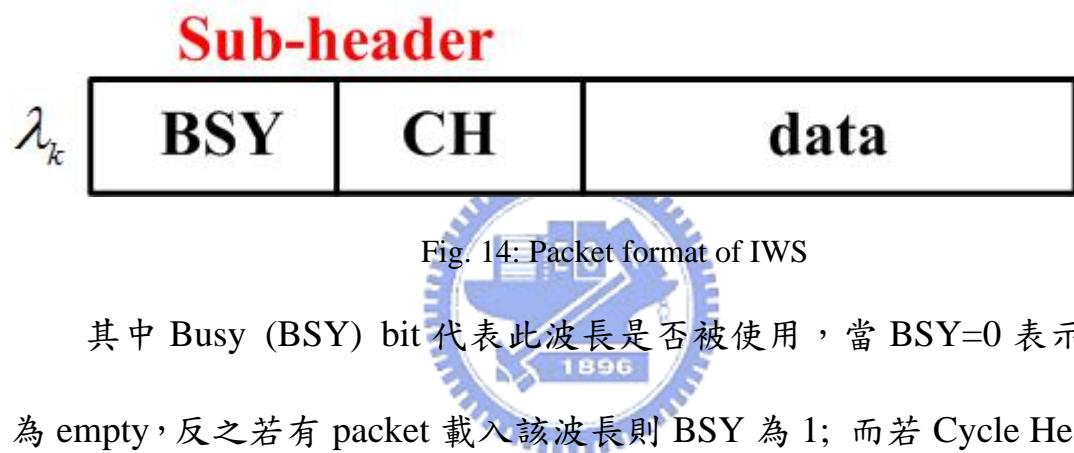

| Figure 14   | Packet format of IWS.....                        | 33 |

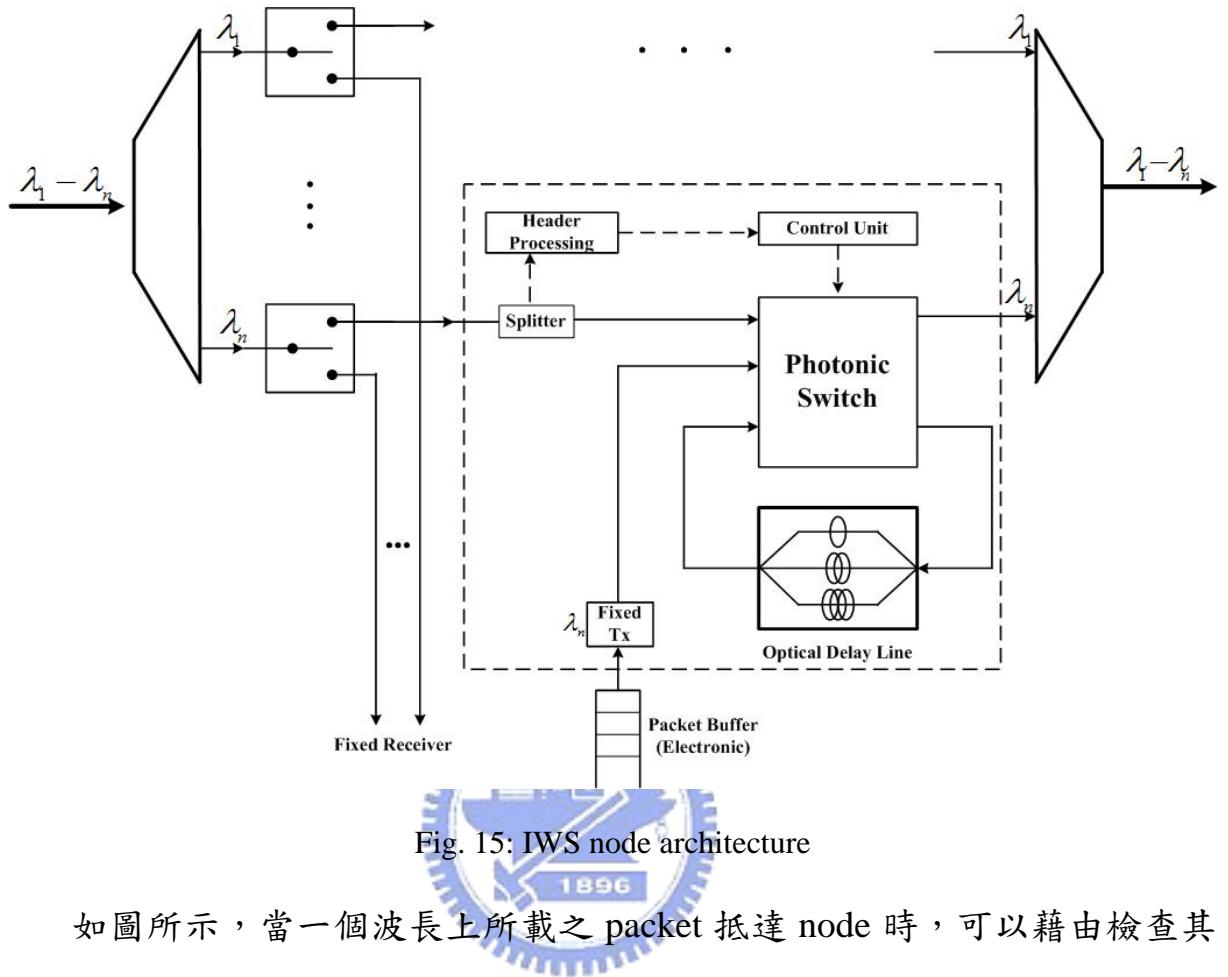

| Figure 15   | IWS node architecture.....                       | 34 |

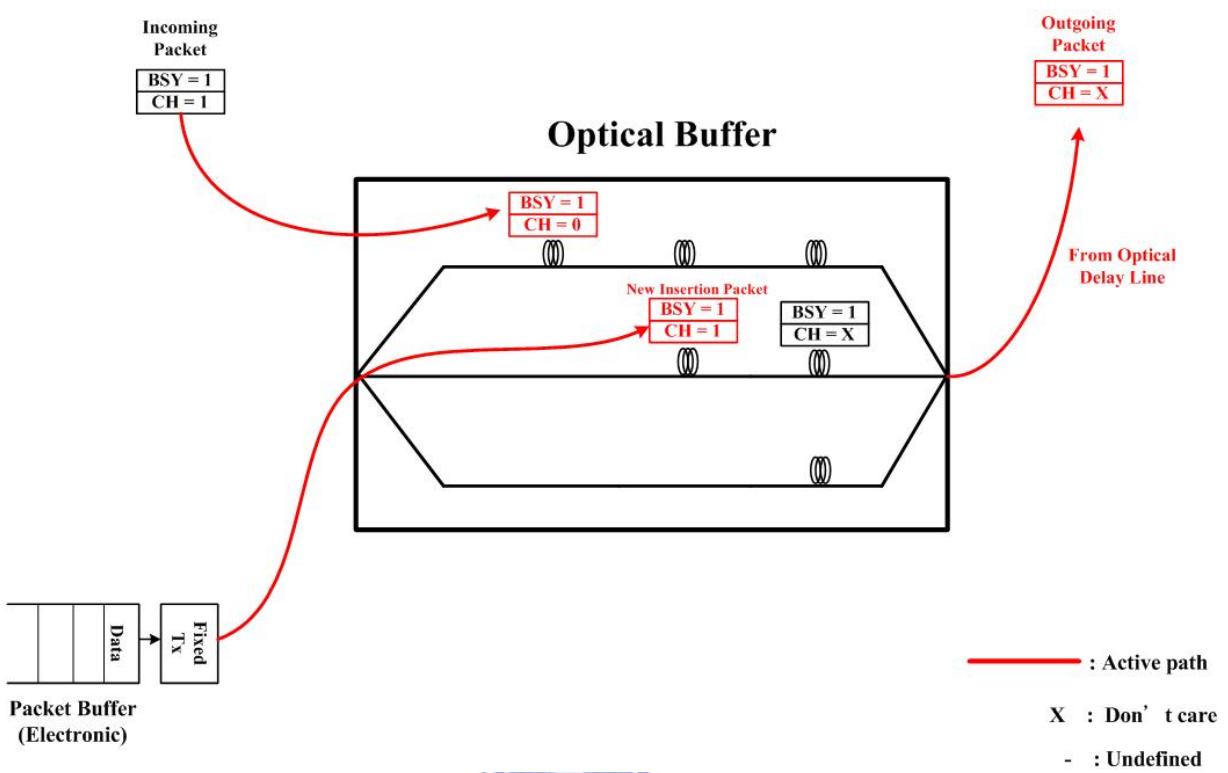

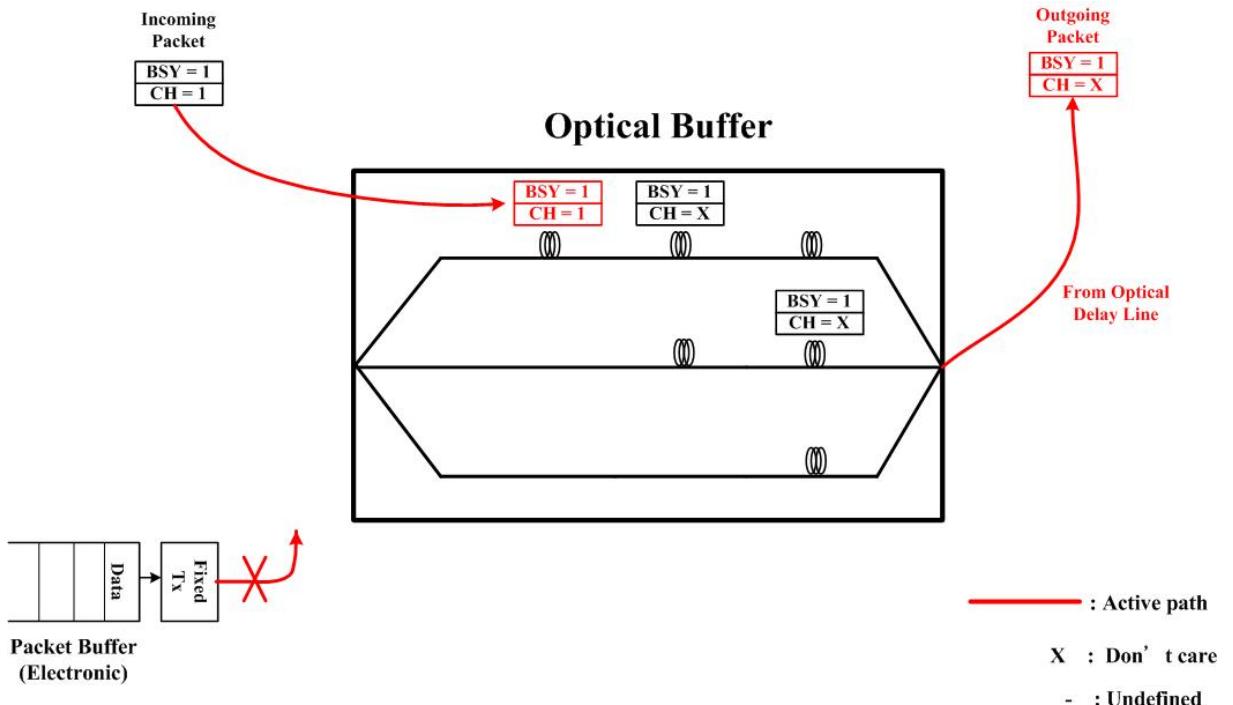

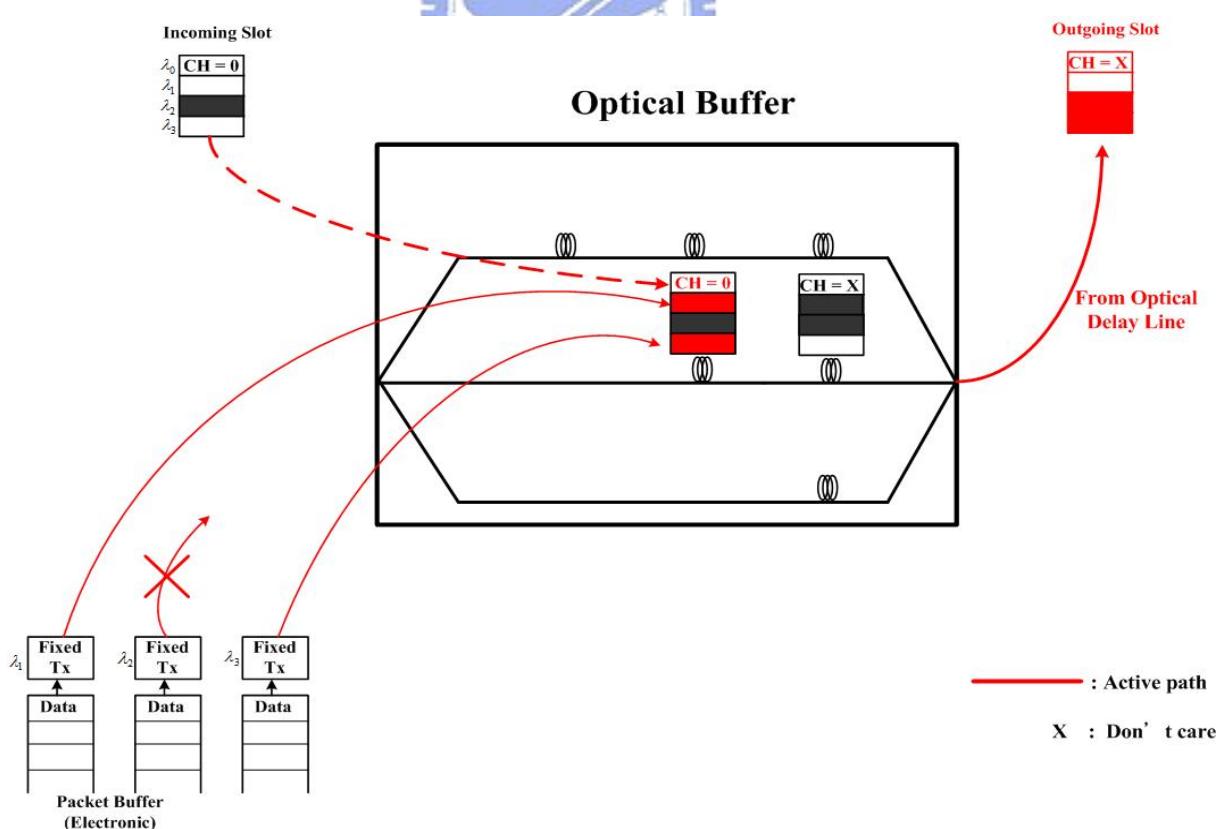

| Figure 16-1 | Transmitting step of case (i) for IWS.....       | 36 |

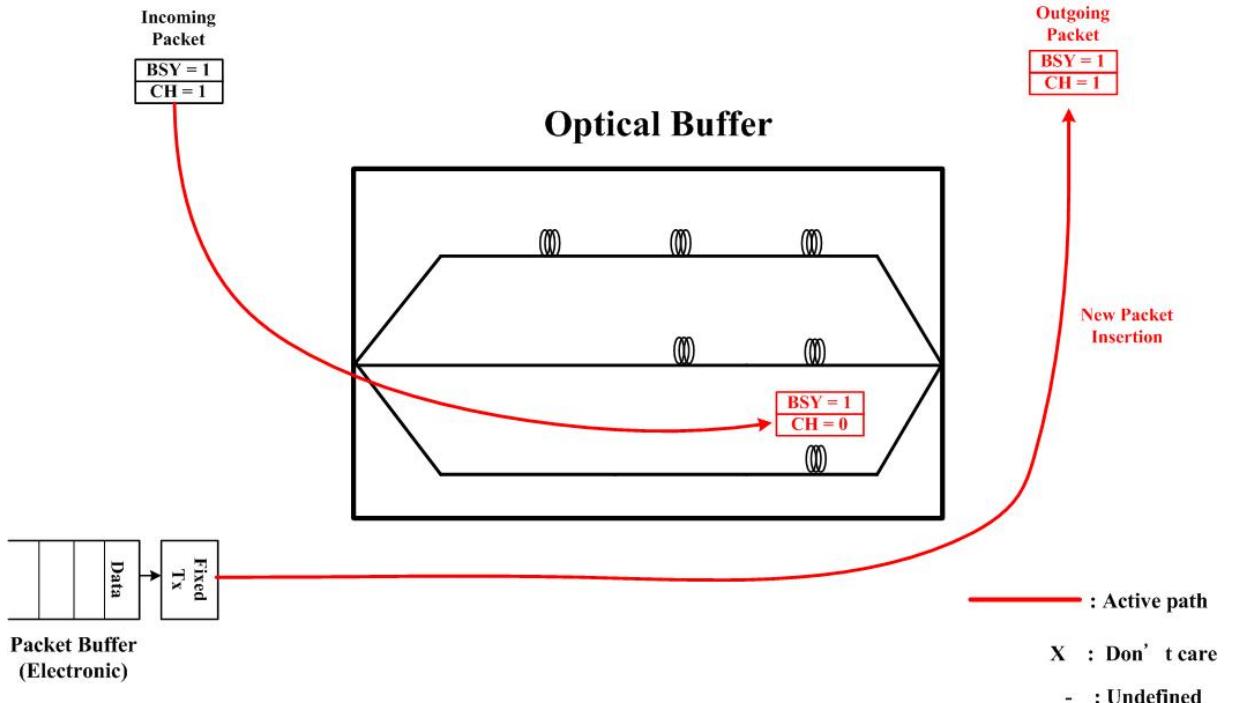

| Figure 16-2 | Transmitting step of case (i)-2 for IWS.....     | 37 |

| Figure 16-3 | Transmitting step of case (i)-3 for IWS.....     | 38 |

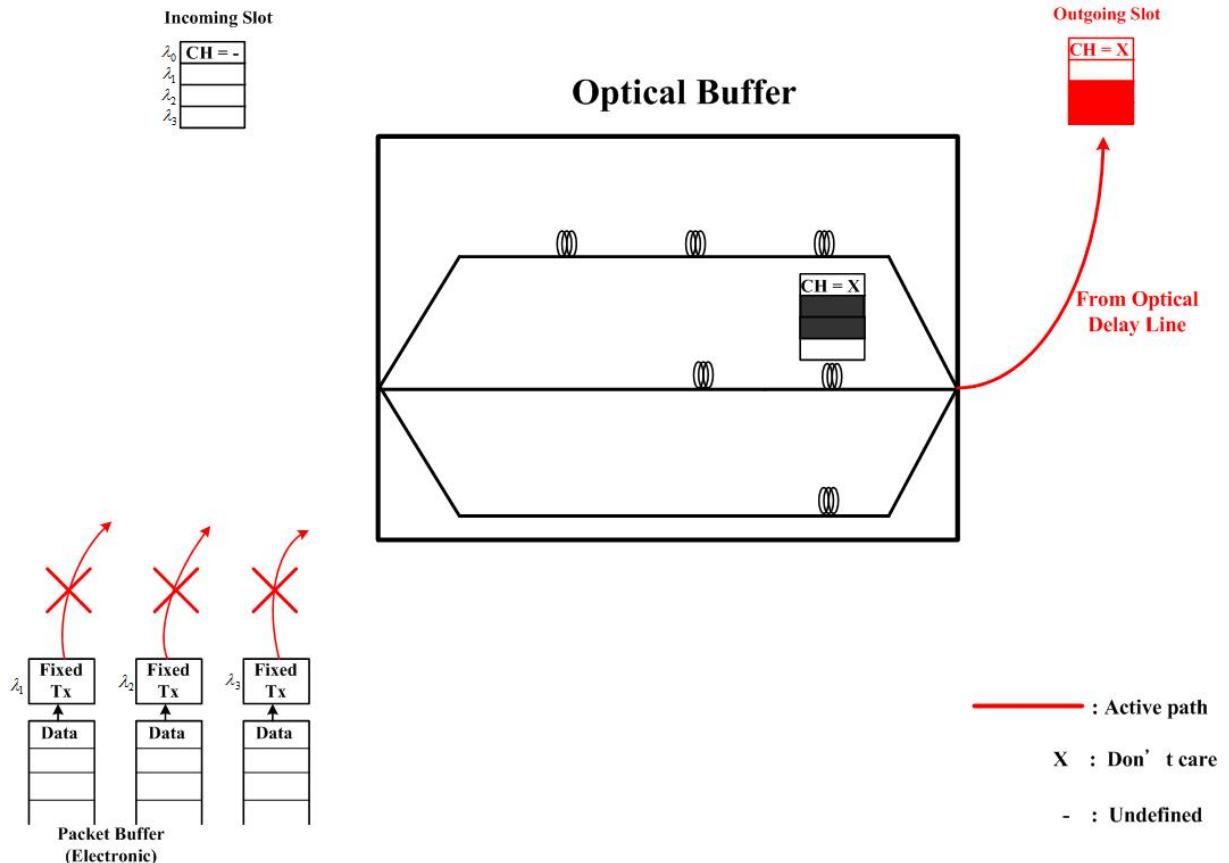

| Figure 17-1 | Transmitting step of case (ii)-1 for IWS.....    | 39 |

| Figure 17-2 | Transmitting step of case (ii)-2 for IWS.....    | 39 |

| Figure 18-1 | Transmitting step of case (iii)-1 for IWS.....   | 40 |

| Figure 18-2 | Transmitting step of case (iii)-2 for IWS.....   | 40 |

| Figure 19-1 | Transmitting step of case (iv)-1 for IWS.....    | 41 |

| Figure 19-2 | Transmitting step of case (iv)-2 for IWS.....    | 41 |

| Figure 20   | Slot format of PSS.....                          | 44 |

| Figure 21   | PSS node architecture.....                       | 45 |

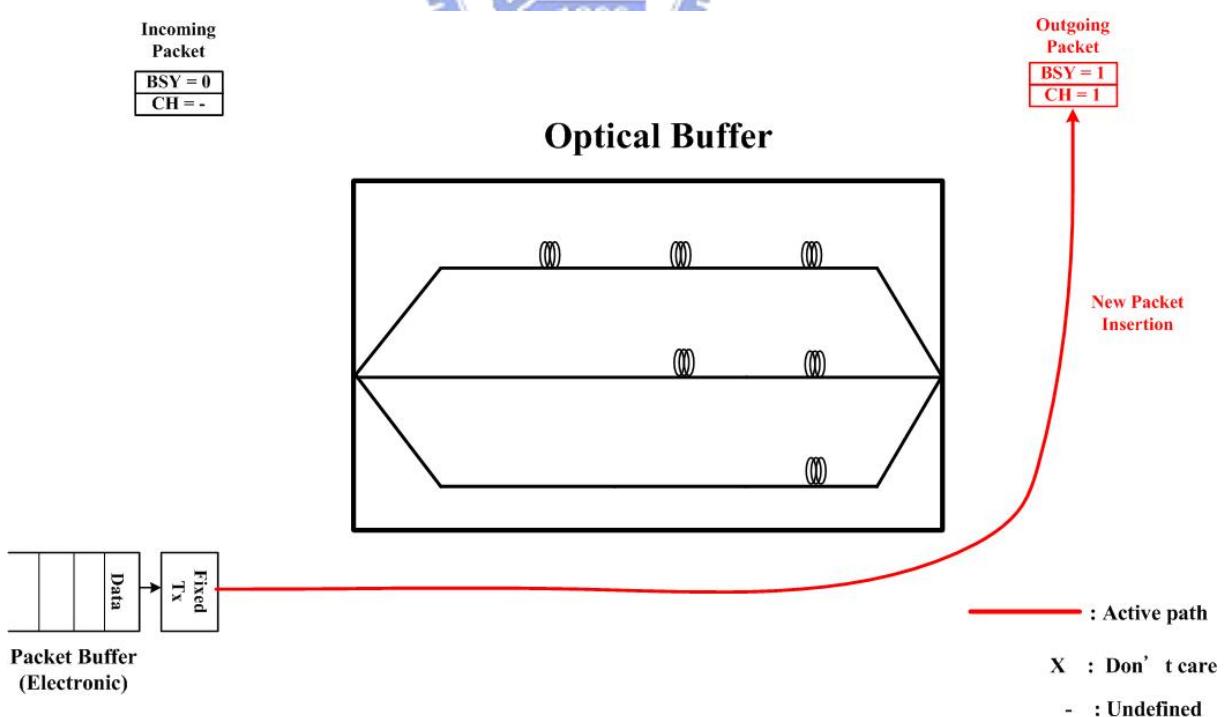

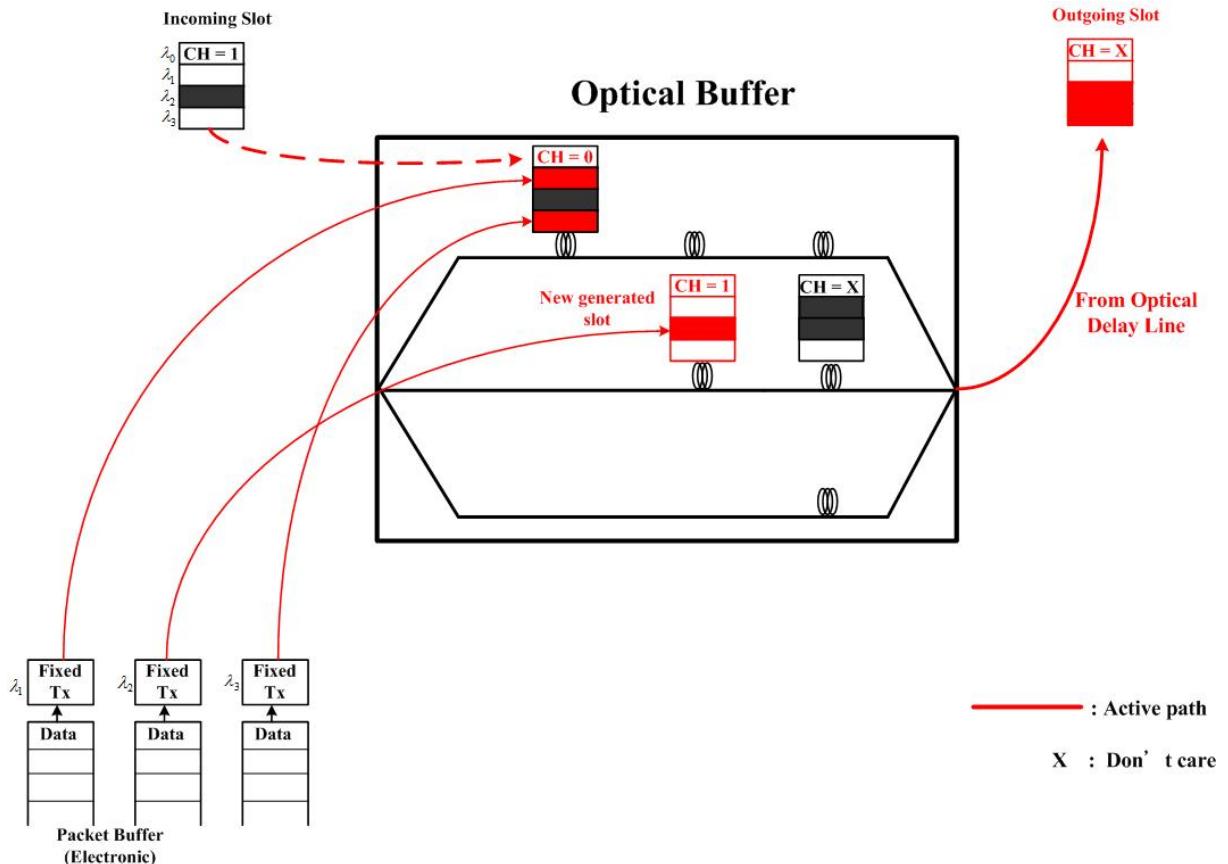

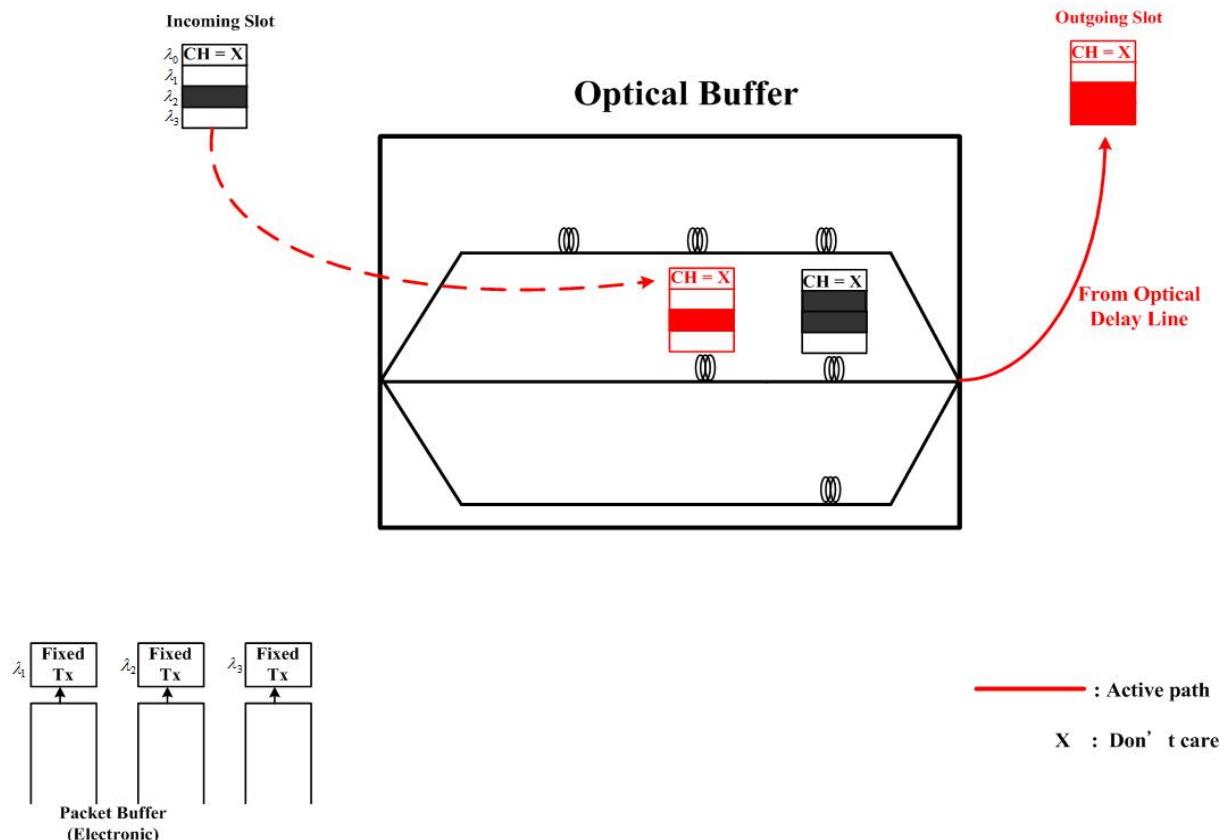

| Figure 22-1 | Transmitting step of case (i)-1 for PSS.....     | 47 |

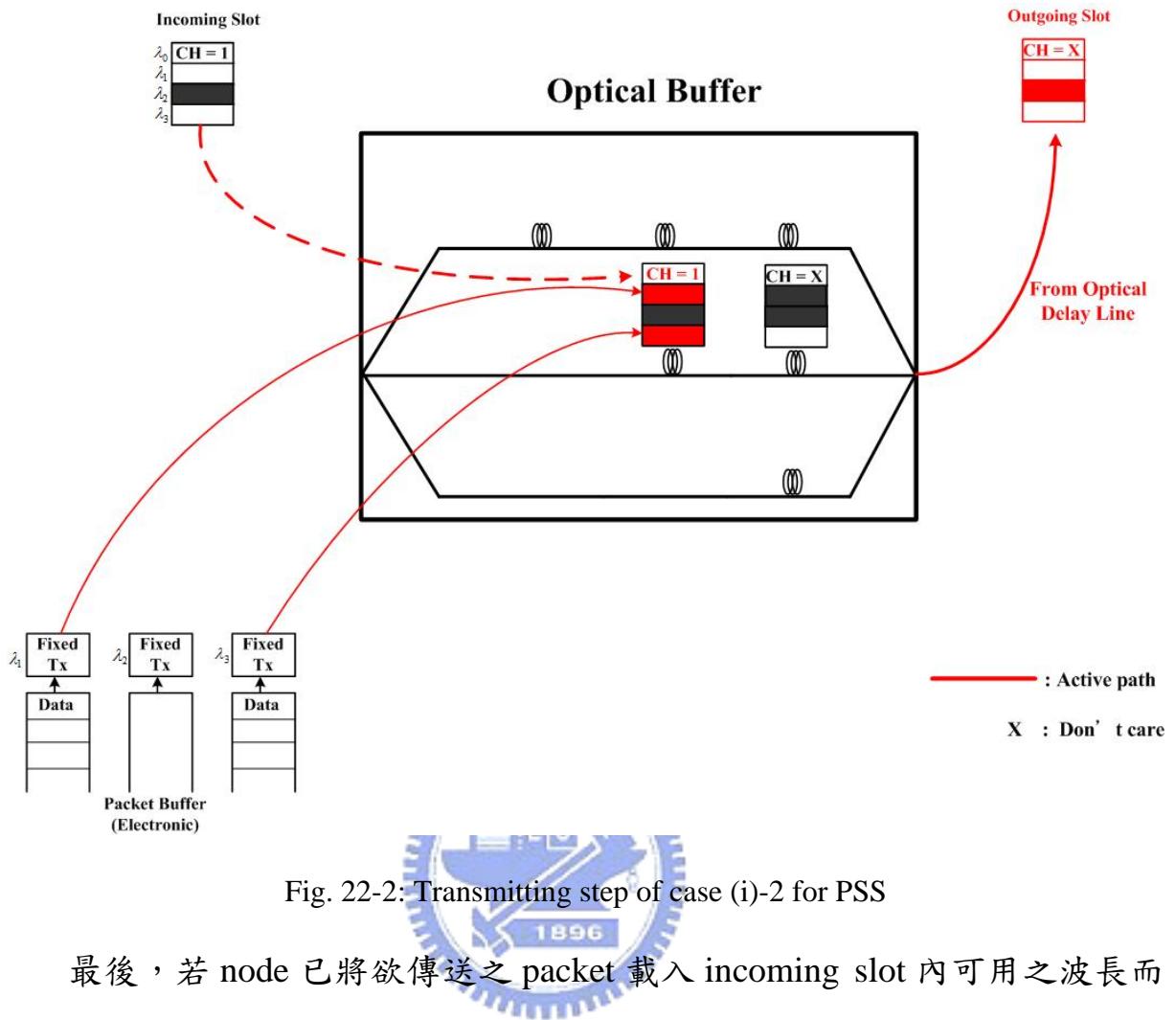

| Figure 22-2 | Transmitting step of case (i)-2 for PSS.....     | 48 |

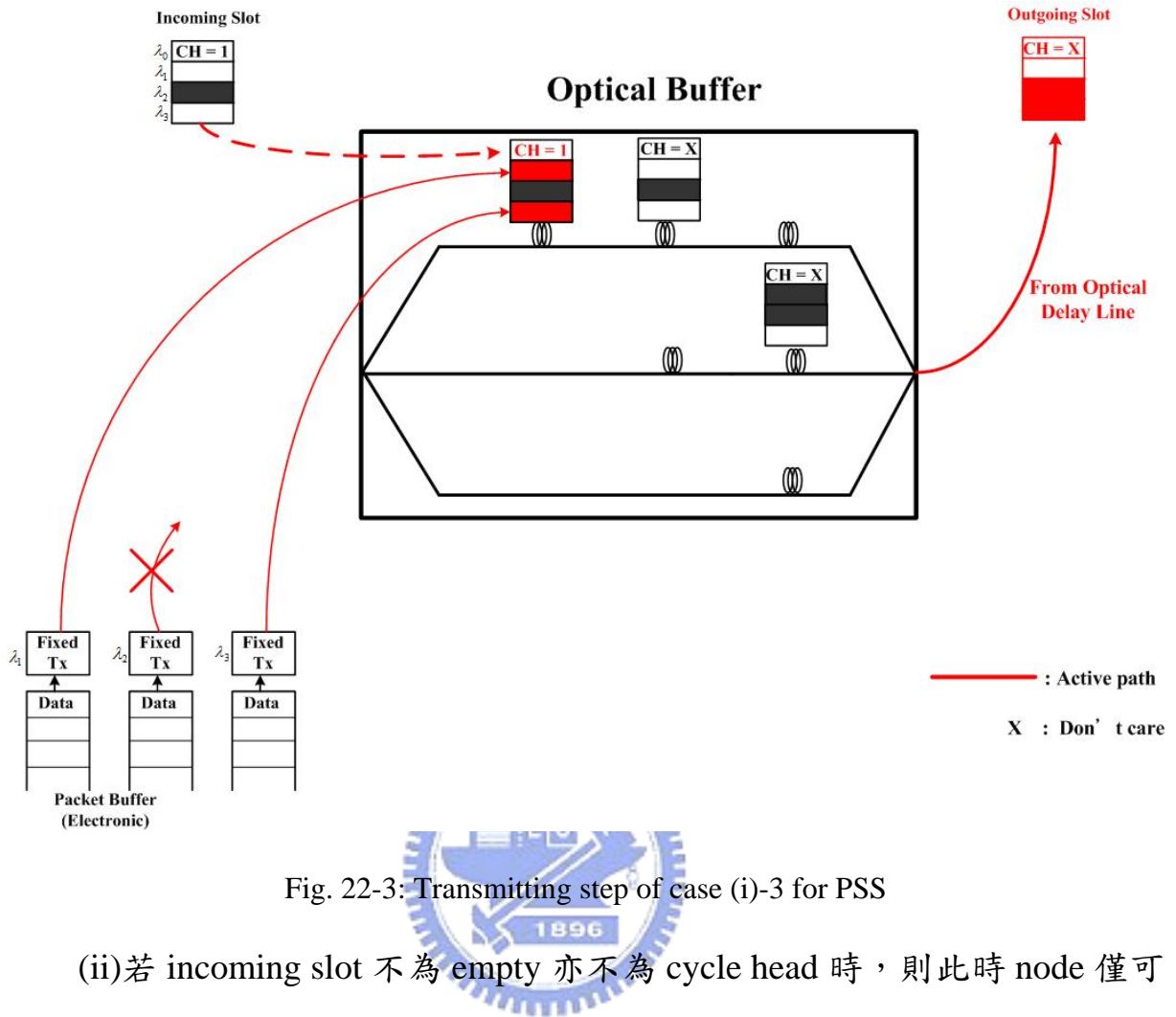

| Figure 22-3 | Transmitting step of case (i)-3 for PSS.....     | 49 |

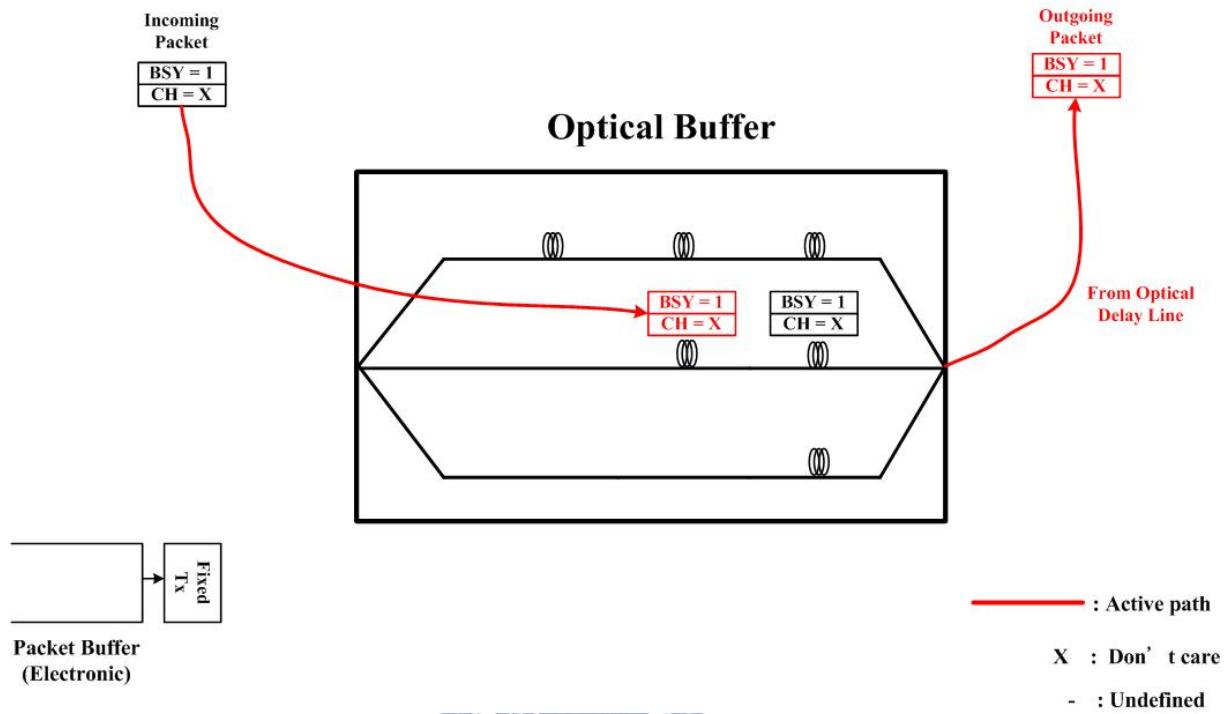

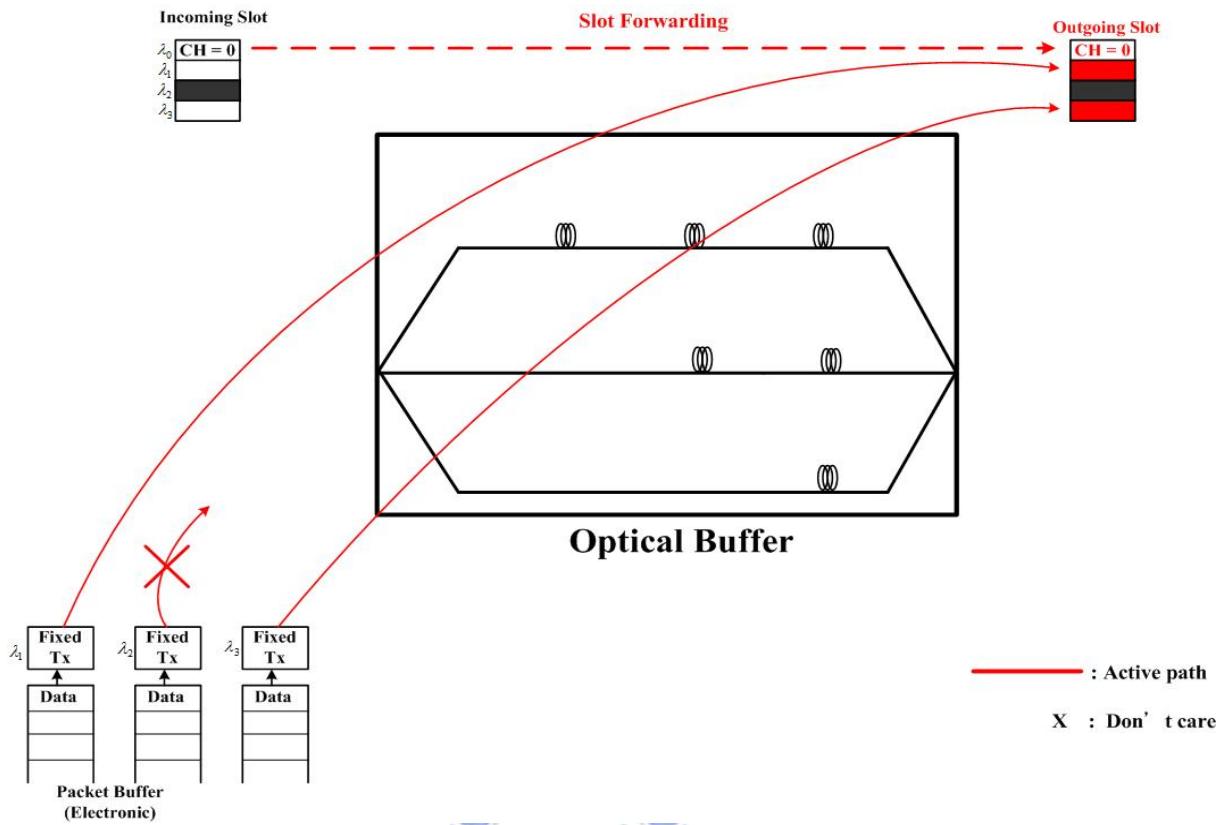

| Figure 23-1 | Transmitting step of case (ii)-1 for PSS.....    | 50 |

| Figure 23-2 | Transmitting step of case (ii)-2 for PSS.....    | 50 |

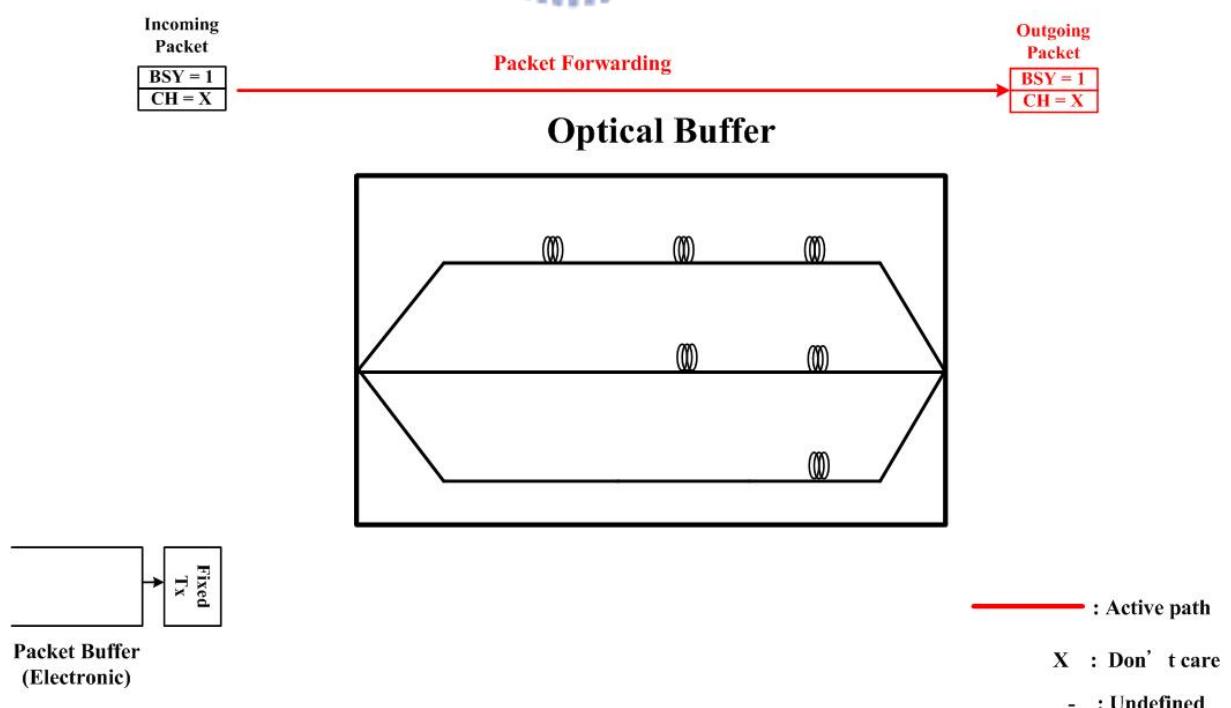

| Figure 24-1 | Transmitting step of case (iii)-1 for PSS.....   | 51 |

| Figure 24-2 | Transmitting step of case (iii)-2 for PSS.....   | 52 |

|             |                                                                                                      |    |

|-------------|------------------------------------------------------------------------------------------------------|----|

| Figure 25-1 | Transmitting step of case (iv)-1 for PSS.....                                                        | 53 |

| Figure 25-2 | Transmitting step of case (iv)-2 for PSS.....                                                        | 53 |

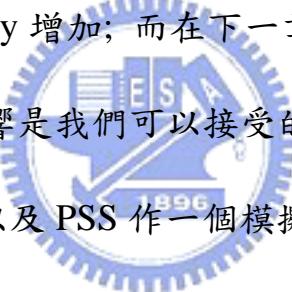

| Figure 26   | Two state bursty traffic model.....                                                                  | 56 |

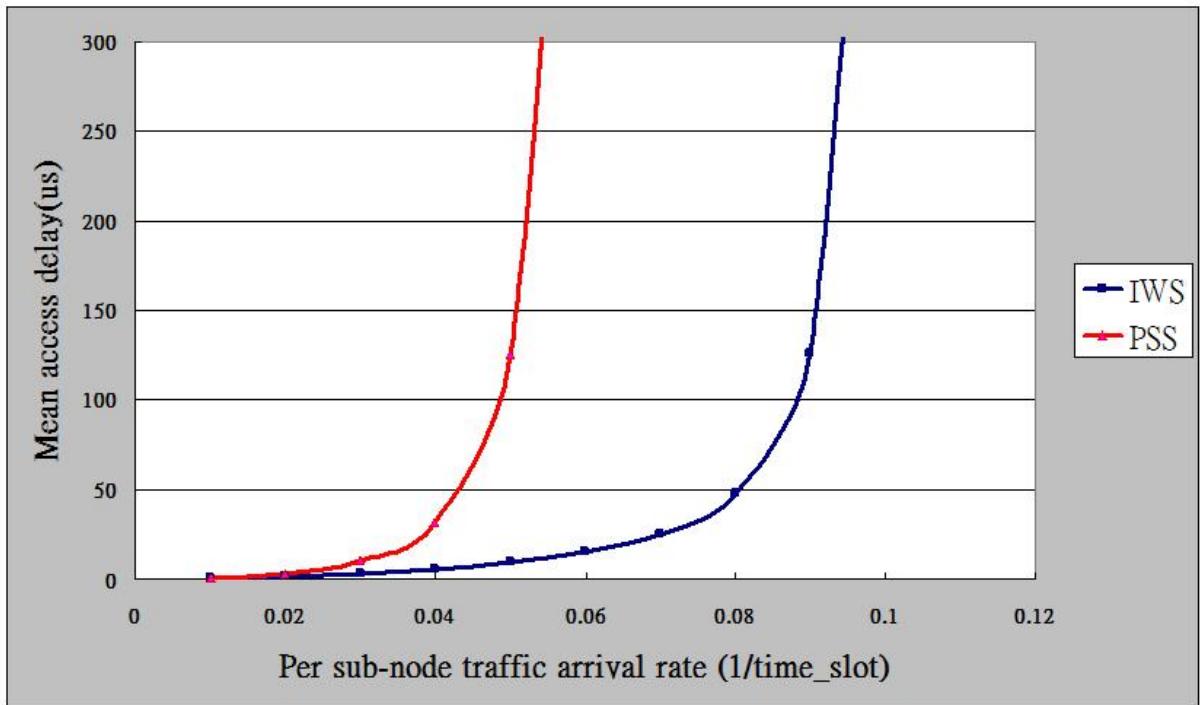

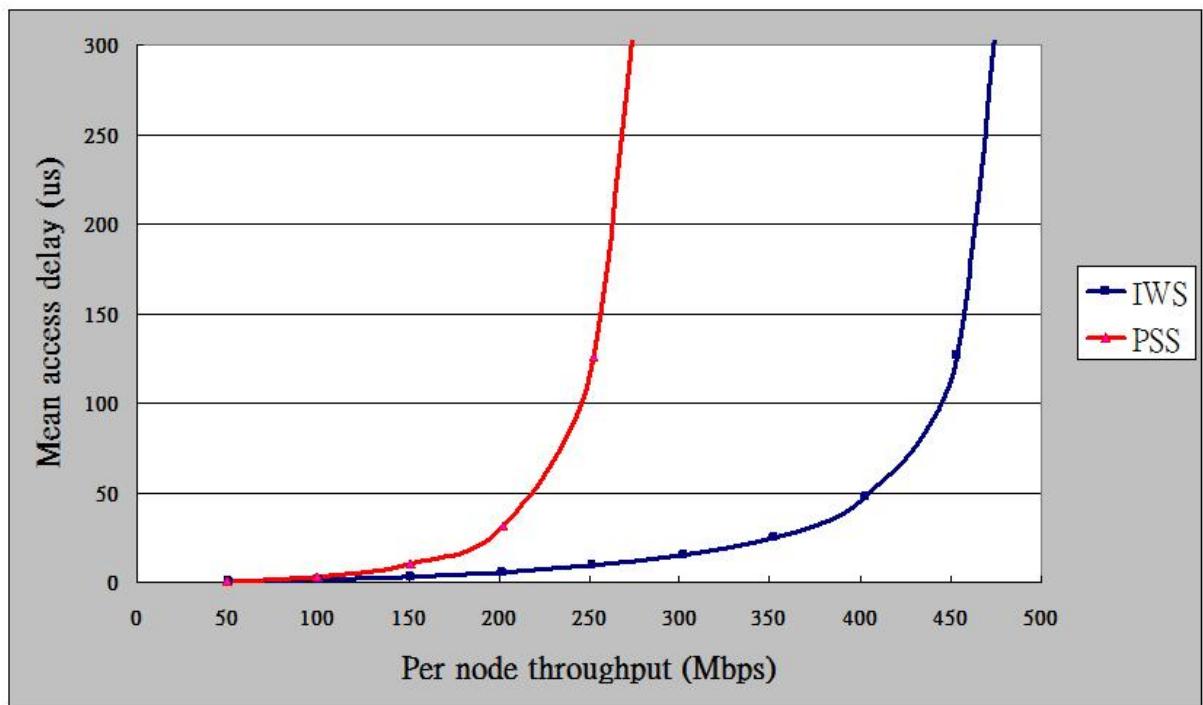

| Figure 27-1 | Mean access delay vs per sub-node traffic arrival rate of IWS and PSS in fully balanced traffic..... | 58 |

| Figure 27-2 | Mean access delay vs per node throughput of IWS and PSS in fully balanced traffic.....               | 59 |

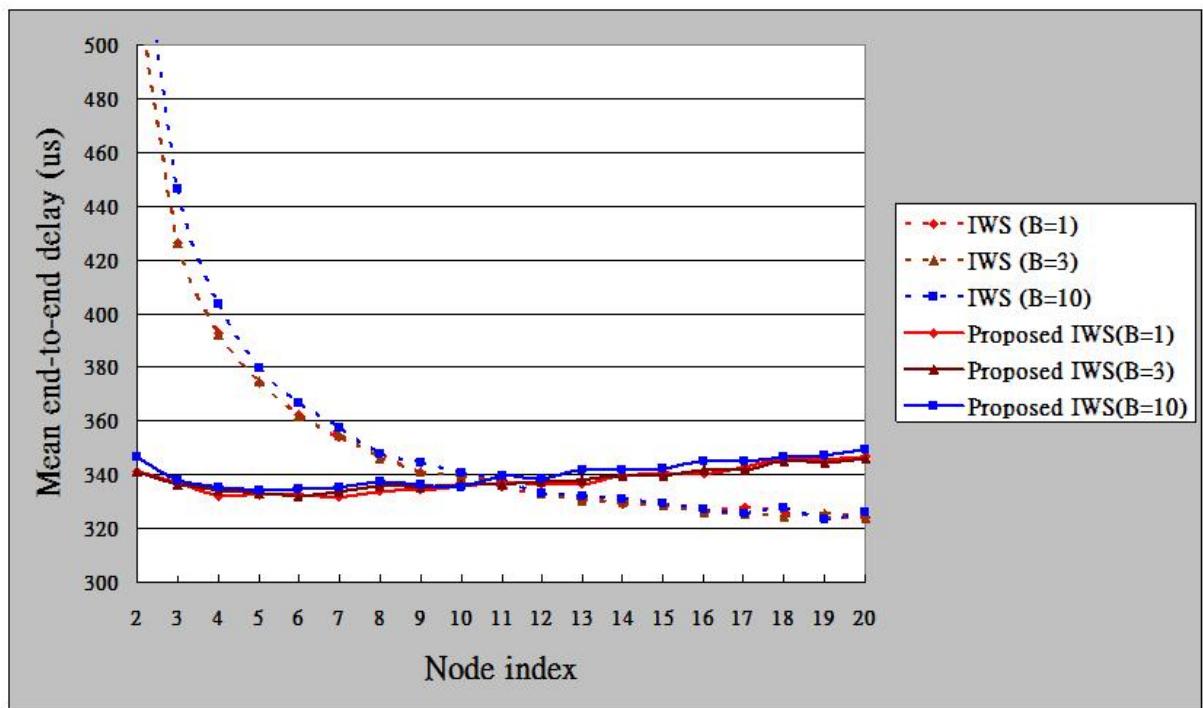

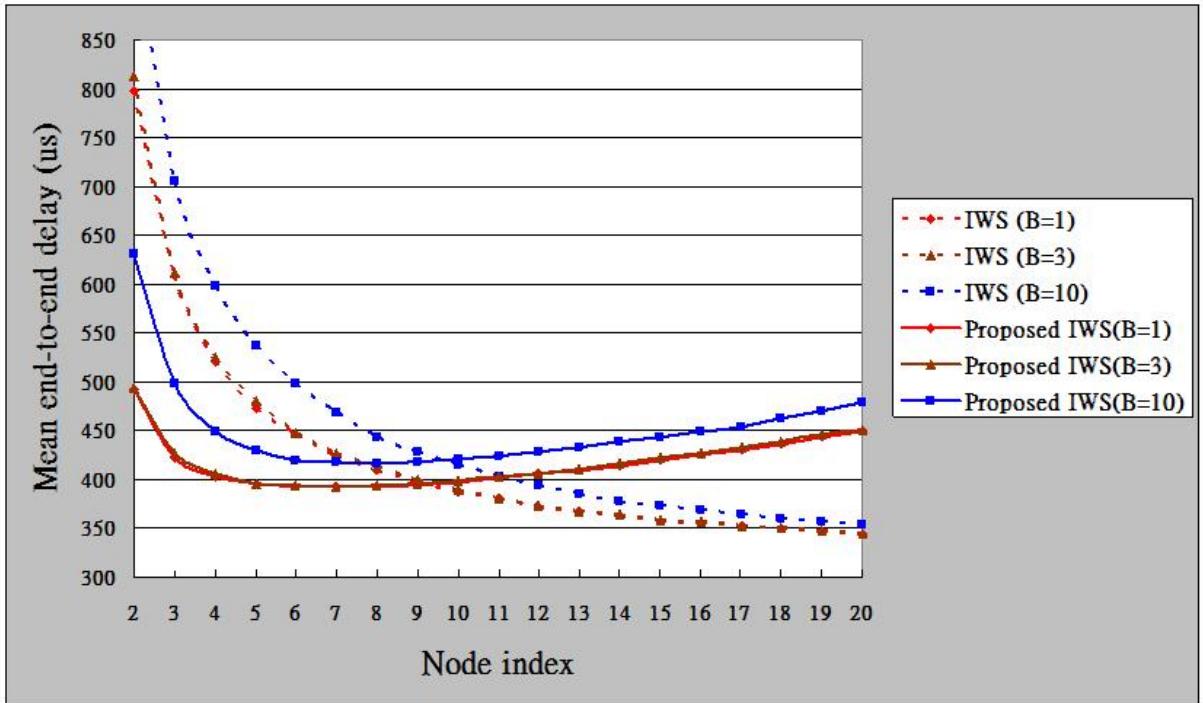

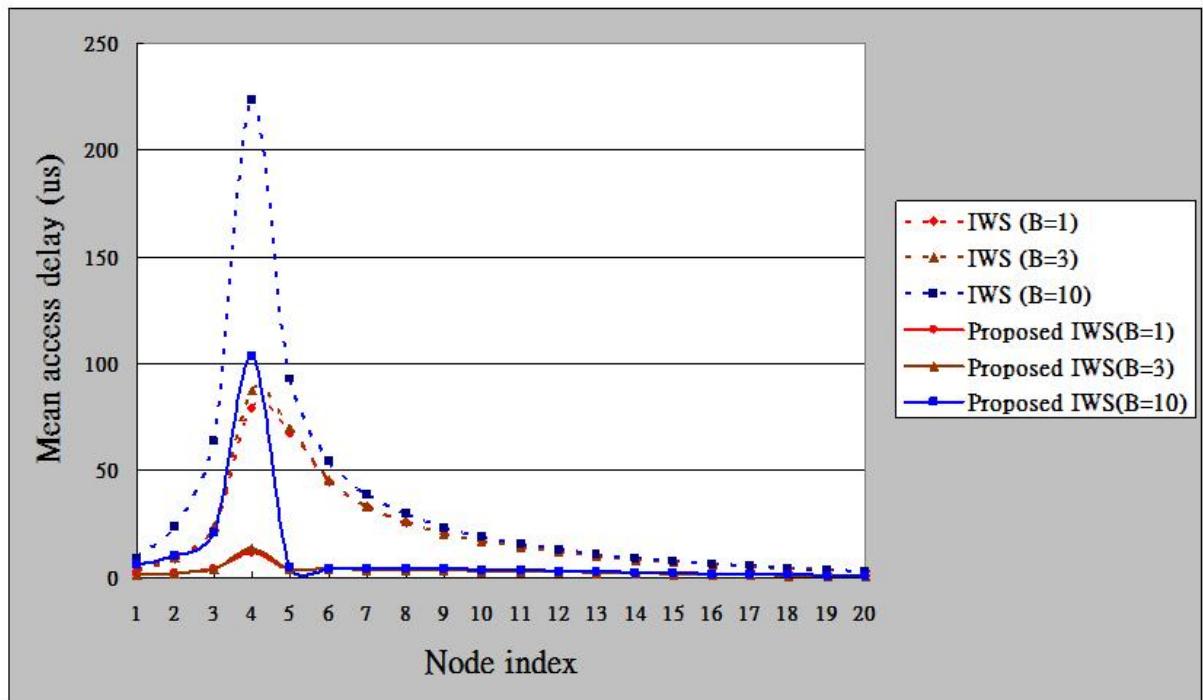

| Figure 28-1 | Mean access delay vs node index in case 1 of unbalanced traffic.....                                 | 61 |

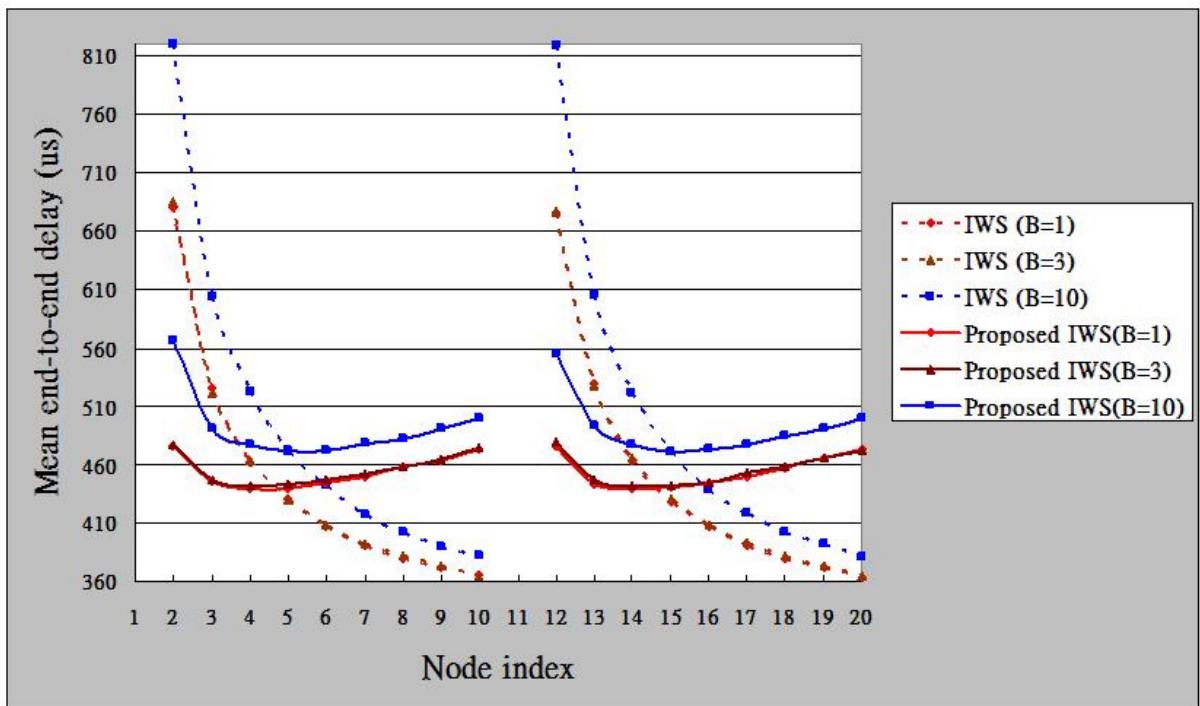

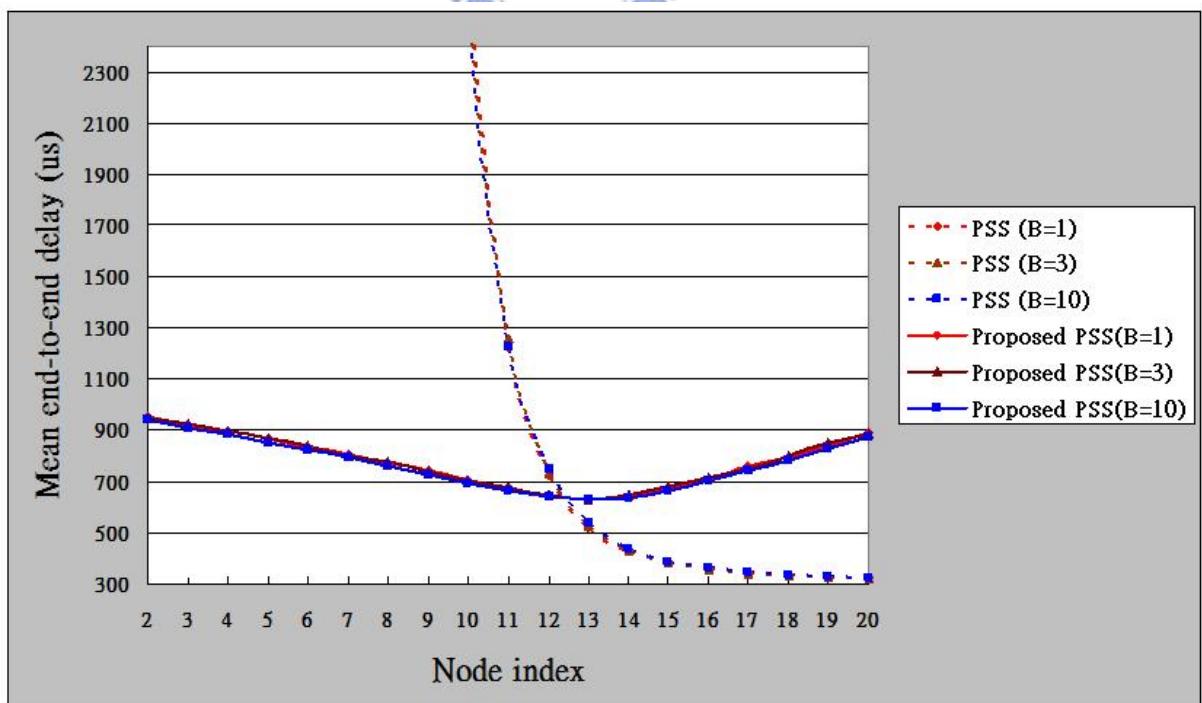

| Figure 28-2 | Mean end-to-end delay vs node index in case 1 of unbalanced traffic.....                             | 62 |

| Figure 29-1 | Mean access delay vs node index in case 2 of unbalanced traffic.....                                 | 62 |

| Figure 29-2 | Mean end-to-end delay vs node index in case 2 of unbalanced traffic.....                             | 63 |

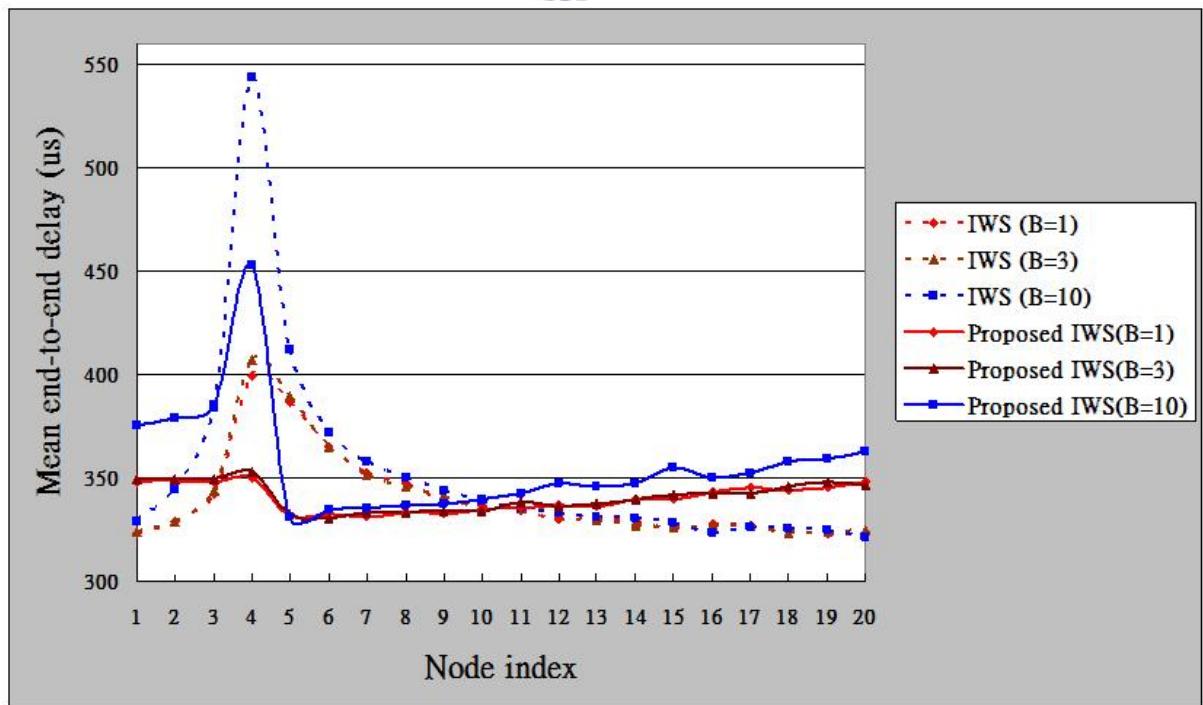

| Figure 30-1 | Mean access delay vs node index in case 3 of unbalanced traffic.....                                 | 65 |

| Figure 30-2 | Mean end-to-end delay vs node index in case 3 of unbalanced traffic.....                             | 66 |

| Figure 31-1 | Mean access delay vs node index in case 4 of unbalanced traffic.....                                 | 66 |

| Figure 31-2 | Mean end-to-end delay vs node index in case 4 of unbalanced traffic.....                             | 67 |

| Figure 32-1 | Mean access delay vs node index in case 5 of unbalanced traffic.....                                 | 69 |

| Figure 32-2 | Mean end-to-end delay vs node index in case 5 of unbalanced traffic.....                             | 69 |

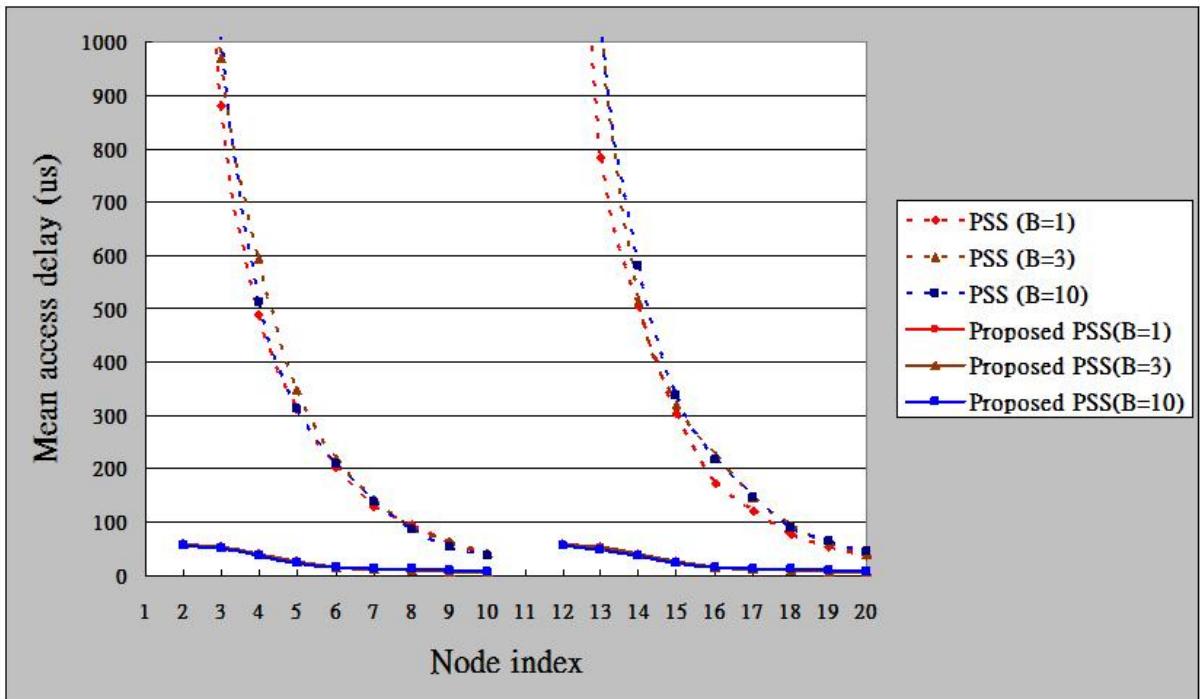

| Figure 33-1 | Mean access delay vs node index in case 1 of unbalanced traffic.....                                 | 71 |

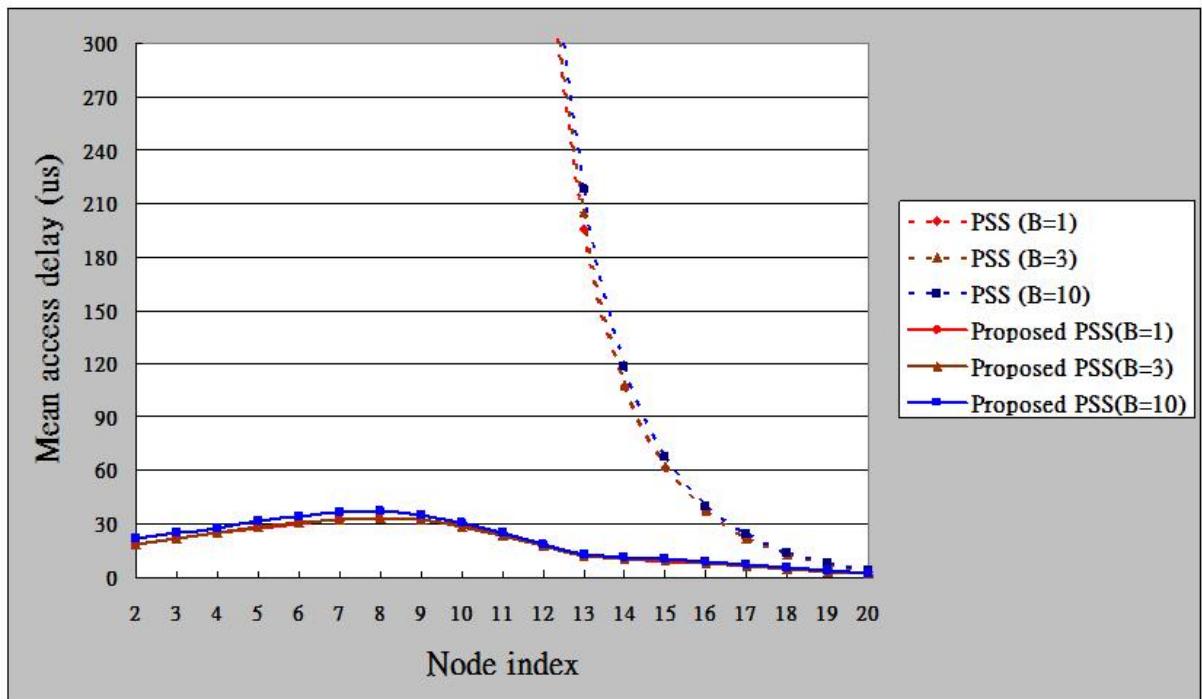

| Figure 33-2 | Mean end-to-end delay vs node index in case 1 of unbalanced traffic.....                             | 71 |

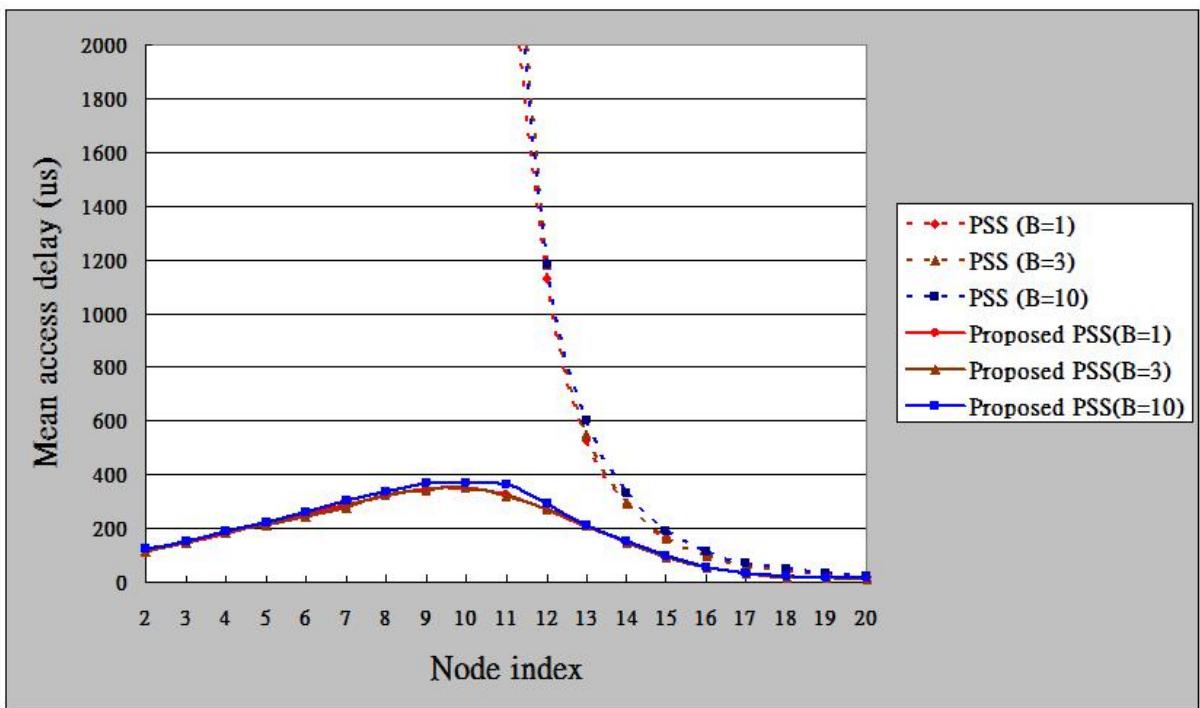

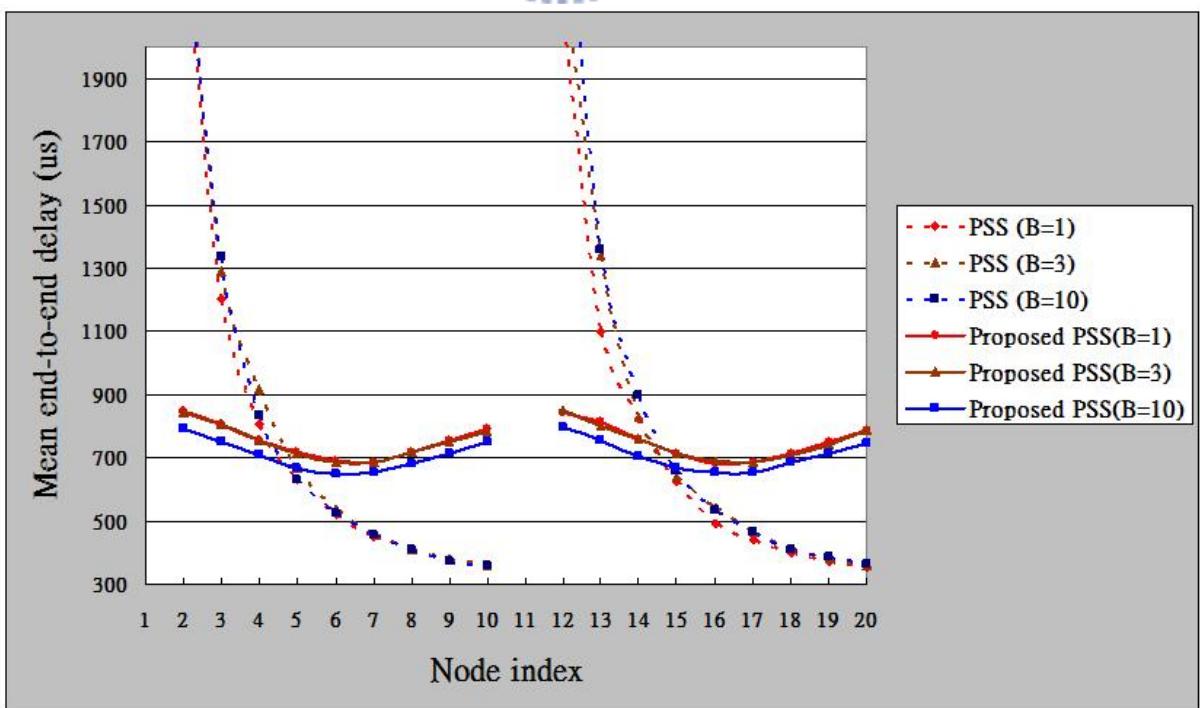

| Figure 34-1 | Mean access delay vs node index in case 2 of unbalanced Traffic.....                                 | 72 |

| Figure 34-2 | Mean end-to-end delay vs node index in case 2 of unbalanced traffic.....                             | 72 |

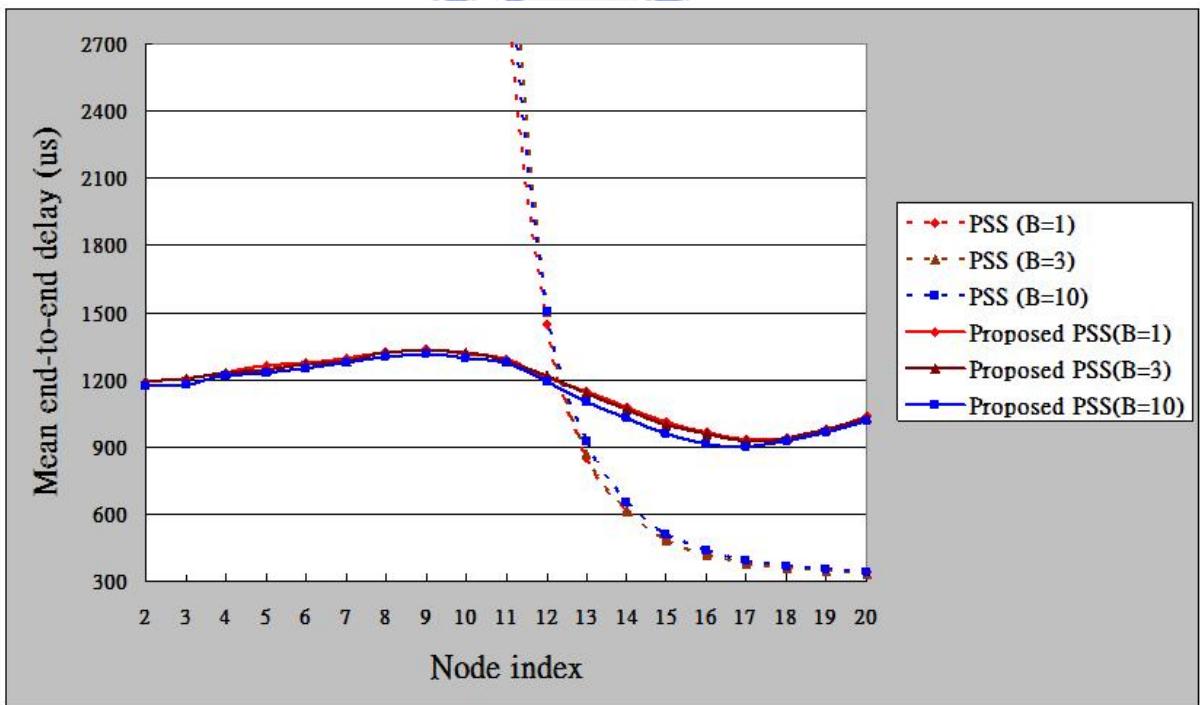

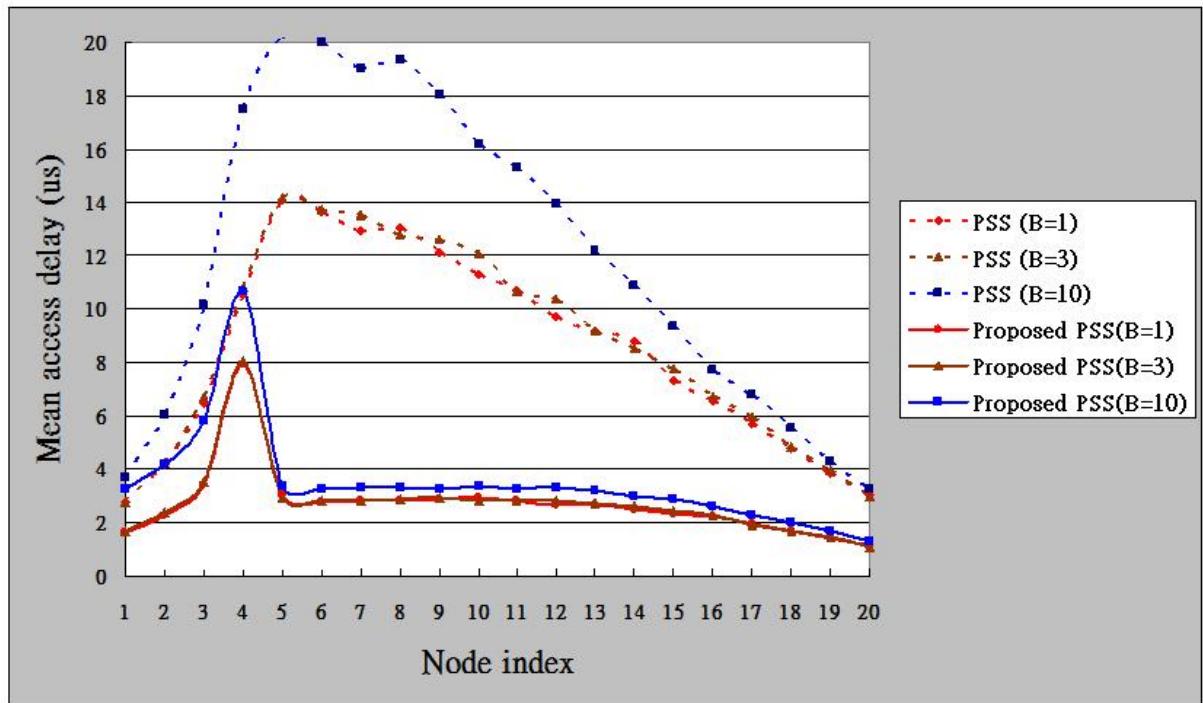

| Figure 35-1 | Mean access delay vs node index in case 3 of unbalanced traffic.....                                 | 74 |

| Figure 35-2 | Mean end-to-end delay vs node index in case 3 of unbalanced traffic.....                             | 74 |

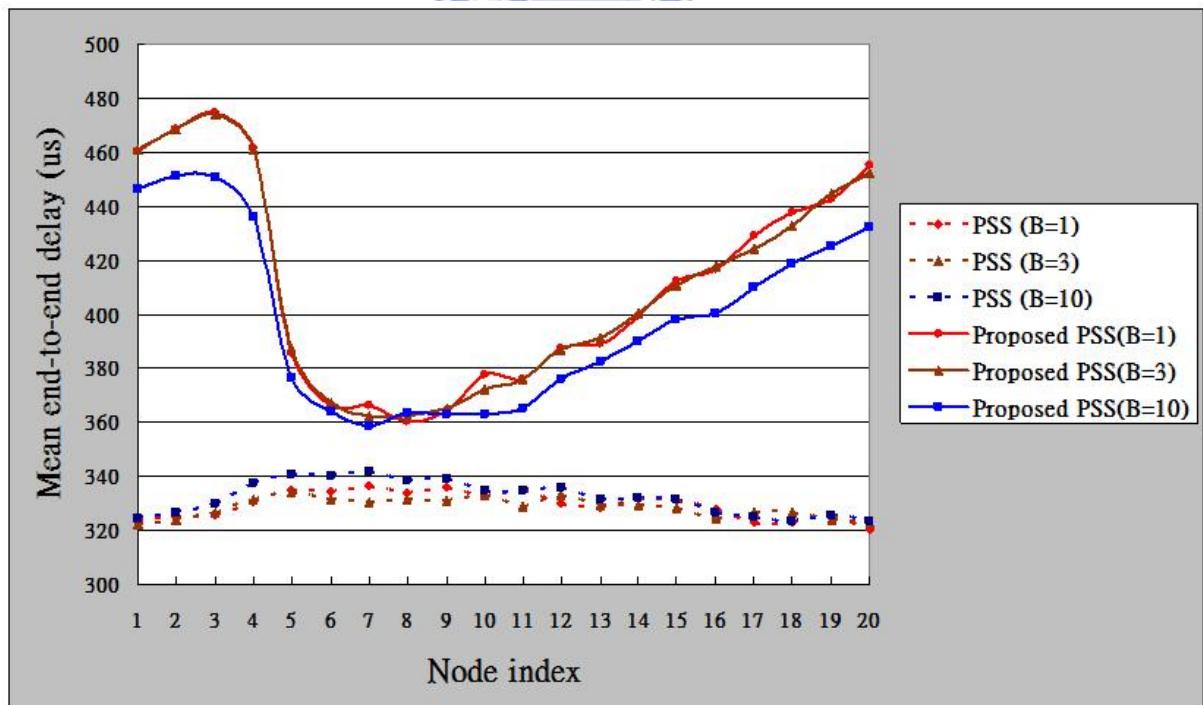

| Figure 36-1 | Mean access delay vs node index in case 4 of unbalanced traffic.....                                 | 76 |

Figure 36-2 Mean end-to-end delay vs node index in case 4 of unbalanced traffic.....

76

## 表 目 錄

|         |                                            |    |

|---------|--------------------------------------------|----|

| Table 1 | Network parameters used in simulation..... | 55 |

| Table 2 | Unbalanced load traffic cases of IWS.....  | 60 |

| Table 3 | Unbalanced load traffic cases of PSS.....  | 70 |

# Chapter 1

## Introduction

近年來隨著網際網路的快速發展，隨之而來的各種整合語音、影像以及數據的各種多媒體運用如 HDTV、VoIP 等使得寬頻網路在頻寬上的要求與日俱增。且這些即時性的多媒體運用必須提供有效率且不間斷的服務品質，故光纖通訊網路技術的發展已經成為解決頻寬不足的最佳選擇以及必經的途徑，而其中 WDM ( Wavelength Division Multiplexing ) [11] optical network 因為採用多波長分工的方式在頻寬上帶來巨大的效益，所以成為近年來研究和發展的重點。然而不管在何種網路架構下，fairness 問題的解決一直是一個很重要的議題，故在這次我們的研究主題中，將提出一個適合運用於都會型單向環狀光纖網路 (Metro Unidirectional WDM Ring Network based on optical packet switching) 上的 MAC protocol 以期能解決在 fairness 上所產生的問題。

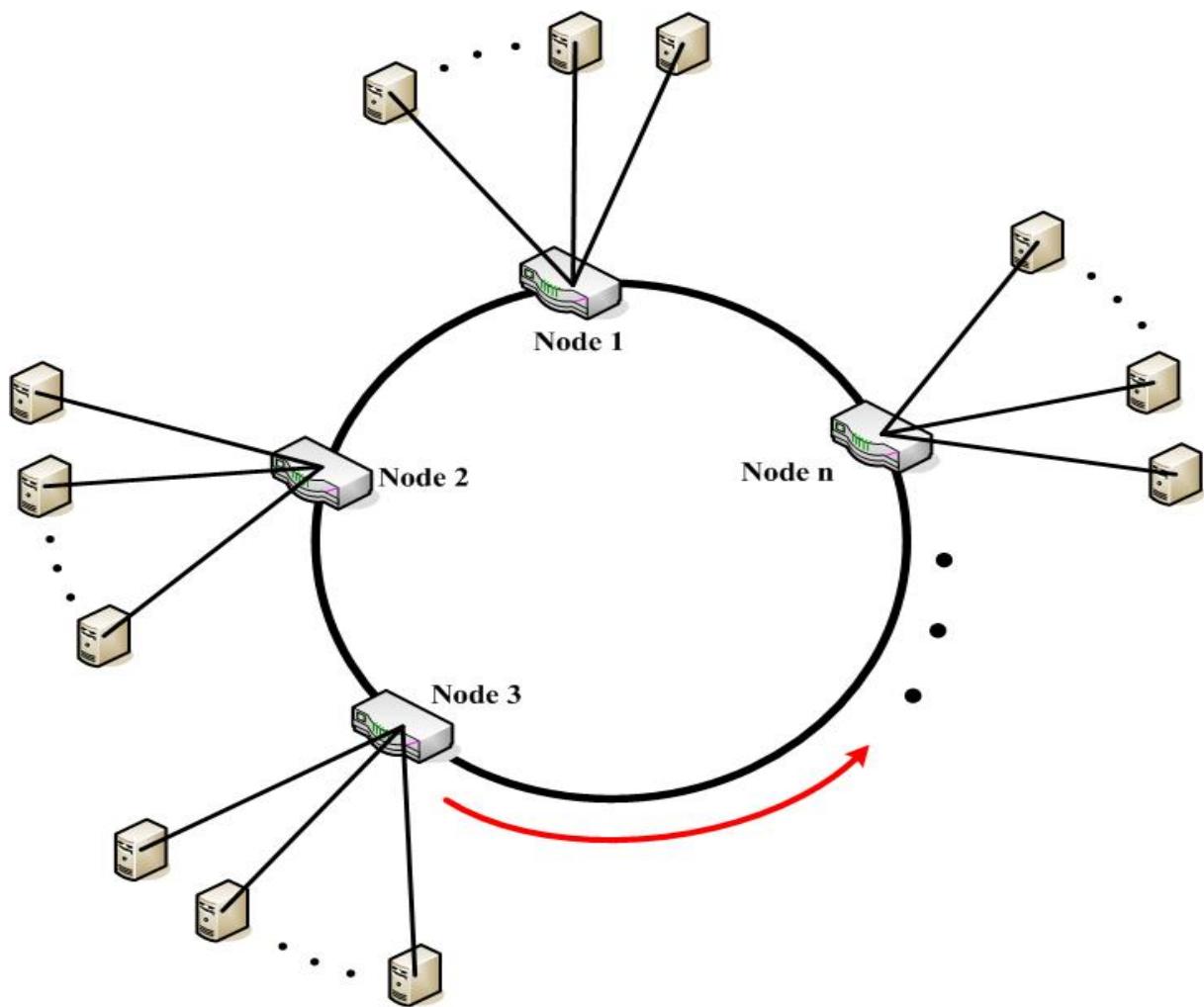

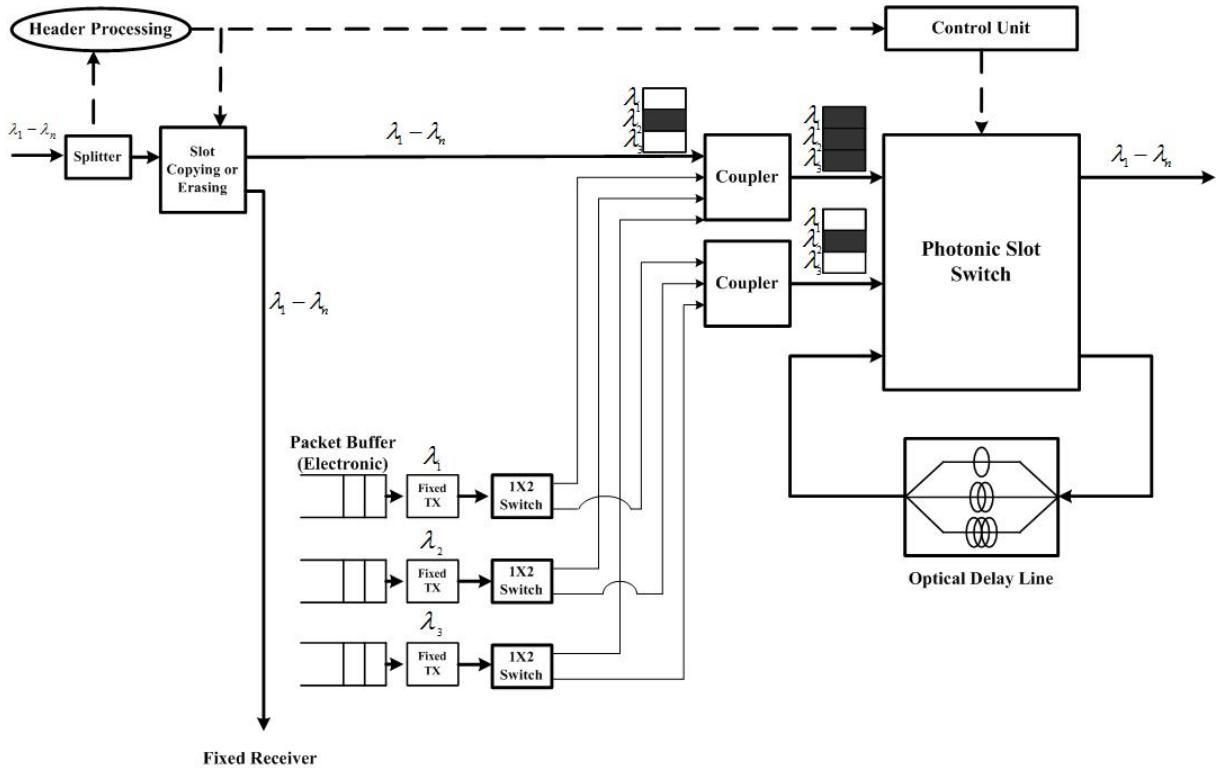

在我們所研究的都會型環狀光纖網路中，骨幹網路中是以單一光纖網路來連結各個 node，故彼此之間訊號的傳遞方式是單向的 (unidirectional)，而每個 node 底下再透過光纖連結數個 sub-nodes。在此架構下每個節點所採用的架構可有兩種方式，分別為 Individual Wavelength Switching (IWS) [5] 以及 Photonic Slot Routing (PSR) [5, 6, 7, 8, 9 and 10]。IWS 因為在每個 node 需經 de-multiplexer 將每個波長分別做交換處理完後

再經 multiplexer 傳送出去，故需要一些 cost 較高的 wavelength sensitive 元件來達成，不過同時因其可以達到 Spatial Reuse 的目的故在頻寬使用上的效率也較好；而 PSR 則是將所有波長視為一個 Photonic Slot，故在每個 node 僅需針對該 Photonic Slot 作交換即可，而這僅需使用較低成本的 wavelength insensitive 元件即可達成；不過 PSR 因為有 slot destination 的 constrain 進而容易造成其在頻寬使用上的效率不高，故我們針對 PSR 修改提出 Photonic Slot Switching (PSS)的方法將 destination 的限制移除。IWS 和 PSS 在頻寬效益和 cost 上各有其優缺點；因此我們將分別針對此兩種架構提出合適的 access protocol 以期能解決關於 Fairness 上的問題。

在環形光纖網路上我們所考慮到關於 Fairness 的問題是若是網路上有些 malicious node 流量突然的遽增，勢必會造成位於其下游的節點因為得不到 access opportunity 而產生 starvation 的現象，造成其在封包傳遞上的延遲加劇。在此我們將採用 insertion ring 的概念並參考運用於 twin bus 上的 ACCI ( Adaptive Cycle Cell Insertion ) access protocol [1] 以及 RPR(Resilient Packet Ring, IEEE 802.17) [2, 3, 4]架構上關於解決 Fairness 的做法，提出一個適合於 all-optical ring network 架構上配合使用的 MAC protocol，此 protocol 具有在 load 低時符合 random access 的原則而不影響到 utilization 的特點，且在 load 高時亦能加以控制以達成動態頻寬分配的功能。我們將在接下來的章節介紹此 protocol 在 IWS 以及 PSS 上詳細的

access procedure，並且最後以模擬的結果驗證在前述 Fairness 問題上的改善。

這篇論文之後的章節編排將如下，首先第二章我們將介紹 ACCI access protocol 以及 RPR fairness algorithm 的詳細作法以及 IWS 和 PSS 的架構，第三章我們將介紹我們所提出的 protocol 運用在 IWS 以及 PSS 的詳細流程，第四章則是模擬環境的介紹以及模擬結果的分析比較。

## Chapter 2

### Background

#### 2.1 The ACCI access protocol

##### 2.1-1 Introduction of ACCI protocol

在這節裡面我們將介紹[1]這篇 paper 裡面針對 twin bus 光纖網路所提供的 access protocol，名為 ACCI (Adaptive Cycle Cell Insertion) protocol。此 protocol 為一種採用全分散式控制機制的 access protocol，且具有 high fairness degree 以及 high throughput 的特點。而 twin bus topology 主要由兩條單一方向的 bus 所構成，在此我們分別稱其為 high 以及 low buses，且信號在其上分別以不同的方向傳遞，而所有的 Network Stations (NS) 可藉由任一 bus 將 cell 往其 destination 傳送。

在此 ACCI protocol 有兩個主要的目標: (i) 在頻寬分配上達到高 fairness 的程度; (ii) 在 twin bus 這個拓樸的限制下盡可能的達到高 throughput; 而在此我們主要關心的是 ACCI protocol 在解決 fairness 問題所採用的方針。因為在 twin bus 這個架構下，它所產生關於 fairness 的問題在於若是 NS 位於越靠近 bus 頭端的位置，則其所獲得的 access opportunities 將會越多，也就是它以頻寬獲得的觀點來看是位於一個較有利的位置；因此若是沒有採用一個合適的 access protocol，那些位於有利位置的 NSs 將會壟斷所有的頻寬。

故在此 ACCI 針對此個問題所提出的方法是於整個網路中採取分散式 buffer 的架構，配合 adaptive access cycles 去公平地分配 access opportunities 且最後再加上 overload control 的機制以避免 buffer 的 overflows。

### 2.1-2 Basic concepts of ACCI protocol

在 ACCI protocol 我們所採用 access 的原則主要是若 bus 沒有偵測到任何 activity 時則以 random access 的方式 access; 反之，若 bus 於 busy 時則採用 controlled access 的方式，即利用我們前面所提到的 access cycles。

每個 access cycles 將會確保每個 NS 一定有一次 access 的機會，且 access cycles 長度的增減則是全分散式的方式，即每個 access cycle 的長度是可變的，將視其所經過 NSs 的 traffic 流量大小而定，且為了達成此功能我們必須在每個 NS-bus interface 加入 Forwarding Buffer (F-Buff); 接下來我們將利用一個 twin bus 且具有 N 個 network stations 的架構來說明。(Figure 1)

在此架構下我們假設所有的 cell 均具有相同的長度，且若是 NS 有 traffic 需要傳送時我們稱其為 active 且採用 1-limited service discipline。故我們知道位於 bus 最上游時，access cycle 只由一個 cell 所組成而該 cell 可為 empty 或 busy; 而該 access cycle 的長度會隨著經過整個網路而有所變

動，例如網路只有一個 NS 為 active 時，則該 access cycle 長度將維持不變，但是若有超過一個以上的 NS 為 active 時，則該 access cycle 的長度將會有所增加。

且每個 NS 可以藉由 incoming empty cells 將其 data 作 insertion，故我們可以將此 insertion 分為兩類: (i) 增加該 access cycle 的長度 (ii)創造一個新的 access cycle; 故我們可以得知在此架構下一個 access cycle 的最大長度為  $N-1$  個 cells 且將會發生在網路的最下游，且一個 access cycle 長度的增加是利用存放 incoming cells 於 F-Buff 中，且當 insertion 結束後存放於 F-Buff 內的 cells 即可 forward; 除此之外，根據我們所採用 cell removal 機制的不同，一個 access cycle 的長度亦可以減少。

因此我們可以得知當在 load 低時，因為網路上具有很多 empty cells，故 access cycles 的長度均不會太長，所以 NS 一旦有 data 需傳送時可以馬

上 access, 類似 random access 的行為；反之，當 load 高時，因為 access cycles 的長度亦隨之增長，此時 access 的行為則像是一個週期性 polling 的機制，即在每個 access cycle 內每個 NS 均有一次 access 的機會。

除此之外，若是 incoming cell 不為 empty 則 insertion 的動作將會使得 F-Buff 內存放的 cells 增加；反之，除非收到 empty cell 且沒有 insertion 的執行，F-Buff 內存放的 cells 才可被傳送出去。故我們需要一個 overload control 的機制來避免 F-Buff 的 overflow 導致 cells 的遺失。在此我們所採用的方法是基於 request of empty cells 的原則，亦即若有一個 NS 發現它的 F-Buff 內 cells 數目超過某個 threshold 值時，則該 NS 會透過另一條 bus 向其上游的 NS 發出 request，而收到該 request 的 NS 則需送出 empty cell 以滿足下游 NS 的需求。且此發送出去的 empty cell 不但可使下游 NS 降低其 F-Buff 佔滿的程度，同時對於那些造成網路壅塞的 NS 亦有抑制其流量的功能。

### 2.1-3 Cell format of ACCI protocol

我們可將整個 channel capacity 視為一連串固定長度的 cells 所組成，而每個 cell 所延續的時間我們稱其為一個 time-slot，故在介紹 ACCI protocol 詳細的 access procedure 之前，我們須先簡介 cell 的 format。ACCI cell 的 format 如 Figure. 2 所示，每個 cell 是由一個 Information Field (IF)

以及一個 Control Word (CW) 所組成，且 CW 具 4 個 bits，其中一個 bit 備用，接下來我們將會介紹 b1, b2 以及 b3 的用途。

Fig. 2: Cell format of ACCI protocol

首先 b1 為 Busy (BSY)，若其為 0 表示該 cell 為 empty；反之，若有 NS 要將 data 填入該 empty cell 時則需將 b1 改為 1。而 b2 在此所表示的意義是 Access Cycle Beginning (ACB)，當 b2 為 1 時表示該 cell 為一個 access cycle 的第一個 cell，且若為 0 時則表示該 cell 位於 access cycle 之內。b2 這個 bit 在 ACCI protocol 內扮演一個很重要的角色，因為若當一個 active NS 收到一個具 b2 為 1 之 cell 時，則此時 NS 可將其 data insert 上去形成一個新的 cell 且該 cell 之 b2 為 1，同時亦把 incoming cell 儲存在 F-Buff 內且必須將其 b2 修改為 0，這就是我們之前所提到當 heavy load 時所採用的 controlled access 方法。最後，b3 (Empty Cell Request)的用途則是用於 overload control，即當某個 NS 發現其 F-Buff 已經超過某個 threshold 時，

則該 NS 會在另一方向的 bus 發送一個具 b3 為 1 之 cell，亦即向上游的 NS 發出 empty cell 的請求；而上游的 NS 一旦收到該 cell 後，需將 b3 reset 且依照請求送出一個 empty cell 以避免下游 NS 的 overflow。

#### 2.1-4 Access procedure of ACCI protocol

在介紹 ACCI protocol 詳細的 access procedure 之前，我們先對 NS-bus interface 的架構作個簡介。[\(Figure. 3\)](#)

首先 Receiving Unit (RU) 會將 incoming cell 的 CWs 和 IFs 分開，其中 CWs 會交由 Protocol Handler Unit (PHU) 去呼叫 Control Unit (CU) 處理所

要進行的 access 動作以及針對 CWs 作必要的修改。且在此除了之前所提到的 F-Buff 用來儲存 incoming cells 之外，Transmitting Buffer (T-Buff) 則是

用來暫存 NSs 自己所產生的 traffic，且這兩個 buffer 如何根據 access

protocol 去進行適當的控制都由 CU 所負責，詳細的 access procedure 將於

之後作討論，且最後 Transmitting Unit (TU) 則負責把處理完的 cells 傳送出

去。

Fig. 3: NS-bus interface of ACCI protocol

接下來我們將針對 ACCI protocol 的 access procedure 作探討，且我們將分為以下的 case 作討論：

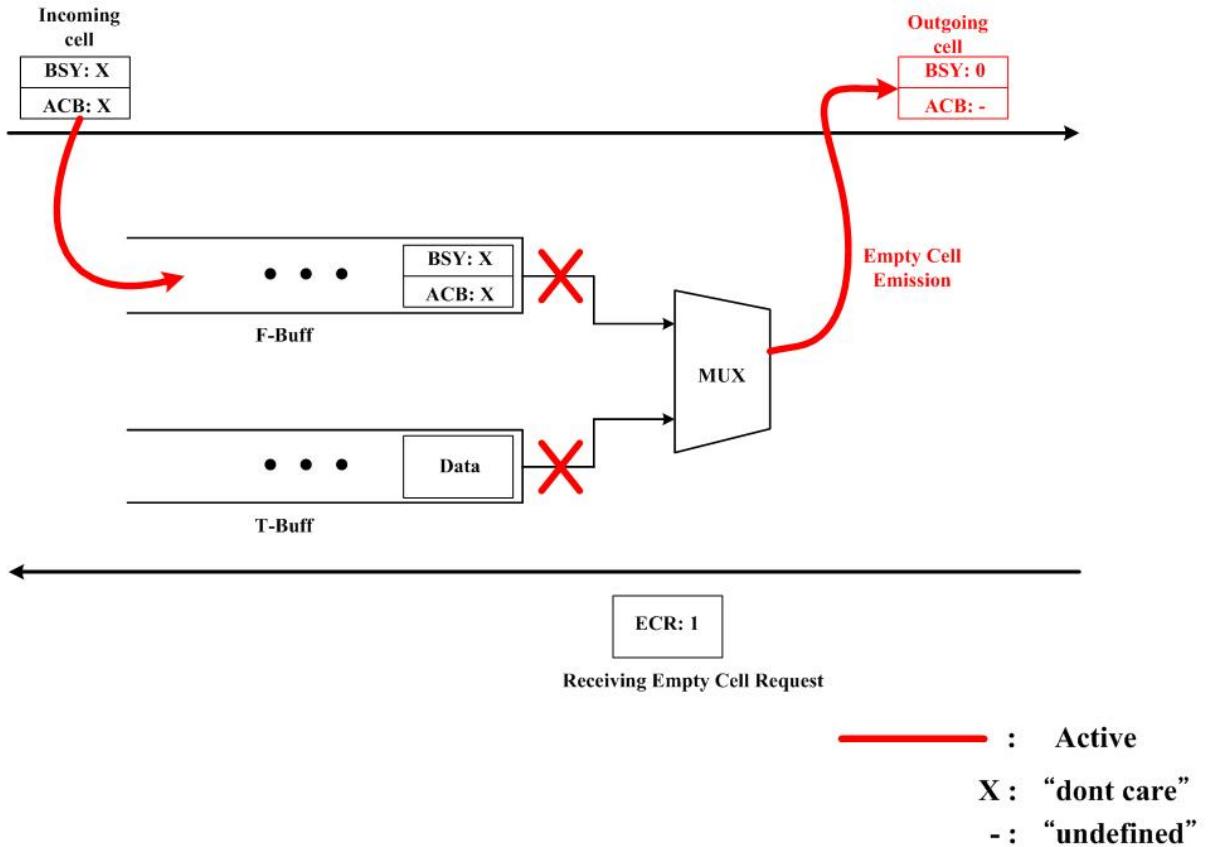

- (i) 當收到 Empty Cell Request 時，則將此視為最高優先權，不管 T-Buff 內有無 data 需傳送且無論 incoming cell 或是儲存於 F-Buff 內的 cell 為何，均必須發送出去一個 empty cell 以避免下游 NSs overflow 導致 cells 的遺失，且若 incoming cell 不為 empty 均先儲存於 F-Buff 內。(Figure 4.1)

Fig. 4-1: Transmitting step of case (i)

以下 case (ii)-(v) 將討論若 channel 為 busy (incoming cell 不為 empty) 或 F-Buff 內有 cells 等待傳送且假設 T-Buff 內均有 data 須傳送，且均無收到 Empty Cell Request，T-Buff 內 data 如何 access 之 rule：

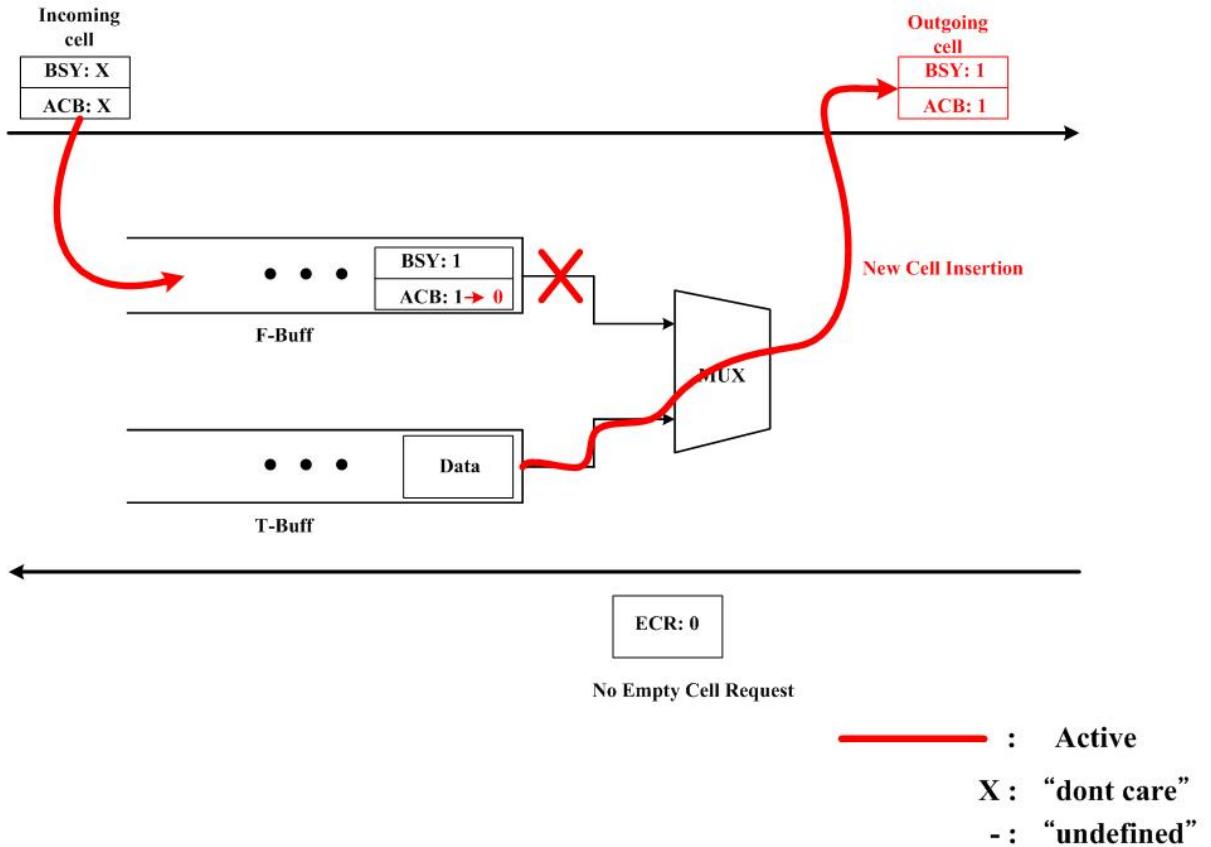

(ii) 若 F-Buff 內有 cells 在等待傳送時，且 F-Buff 內的第一個 cell 其 ACB bit 為 1 時 (表示為 access cycle beginning)，則位於 T-Buff 內的 data 可以 insertion 的方式作傳送 (產生一個具 ACB 為 1 之新的 cell)，且同時需將原先 F-Buff 第一個之 cell 之 ACB bit 改為 0，且若 incoming cell 不為 empty 均先儲存於 F-Buff 內。[\(Figure 4.2\)](#)

Fig. 4-2: Transmitting step of case (ii)

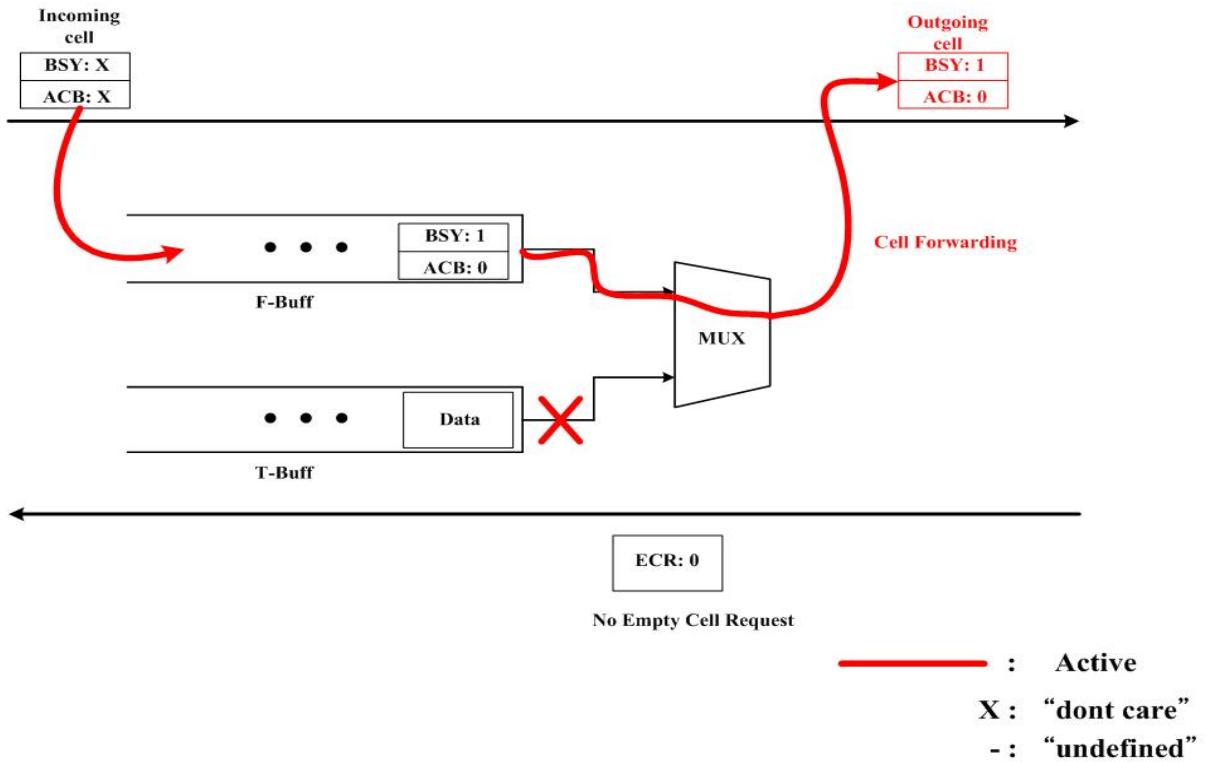

(iii) 若 F-Buff 內有 cells 在等待傳送，但 F-Buff 內的第一個 cell 其 ACB bit 為 0，則位於 T-Buff 內的 data 不可 insertion，故 F-Buff 內的 cell 須 forwarding，且若 incoming cell 不為 empty 均先儲存於 F-Buff 內。(Figure 4.3)

(iv) 若 F-Buff 內沒有 cells 等待傳送，且 incoming cell 不為 empty 且 ACB bit 為 1，則 T-Buff 內之 data 可 insertion，且需把 incoming cell 之 ACB 改為 0 並儲存於 F-Buff 內。(Figure 4.4)

Fig. 4-3: Transmitting step of case (iii)

Fig. 4-4: Transmitting step of case (iv)

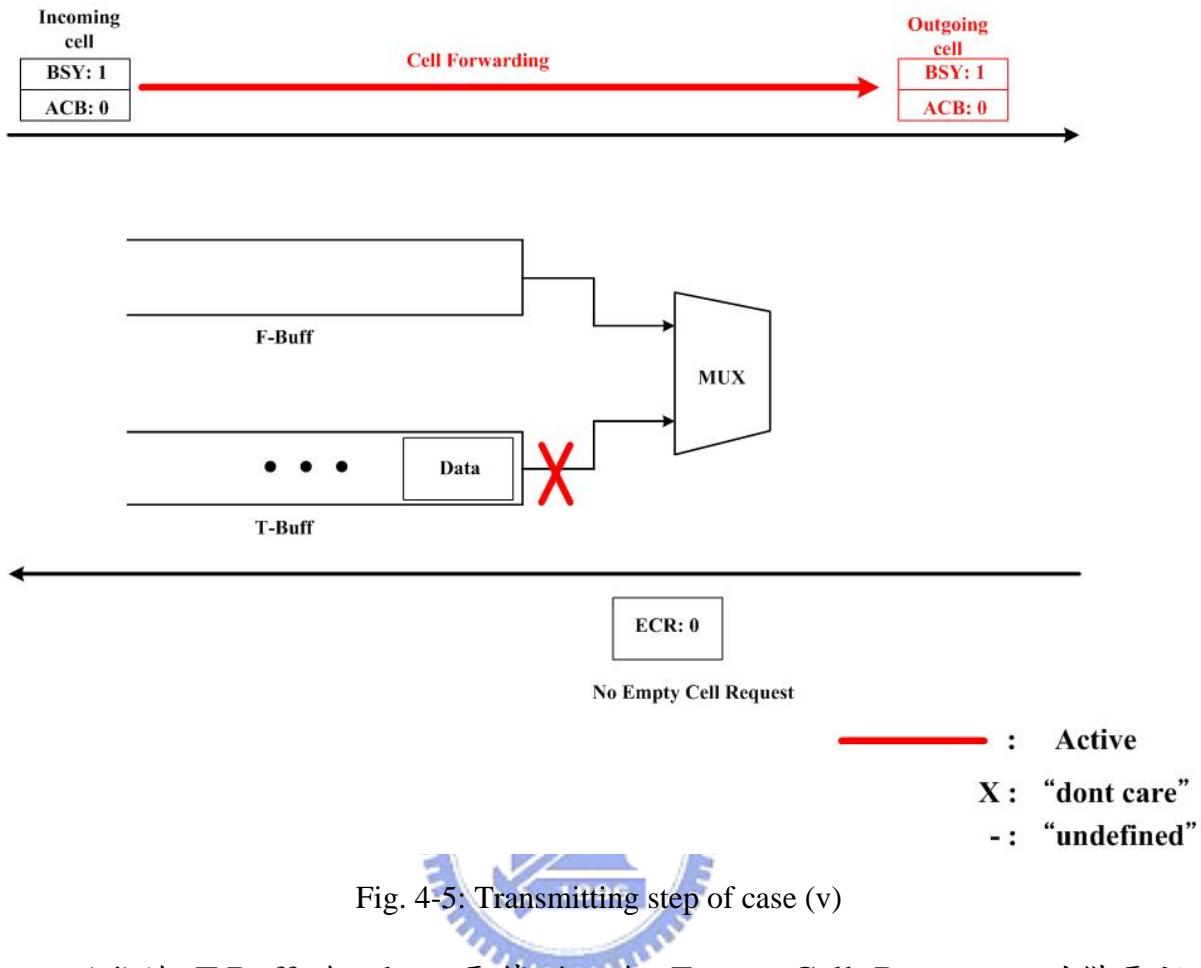

(v) 若 F-Buff 內沒有 cells 等待傳送, incoming cells 不為 empty 但 ASB bit 為 0, 則 T-Buff 內之 data 不可作 insertion, 故僅需將 incoming cell

forwarding。(Figure 4.5)

Fig. 4-5: Transmitting step of case (v)

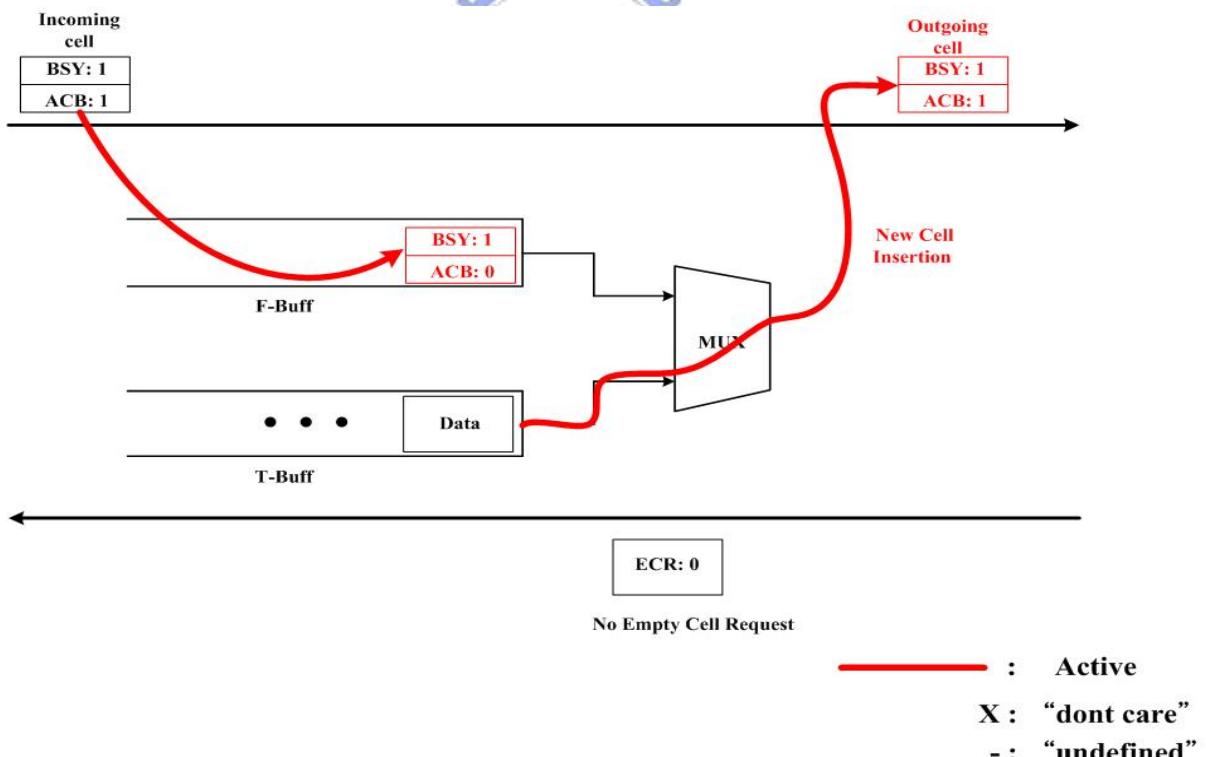

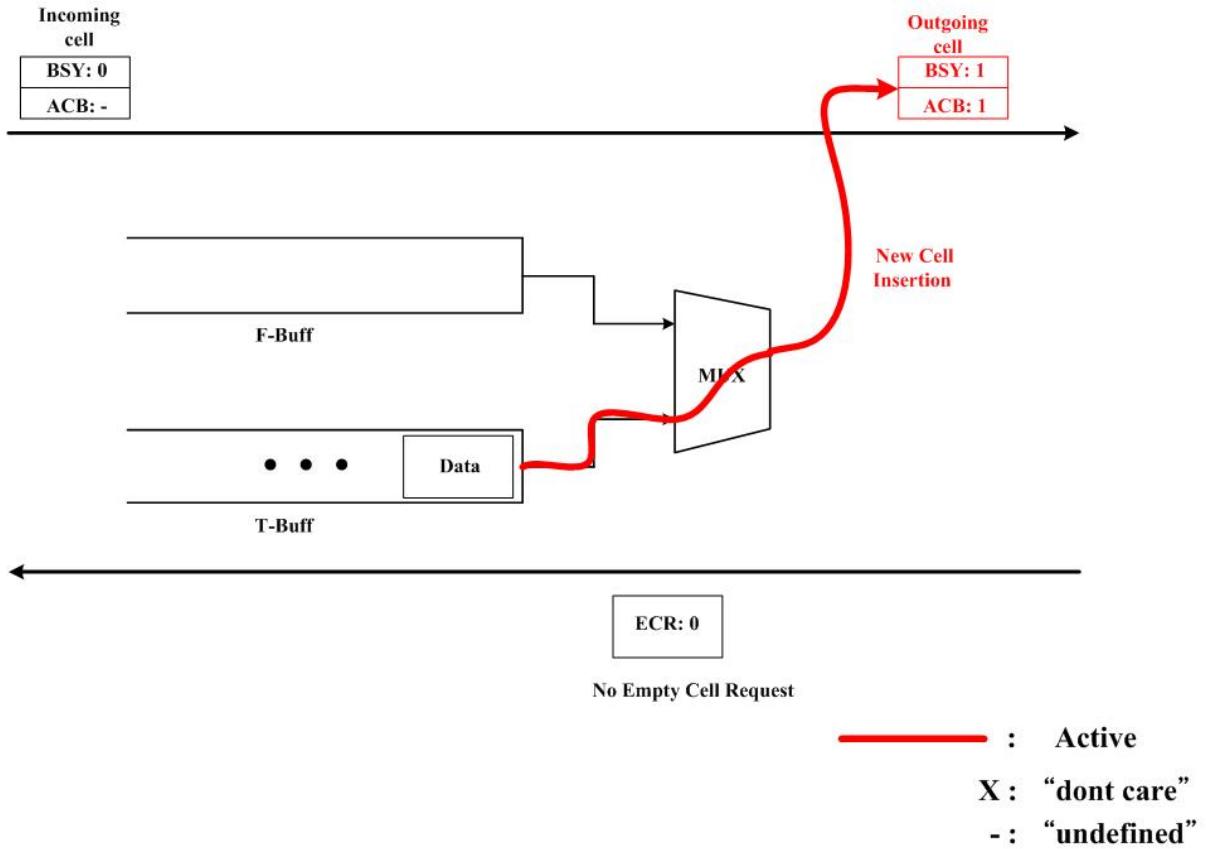

(vi)若 T-Buff 無 data 需傳送且無 Empty Cell Request，則僅需視 incoming cell 及 F-Buff 內的狀況將 cell 作適當的 Forwarding 即可；反之，若 T-Buff 內有 data 需傳送且無 Empty Cell Request，incoming cell 為 empty (channel 為 IDLE)且 F-Buff 亦無 cells 等待傳送，則 T-Buff 內之 data 可 insertion 形成一個新的 cell 且 ACB bit 為 1。(Figure 4.6)

Fig. 4-6: Transmitting step of case (vi)

## 2.1-5 Overload control of ACCI protocol

ACCI protocol 的 overload control 主要決定於每個 NS 其 F-Buff 內儲存的 cells 是否有超過某個 threshold 值，若是大於或等於該 threshold 值，我們稱該 NS-bus interface 此時在 Alarm Mode，反之，則稱其為 Normal Mode。

當一個 NS 處於 Alarm Mode 時，則其必須不停的於相反方向的 bus 上往其上游的 NSs 送出 ECR (Empty Cell Request)直到其 F-Buff 內的 cells 數目小於該 threshold 值，且當恢復成 Normal Mode 時，送出 ECR 的動作

必須立即停止。

故如何決定該 threshold 值是我們所需關心的，在此我們假設某個 NS 與其上游最靠近之 NS 的 round trip delay 為  $P$  個 time-slots，且 F-Buff 之 Size 為  $S$  個 cells；故若一個處於 Alarm Mode 的 NS，其發送出去 ECR 直到它真正收到 empty cell 的時間剛好會是  $P$  個 time-slots，所以我們可以很容易瞭解到該 threshold 值一定需小於等於  $S-P$ ，如此才可避免 overflows 發生而導致 Cells 的遺失。

在此我們所介紹的 ACCI protocol 主要是針對 twin bus 架構所提出，且它在 F-Buff 上是以電的媒介作儲存；而我們這篇論文將針對此 protocol 的想法去作修改，使其能運用在都會型單一方向環狀網路且達成全光 (all-optical) 的目的，亦即 F-Buff 在此使用電的 buffer 而之後我們所提出的 protocol 將用光的 Buffer 來替代，且最後我們亦會以 simulation 的結果來驗證，這將會於之後的章節有詳細的說明。

## 2.2 The RPR Fairness Algorithm

Resilient Packet Ring (RPR, IEEE 802.17)[2, 3, 4]是一個由 IEEE 802.17 RPR 工作小組所制定的 ring-based network protocol。RPR 是一種雙向環狀光纖網路，故就算其中一條 link failure，frame 仍可由另一條 link 抵達其 destination，這也是為何我們稱其為 Resilient 的原因；且 RPR 具有 Spatial Reuse[2]的特性，也就是若 station 收到一個 destination 為自己的 frame 時，則該 station 會將 frame 移除而不是只複製該 frame 的內容，故多出來的頻寬可以讓其他 stations 繼續利用，因此不同的資料可以同時在網路上的不同區域傳送，且傳送封包時會決定不同服務等級封包的傳送順序。

RPR 將 traffic 分成三種等級，首先 class A 須具有 low-latency 以及 low-jitter，class B 則須具可預料的 latency 以及 jitter 而 class C 則採 best effort 的方式傳送，故對其的 latency 以及 jitter 並無任何保證。而其中 class A 的 traffic 還可分為 A0 以及 A1，class B 則可分為 B-CIR (committed information rate) 及 B-EIR (excess information rate)，最後 class C 以及 B-EIR 則為 fairness eligible (FE)，這些 FE traffic 將由我們之後所介紹的 fairness algorithm 所控制；且其中針對 A0, A1 以及 B-CIR 所需的頻寬必須預先分配，且我們稱保留給 A0 的頻寬為 reserved (即該頻寬即使未被使用亦不可給其他 class 的 traffic 使用) 而保留給 A1 以及 B-CIR 的頻寬則為 reclaimable

(若該頻寬未被使用可用來傳送 FE 的 traffic)。

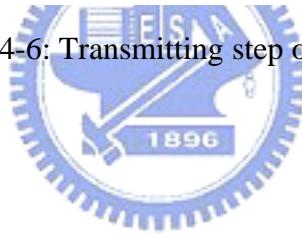

根據以上 traffic priority 的介紹，我們可以將每個 RPR station 以一個 dual-transit-queue station 架構表示[2]。(Figure 5)

其中 PTQ (primary transit queue)用來存放 high-priority transit frames (class A)而 STQ (secondary transit queue)則存放 class B 以及 C 的 frames。且由 PTQ 出去的 traffic 須具有最高的 priority 以確保 class A 的 traffic 在 delay 上的需求，而其餘 queue 的 priority 如圖小圓圈裡面的數字所示。

接下來我們將針對 RPR 在處理 fairness 問題上所提出的演算法作介紹；RPR Fairness Algorithm 主要針對 buffer insertion ring 的概念去作修改，在 buffer insertion ring 裡每個 station 會具有一個 buffer 來當作 transit queue，且每個 station access 的方式根據兩個基本的原則，即若 station 有 data 要傳送時需等到 transit queue 為 empty 時才可傳送且若一個 transiting frame

在 station 正在傳送 data 時抵達，則該 transiting frame 需先暫存於 transit queue。(Figure 6)

Fig. 6: Concepts of Buffer Insertion Ring

然而此種架構卻很容易使得位於下游的 stations 因為上游的 traffic 太多而導致 starvation 的現象產生，故 RPR fairness algorithm 的目的是將那些 unallocated 以及 unused reclaimable 頻寬作公平的分配，且此頻寬將用於傳送 FE traffic。

當一個 station 的 transmit link 頻寬用完時，則我們稱該 station 以及該 link 為 congested，且此時 RPR fairness algorithm 將會作用。我們可以很容易瞭解到 congestion 發生的原因是由於該 station 以及上游最靠近的 stations 所造成的，故在此 RPR fairness algorithm 的作法是由該 congested station

往上游傳送 fairness message 以解決其 congestion，如 Figure 7 所示[2]。

Fig. 7: When a station becomes congested: Sends a fairness message upstream

且該 congested station 需根據目前網路的狀況計算出一個 fair rate，此 fair rate 將透過前述所提到的 fairness message 往上游傳遞給所有造成此 congestion 發生的 stations，而所有收到此 fair rate 的 stations 需根據該 fair rate 去調整其 FE traffic 的流量；我們稱該 congested station 以及所有收到該 fairness message 的 stations 構成一個 congestion domain。

Fig. 8: Congestion domain of RPR fairness algorithm

如 Figure 8 所示[3]，node 0, 1, 2, 3 所送之 traffic 均會經過 node 3 與 4 中間之 link 造成該 link congested，故此時我們稱 node 3 為 congestion domain 之 head，且其必須負責計算出目前所需的 fair rate 為何，並且將此 fair rate 往上游傳遞給 congestion domain 裡面的每一個 station 得知；而造成此 congestion 最上游之 station 我們則稱其為 tail，它則必須把從 head 傳遞過來的 fairness message 移除。

且 RPR fairness algorithm 針對此 fair rate 的傳遞亦有兩種操作模式，分別為 conservative mode 以及 aggressive mode[2]；當操作於 conservative mode 時，congestion domain 裡的 head station 必須等到確定所有 domain 裡的

stations 都已經將其傳送速率調整為 fair rate 時才可以再根據目前網路的狀況再傳送出一個新的 fair rate。而若是操作於 aggressive mode 時，該 head station 則會以一個固定的时间發送出一個新的 fair rate，直到確定該 congestion 的現象消失為止。

在此我們所介紹的 RPR fairness algorithm 是應用於雙向環狀光纖網路 上，且在每個 station 裡需要加上一些電的 buffer 來處理 transiting traffic；如此一來在 traffic 抵達至 destination 之前在每個 station 都需經過光電的轉換，如此一來在傳輸速度上就會產生一些瓶頸而受到限制；此外每個 station 還必須加上能夠計算出 fair rate 的功能，如此在 cost 上所需的成本又更高了。因此在下一章我們將會介紹我們所提出來適合於單一環狀光纖網路且全光的 access protocol，即在我們所提出的 protocol 裡 traffic 由 source 傳遞至 destination 的過程中並不需要多餘的光電轉換進而可以達到全光 (all-optical) 的目的，且在我們所提出的架構裡每個 station 僅需對每個 incoming packet 作一些判斷後作交換即可，而不需由複雜的 fair rate estimate 來達到 fairness 的目的，故在每個 station 的複雜度都可以有大幅度的降低。

## 2.3 Individual Wavelength Switching and Photonic Slot Switching

在我們所研究的環狀光纖網路中，每個 node 的架構依 cost 的考量可採用 IWS[5] (Individual Wavelength Switching) node 以及 PSS (Photonic Slot Switching) node 兩者架構。

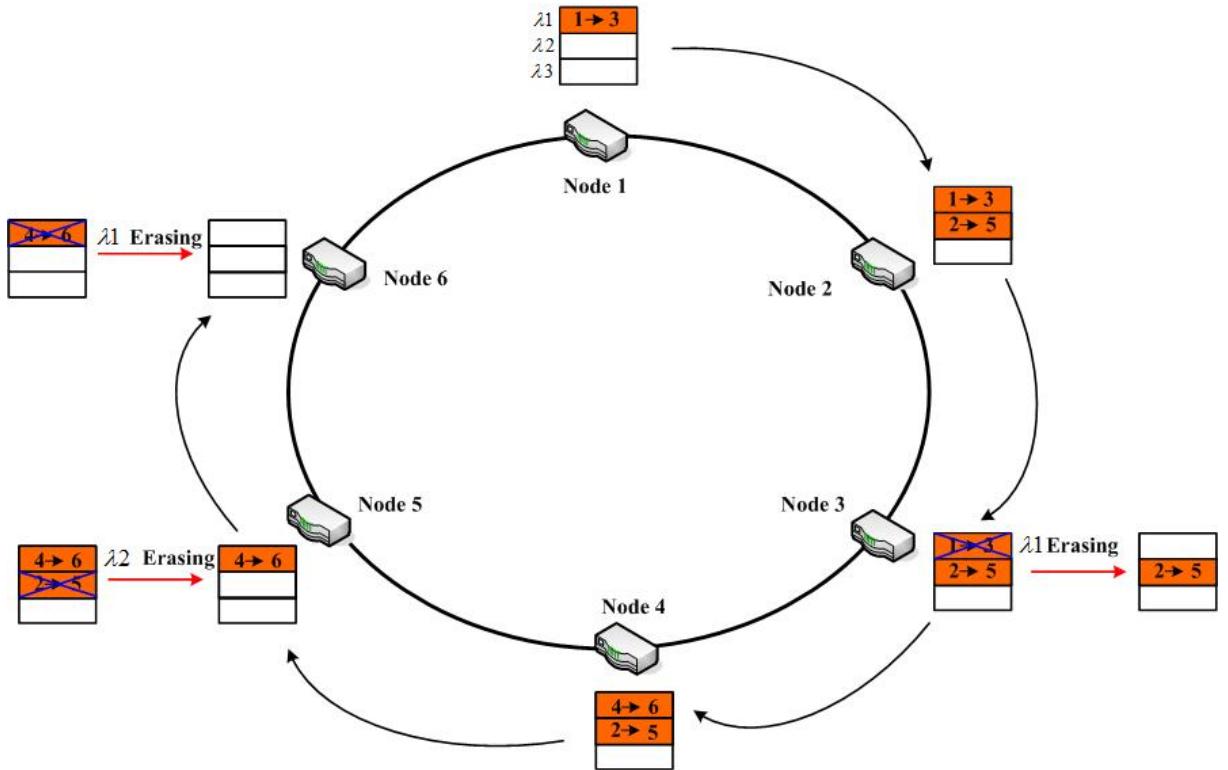

簡單來說，IWS 將每個 wavelength 視為單獨的個體來處理且每個 wavelength 均由固定長度的 packet 所組成且稱一個 packet 的時間長度為一個 time-slot，故在每個 node 均需有 de-multiplexing 及 multiplexing 的動作，且每個 wavelength 需個別去作 switch 且分別處理每個 wavelength 上所載 packet 的 header，如此一來因為需使用到 wavelength-sensitive 的元件來處理故其在 cost 上的成本會較高；不過由於 IWS 只要該 wavelength 所載的 packet 確實被接收後便可將該 wavelength 清空再使用，故可達到 Spatial Reuse 的目的進而使得頻寬的使用率較好。如 [Figure 9](#) 所示，node 1 使用  $\lambda_1$  將 packet 傳至 node 4，且 node 2 使用  $\lambda_2$  傳送 packet 至 node 5；而當該 slot 抵達 node 3 時，因為  $\lambda_1$  所載的 packet 已被 node 3 所接收，此時 node 3 便可將該波長清除，故當該 slot 抵達 node 4 時，node 4 便可使用  $\lambda_1$  傳送 packet 至 node 6；同理 node 5 和 6 分別收下傳至自己的 packet 且將對應的波長清除。

Fig. 9: Spatial Reuse of IWS node

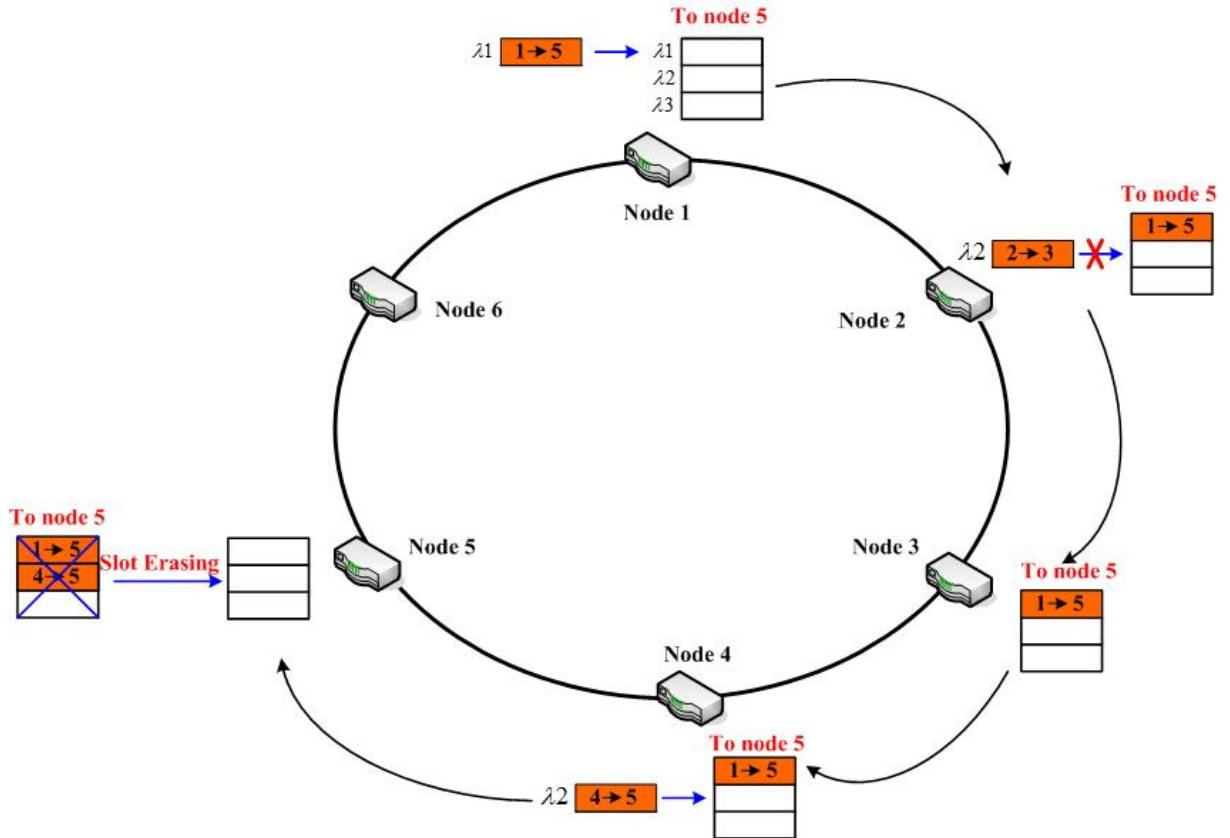

在我們這邊所考慮的 Photonic Slot Switching (PSS)是根據 Photonic Slot Routing (PSR)[5, 6, 7, 8, 9 and 10]的架構去作修改，因此我們先對 PSR 作一個簡介。PSR 是 time-slotted 但 data 以 Photonic Slot 的方式傳送，每個 Photonic Slot 具有固定的長度且由所有可用的波長所組成；且在 Photonic Slot 裡每個波長所載的 packet 之 destination node 均必須相同，故我們可將每個 Photonic Slot 視為單一且不可分割的個體去處理，而在每個 intermediate node 僅需針對該 Photonic Slot 去作交換而不需經由 de-multiplexing 以及 multiplexing 的動作，且亦不需針對每個 packet 的 header 去作處理，故僅需利用 wavelength-insensitive 的元件即可達成，如此一來在 cost 上的成本可以有效降低；然而由於 PSR 在 destination 上的

constraint，會使得在頻寬上的使用率降低。如 Figure 10 所示，node 1 使用  $\lambda_1$  將 packet 傳送至 node 5，且因為此 packet 為該 Photonic Slot 所放入的第一個 packet，故決定此 slot 之 destination node 為 node 5；而當該 slot 抵達 node 3 時，node 3 欲使用  $\lambda_2$  將 packet 傳至 node 3，可是因為與該 slot 之 destination node 不同，故該 packet 無法載上該 slot 而造成頻寬的浪費；當該 slot 抵達 node 4 時，node 4 所產生之 packet 欲傳送之 node 5，故其可以使用  $\lambda_2$  將 packet 載入，最後當該 slot 抵達 node 5 後再由 node 5 作 Slot Erasing 的動作。

Fig. 10: Destination constrain of PSR

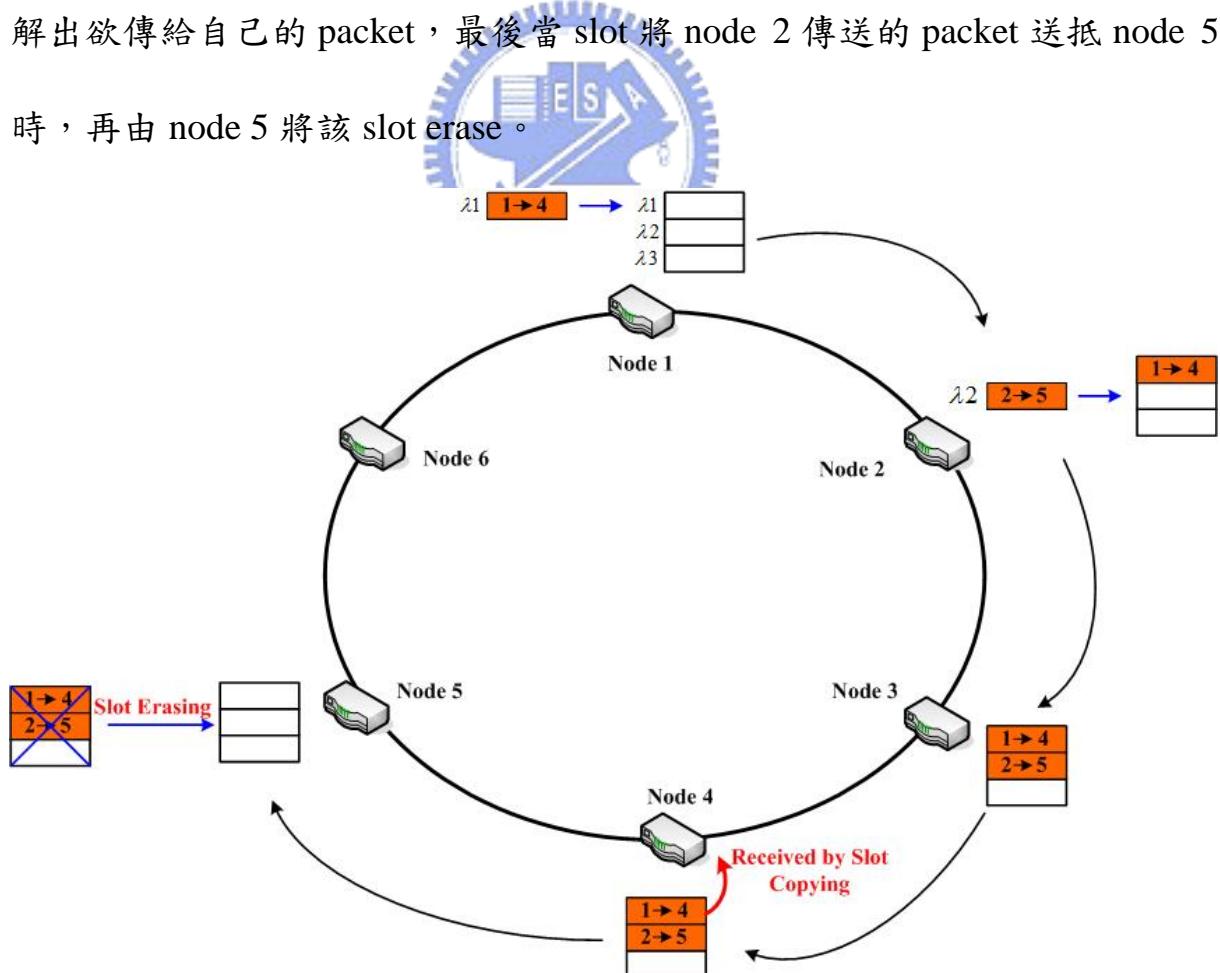

為了提高 PSR 的頻寬使用效率，因此我們在這篇論文所採用的 PSS 是

將 destination 的 constrain 拿掉，亦即當有 packet 需要傳送時，只要確定該 wavelength 仍可使用即可將 packet 載入且途中所經過的 intermediate node 只需利用 slot copying 的功能將該 slot 複製下來再解開自己所需的波長，而當確定該 slot 所有載入的 packet 均已被接受過後，再由最後一個 node 負責作 slot erasing 的動作。如 Figure 11 所示，node 1 將傳送至 node 4 的 packet 以  $\lambda_1$  載入，當該 slot 抵達 node 2 時，因為此時已沒有 destination 的 constrain，故 node 2 可以將其欲傳送至 node 5 的 packet 以  $\lambda_2$  載入該 slot，而當 slot 抵達 node 4 時，便可利用 slot copying 的功能將該 slot 複製下來且 node 4 亦可解出欲傳給自己的 packet，最後當 slot 將 node 2 傳送的 packet 送抵 node 5 時，再由 node 5 將該 slot erase。

Fig. 11: PSS (removal of destination constrain)

整體而言，因為 IWS 具有完全的 Spatial Reuse 功能，故它在頻寬的使用率上較 PSS 來的好，但是在硬體上所需的 cost 也較高；反之，在此我們所提到的 PSS 即使有些波長所載的 packet 已被接收過了，但是因為我們將整個 Photonic Slot 在整個傳輸的過程中視為一個不可分割的個體，故該波長仍需等到整個 slot 被 erase 後多餘的頻寬才可釋放出來，故其在頻寬的使用率上較低，不過卻可以節省在硬體上的成本；因此欲採用何種架構將視效能與成本之間的取捨，而在下一章我們將對此兩種架構分別提出一個合適的 access protocol 以期能解決在網路 load 不平衡下所產生的 fairness 問題。

## Chapter 3

### Proposed Protocol

#### 3.1 Network architecture and format of Photonic Slot

在我們這篇論文中我們所考慮的網路架構為都會型單一環狀光纖網路，而此一網路上主要由  $n$  個 node 所構成，node 與 node 間透過骨幹光纖網路連結形成一個環形的網路，且在此基於都會型網路成本的考量我們所考慮的是單向網路，亦即 node 與 node 間僅可透過一個固定的方向傳遞封包，而每個 node 底下可再透過光纖支援  $k$  個 sub-nodes，如 Figure 12 所示。

Fig. 12: Network architecture

此網路架構下因採用 WDM (Wavelength-division multiplexing)的技術，故於骨幹網路上共有  $w$  個波長可用，且每個 sub-node 配置有一個 fixed-receiver 用來接收特定波長所載之資料，故所有欲送往該 sub-node 之 traffic 就必須使用該特定波長來做傳送。如假設 node 3 底下之 sub-node 1 只能接收  $\lambda_1$  之波長，則若是 node 2 底下之 sub-node 5 欲傳送 data 過去，則必須先將 data 透過光纖往上傳至 node 2，再藉由  $\lambda_1$  往 node 3 傳送，而當該封包抵達 node 3 時，node 3 再藉由檢查該封包之 header 判斷其是要送至底下之 sub-node 1 進而將  $\lambda_1$  解開而往下傳送給 sub-node 1。

且在此為了之後模擬驗證的方便，我們假設環狀網路中可使用的波長數目與每個 node 底下 sub-node 的數目相同，且於每個 node 中針對不同的波長均配置有電的 buffer 以儲存底下 sub-node 所傳上來的 traffic，如該 data 欲使用  $\lambda_1$  傳送，則會先儲存於  $\lambda_1$  所對應的 buffer 內再透過 transmitter 將該 data 以  $\lambda_1$  的波長傳送於骨幹網路上。

而在[9]這篇 paper 裡有對一個 Photonic Slot 的 format 作簡介，如 Figure 13 所示。我們可稱 WDM channels 是由一個個 Photonic Slots 所構成的，每個 wavelength 代表一個 channel 而 Photonic Slot 中每個 wavelength 可以載一個 packet。且 Photonic Slot 中的 slot header 會額外用一個波長去承載，而該 header 會記載一些 information 如哪些波長仍可使用且若是在 PSS 系統中仍可記載該 slot 的 destination; 另外在每個 packet 裡面又有屬於該 packet 的

sub-header 用來記載屬於該 packet 的 information。最後為了避免 Photonic Slot 可能產生的 dilation 現象，於每個 slot 後面會加上一段 padding。

| $\lambda_0$ | Slot header |            |      | padding |

|-------------|-------------|------------|------|---------|

| $\lambda_1$ | used        | Sub-header | data |         |

| $\lambda_2$ | used        | Sub-header | data |         |

| $\lambda_3$ | used        | Sub-header | data |         |

Fig. 13: Format of Photonic Slot

## 3.2 Proposed protocol for IWS

### 3.2-1 Basic concepts

在此我們提出這個 protocol 的目的是希望能解決當網路 load 不平衡時，可能會造成某些 node 因為拿不到 access opportunities 所衍生的 fairness 問題。因此針對這個成因我們有了 insertion credit 的想法，亦即我們希望當某個 node 因為其上游 node 不正常過量的 traffic 而導致該 node 產生 starvation 現象時，仍可以透過 insertion credit 這個機制獲得 access 的機會。

且因為此篇論文我們所欲應用的網路架構是 all-optical 的以達到高速網路的目的，故不同於之前 ACCI protocol 使用 F-Buff 來暫存 incoming cell，我們將使用 optical delay line[12]的元件去達到 optical buffer 的目的，且其特性也和電的 buffer 不同，故我們也須針對此特性發展出一個合適的演算法。

而在 IWS 系統中，因為在每個 node 會經由 de-multiplexing 的動作將每個波長分別解開處理後最後再 multiplexing 傳送出去。故在此我們所提出的想法是於每個波長上的 packet 引入之前 ACCI protocol 所提出的 access cycle 概念，讓每個波長上均有 access cycles 來控制 node access 的行為，即每個 access cycle 均有一次 access opportunity；當 channel 為 idle 時 node 傳送 packet 可 random access，而若 channel 為 busy 時則其可以藉由判斷目前 incoming packet 是否為 access cycle 之 head 來作 packet insertion

的動作並且將 incoming packet 暫存於 optical buffer 內。

值得注意的是與 ACCI protocol 不同的是此處我們運用 optical buffer 來扮演 forwarding buffer 的角色因此 packet 進入 optical buffer 內一段時間後就一定必須離開，故我們一律以 incoming packet 而不以 optical buffer 內即將輸出的 packet 來判斷是否可作 packet insertion; 且此時新產生的 packet 因為需要考慮到 optical buffer 只是運用一些 delay 的技巧而無法達到永久儲存的目的，亦即 optical buffer 亦可能有 packet 輸出而參與 outgoing packet 的競爭，故為了避免 packet 的 loss，一旦 optical buffer 內有 packet 需要傳送時我們一律讓該 packet 具有最高優先權傳送；而新產生的 packet 連同 incoming packet 則放入 optical buffer 內。

最後關於在 overload control 的部分，因為在此我們討論的是單一方向的環狀網路，故我們並無法如 ACCI protocol 般可以藉由往上游發送出 Empty Cell Request 來避免其 F-Buff 的 overflow; 所以我們在此的作法是若當 optical buffer 內仍載有 packet 等待輸出且此時收到 incoming packet 為 empty 時，則為了降低 optical buffer 的負載，我們將不對該 empty packet 作 random access 的動作；如此一來當一個 time-slot 時間經過後，optical buffer 將可以輸出一個 packet 進而降低其 buffer 滿載的程度。

而若當 incoming packet 為 cycle head 而需要執行 packet insertion 的動作時，此時若 optical buffer 內亦無足夠的空間存放 incoming packet 以及

insertion packet，則我們就不執行該 packet insertion 的動作以避免 packet 的 loss，詳細的流程我們將於之後作說明。

### 3.2.2 Node architecture and removal mechanism

在此我們的想法是在每個 packet 所處波長的 sub-header 內加上一個 cycle head 的判斷機制，如 Figure 14 所示。

其中 Busy (BSY) bit 代表此波長是否被使用，當 BSY=0 表示 packet 為 empty，反之若有 packet 載入該波長則 BSY 為 1；而若 Cycle Head (CH) 為 1 時，表示該 packet 為該 access cycle 之 head，故當此 packet 經過某個 active node 時，則該 node 可以藉此將其 packet insert 上來，而此 insert 之 packet 取代 incoming packet 成為該 access cycle 之 head，亦即每個新產生之 packet 其 CH 均為 1；而此時被 insert 之 packet 需將其 CH 改為 0 表示其位於此 access cycle 之內。

為了實現我們之前所提到的 access cycle 概念且應用於 all-optical 的環境中，故在每個 IWS node 中我們必須加入 optical delay line 來扮演之前於 ACCI protocol 內 F-Buff 的角色，且利用 Packet Buffer (electronic)來儲存

sub-nodes 傳上來且欲以該波長傳送之 packet。(Figure 15)

Fig. 15: IWS node architecture

如圖所示，當一個波長上所載之 packet 抵達 node 時，可以藉由檢查其 header 來判斷該 packet 是否需存入 optical delay line 內；值得注意的是，當 packet 一旦進入 optical delay line 後經過一定 delay 的時間後它會被輸出，為了避免 packet 的 loss 我們必須讓該 packet 成為 outgoing packet，而此時若是 incoming packet 恰為 cycle head，則我們需將 incoming packet 及由 Packet Buffer 新產生之 packet 放入 optical delay line 內。

至於在 packet removal 的機制方面，因為在此我們於每個 IWS node 均會將所有的波長解開再針對個別波長去作處理，因此當該波長所載的 packet 已確實被接受下來後，則我們可以將該 packet 清空使接下來的 node 可以使

用該波長，詳細的步驟我們已於 2.3 節的 Figure 9 說明。

### 3.2.3 Access procedure of proposed protocol for IWS

之前我們已提到此處我們所提出的 protocol 是將每個波長上所載的 packet 應用 ACCI protocol 裡關於 access cycle 的概念，且因應 optical delay line 的特性，故每個 node 其 access 的行為將完全由 incoming packet 所決定，不同於之前 ACCI protocol 以 F-Buff 內儲存的第一個 cell 所決定，除非 F-Buff 內無儲存 cell 時才由 incoming cell 決定。

為了說明的方便，我們一樣將 access 的行為分為以下的 case 作討論，且以下 case (i) – (iii) 我們均先假設 Packet Buffer 內有 data 等待傳送：

(i) 當 incoming packet 不為 empty 且為 cycle head 時並且假設 optical buffer 內仍有足夠的空間執行 packet 的 insertion，則此時 node 新產生的 packet 可藉由 insertion 放入網路上，而將 incoming packet 放入 optical delay line 內暫存；但這邊值得注意的是，同時間 optical delay line 內亦有可能有 packet 輸出，故為了避免 collision 的發生，我們必須讓該 packet 成為 outgoing packet。而此時由 Packet Buffer 新產生的 packet 連同 incoming packet 均放入 optical delay line 內並將 incoming packet 之 CH bit 改為 0。

在此我們尚須注意此處此兩個 packet 放入 optical delay line 需以避免他們從 optical delay line 輸出時發生 collision 為最大原則，故我們在此採用的

方法是將此兩個 packet 分別放入不同 delay 時間長度的 delay line 內，如此則可以保證 optical delay line 的輸出永遠不會有 packet collision 的情形，如 Figure 16-1 所示。

Fig. 16-1: Transmitting step of case (i) for IWS

反之，若 optical delay line 沒有 packet 輸出時即表示此刻 optical buffer 內為 empty，則此時我們可讓新產生的 packet 直接輸出成為 outgoing packet，且 incoming packet 暫存入 optical buffer 內所需 delay 最少之 delay line 並將其 CH bit 改為 0。(Figure 16-2)

Fig. 16-2: Transmitting step of case (i)-2 for IWS

前述我們所討論的均假設當 incoming packet 為 cycle head 時，optical buffer 仍有足夠的空間來暫存 incoming packet 以及 new inserted packet；反之，由於 optical delay line 的特性此時 optical buffer 內可能只有一個空間可以暫存 packet，故此時我們必須限制 new generated packet 的 insertion，以避免 optical buffer 的 overflow 導致 packet loss。故此時我們僅需將 incoming packet 放到 optical buffer 內而讓 optical buffer 輸出的 packet 成為 outgoing packet 即可(Figure 16-3)

Fig. 16-3: Transmitting step of case (i)-3 for IWS

(ii) 若 incoming packet 不為 empty 且不為 cycle head 時，則此時存於 Packet Buffer 內之 data 不可作 insertion; 而若 optical buffer 有 packet 輸出時，則需讓該 packet 成為 outgoing packet 且將 incoming packet 放入 optical buffer 內適當的位置 (Figure 17-1)。反之，若此時 optical buffer 並無 packet 輸出時，即表示此刻 optical buffer 內並無 packet 暫存，故我們僅需將該 incoming packet 放入 optical buffer 內所需 delay 最少之 optical delay line (Figure 17-2)。

Fig. 17-1: Transmitting step of case (ii)-1 for IWS

Fig. 17-2: Transmitting step of case (ii)-2 for IWS

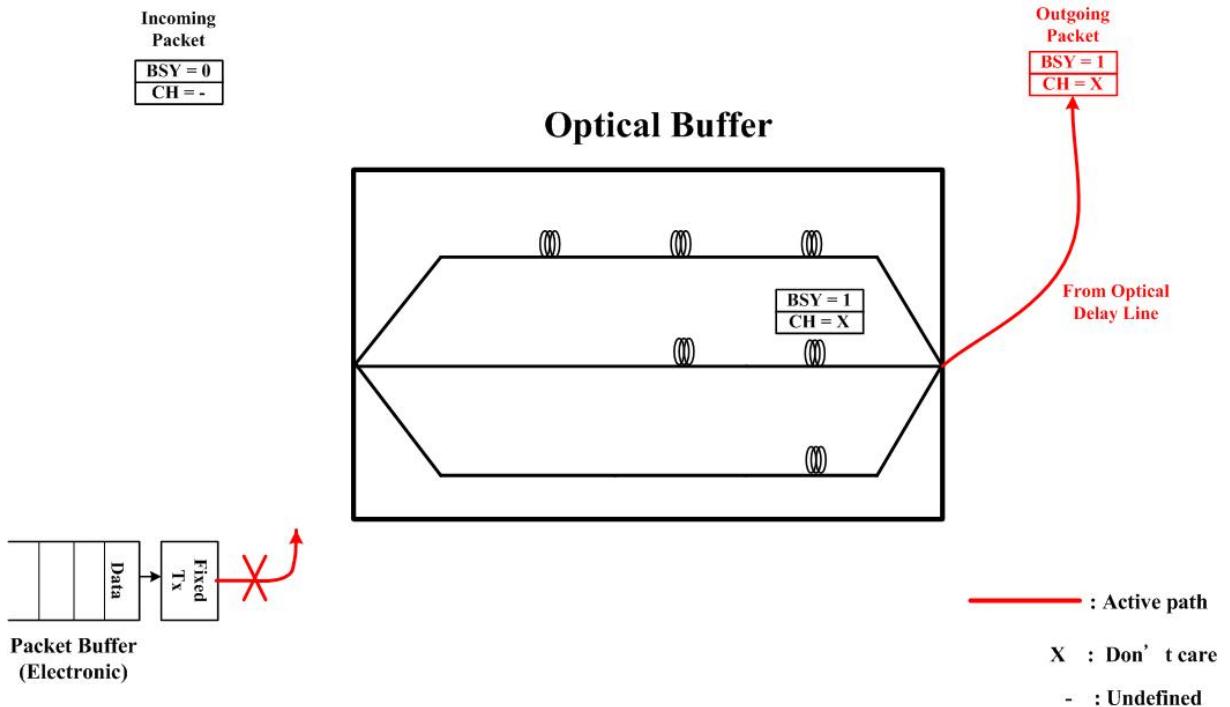

(iii) 若 incoming packet 為 empty 時，則我們為了降低 optical buffer 佔滿的程度且避免 optical buffer 的 overflow，故當 optical buffer 內有 packet 等待輸出時，則存於 Packet Buffer 內的 data 將不能輸出 (Figure 18-1); 反之，若

此刻 optical buffer 內無 packet 暫存時，則我們可以讓 new generated packet 成為 outgoing packet 輸出 (Figure 18-2)。

Fig. 18-1: Transmitting step of case (iii)-1 for IWS

Fig. 18-2: Transmitting step of case (iii)-2 for IWS

(iv)以上我們均假設 Packet Buffer 內有 data 等待傳送，而若 Packet Buffer

內並無 data 需要傳送時且 incoming packet 亦不為 empty 時，則此時我們僅需視目前 Optical Buffer 是否有 packet 等待輸出將 incoming packet 作適當的 forwarding 即可 (Figure 19-1, 19-2)。

Fig. 19-1: Transmitting step of case (iv)-1 for IWS

Fig. 19-2: Transmitting step of case (iv)-2 for IWS

### 3.3 Proposed protocol for PSS

#### 3.3-1 Basic concepts

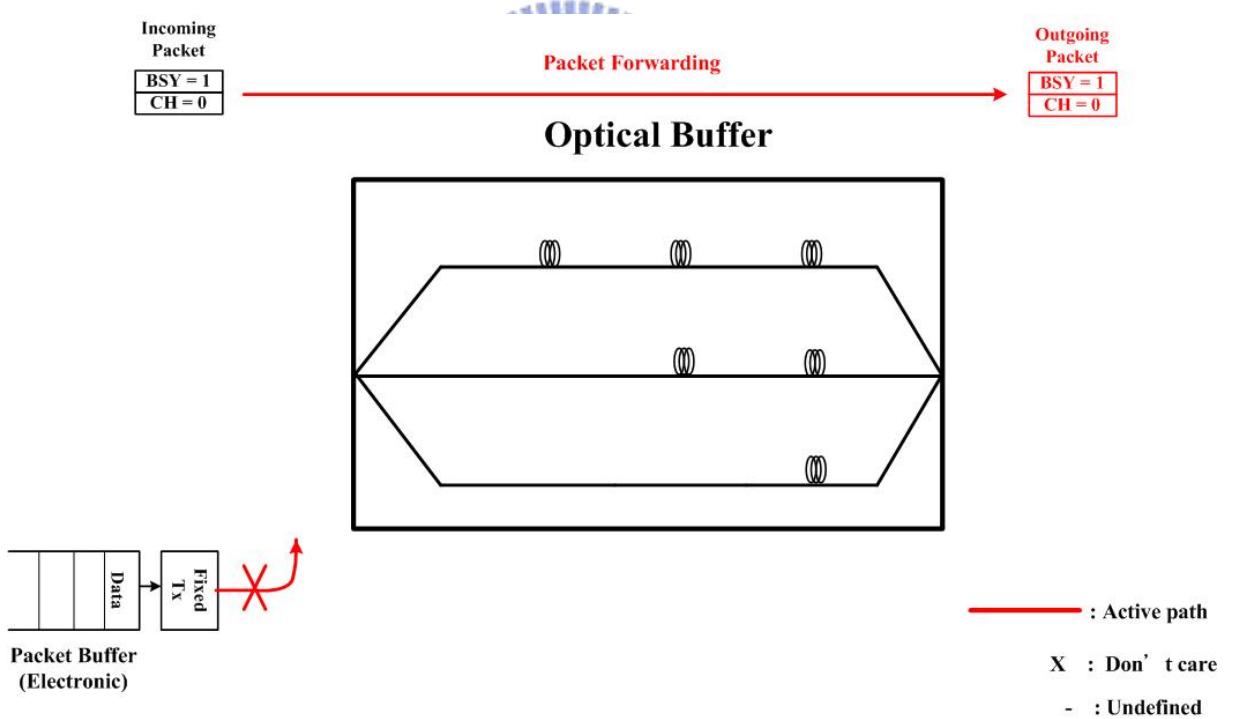

不同於 IWS node 需將每個 photonic slot 經 de-multiplexer 將所有波長解開處理，最後再藉由 multiplexer 傳送出去；在 PSS 系統裡，node 只要針對每個 photonic slot 去作交換以及處理，故在此我們所引入的 access cycle 概念將針對每個 photonic slot 而言，亦即每個 photonic slot 可為 access cycle head 或位於該 access cycle 之內。

如同之前於 IWS 所提到的作法，此 access cycle 將允許當 node 因為 channel 為 busy 時而無法傳送 data 時，在每個 access cycle 內可以藉由 insertion 而得到 access 的機會。不過值得注意的是，因為在此我們是以整個 photonic slot 視為一個不可分割的個體來處理，亦即 incoming photonic slot 上可能有些波長已被使用，而有些波長尚未被使用過。故當 node 若欲傳送的 packet 是使用尚未載有 packet 的波長時，我們僅需使用 coupler 將 packet 載入該波長且不需藉由 cycle head 的想法來作 insertion；反之，當一個 photonic slot 抵達時，node 發現該 slot 裡欲使用的波長已載有 packet 的話，則我們可以利用判斷該 slot 是否為 cycle head 來產生一個新的 photonic slot 來承載欲傳送之 packet 並作 slot 的 insertion。

因此不同於之前 IWS 所提到的當 node 產生的 packet 無法 access 上去時，僅需判斷該 incoming packet 是否為 access cycle head，便可藉由 packet

insertion 將所產生的 packet 放入網路。在 PSS 裡 node 將先把 packet 載入 incoming slot 裡尚未使用過的波長，之後如果仍有 packet 無法傳送上去，則我們判斷該 incoming slot 是否為 cycle head; 若為 cycle head 的話則可以產生一個新的 photonic slot 並且用於承載那些無法 access 上去的 packet。

而如同之前 IWS 的作法，我們亦使用 optical delay line 做為 optical buffer 來扮演 F-Buff 的角色；而 incoming slot 以及 new generated slot 將視 optical buffer 的狀況來作適當的 forwarding，亦即一旦 optical buffer 內有 photonic slot 要輸出時，我們一律讓該 slot 成為 outgoing slot 以避免 packet 的 loss；同時 incoming slot 以及 new generated slot 則放入 optical buffer 內暫存。

最後關於 overload control 的部份，我們的作法跟之前針對 IWS 提出的方法很類似，即當一個 empty 的 incoming slot 抵達 node 時，若此刻 optical buffer 內有 photonic slot 暫存的話，則為了降低 optical buffer 的 load，我們將禁止 node 產生新的 photonic slot 來承載 packet；且若 incoming slot 為 cycle head 時，此刻若有需要產生新的 slot 來承載無法傳送之 packet 時，我們亦需在 optical buffer 仍有足夠的空間來存放 incoming slot 以及 new generated slot 之前提下，才可執行 new slot 的 insertion，詳細 access 的流程我們亦於之後作說明。

### 3.3-2 Node architecture and removal mechanism

因為在此我們是針對每個 photonic slot 加入 access cycle 的概念，故我們將在每個 photonic slot 的 header 裡加入一個是否為 cycle head 的判斷機制 [9] (Figure 20)。

| Slot header |             |                   |                        |

|-------------|-------------|-------------------|------------------------|

| $\lambda_0$ | <b>BSY</b>  | <b>CH</b>         | Other Slot Information |

| $\lambda_1$ | <b>used</b> | <b>Sub-header</b> | <b>data</b>            |

| $\lambda_2$ | <b>used</b> | <b>Sub-header</b> | <b>data</b>            |

| $\lambda_3$ | <b>used</b> | <b>Sub-header</b> | <b>data</b>            |

|             |             |                   | <b>padding</b>         |

Fig. 20: Slot format of PSS

如圖所示 Bust (BSY) bit 用來判斷該 photonic slot 是否為 empty，當 BSY 為 0 時表示該 slot 為 empty，亦即其上所有波長均沒有承載任何 packet；而 Cycle Head (CH) bit 則用來判斷該 slot 是否為 access cycle 的 cycle head，以作為是否產生新的 photonic slot 來作 insertion 的依據，若該 slot 之 CH bit 為 1 時則允許 node 將未能傳送之 packet 以產生新的 photonic slot 來承載，且我們亦需注意所有新產生的 photonic slot 其 CH bit 均為 1，用來取代 incoming slot 其 cycle head 的地位或是形成一個新的 access cycle。

而我們針對 PSS 所提出的 node architecture 則如 Figure 21 所示。

Fig. 21: PSS node architecture

當一個 incoming slot 抵達該 node 時，首先先藉由 splitter 解開其 header 獲得該 slot 相關的資訊，且因為該 incoming slot 可能載有傳送至該 node 的 packet 所以藉由 slot copying 擷取欲傳送給自己的 packet，且若是確定該 slot 上所載的 packet 均已被接受過後，則同時將該 incoming slot 作 erase 的動作。接下來再由 header 得知的資訊判斷仍有哪些波長可用以及該 slot 是否為 cycle head，若為 cycle head 則 node 無法 access 上去之 packet 亦可產生新的 photonic slot 來承載，最後並利用 optical delay line 來暫存無法立即輸出的 photonic slot。

而至於 slot removal 的機制，我們已於 2.3 節討論過因此在此就不多作贅述，詳細步驟可參閱 [Figure 11](#)。

### 3.3-3 Access procedure of proposed protocol for PSS

在這節裡面我們將針對每個 PSS node 的 access procedure 作探討，且如同之前 IWS 所提到的，為了因應 optical delay line 無法永久儲存 photonic slot 的特性，因此我們將以 incoming slot 是否為 cycle head 來作為當 node 有 packet 無法傳送時是否執行 slot insertion 的依據。

同樣我們將 access procedure 分為以下幾個 case 作探討，其中在 case (i)-(iii)我們假設於 Packet Buffer 內均有 packet 等待傳送，且在此我們均假設 optical buffer 內均有 photonic slot 等待輸出：

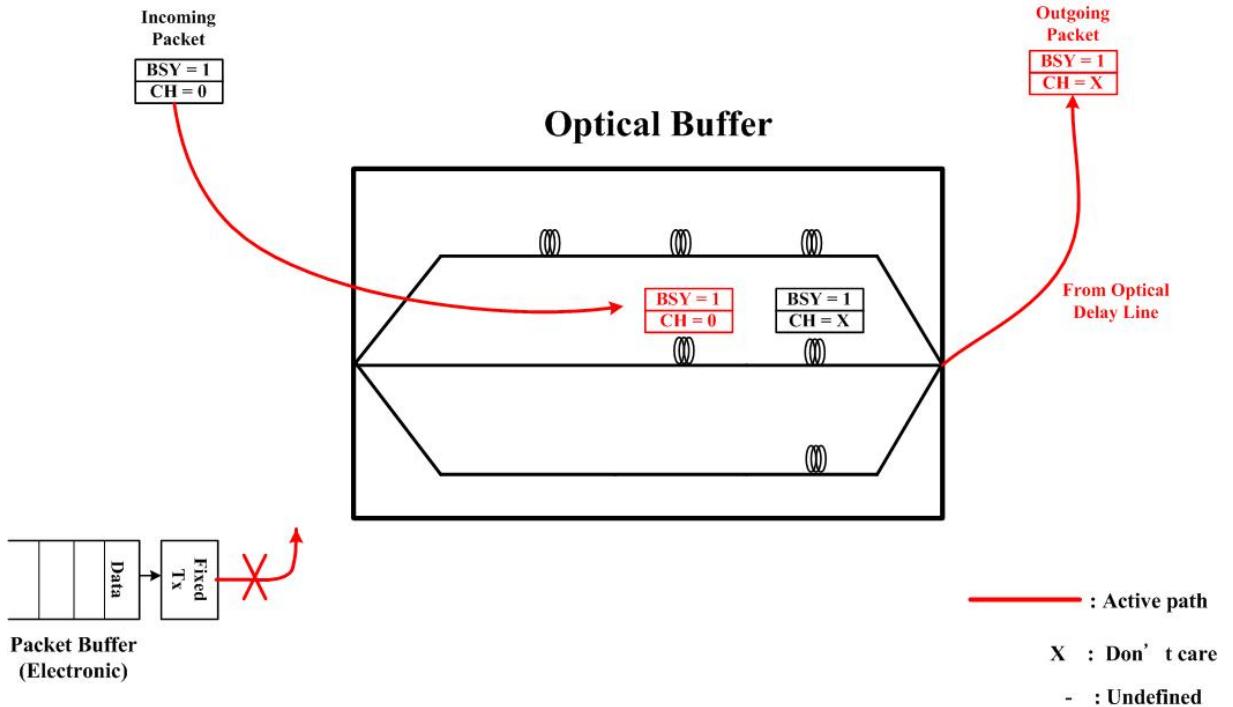

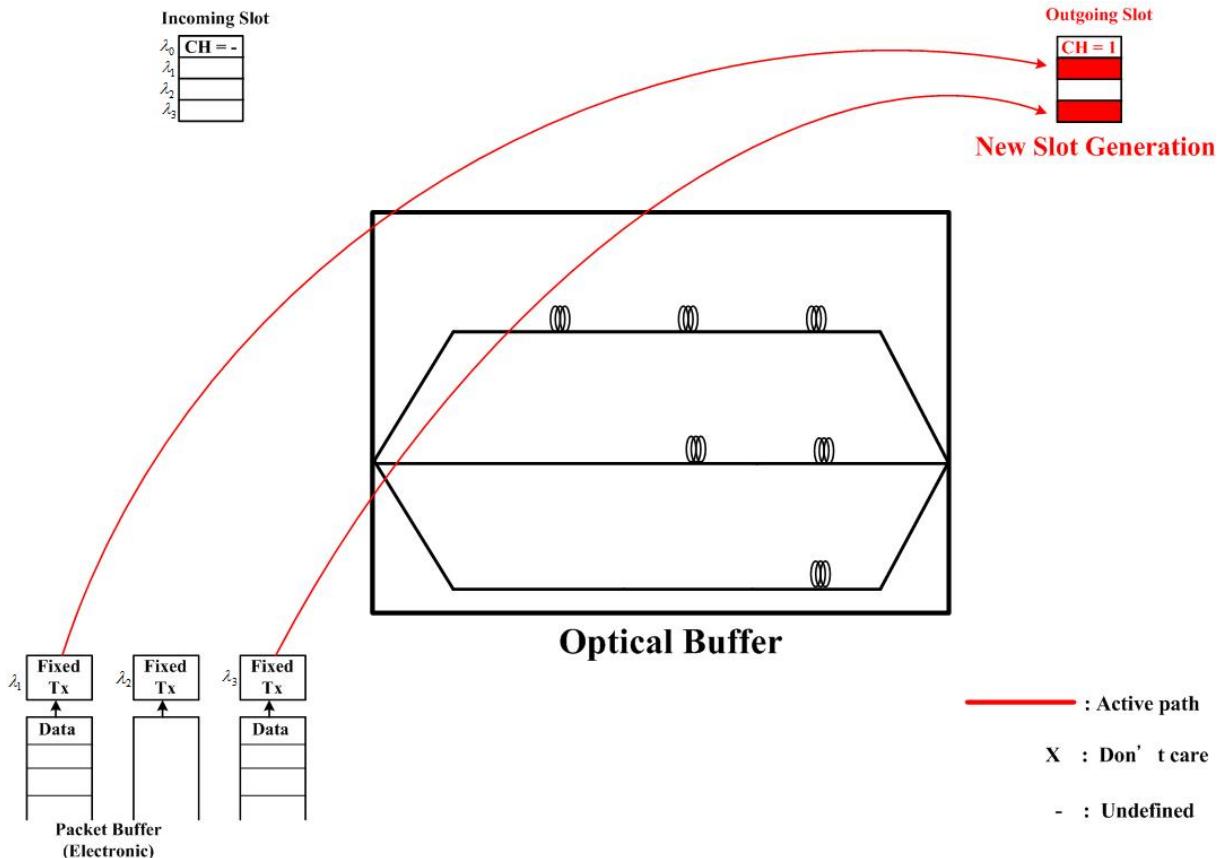

(i) 當 incoming slot 不為 empty 且為 cycle head 時，則當 node 先將 packet 載入 incoming slot 內仍未被使用的波長後，若 node 仍有未被傳送的 packet 且此時我們可產生一個新的 photonic slot 來承載無法傳送之 packet，且此 slot 之 CH bit 為 1，同時該 incoming slot 之 CH bit 亦需改為 0，故我們將以 slot 不會發生 collision 為原則將 incoming slot 以及 new generated slot 放入 optical buffer 內適當的位置，且讓 optical buffer 內輸出之 photonic slot 成為 outgoing slot([Figure 22-1](#))。而若是 optical buffer 內並無 slot 暫存時，則我們會讓 new generated slot 成為 outgoing slot 而將 incoming slot 暫存於 optical buffer 內。

Fig. 22-1: Transmitting step of case (i)-1 for PSS

反之，若 incoming slot 未被使用之波長就足以承載所有 node 欲傳送之 packet，則我們僅需將 packet 載入該 incoming slot 且放入 optical delay line 適當之位置，而無須修改其 CH bit (因為此時我們並無須產生新的 slot 來承載未能 access 之 packet)，且讓 optical delay line 輸出之 slot 成為 outgoing slot (Figure 22-2)。同理，若 optical buffer 內並無 slot 暫存則該 incoming slot 可直接 forwarding 成為 outgoing slot。

Fig. 22-2: Transmitting step of case (i)-2 for PSS

最後，若 node 已將欲傳送之 packet 載入 incoming slot 內可用之波長而仍有 packet 因該波長原先已載有 packet 而無法傳送時，而此時 optical buffer 內只剩一個位置可存放 slot，則此時為了避免 optical buffer 的 overflow，故即使該 incoming slot 為 cycle head 我們仍不可產生新的 slot 來承載未能傳送之 packet (Figure 22-3)。

Fig. 22-3: Transmitting step of case (i)-3 for PSS

(ii) 若 incoming slot 不為 empty 亦不為 cycle head 時，則此時 node 僅可將欲傳送之 packet 載入該 incoming slot 仍可使用之波長，而若有 packet 未傳送時因為該 incoming slot 不為 cycle head，故無法藉由產生新的 photonic slot 來承載該 packet。且若 optical buffer 此刻無 photonic slot 正要輸出，則我們允許讓該 incoming slot 成為 outgoing slot (Figure 23-1); 反之，若此刻 optical buffer 內有 slot 正準備輸出，則該 incoming slot 需放至 optical buffer 內適合之 optical delay line (Figure 23-2)。

Fig. 23-1: Transmitting step of case (ii)-1 for PSS

Fig. 23-2: Transmitting step of case (ii)-2 for PSS

(iii) 若 incoming slot 為 empty 時，則為了降低 optical buffer 之負載；若當 optical buffer 內仍有 slot 準備輸出時，即使該 incoming slot 有可用之波長供 node 傳送 packet，我們仍須禁止 packet 的傳送 (Figure 24-1)。

Fig. 24-1: Transmitting step of case (iii)-1 for PSS

反之，假若此刻 optical buffer 內沒有 photonic slot 等待輸出，則我們允許 node 將所有欲傳送之 packet 載入該 empty slot，亦即作 random access 的動作，且讓該 slot 成為一個新的 access cycle 之 cycle head (具 CH bit 為 1) 並且作為 outgoing slot (Figure 24-2)。

Fig. 24-2: Transmitting step of case (iii)-2 for PSS

(iv) 以上我們均假設 node 有 packet 需被傳送之前提去作討論；反之，若 node 無任何 packet 需要傳送時，則我們僅需將 incoming slot 針對 optical buffer 目前是否有 slot 輸出作適當的 forwarding 即可 (Figure 25-1, Figure 25-2)。

Fig. 25-1: Transmitting step of case (iv)-1 for PSS

Fig. 25-2: Transmitting step of case (iv)-2 for PSS

以上 3.2 以及 3.3 節我們已詳細介紹我們所針對 IWS 以及 PSS 系統所提供的 access protocol，在這邊我們主要用一些 optical buffer 來達成即使在網路 loading 很重時仍可 packet insertion 的目的，且不同於 ACCI protocol 以及 RPR fairness algorithm 需要在每個 node 使用 electronic buffer 來暫存 packet，我們是利用 optical delay line 的特性來達到 optical buffer 的功能；也因此能適用於 all-optical 的網路克服在光電轉換上的瓶頸，進而達到高速網路的目的。

不過值得注意的是，我們在每個 node 裡面加入 optical delay line 却有可能使得 packet 傳送的 delay 增加；而在下一章節我們將會以 simulation 來說明此在 packet delay 的影響是我們可以接受的，且我們亦會分別針對我們所提出的 protocol for IWS 以及 PSS 作一個模擬的分析，來驗證我們一開始提出這個 protocol 的目的，亦即解決在網路 loading 不平衡的情況下所產生的 fairness 問題。

## Chapter 4

### Simulation Results and Performance Analysis

這節我們主要對之前我們所提出的 MAC protocol 進行模擬，並針對模擬結果作一個分析以確定此 protocol 能有效解決之前我們所提到的 fairness 問題。

#### 4.1 Network parameters and traffic model

在此我們針對此單一環狀光纖網路所採用的模擬參數如 [Table 1](#) 所示。

| Parameter                                           | Value     |

|-----------------------------------------------------|-----------|

|                                                     |           |

| Number of nodes                                     | 20        |

| Number of sub-nodes                                 | 5         |

| Number of wavelength channels                       | 5         |

| Per-wavelength capacity                             | 1 Gbps    |

| Packet size                                         | 1000 byte |

| Packet buffer (Electronic) size                     | infinite  |

| Optical buffer size (Number of optical delay lines) | 10        |

| Node to node distance                               | 10 km     |

Tab. 1: Network parameters used in simulation

且我們所採用的 traffic model 為 bursty traffic，即 traffic 並不是由單一的 mean arrival rate 所構成，而是由兩個 state 的 traffic 所組成，如此一來較能貼近實際 traffic 的狀況；分別為 high state 以及 low state，當處於 high state 時 traffic 具有較高的 arrival rate；反之，若處於 low state 則此時 traffic 之 arrival rate 較低。(Figure 26)

Fig. 26: Two-state bursty traffic model

如圖所示，當 traffic 處於 high state 時具  $\lambda_H$  之 arrival rate，反之則為  $\lambda_L$  之 arrival rate。且當 traffic 於 high state 時每執行完一次 packet generation 的動作便有  $\alpha$  的機率轉為 low state，亦即其仍停留在 high state 的機率為  $1-\alpha$ ；同理於 low state 之 state 轉換的機率為  $\beta$ ，而其停留在 low state 之機率為  $1-\beta$ 。

由此 bursty traffic model，我們可以算出 mean arrival rate  $\lambda$ ：

$$\lambda = \frac{\alpha \cdot \lambda_L + \beta \cdot \lambda_H}{\alpha + \beta}$$

且我們亦可定義出 Burstiness 來表示此 traffic bursty 的程度：

$$B(\text{Burstiness}) = \frac{\lambda_H}{\lambda}$$

而於之後的 simulation 我們所採用的 state transition probability 分別為  $(\alpha, \beta) = (0.2, 0.02)$ ，且在相同的 mean arrival rate  $\lambda$  下針對不同的 Burstiness 值去調整  $\lambda_H$  以及  $\lambda_L$ 。

最後我們將針對我們欲探討的 IWS 系統找出一個系統在 balanced load 下每個 sub-node 所能允許的最大 traffic arrival rate，並以該 arrival rate 去作 normalize。

最後因為在此我們每個針對單一環狀網路裡每個 IWS node 是採用 fixed receiver，且每個 node 底下包含五個 sub-nodes 且共同使用五個 wavelength 傳送，故我們可以利用在 balanced load 下針對每個 wavelength 去考慮每個 node 之 traffic arrival rate 以及 traffic departure rate 相等的情況下，來找出整個系統所最大能承載之 per sub-node traffic arrival rate，如下所示：

$n$  : Number of nodes

$a$  : Per sub-node traffic arrival rate

$$1 - a \times \left[ \frac{n-2}{n-1} + \frac{n-3}{n-1} + \dots + \frac{1}{n-1} \right] = a$$

我們可以算出在 balanced load 底下當  $a = \frac{2}{n}$  時此時系統為飽和，且因為在此我們所考慮的是  $n = 20$ ，故 per sub-node 所能允許之最大的 traffic arrival rate

為 0.1，且我們在之後 IWS 以及 PSS 的分析將以此值去作 normalize。

現在我們便以之前 Table 1 所提到的 network parameters 針對 IWS 以及 PSS 系統去作模擬，以驗證在前述所計算出之 per sub-node traffic arrival rate 下系統為飽和。

Fig. 27-1: Mean access delay vs per sub-node traffic arrival rate of IWS and PSS in fully balanced traffic

如 Figure 27-1 所示，在此我們 mean packet access delay 所代表的意義是指每個 packet 從 sub-node 向上傳遞至該 node 之 packet buffer 暫存後一直到該 packet 真正被傳送到網路上所需的時間；我們可以看出在 IWS 系統且 balanced load 底下，當每個 sub-node 所提供的 traffic arrival rate 為 0.1 時，則此系統達到飽和，這與之前我們所計算出的相符合，故之後我們將以此 arrival rate 值去作 normalize，亦即若 traffic arrival rate 為 0.06，則其 normalized

過後的值為 0.6。

且由 Figure 27-1 我們亦可看出 PSS 系統裡每個 sub-node 最大允許的 packet arrival rate 為 0.06，此亦驗證了之前我們所提到的 PSS 系統由於在每個 node 裡面雖然可以使用 wavelength insensitive 的元件來降低 cost，然而其在頻寬的使用率上會較低。

接下來，我們亦針對此兩系統在 balanced load 底下每個 node 所能達到最大的 throughput 作模擬。(Figure 27-2)

Fig. 27-2: Mean access delay vs per node throughput of IWS and PSS in fully balanced traffic

由上圖我們可以看出在 balanced load 下，每個 IWS node 可達到的最大 throughput 約為 500 Mbps，而若為 PSS node 則約為 300 Mbps，此亦與之前我們所提到的結論相符合。

## 4.2 Simulation results for IWS

在這節裡面我們將針對我們之前對 IWS 所提出的 MAC protocol 作模擬，並與原始未採用此 protocol 之架構作比較，且驗證是否有解決我們前述所提到的在網路 load 不平衡狀態下所產生的 fairness 問題。

且在此我們將觀察在幾個不同 unbalanced load 底下 (Table 2)，此 protocol 對 fairness 改進的程度，且我們亦會考慮若為 bursty traffic 且在不同 burstiness 底下是否仍有相同的效果。

| Unbalanced Traffic | Normalized traffic arrival rate offered by per sub-node |                     |

|--------------------|---------------------------------------------------------|---------------------|

| Case 1             | <b>Node 1 = 10</b>                                      | <b>Others = 0.3</b> |

| Case 2             | <b>Node 1 = 10</b>                                      | <b>Others = 0.7</b> |

| Case 3             | <b>Node 1,11 = 5</b>                                    | <b>Others = 0.3</b> |

| Case 4             | <b>Node 1,11 = 5</b>                                    | <b>Others = 0.7</b> |

| Case 5             | <b>Node 1,2,3,4 = 2</b>                                 | <b>Others = 0.2</b> |

Tab. 2: Unbalanced load traffic cases of IWS

我們在此共考慮五種 unbalanced load 的情況，在 case 1 跟 2 我們均假設

node 1 為 malicious node，亦即其 traffic 流量非常大且超乎我們所預期，我們將觀察在此情況下它會對其他 node 產生的影響以及我們所提出的 protocol 是否能克服此影響；而 case 3 跟 4 我們則假設若網路中的 malicious node 不只一個，考慮其他 node 在 load 低或 load 高時可能的影響；最後在 case 5 我們考慮的是具四個高流量的節點且探討此高流量節點間 fairness 的問題。

接下來我們考慮 IWS 系統在此五個 case 下針對不同 burstiness 的 busty traffic 去作分析，且其中 mean end-to-end delay 代表的是一個從 packet 自其抵達 packet buffer 等待傳送一直到被接收下來所需的時間。

Fig. 28-1: Mean access delay vs node index in case 1 of unbalanced traffic

Fig. 28-2: Mean end-to-end delay vs node index in case 1 of unbalanced traffic

Fig. 29-1: Mean access delay vs node index in case 2 of unbalanced traffic

Fig. 29-2: Mean end-to-end delay vs node index in case 2 of unbalanced traffic

由 Figure 28-1 以及 Figure 28-2 我們可以看出在 case 1 底下，由於 node 1 為 malicious node 其 traffic 流量非常大，因此造成位於其下游的節點因為可用的頻寬絕大部分都被 node 1 純搶走了，故產生 starvation 的現象，且由圖我們可以發現越靠近 node 1 之 node 其 mean access delay 越大，表示其因為一直得不到 access 的機會造成封包平均必須停留在 packet buffer 內等待很長的時間才有辦法傳送出去，因此也造成其 mean end-to-end delay 在越靠近 malicious node 之 node 會越大。且在此我們亦考慮不同 burstiness 的 traffic，我們亦可發現當 burstiness 越大時，packet 的平均 delay 均會越大。

而若是套用我們所提出的 MAC protocol for IWS，我們可以發現原先靠近所有節點的 mean access delay 幾乎不會因為 node 1 為 malicious node 而有所影響，亦即所有 node 大家的 access 機會是相等的，並不會因為離 node 1

距離的遠近而有所改變；原因是因為我們採用了 access cycle 的想法，即使有些 node 因為得不到頻寬而產生 starvation 的現象，我們亦可藉由此 access cycle 去增加其 access 的機會，進而保障其該得的頻寬。

我們再觀察 mean end-to-end delay 亦呈現一個近乎平坦的現象，原先在 node 11 之前的節點受 node 1 影響導致 end-to-end delay 增大的效應已有了非常明顯的改善，但值得注意的是 node 11 之後的節點其 end-to-end delay 亦有所增長；而這是合理的，因為在我們所提出的架構裡我們利用了 optical delay line 於每個 node 使用，故原先遠離 node 1 之節點會因為此 optical delay line 的效應造成其 mean end-to-end delay 增長，不過由 simulation 的結果我們可以確認此結果是我們可容忍的，因為所有 node 的 mean end-to-end delay 由 simulation 結果發現並不會因為距離 malicious node 的遠近而有很大的差別。

而由 [Figure 29-1](#) 以及 [Figure 29-2](#) 我們亦可看出若其他 node 提高其 load 時，在 fairness 問題的改善上亦有顯著的成果，不同的是我們可以發現在 node 2 以及 node 3 其 packet delay 的降低不若其他 node 來得明顯；這是因為我們現在提高了其他 node 的 load，而當越靠近 malicious node 之節點其 access 機會的獲得就越需要 access cycle 的幫助，而我們之前 access cycle 的概念是在一個 cycle time 內可以允許有一次 access 的機會，而此刻因為 node 2 和 node 3 的 load 增加了，故該 access cycle 雖然亦可增加其 access 的機會

卻可能無法完全滿足，不過與原始不採用此 protocol 的架構相比，卻已有很明顯的改善了。同理在 mean end-to-end delay 上後段節點 mean end-to-end delay 的增加亦是因為 optical delay line 的影響，而在前段靠近 malicious node 的節點其 mean end-to-end delay 亦可以有效的降低，整體而言仍是處於一個較 fair 的狀況。

而我們亦可發現不同 burstiness 的 traffic 在此 protocol 的運用下均可有效改善其 fairness 的問題，只是若 burstiness 越大時其 delay 亦會較大。

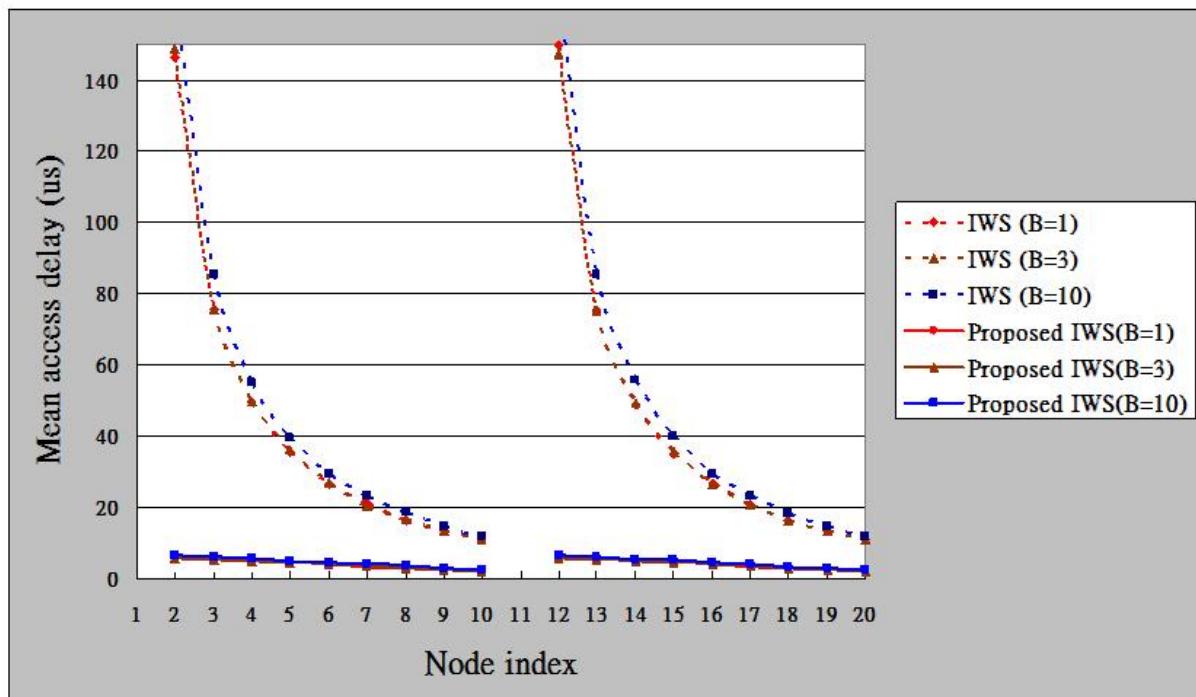

接下來我們將考慮若網路中的 malicious node 不只一個，在此我們假設 node 1 及 node 11 具有較高的流量，觀察其他 node 在此情況下會受到何種影響以及我們所提出的 access protocol 是否能改善此種效應，如 case 3 及 case 4 所示。

Fig. 30-1: Mean access delay vs node index in case 3 of unbalanced traffic

Fig.30-2: Mean end-to-end delay vs node index in case 3 of unbalanced traffic

Fig. 31-1: Mean access delay vs node index in case 4 of unbalanced traffic

Fig. 31-2: Mean end-to-end delay vs node index in case 4 of unbalanced traffic

由 Figure 30-1 及 Figure 30-2 我們可以看出若網路上具有兩個高流量的節點 node 1 及 node 11 時，則我們可看出此兩個 node 將會造成其下游接近節點之 mean access delay 較遠離該 node 的大許多，因此即使其他節點均具有相同的 traffic arrival rate 却產生 unfair 的現象。而若是在 medium access control 上加入我們所提出的 protocol，我們可以發現在 mean access delay 上所產生的 unfair 現象可獲得很好的改善，亦即原先靠近流量大的節點已經因為 access cycle 的機制而得到其應有的頻寬。而在 Figure 30-2 裡我們亦可看出靠近該兩個 node 的 mean end-to-end delay 亦可有效降低，而較遠離之節點如 node 6-10 以及 node 16-20 會因為當 packet 在傳送的過程當中可能需要進入 optical delay line 內暫存而導致 mean end-to-end delay 的增加，不過因為所有的 node 的 mean end-to-end delay 均不會有太大的差別，故這種情況

是我們可以接受的。

同理，在 Figure 31-1 及 Figure 31-2 我們所考慮的是其他 node 的 traffic arrival rate 亦增加的情況下，則此時在 unfair 程度的改善雖不若 case 3 來得好，但是我們對於如 node 2 以及 node 12 因為 starvation 的現象而導致 mean access delay 急遽上升的情形，在運用此 protocol 後亦可以有相當幅度的抑制，亦即原先 unfair 的情形亦獲得緩和，且 mean end-to-end delay 亦較原先不採取此 protocol 比有明顯的改善。

最後我們考慮在網路中若具有四個高流量的節點而其他節點的流量正常的 case 下所得的模擬結果(Figure 32-1, Figure 32-2)。我們可發現雖然經過 insertion 的機制後，原先流量正常的節點如 node 5 以後的節點所受到的 unfair 現象已獲得改善；但是就 node 1 至 node 4 之間，我們仍可發覺 node 1 相較於 node 4 仍是處於一個較有利的位置，它們之間仍存在 unfair 的問題，亦即我們對於那些流量高的節點之間所產生的公平性問題仍有待克服。

Fig. 32-1: Mean access delay vs node index in case 5 of unbalanced traffic

Fig. 32-2: Mean end-to-end delay vs node index in case 5 of unbalanced traffic

### 4.3 Simulation results for PSS

在這節我們同樣對 PSS 系統作模擬，並且觀察我們針對 PSS 所提出的 MAC protocol 是否同樣能解決在 unbalanced load 下所產生的 fairness 問題。

在此我們同樣觀察幾個不同 unbalanced load 的 case，如 [Table 3](#) 所示。

| Unbalanced Traffic | Normalized traffic arrival rate offered by per sub-node |                     |

|--------------------|---------------------------------------------------------|---------------------|

| Case 1             | <b>Node 1 = 8</b>                                       | <b>Others = 0.2</b> |

| Case 2             | <b>Node 1 = 8</b>                                       | <b>Others = 0.4</b> |

| Case 3             | <b>Node 1,11 = 4</b>                                    | <b>Others = 0.2</b> |

| Case 4             | <b>Node 1,2,3,4 = 1</b>                                 | <b>Others = 0.1</b> |

Tab. 3: Unbalanced load traffic cases of PSS

如同之前於 IWS 所採用的分析方法，在 case 1 跟 case 2 我們同樣假設網路中有一個 malicious node 具超乎預期的流量產生，觀察所可能產生的 unfair 情形以及我們針對 PSS 所提出的 protocol 對此情形的改進程度；且此處我們所採取的 normalized arrival rate 是以前述 IWS 系統在 balanced load 底下飽和時為基準所算出的 per sub-node traffic arrival rate 去作 normalize。而 case 3，4 我們則考慮若網路中高流量的節點不只一個時，探討對其他節

點產生的影響以及改善的程度。

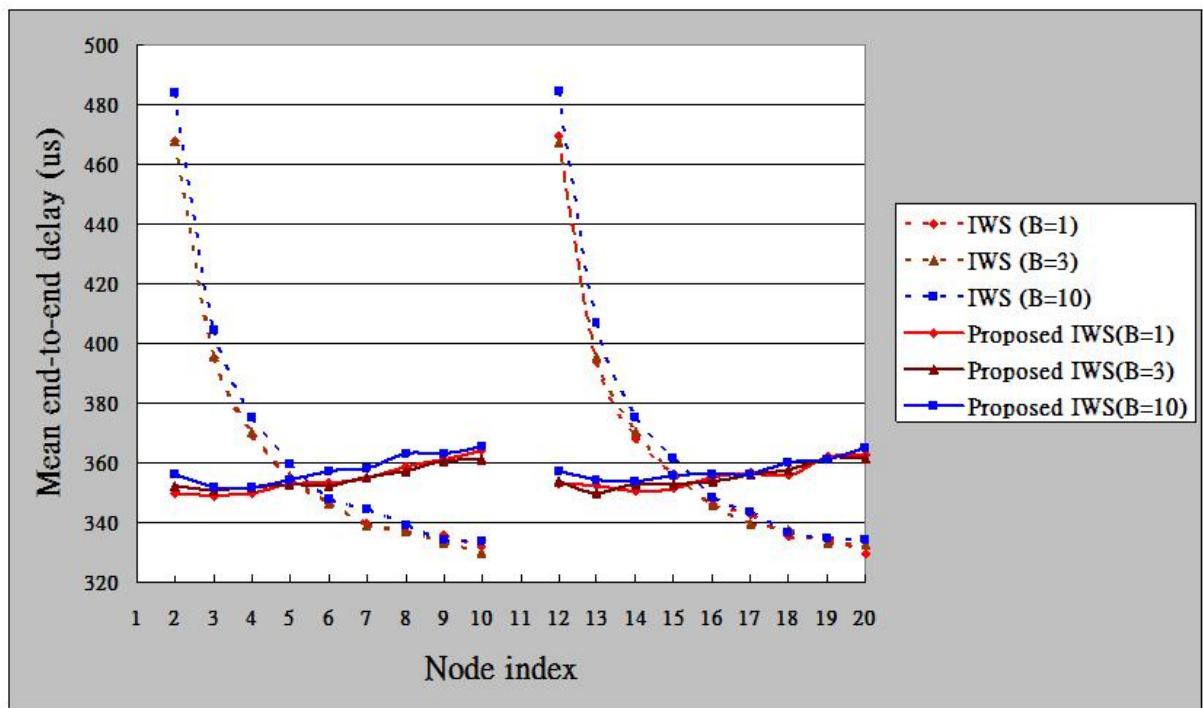

Fig. 33-1: Mean access delay vs node index in case 1 of unbalanced traffic

Fig. 33-2: Mean end-to-end delay vs node index in case 1 of unbalanced traffic

Fig. 34-1: Mean access delay vs node index in case 2 of unbalanced traffic

Fig. 34-2: Mean end-to-end delay vs node index in case 2 of unbalanced traffic

由 Figure 33-1 及 Figure 33-2 我們可以發現在 PSS 系統裡，若是網路中存在一個 malicious node，則該 malicious node 壟斷網路頻寬的情形較之前 IWS 來得更為嚴重；這點我們可以由在 node 1 為 malicious 時，node 2 至 node 10 之 mean access delay 均非常大，而這是因為幾乎拿不到 access 的機會導致其 packet buffer 會呈現一個無限增長的情形所造成的，因此 mean end-to-end delay 在那些 node 亦是處於一個非常大的狀況下，故此 malicious node 造成其他 node 產生 unfair 的現象，也就是越靠近該 malicious node 的節點將越難得到應有的頻寬。

而若是運用我們所提出的 access protocol 之後，我們可發現對於該 unfair 現象改善得非常明顯，如 node 2-10 現在 mean access delay 均約在  $30\mu s$  左右，表示我們已經解決了那些 nodes 的 starvation 現象；而 mean end-to-end delay 此時所有 nodes 約在  $700-900\mu s$  間，如同之前我們在 IWS 裡的分析所得到的結果類似。

同理在 case 2 裡我們加大其他 node 的 traffic arrival rate，如 Figure 34-1 及 34-2 所示，產生 unfair 的現象亦跟 case 1 很類似。而在採用我們所提出的 access protocol 後發現在前段 nodes 的改善亦相當明顯，不過此刻因為 traffic arrival rate 加大故平均 mean access delay 也較 case 1 來得大，且在 mean end-to-end delay 上則約散佈於  $900-1200\mu s$  較 case 1 來得大；這是因為此刻的 traffic arrival rate 較大，故 optical buffer size 內亦會存有較多的 packet，

因此平均每個 packet 所需遭遇的 delay 亦會增加。

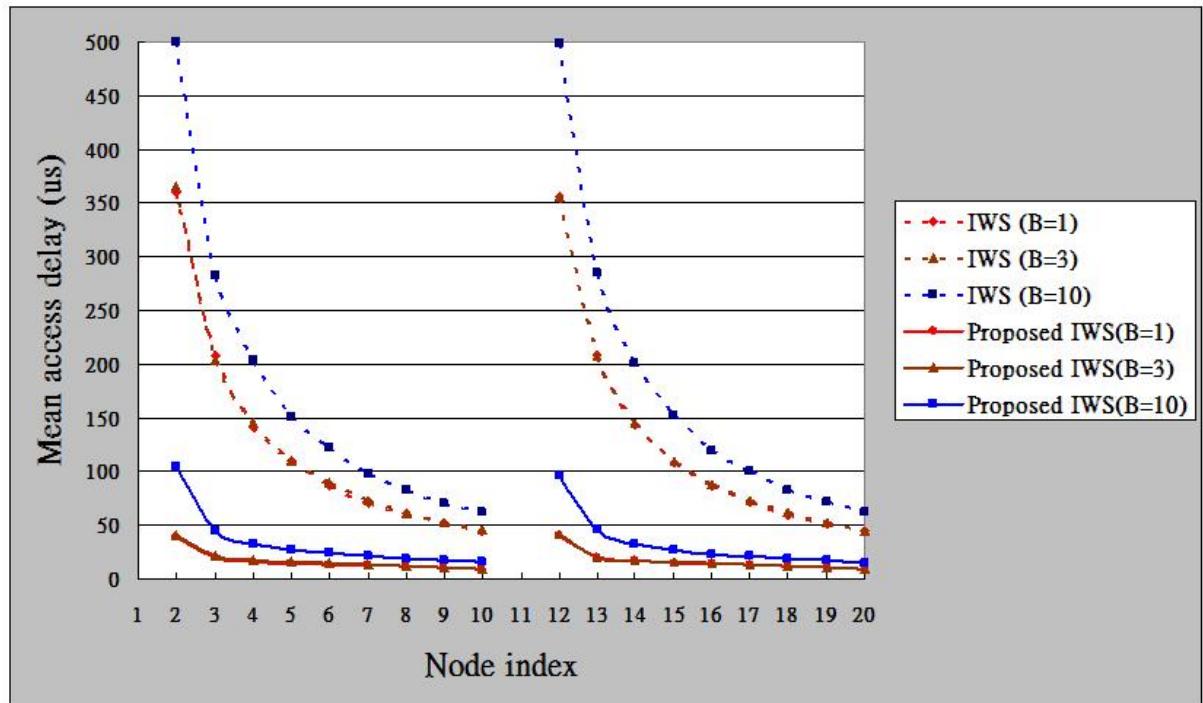

我們再就 case 3 作探討，考慮網路上萬一不只一個 malicious node 時可能對其他 node 產生的影響。(Figure 35-1, 35-2)

Fig. 35-1: Mean access delay vs node index in case 3 of unbalanced traffic

Fig. 35-2: Mean end-to-end delay vs node index in case 3 of unbalanced traffic

如同之前於 IWS 中 case 3 以及 case 4 的探討，於 PSS 中若是有兩個 node 具有高流量時，其亦會造成其下游靠近的節點的 access opportunity 受到影響，如 [Figure 35-1](#) 所示，越靠近該兩個 node 則 mean access delay 越大，且 mean end-to-end delay 亦有相同的影響。

而採用我們所提出的 access protocol 後，由 [Figure 35-1](#) 可看出所有 nodes 的 mean access delay 均在  $80\mu s$  以下，可有效改善 node 1 和 node 11 所造成的 unfair 現象，且 mean end-to-end delay 亦呈現一個較均勻的現象而不會因為距離該 malicious node 的遠近而有所差別。

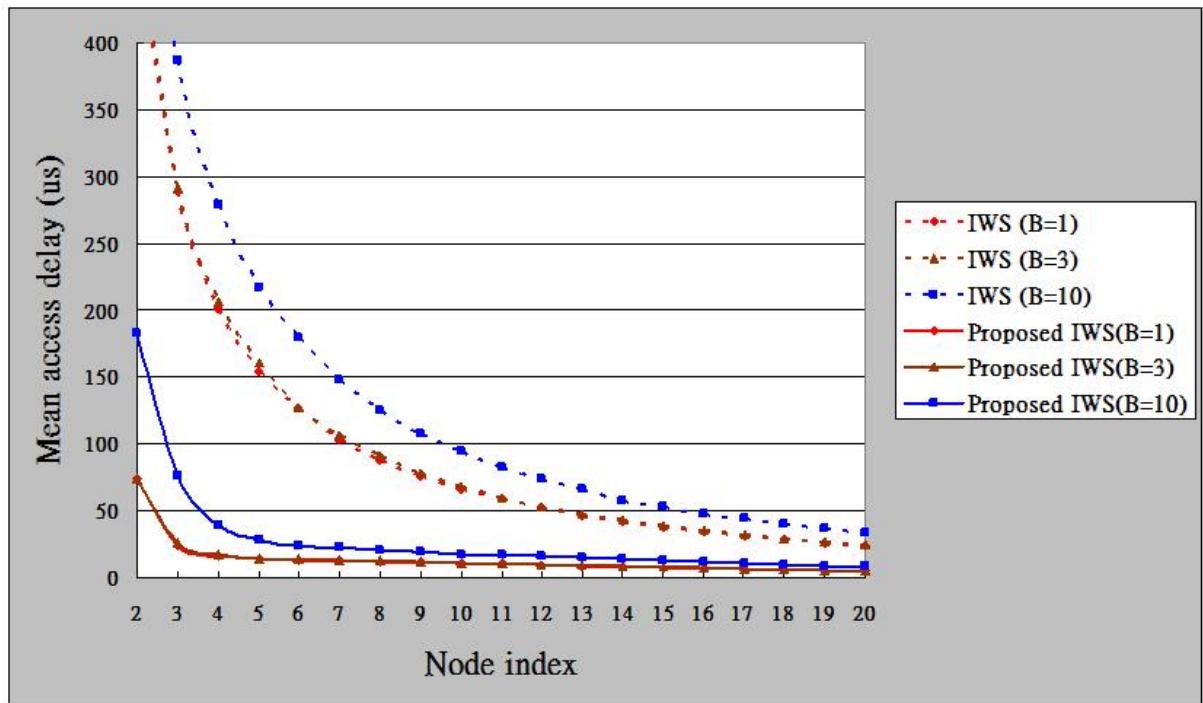

最後我們同樣考慮 case 4，也就是四個高流量節點的情況下觀察此四個節點間的 fairness 現象。[\(Figure 36-1, 36-2\)](#)

同樣如同之前在 IWS 已做過的分析，雖然其他正常流量節點原先所遭遇到的 unfair 現象已被克服，但是我們可以發現在那四個高流量節點間仍存在有 unfair 的問題待解決，亦即 node 1 較 node 4 更容易獲得 access 的機會，且同時我們去觀察此刻 mean end-to-end delay 亦因為 optical delay line 的使用導致 packet 的平均 delay 均有增加。

Fig. 36-1: Mean access delay vs node index in case 4 of unbalanced traffic

Fig. 36-2: Mean end-to-end delay vs node index in case 4 of unbalanced traffic

## Chapter 5

### Conclusions and Future Works

在這篇論文裡面我們主要著重在設計一個 MAC protocol 以便能應用在都會型單一環狀光纖網路的架構中，且主要的目的是為了解決在此環狀拓樸中所可能產生的 fairness 問題；同時在此光纖環狀網路架構下每個 node 依據 cost 的考量可為 IWS node 或是 PSS node，而我們分別針對此兩種架構提出合適的 MAC protocol 並且為了達到 all-optical 高速網路的目的，我們使用 optical delay line 的元件來達成 optical buffer 的功能並且配合此 protocol 使用。

最後由 simulation 的結果，我們亦驗證了我們所提出的 MAC protocol 確實可以解決在網路 load 不平衡狀態下所衍生的 fairness 問題。

由於我們所提出的 MAC protocol 是針對單一方向的環狀光纖網路所設計的，因此就未來的研究方面，我們可以朝如何應用於雙向光纖環狀網路以達成更高的頻寬去改進；或是就頻寬分配所可能產生的問題亦是我們可以研究的一個方向。

## Reference:

- [1] Baiocchi, A.; Carosi, M.; Listanti, M.; Pacifici, G.; Roveri, A.; Winkler, R.; “The ACCI access protocol for a twin bus ATM metropolitan area network”, *INFOCOM '90. Ninth Annual Joint Conference of the IEEE Computer and Communication Societies. 'The Multiple Facets of Integration'. Proceedings.*, IEEE, vol. 1, pp. 165 - 174, June. 1990.

- [2] Davik, F.; Yilmaz, M.; Gjessing, S.; Uzun, N.; “IEEE 802.17 resilient packet ring tutorial”, *Communications Magazine, IEEE*, vol. 42, pp. 112 – 118, Mar. 2004.

- [3] Davik, F.; Kvalbein, A.; Gjessing, S.; “Improvement of resilient packet ring fairness”, *Global Telecommunications Conference, 2005. GLOBECOM '05. IEEE*, vol. 1, Page(s):6 pp., 28 Nov.-2 Dec. 2005.

- [4] Ping Yuan; Gambiroza, V.; Knightly, E.; “The IEEE 802.17 media access protocol for high-speed metropolitan-area resilient packet rings”, *Network, IEEE*, vol. 18, Issue 3, pp. 8 – 15, May-June. 2004.

- [5] Elek, V.; Fumagalli, A.; Wedzinga, G.; “Photonic slot routing: a cost effective approach to designing all-optical access and metro networks”, *Communications Magazine, IEEE*, vol. 39, Issue 11, pp. 164 – 172, Nov. 2001

- [6] Hui Zang; Jue, J.P.; Mukherjee, B.; “Photonic slot routing in all-optical WDM mesh networks”, *Global Telecommunications Conference, 1999. GLOBECOM '99*, vol. 2, pp. 1449 – 1453, 1999

- [7] Chlamtac, I.; Elek, V.; Fumagalli, A.; Szabo, C.; “Scalable WDM network architecture based on photonic slot routing and switched delay lines”, *INFOCOM '97. Sixteenth Annual Joint Conference of the IEEE Computer*

*and Communications Societies. Proceedings IEEE*, vol. 2, pp. 769 – 776, 7-11 April 1997.

- [8] Chlamtac, I.; Elek, V.; Fumagalli, A.; Szabo, C.; “Scalable WDM access network architecture based on photonic slot routing”, *Networking, IEEE/ACM Transactions*, vol. 7, Issue 1, pp. 1 – 9, Feb. 1999.

- [9] Hui Zang; Jue, J.P.; Mukherjee, B.; “Capacity allocation and contention resolution in a photonic slot routing all-optical WDM mesh network”, *Light-wave Technology, Journal*, vol. 18, pp. 1728 – 1741, Dec 2000.

- [10] Boroditsky, M.; Lam, C.F.; Woodward, S.L.; Smiljanic, A.; Frigo, N.J.; Dreyer, K.F.; Ackerman, D.A.; Johnson, J.E.; Ketelsen, L.J.P.; Antao Chen.; “Composite packet switched WDM networks”, *Lasers and Electro-Optics Society, 2001. LEOS 2001. The 14th Annual Meeting of the IEEE*, vol. 2, pp. 738 – 739, Nov. 2001.

- [11] Boroditsky, M.; Frigo, N.J.; Lam, C.F.; Dreyer, K.F.; Ackerman, D.A.; Johnson, J.E.; Ketelsen, L.J.P.; Antao Chen; Smiljanic, A.; “Experimental demonstration of composite-packet-switched WDM network”, *Lightwave Technology, Journal*, vol. 21, pp. 1717 – 1722, Aug. 2003.

- [12] Chlamtac, I.; Fumagalli, A.; Kazovsky, L.G.; Melman, P.; Nelson, W.H.; Poggolini, P.; Cerisola, M.; Choudhury, A.N.M.M.; Fong, T.K.; Hofmeister, R.T.; Chung-Li Lu; Mekkittikul, A.; Sabido, D.J.M., IX; Chang-Jin Suh; Wong, E.W.M.; “CORD: contention resolution by delay lines”, *Selected Areas in Communications, IEEE Journal*, vol. 14, Issue 5, pp. 1014 – 1029, June. 1996.