## Novel coexisted sol-gel derived poly-Si-oxide-nitride-oxide-silicon type memory

Hsin-Chiang You, Chi-Chang Wu, Fu-Hsiang Ko, Tan-Fu Lei, and Wen-Luh Yang

Citation: Journal of Vacuum Science & Technology B 25, 2568 (2007); doi: 10.1116/1.2794327

View online: http://dx.doi.org/10.1116/1.2794327

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/25/6?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Effect of Fe incorporation on the optical behavior of ZnO thin films prepared by sol-gel derived spin coating techniques

AIP Conf. Proc. 1512, 1200 (2013); 10.1063/1.4791480

UV irradiation effect on sol-gel indium tin oxide nanopatterns replicated by room-temperature nanoimprint J. Vac. Sci. Technol. B **27**, 2805 (2009); 10.1116/1.3243167

Sol-gel-derived double-layered nanocrystal memory Appl. Phys. Lett. **89**, 252111 (2006); 10.1063/1.2416248

Appl. 1 11/3. Lett. **63**, 232111 (2000), 10.1003/1.2410240

Annealing temperature effect on the performance of nonvolatile HfO 2 Si-oxide-nitride-oxide-silicon-type flash memory

J. Vac. Sci. Technol. A 24, 682 (2006); 10.1116/1.2174021

Five-day-long ferroelectric memory effect in Pt (Bi, La) 4 Ti 3 O 12 HfO 2 Si structures Appl. Phys. Lett. **85**, 4448 (2004); 10.1063/1.1814437

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Novel coexisted sol-gel derived poly-Si-oxide-nitride-oxide-silicon type memory

Hsin-Chiang You

Institute of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

Chi-Chang Wu and Fu-Hsiang Ko<sup>a)</sup>

Institute of Nanotechnology, and Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

Tan-Fu Lei

Institute of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

Wen-Luh Yang

Department of Electronic Engineering, Feng Chia University, Taichung 407, Taiwan

(Received 22 May 2007; accepted 11 September 2007; published 11 December 2007)

The authors use a very simple sol-gel spin coating method at 900 °C and 1 min rapid thermal annealing to fabricate three different poly-Si-oxide-nitride-oxide-silicon-type flash memories. The memory windows estimated from the curve of drain current versus applied gate voltage are 3, 3.3, and 4 V for (i) HfO<sub>2</sub> thin film, (ii) hafnium silicate nanocrystal, and (iii) coexisted hafnium silicate and zirconium silicate nanocrystal memory, respectively. Together with the measurement from gate disturbance and drain disturbance on these fabricated devices, the coexisted nanocrystal devices exhibit better reliability than both the thin film type memory and single nanocrystal type memory. © 2007 American Vacuum Society. [DOI: 10.1116/1.2794327]

### I. INTRODUCTION

Conventional flash memory devices use a floating gate structure and charge is stored in a polysilicon floating gate. However, when the tunneling oxide is below 85 nm, a floating gate structure faces scaling issues.<sup>2</sup> The stored charge can leak due to defects in the tunneling oxide formed by repeated program/erase cycles. Therefore, discrete trap memory devices such as thin film poly-Si-oxide-nitride-oxide-silicon (SONOS) or nanocrystal-based memories are widely studied to replace the floating gate structure for semiconductor memory applications.<sup>3–7</sup> The charge trapping layer of traditional SONOS memory is silicon nitride (Si<sub>3</sub>N<sub>4</sub>). High-K materials such as HfO2 or ZrO2 thin films are considered as charge storage material to achieve the faster programing speed and better charge retention performance. SONOS high-K memory encounters the electron migration problem in the charge trapping layer,<sup>5</sup> and this effect will cause the charge loss and degrade the charge retention performance during memory operation. The nanocrystal memory can keep the trapped charge tightly to avoid the charge loss problem of SONOS memory and also achieve the advantages such as fast program/erase speed, low programing voltage, and good endurance.<sup>8,9</sup> Hence, the device reliability would be significantly enhanced.

Numerous technologies have been developed recently for the preparation of various high-*K* films. To prepare insulating thin films, atomic layer deposition (ALD), physical vapor deposition (PVD), and chemical vapor deposition (CVD) methods have all been used to prepare films for new technologies. <sup>10–12</sup> The sol-gel method is a very interesting

simple preparing technique for ceramic films.<sup>13</sup> The sol-gel method can provide colloidal solvents or precursor compounds when metal halides are hydrolyzed under controlled conditions. In the sol-gel process, hydrolysis, condensation, and polymerization steps occur to form metal oxide networks. These reactions play significant roles in modifying the final material's properties. The most interesting feature of sol-gel processing is its ability to synthesize various types of materials that are known as "inorganic-organic hybrids." The film preparation with spin coating is a more simple method than ALD, PVD, or CVD due to its simpler operation, cheaper precursor, and lower tool price. In addition, the film can be fabricated in an atmospheric pressure system instead of a complex high vacuum system.

Regarding device reliability, there also arises a challenge as the flash memory is repeatedly programed and erased. The memory will be degraded as if the device suffers from the formation of a new defect during the applied voltage. In addition, the developed flash memory is designed as an array for regular operation. The continuous stressing on the device of interest may influence the performance of surrounding devices. Therefore, the flash memory also needs to check the gate disturbance and drain disturbance to ensure the fabrication reliability.<sup>14</sup>

In this article, we develop the sol-gel spin coating method and annealing technique to fabricate three SONOS-type flash memories: (i) 10 nm  $HfO_2$  thin film, (ii)  $HfSi_xO_y$  nanocrystal, and (iii) coexisted  $HfSi_xO_y$  and  $ZrSi_xO_y$ . The performance of the drain current versus applied gate voltage, gate disturbance, and drain disturbance is conducted to evaluate the device reliability.

a)Electronic mail: fhko@mail.nctu.edu.tw

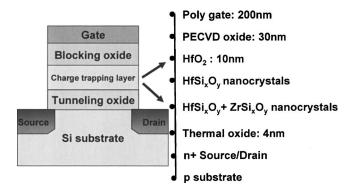

Fig. 1. Schematic diagram of the SONOS-type memory device structure with spin-coated sol-gel charge trapping layers.

#### II. EXPERIMENT

We separately prepared HfCl<sub>4</sub> (99.5%, Aldrich, St. Louis, MO), ZrCl<sub>4</sub> (99.5%, Aldrich, St. Louis, MO), and SiCl<sub>4</sub> (99.5%, Aldrich, St. Louis, MO) as precursors and dissolved into isopropanol (IPA, Fluka, water content <0.1%) solvent to fabricate three sol-gel solutions for high-*K* films and nanocrystals. The first device with 10 nm HfO<sub>2</sub> thin film used the HfCl<sub>4</sub> sol-gel solution.<sup>15</sup> The second device used the coexisted HfCl<sub>4</sub> and SiCl<sub>4</sub> sol-gel solutions to prepare the initial thin film.<sup>16</sup> The film will be transferred into 5 nm HfSi<sub>x</sub>O<sub>y</sub> nanocrystals in the subsequent annealing step. The third device was prepared by mixing the three sol-gel solutions of HfCl<sub>4</sub>, ZrCl<sub>4</sub>, and SiCl<sub>4</sub> to the initial thin film, and then transferred into coexisted 5 nm nanocrystals by the subsequent annealing.<sup>17</sup>

The structure of the fabricated devices is shown in Fig. 1. The fabrication of sol-gel spin coating nanocrystal memory is started with local oxidation of Si process on p-type (100) 150 mm silicon substrate. At the beginning, a 4 nm tunneling oxide was thermally grown at 925 °C in a furnace. The thin film was deposited by spin coating at 3000 rpm for 60 s at ambient temperature (25 °C). The spin coater used was TEL Clean Track model-MK8 (Japan). After spin coating, the wa-

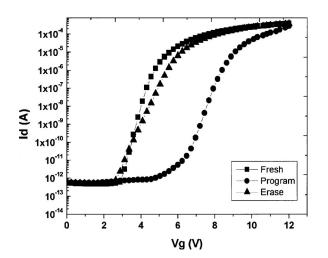

Fig. 2.  $I_d$ - $V_g$  curve of SONOS-type memory from 10 nm  ${\rm HfO_2}$  thin film fabrication.

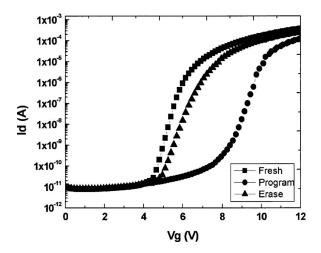

Fig. 3.  $I_d$ – $V_g$  curve of SONOS-type memory from  $HfSi_xO_y$  array nanocrystals fabrication.

fer was rapid thermal annealed (RTA) at 900 °C for 60 s in O<sub>2</sub> ambient to form the memories with (i) HfO<sub>2</sub> layer, (ii) HfSi<sub>x</sub>O<sub>y</sub> nanocrystal, and (iii) coexisted HfSi<sub>x</sub>O<sub>y</sub> and ZrSi<sub>x</sub>O<sub>y</sub> nanocrystals, respectively. The 30-nm-thick blocking oxide was deposited by low pressure chemical vapor deposition (LPCVD) tetra-ethyl-ortho-silicate (TEOS) followed by 200 nm poly-Si gate deposition. After the LPCVD TEOS deposition, the TEOS oxide is densified in N<sub>2</sub> ambient at 900 °C for 30 s. Finally, gate pattering, source/drain implant, and the rest of the subsequent complementary metal oxide semiconductor processes were used to fabricate this SONOS-type memory.

#### III. RESULTS AND DISCUSSION

The drain current with respect to the applied gate voltage for the fabricated devices is demonstrated in Figs. 2–4. The HfO<sub>2</sub> thin film SONOS-type memory in Fig. 2 is measured by channel hot electron injection for programming and band to band tunneling induced hot hole injection for erasing. The

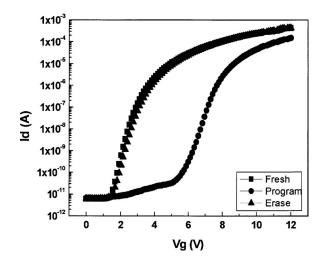

Fig. 4.  $I_d$ - $V_g$  curve of SONOS-type memory from the coexisted  $HfSi_xO_y$  and  $ZrSi_xO_y$  array nanocrystals fabrication.

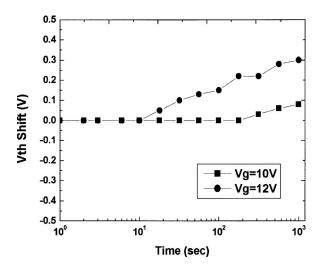

Fig. 5. Gate disturbance of memory fabricated by 10 nm HfO<sub>2</sub> thin film.

programming condition is operated at  $V_g$  (gate voltage) = 15 V and  $V_d$  (drain voltage) = 10 V for 10 ms, while the erasing condition is operated at  $V_g$ =-10 V and  $V_d$ =10 V for 1 s. The memory window of this device is about 3 V at the drain current of  $10^{-8}$  A. In the  $\mathrm{HfSi}_x\mathrm{O}_y$  nanocrystal memory, the memory window from drain current versus gate voltage in Fig. 3 is estimated to 3.3 V at the drain current of  $10^{-8}$  A. This observation suggests that the nanocrystal type memory operates better than the thin film SONOS-type memory. The nanocrystal memory can trap more charge carriers, and therefore exhibits the better memory window. This increased performance can promote the reliability of the memory.

Instead of the single type of nanocrystals in Fig. 3, the memory in Fig. 4 is fabricated with two types of nanocrystals (i.e.,  $HfSi_xO_y$  and  $ZrSi_xO_y$ ). The memory window is about 4 V at the drain current of  $10^{-8}$  A. This SONOS-type memory with coexisted nanocrystals has the largest  $V_{th}$  shift compared to the memories with  $HfO_2$  film or  $HfSi_xO_y$  nanocrystal due to more nanocrystals in the charge trapping layer. The observation from Figs. 3 and 4 suggests that the formation of nanocrystals for the memory's charge program/erase is an effective way of improving the device reliability.

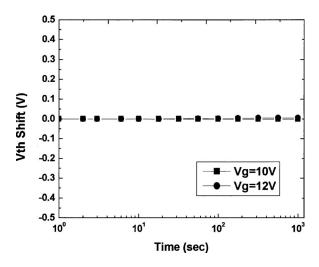

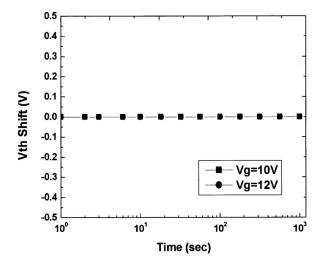

The gate disturbance for the fabricated three devices is illustrated in Figs. 5–7. We measure the erased state for these devices and apply the  $V_g = 10$  or 12 V with the drain, source, and substrate grounded. In Fig. 5, the threshold voltage shift  $(V_{th})$  for  $V_g = 10$  V remains constant for 1–200 s, and gradually increases for 200–1000 s. Interestingly, the device  $V_{\rm th}$ shift for  $V_g = 12$  V is observed at 10 s and  $V_{th}$  shift=0.3 V at 1000 s. The HfO<sub>2</sub> thin film device is easily degraded during gate biasing. In the regular memory operation, the unstable  $V_{\rm th}$  shift will induce the loss of data storage. On the contrary, the SONOS-type memories fabricated by nanocrystal processing have very stable  $V_{\rm th}$  shift for gate stressing at 10 or 12 V in Figs. 6 and 7. This is because the nanocrystal is surrounded by SiO<sub>2</sub>, and this increases the equivalent tunneling oxide thickness. When the tunneling oxide thickness is increased, the electrons in the substrate are less able to tunnel to the nanocrystal by Fowler-Nordheim tunneling operation.

Fig. 6. Gate disturbance of memory fabricated by  $HfSi_xO_y$  array nanocrystals.

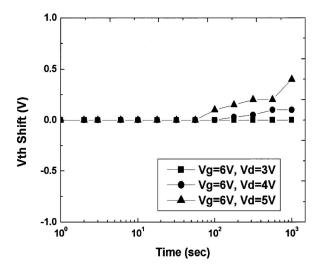

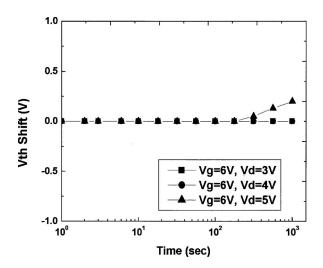

The drain disturbance measurement for these devices is depicted in Figs. 8–10. We measured the erased state for these devices, and applied the  $V_g$ =6 V at various drain voltages of 3, 4, and 5 V, respectively. In Fig. 8 for the HfO<sub>2</sub> thin film memory, the curve for  $V_d$ =3 V remains constant at 1 to 1000 s. The increase of  $V_{th}$  shift is observed at 60 and 100 s for the drain voltages of 5 and 4 V, respectively. In Fig. 9 for the HfSi<sub>x</sub>O<sub>y</sub> nanocrystal memory, the curves for drain voltages of 3 and 4 V also remain constant from 1 to 1000 s. The increase of  $V_{th}$  shift is only observed for 200 s for the drain voltages of 5 V.

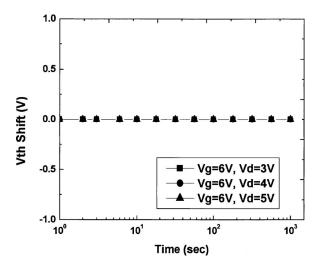

The coexisted nanocrystals in Fig. 10 indicates that the  $V_{\rm th}$  for all three drain stressing voltages is very stable. Hence, the coexisted hafnium silicate and zirconium silicate nanocrystal memory devices have better electrical performance than the  ${\rm HfO_2}$  thin film type or  ${\rm HfSi_xO_y}$  nanocrystal type. This phenomenon is also attributed to the surrounding effect of  ${\rm SiO_2}$  mentioned above. The equivalent tunneling oxide thickness is increased after nanocrystal formation. When the tunneling

Fig. 7. Gate disturbance of memory fabricated by coexisted  $HfSi_xO_y$  and  $ZrSi_xO_y$  array nanocrystals.

Fig. 8. Drain disturbance of memory fabricated by 10 nm  $HfO_2$  thin film.

oxide thickness is increased, the electrons in the substrate are less able to tunnel to and to be trapped in the nanocrystal. This observation also suggests that the formation of nanocrystals is an effective way of enhancing the device reliability. The coexisted hafnium silicate and zirconium silicate nanocrystal memory devices with higher density of nanocrystals demonstrate the best reliability.

### **IV. CONCLUSIONS**

In this article, we use a sol-gel spin coating method to fabricate three types of flash memories from (i)  $HfO_2$  thin film, (ii) hafnium silicate nanocrystal, and (iii) coexisted hafnium silicate and zirconium silicate nanocrystal memory. We have verified the device performance with drain current versus applied gate voltage, gate disturbance, and drain disturbance measurements. The quality of the coexisted hafnium silicate and zirconium silicate nanocrystals formed by the sol-gel spin coating method and RTA treatment exhib-

Fig. 9. Drain disturbance of memory fabricated by  $\mathrm{HfSi}_x\mathrm{O}_y$  array nanocrystals.

Fig. 10. Drain disturbance of memory fabricated by coexisted  $HfSi_xO_y$  and  $ZrSi_xO_y$  array nanocrystals.

its better reliability in terms of broad memory window due to more trapping sites. In addition, the memory fabricated by the coexisted hafnium silicate and zirconium silicate nanocrystals has better gate and drain disturbance due to the contribution of surrounding  ${\rm SiO}_2$  to increase the equivalent tunneling oxide thickness.

#### **ACKNOWLEDGMENTS**

This research was financially supported by the Ministry of Education "Aim for the Top University" program, and we thank the National Nano Device Laboratories through Contract No. NDL-95S-C130.

<sup>1</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices **49**, 1606 (2002).

<sup>2</sup>B. D. Salvo *et al.*, IEEE Trans. Device Mater. Reliab. **4**, 377 (2004).

<sup>3</sup>Y.-N. Tan, W.-K. Chim, B. J. Cho, and W.-K. Choi, IEEE Trans. Electron Devices **51**, 1143 (2004).

<sup>4</sup>K. K. Yadavalli, N. R. Anderson, T. A. Orlova, A. O. Orlov, G. L. Snider, and J. Elam, J. Vac. Sci. Technol. B 22, 3119 (2004).

<sup>5</sup>T. Sugizaki et al., VLSI Tech. Symp. **2003**, 27.

<sup>6</sup>X. Wang and D. L. Kwong, IEEE Trans. Electron Devices **53**, 78 (2006). <sup>7</sup>I. H. Cho, T.-S. Park, J. D. Choe, H. J. Cho, D. Park, H. Shin, B.-G. Park,

J. D. Lee, and J.-H. Lee, J. Vac. Sci. Technol. B **24**, 1266 (2006).

<sup>8</sup>M. She and T. J. King, IEEE Trans. Electron Devices **50**, 1934 (2003).

<sup>9</sup>M. Takata, S. Kondoh, T. Sakaguchi, H. Choi, J.-C. Shim, H. Kurino, and M. Koyanagi, Tech. Dig. - Int. Electron Devices Meet. 2003, 553.

<sup>10</sup>S. X. Lao, R. M. Martin, and J. P. Chang, J. Vac. Sci. Technol. A 23, 488 (2005).

<sup>11</sup>W.-L. Yang, T.-S. Chao, S.-C. Chen, C.-H. Yang, and W.-C. Peng, Jpn. J. Appl. Phys., Part 1 45, 6902 (2006).

<sup>12</sup> J. P. Chang, Y.-S. Lin, and K. Chu, J. Vac. Sci. Technol. B 19, 1782 (2001)

<sup>13</sup>E. S. González, P. Miranda, A. D. Parralejo, A. Pajares, and F. Guiberteau, J. Mater. Res. 20, 1544 (2005).

<sup>14</sup>Y.-H. Lin, C.-H. Chien, T.-H. Chou, T.-S. Chao, and L.-F. Lei, IEEE Electron Device Lett. 28, 267 (2007).

<sup>15</sup>H.-C. You, T.-H. Hsu, F.-H. Ko, J.-W. Huang, W.-L. Yang, and T.-F. Lei, IEEE Electron Device Lett. 27, 653 (2006).

<sup>16</sup>H.-C. You, T.-H. Hsu, F.-H. Ko, J.-W. Huang, and T.-F. Lei, IEEE Electron Device Lett. 27, 644 (2006).

<sup>17</sup>F.-H. Ko, H.-C. You, and T.-F. Lei, Appl. Phys. Lett. **89**, 252111 (2006).