# A Coupled-Simulation-and-Optimization Approach to Nanodevice Fabrication With Minimization of Electrical Characteristics Fluctuation

Yiming Li, Member, IEEE, and Shao-Ming Yu, Student Member, IEEE

Abstract—In this paper, a simulation-based optimization methodology for nanoscale complementary metal-oxide-semiconductor (CMOS) device fabrication is advanced. Fluctuation of electrical characteristics is simultaneously considered and minimized in the optimization procedure. Integration of device and process simulation is implemented to evaluate device performances, where the hybrid intelligent approach enables us to extract optimal recipes which are subject to targeted device specification. Production of CMOS devices now enters the technology node of 65 nm; therefore, random-dopant-induced characteristic fluctuation should be minimized when a set of fabrication parameters is suggested. Verification of the optimization methodology is tested and performed for the 65-nm CMOS device. Compared with realistic fabricated and measured data, this approach can achieve the device characteristics; e.g., for the explored 65-nm n-type MOS field effect transistor, the on-state current >0.35 mA/ $\mu$ m, the off-state current < 1.5e - 11 A/ $\mu$ m, and the threshold voltage = 0.43 V. Meanwhile, it reduces the threshold voltage fluctuation ( $\sigma_{\rm vt\,h}~\sim~0.017$  V). This approach provides an alternative to accelerate the tuning of process parameters and benefits manufacturing of nanoscale CMOS devices.

Index Terms—Characteristics fluctuation, complementary metal—oxide-semiconductor (CMOS) fabrication, device simulation, modeling, nanodevices, optimization, process recipe, process simulation, simulation, technology computer-aided (TCAD) design.

#### I. INTRODUCTION

To pursue high-performance complementary metal-oxide-semiconductor (CMOS) devices for circuit designs, semiconductor manufacturing companies and foundries have to fabricate devices with different specifications. For example, logic, analog, and memory designs may require high threshold voltage, high speed, and low-power devices. Process and device engineers experimentally split

Manuscript received January 30, 2007; revised May 30, 2007. This work was presented at the 2006 IEEE Conference on Nanotechnology, Cincinnati, OH, July 2006. This work was supported in part by the National Science Council of Taiwan under Contract NSC-95-2221-E-009-336, Contract NSC-95-2752-E-009-003-PAE, Contract NSC-96-2221-E-009-210, Contract NSC-96-2752-E-009-003-PAE, and by the Ministry of Education (MoE) Aim for the Top University and Elite Research Center Development Plan (ATU) Program under a 2006-2007 grant, and by the Taiwan Semiconductor Manufacturing Company under a 2006-2008 grant.

Y. Li is with the Department of Communication Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymli@faculty.nctu.edu.tw)

S.-M. Yu is with the Department of Computer Science, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

Color versions of some of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TSM.2007.907623

the process conditions, such as channel and source/drain implantations, and fabricate test samples in developing the required process modules. This empirical approach directs the engineer to realistic devices. However, as dimensions of metal-oxide-semiconductor field effect transistors (MOSFETs) enter the sub-65-nm era [1]-[5], proper use of computer simulation-and-optimization-aided manufacturing techniques can reduce the number of test runs. Diverse simulation and optimization methods including statistical schemes have been reported in optimal fabrication of CMOS devices [3], [6]-[13], [19], [21]-[25]. The conventional methods use design of experiments (DOE) and external simulations to generate the response surface model (RSM) and then analyze the statistical variation of process parameters to perform optimization of manufacturing process; these methods have their advantages [7]–[10], [23]. Fluctuation of electrical characteristics is evident in sub-65-nm technology [12]-[15], [21], [22]. Therefore, it will be a crucial investigation if the random-dopant-induced characteristics fluctuation can be simultaneously minimized in the solution procedure of the simulation-based optimization methodology.

In this paper, we implement a technology computer-aided design (TCAD) simulation-based optimization methodology for nanoscale CMOS device fabrication. The TCAD simulation integrates two-dimensional (2-D) process simulation and device simulation. Threshold voltage fluctuations resulting from process variation effects and random dopant-induced effects should be taken into consideration and minimized in the optimization process. Here, we focus on the latter. The 2-D TCAD simulation is sequentially performed to evaluate device performance using the hybrid intelligent approach [17]-[20] which enables us to extract optimal recipes subject to designed device specifications. The hybrid optimization is mainly based on evolutionary computational techniques, numerical optimization methods, and expertise knowledge. The process simulation focuses on device structure and doping profile simulation. Next, the density-gradient-based drift-diffusion model is solved for device simulation [16], [26]-[28]. Finally, a quantum correction model is solved by perturbation and monotone iterative methods to estimate the random dopant-induced fluctuations [11], [12], [21], [22]. The developed prototype environment not only can integrate in-house developed simulation programs, but also provides a flexible interface to well-known TCAD software. Verification of the proposed computational methodology is performed on 65-nm CMOS devices. For a 65-nm n-type MOSFET, the on-state current >0.35 mA/ $\mu$ m, the off-state current < 1.5e - 11 A/ $\mu$ m, the threshold voltage = 0.43 V, and

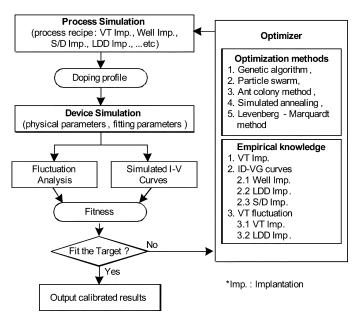

Fig. 1. Working flow of implement methodology for reverse modeling problem in tuning fabrication parameters.

the threshold voltage fluctuation  $\sigma_{\rm vth}\sim 0.017~{\rm V}$  are adopted as targets to be achieved. Optimized recipes are automatically suggested then compared with realistic fabricated and measured data until results meet the device performance within a specified tolerance.

This paper is organized as follows. In Section II, we briefly describe the proposed coupled simulation-optimization methodology and architecture of the implemented prototype. In Section III, the experimental and theoretical calculated results are reported to show the robustness of the method. Finally, we draw conclusions and suggest future work.

# II. SIMULATION-OPTIMIZATION METHODOLOGY

As shown in Fig. 1, a flowchart of the simulation-based optimization methodology illustrates the sequence of process and device simulations [1], [2], [11], [16], [24]-[28], fluctuation analysis [12], [13], [21], [22], and a hybrid optimization kernel [17]–[20]. For a given device specification, such as the onand off-state currents and the threshold voltage, the simulator searches out a set of optimal settings to fit the prescribed target and then estimates the variation of the threshold voltage accordingly. Starting from an initial process recipe, we apply 2-D process simulation to generate the corresponding device structure and doping profile. Together with device parameters and physical models, they are used in the 2-D device simulation to obtain the preliminary results. If we include the random-dopant-induced characteristics fluctuation, we pass the physical results to perform the fluctuation analysis by solving the quantum correction model with perturbation and monotone iterative methods. At the same time, we calculate the error between the simulated result and the target to get the fitness (or the cost function). When the stopping tolerance is met, the solution procedure is terminated and the final results are output. Otherwise, the hybrid optimization is enabled to do the evolutionary searching process with respect to several specified constraints. The refined fabrication conditions as well

as the physical model parameters are then used as inputs to the process simulation and device simulation is repeated. The iteration between the TCAD simulation and optimization is terminated when the simulated device's specification and the correspondingly computed tolerance of characteristic fluctuation meet the target. We note that to automatically search for the optimal recipes for device fabrication, the problem is now treated as a reverse modeling problem, which is a multidimensional minimization problem. It minimizes the errors between the specified (or measured) physical (and electrical) characteristics and the simulated results. The dimension of the optimization problem depends upon how many parameters are to be optimized; in general, it is about 30 process and device parameters. For ultra-small devices, 3-D simulation should be considered to account for the geometry effect.

The developed evolutionary system for the semiconductor device fabrication contains two independent parts, the evolutionary core kernel and the external simulation programs, shown in Fig. 1. The former part mainly uses evolutionary algorithms, such as the genetic algorithm and the particle swarm method incorporated with other numerical optimization techniques [19]. The external programs consist of the codes for device simulation and process simulation which can be replaced with any existing TCAD software. During the iterative procedure, the optimizer computes the fitness score for each setting (i.e., the process recipe) through a fitness function. The fitness function measures the error between simulated and target characteristics and the fluctuation of threshold voltage. The fitness function used in this paper is

$$\begin{split} \text{fitness} &\equiv \text{weight}_{\text{ID}} \left( \frac{\log(I_D) - \log\left(I_D^{\text{target}}\right)}{\log(I_D^{\text{target}})} \right) \\ &+ \text{weight}_{\sigma \text{vth}} \left( \frac{\sigma_{\text{vth}}}{V_T} \right) \end{split} \tag{1}$$

where  $I_D$  means the simulated data, the  $I_D^{\mathrm{target}}$  is the specified target to be achieved, and  $\sigma_{\rm vth}$  is the fluctuation of the threshold voltage  $(V_T)$ , weight<sub>ID</sub> and weight<sub> $\sigma vth$ </sub> are the weighted value for the I-V curves and  $\sigma_{\rm vth}$ , respectively. In our paper, we set weight<sub>ID</sub> = weight<sub> $\sigma vth$ </sub> = 1, which means that the device performance and the fluctuation of the threshold voltage have the same weight. However, it can be adjusted according to different design purposes. To retrieve the simulated physical characteristics including I-V curves, the optimizer sends the setting to be evaluated to the external process and device simulation programs, and the external programs perform the simulations and generate the I-V curves. Physical-based empirical knowledge embedded in the evolutionary core kernel defines the relationship of the parameters and the device characteristics. According to engineering observation, parameters to be optimized are grouped into two categories, one is process related and the other is device related. The former part plays the important role of determining a device's preliminary characteristics. The I-V curves are physically divided into the linear, the off-state, and the saturation regions. We first optimize process-related parameters by minimizing errors between simulation and target in the linear and off-state regions. To achieve error minimization, parameters relating to implantations of V<sub>T</sub>, well, lightly doped drain (LDD), and source/drain are first computed simultaneously, allowing an accurate threshold voltage to be obtained. In the evolutionary part of the procedure, parameters coupled to band-to-band tunneling and saturation velocity are taken into consideration [16], [29]-[31]. Otherwise, parameters may possess unreasonable physical meanings, and then the optimization becomes meaningless. By minimizing errors in the saturation and off-state regions, device-related parameters are optimized with respect to the mobility model, band-to-band tunneling model, and saturation velocity [16], [29]–[31]. To reduce the fluctuation of the threshold voltage, we focus on V<sub>T</sub> and LDD implantations. Finally, if necessary, the linear, off-state, and saturation regions are simultaneously optimized one more time. The optimization is terminated when errors are minimized for all I-V curves. We note that the device performance, in particular, for V<sub>T</sub> and the linear region of I-V curves, is significantly dominated by process-related parameters. Therefore, we put emphasis on the linear region and then the saturation region of I-V curves in the optimization procedure. During the optimization procedure, once a larger error within a certain region of I-V curves is observed, an empirical rule is employed to destroy the evolution, which may result in different mutation and is useful in the iteration loop of simulation and optimization.

For device-related parameters, the mobility models used in the device simulation, according to Mathiessen's rule [16], consist of the following three parts. 1) The surface contribution due to acoustic phonon scattering

$$\mu_{\text{surf\_aps}} = \frac{B}{E} + \frac{C(N_i/N_0)^{\lambda}}{E^{1/3}(T/T_0)^K}$$

(2)

where  $N_i = N_A + N_D$ ,  $T_0 = 300$  K and E is the transverse electric field normal to the interface of semiconductor and insulator. 2) The contribution attributed to surface roughness scattering

$$\mu_{\text{surf\_aps}} = \left(\frac{(E/E_{\text{ref}})^{\Xi}}{\delta} + \frac{E^3}{\eta}\right)^{-1} \tag{3}$$

where

$$\Xi = A + \frac{\alpha \cdot (n+p)N_{\text{ref}}^{v}}{(N_i + N_1)} \tag{4}$$

and  $E_{\rm ref}$  is a reference electric field,  $N_{\rm ref}$  is a reference doping concentration. 3) The bulk mobility

$$\mu_{\text{bulk}} = \mu_L \left(\frac{T}{T_0}\right)^{-\zeta} \tag{5}$$

where  $\mu_L$  is the mobility due to bulk phonon scattering and T is lattice temperature. For the saturation velocity, we use

$$V_{\rm sat} = V_{\rm sat0} \left(\frac{T}{T_0}\right)^{V_{\rm sat1}}.$$

(6)

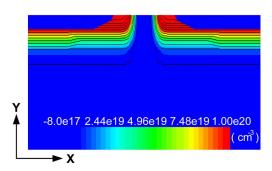

Fig. 2. Initial doping profile for explored 65-nm N-MOSFET.

Details of the mobility models and coefficients are described in [16], [29], and [30]. For the band-to-band tunneling, we used the model reported in [31]. Generally, the number of parameters to be optimized depends upon the device parameters selected in the TCAD simulation and the process-related parameters that directly affect the device structure and doping profile. From empirical knowledge, we especially investigate the parameters for  $V_{\mathrm{T}}$ , LDD, and well implantations due to their significance in the threshold voltage and the linear region of the I-V curves. Moreover, the V<sub>T</sub> and LDD implantations are crucial when considering the random-dopant-induced characteristics fluctuation. We also adjust the mobility and saturation velocity parameters in the device simulation for fine-tuning the I-V curves. This study is mainly based upon our recent work on a unified optimization framework (UOF), where the developed open-source project UOF is available in the public domain [32]–[34].

### III. RESULTS AND DISCUSSION

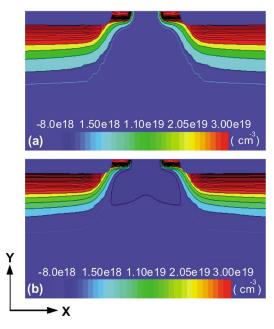

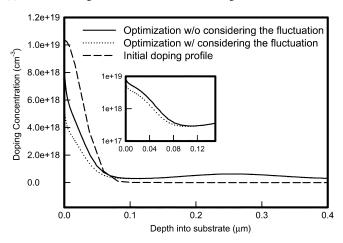

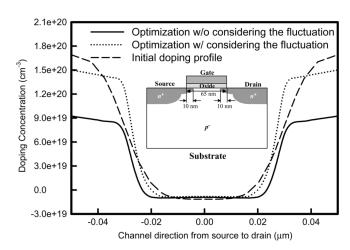

In this section, the optimized parameters for on-target fabrication of the 65-nm CMOS devices will be investigated. For the sake of simplicity, we focus on the results of the 65-nm N-MOSFET. The device characteristics and the fluctuation tolerance of the threshold voltage are summarized in column 2 of Table I. In this investigation, the on- and off-state currents, the threshold voltage as well as the device's fluctuation tolerance have been optimized simultaneously. With these four physical constraints, the coupled simulation and optimization methodology was self-consistently performed with the specified fitness function. The initial doping profile used in the optimization procedure is shown in Fig. 2. The simulated doping of the optimized device, both with and without the reduction of the threshold voltage fluctuation, are shown in Fig. 3(a) and (b), respectively. Fig. 4 shows a 1-D section in the center of the device channel of the 2-D doping profile distributions shown in Figs. 2 and 3. It can be observed that the minimization of the threshold voltage fluctuation (dotted line) results in a lower doping level compared with the optimization without consideration (dashed line). This optimization automatically achieved the target parameters and confirms the studies reported in [13], [21], and [22]. Fig. 5 shows the horizontal doping profile 2 nm below the channel surface between the source and drain. Together with the results, shown in Fig. 4, the higher doping level along the channel for the device, when the threshold voltage fluctuations were also optimized, maintains the same device characteristics as the one where dopant fluctuations were not considered.

Fig. 3. Optimized 65-nm N-MOSFET doping profile for device (a) without and (b) with considering minimization of threshold voltage fluctuation.

Fig. 4. Optimized doping profiles from channel surface deep into substrate. The 1-section is located at center of device channel (x=0).

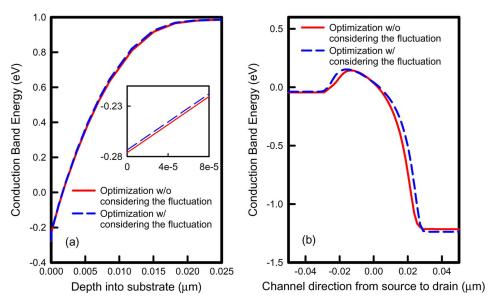

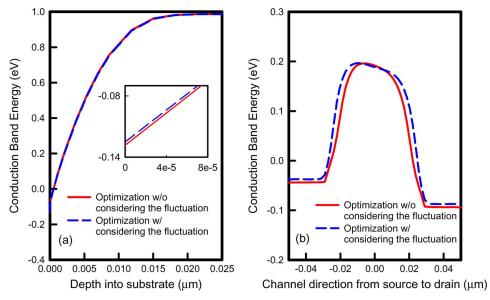

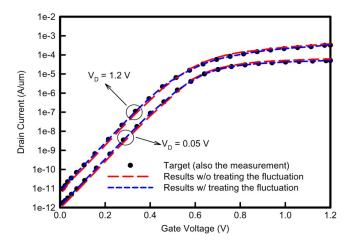

The results of the optimized 65-nm N-MOSFET are summarized in Table I. If the threshold voltage fluctuation minimization is not be activated in the optimization, there is a 6.7% threshold voltage fluctuation, which significantly shifts the process away from the design window (3.89%). The band profiles for the devices in the on- and off-states are shown in Figs. 6(a) and 7(a) for both of the optimization cases. The optimization without minimization of the threshold voltage fluctuation has a little bit lower band edge than its counterpart due to a higher doping level [Figs. 6(a) and 7(a)]. Figs. 6(b) and 7(b) once again show the horizontal profile along channel for both optimization cases. For the optimization without minimization of fluctuation, both the on- and off-state bands (2 nm below the channel surface) are lower than that the optimization minimizing the fluctuations. Both the specified target and the optimized results are shown in Fig. 8. The results with and without considering the threshold voltage fluctuation are very close to the specified target. Nevertheless, the strategy of including the reduction of threshold voltage fluctuation successfully reduced

Fig. 5. Doping profile from source to drain along channel direction 2 nm below interface between gate oxide and silicon substrate. Inset of figure shows structure of optimized 65-nm N-MOSFET.

TABLE I

COMPARISON LIST OF ACHIEVED RESULTS WITH RESPECT TO TWO DIFFERENT

EXTRACTIONS. TARGET SPECIFICATION IS ADOPTED FROM REALISTIC

FABRICATED AND MEASURED DATA

|                                     | Target to be | Result without $\sigma_{vth}$ | Result with $\sigma_{vth}$ |

|-------------------------------------|--------------|-------------------------------|----------------------------|

|                                     | achieved     | reduction                     | reduction                  |

| Ion (mA/µm)                         | > 0.35       | 0.35                          | 0.39                       |

| Ioff (A/μm)                         | < 1.5e-11    | 1.05e-11                      | 1.13e-11                   |

| $V_{th}(V)$                         | ~0.436       | 0.442                         | 0.432                      |

| $\sigma_{\text{vth}}\left(V\right)$ | ~0.017       | 0.03                          | 0.014                      |

| $\sigma_{vth}/V_{th}$ (%)           | 3.89         | 6.78                          | 3.24                       |

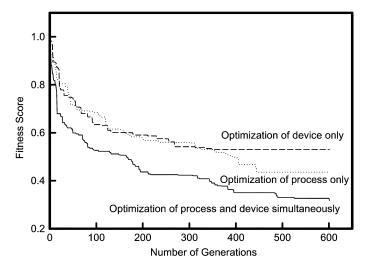

the threshold voltage fluctuation and is shown in Table I. A list of the process recipe and device parameters used for simulation, and the extracted parameters, with and without fluctuation reduction, are summarized in Table II. It can be noted that there is a major difference between the core  $V_{\rm T}$  implantation and the result with and without  $\sigma_{\rm Vth}$  reduction. To verify the efficiency of the proposed method, three examinations are performed on our PC-based Linux cluster system with 16 CPUs [24], [25]. The fitness score versus the number of evolutionary generations is shown in Fig. 9. For the given target, it shows that the methodology with simultaneously considering the parameters of the process and device physics provides better computational efficiency.

## IV. CONCLUSION

A coupled TCAD-simulation-based optimization algorithm has been implemented and applied to fabrication optimization of the 65-nm CMOS devices. Fluctuations in the solution procedure are induced, which enables us to search out the optimum recipe for minimization of the threshold voltage fluctuation. Reducing the doping level in the device channel suppresses the threshold voltage fluctuation; but, it also modifies the device performance. This difficulty is one of the important issues in developing reliable fabrication technique in semiconductor foundries. In this example, both the threshold voltage implant and LDD implant are automatically optimized at the same time. Our investigation shows that to meet the goal discussed in Table I of Section III, the LDD dopant should be increased in the source and drain, and the concentration of the threshold

Fig. 6. Plots of band profile for optimization with and without considering threshold voltage fluctuation under on-state. (a) Surface to the substrate. (b) Along channel direction from source to the drain, which is about 2 nm below channel surface.

Fig. 7. Plots of band profile for optimization with and without considering threshold voltage fluctuation under off-state. (a) Surface to substrate. (b) Channel direction from source to drain which is about 2 nm below channel surface.

Fig. 8. Achieved accuracy of extracted I-V curves for explored 65-nm N-MOSFET.

TABLE II

LIST OF PROCESS RECIPE AND DEVICE PARAMETERS FOR DEVICE

OPTIMIZATION W/ AND W/O CONSIDERING FLUCTUATION REDUCTION

| Parameters          | Parameters Range                                | Result w/o σ <sub>vth</sub> reduction | Result w/ $\sigma_{vth}$ reduction |

|---------------------|-------------------------------------------------|---------------------------------------|------------------------------------|

| Core V <sub>T</sub> | Energy: 20~80 KeV                               | 58                                    | 24                                 |

| implantation        | Dose: 1e12~2e13 cm <sup>-2</sup>                | 2.7e12                                | 1.3e13                             |

| N-LDD               | Energy: 10~50 KeV                               | 28                                    | 29                                 |

| implantation        | Dose: 1e13~5e13 cm <sup>-2</sup>                | 3.1e13                                | 3.8e13                             |

| P-WELL              | Energy: 200~400 KeV                             | 250                                   | 250                                |

| implantation        | Dose: 1e13~4e13 cm <sup>-2</sup>                | 2.4e13                                | 2.4e13                             |

| Mobility            | B: 2e7~8e7 cm/s                                 | 3.5e7                                 | 3.41e7                             |

| model               | C: $100 \sim 500 \text{ cm}^{5/3} / (V^{2/3}S)$ | 160                                   | 170                                |

| Velocity            | V <sub>sat0</sub> : 1e6~1e8 cm/s                | 9e6                                   | 9e6                                |

| saturation          | V <sub>sat1</sub> : 0.5~1.0                     | 0.81                                  | 0.82                               |

voltage implant should be reduced at the channel surface. We believe that this approach provides an alternative to accelerate the tuning of process parameters and benefits fabrication of high

Fig. 9. Performance comparisons among three different evolutionary strategies. There are totally 31 process and device parameters to be optimized in the case of 2-D process and device simulations. Total time is about 70 h on PC-based Linux cluster with 16 CPUs.

performance device for sub-65-nm technologies, in particular, for the semiconductor foundry industry.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. F.-L. Yang and Dr. J.-R. Hwang of the Taiwan Semiconductor Manufacturing Company for supplying measurement data and device fabrication. They also appreciate the reviewers for providing constructive comments, which were very helpful in revising the manuscript.

## REFERENCES

- [1] N. Sano, A. Hiroki, and K. Matsuzawa, "Device modeling and simulations toward sub-10 nm semiconductor devices," *IEEE Trans. Nanotechnol.*, vol. 1, no. 1, pp. 63–71, Mar. 2002.

- [2] G. Pei, J. Kedzierski, P. Oldiges, M. Ieong, and E. C.-C. Kan, "FinFET design considerations based on 3-D simulation and analytical modeling," *IEEE Trans. Electron Devices*, vol. 49, no. 8, pp. 1411–1419, Aug. 2002.

- [3] S. Xiong and J. Bokor, "Sensitivity of double-gate and FinFET devices to process variations," *IEEE Trans. Electron Devices*, vol. 50, no. 11, pp. 2255–2261, Nov. 2003.

- [4] F.-L. Yang, D.-H. Lee, H.-Y. Chen, C.-Y. Chang, S.-D. Liu, C.-C. Huang, T.-X. Chung, H.-W. Chen, C.-C. Huang, Y.-H. Liu, C.-C. Wu, C.-C. Chen, S.-C. Chen, Y.-T. Chen, Y.-H. Chen, C.-J. Chen, B.-W. Chan, P.-F. Hsu, J.-H. Shieh, H.-J. Tao, Y.-C. Yeo, Y. Li, J.-W. Lee, P. Chen, M.-S. Liang, and C. Hu, "5nm-gate nanowire FinFET," in *Proc. Symp. VLSI Technology*, 2004, pp. 15–17.

- [5] V. A. Sverdlov, T. J. Walls, and K. K. Likharev, "Nanoscale silicon MOSFETs: A theoretical study," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1926–1033, Sep. 2003.

- [6] S. M. Ramey and D. K. Ferry, "Modeling of quantum effects in ultrasmall FD-SOI MOSFETs with effective potentials and three-dimensional Monte Carlo," *Physica B*, vol. 314, pp. 350–353, Mar. 2002.

- [7] A. R. Alvarez, B. L. Abdi, D. L. Young, H. D. Weed, J. Teplik, and E. R. Herald, "Application of statistical design and response surface methods to computer-aided VLSI device design," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 7, no. 2, pp. 272–288, Feb. 1988.

- [8] D. S. Boning and P. K. Mozumder, "DOE/Opt: A system for design of experiments, response surface modeling, and optimization using process and device simulation," *IEEE Trans. Semicond. Manuf.*, vol. 7, no. 2, pp. 233–244, May 1994.

- [9] G. J. Gaston and A. J. Walton, "The integration of simulation and response surface methodology for the optimization of IC processes," *IEEE Trans. Semicond. Manuf.*, vol. 7, no. 1, pp. 22–33, Feb. 1994.

- [10] D. S. Boning, M. B. McIlrath Jr., P. Penfield, and E. M. Sachs, "A general semiconductor process modeling framework," *IEEE Trans. Semicond. Manuf.*, vol. 5, no. 4, pp. 266–280, Nov. 1992.

- [11] Y. Li and S.-M. Yu, "A unified quantum correction model for nanoscale single-and double-gate MOSFETs under inversion conditions," *Nanotechnology*, vol. 15, no. 8, pp. 1009–1016, 2004.

- [12] Y. Li and S.-M. Yu, "Quantum correction simulation of random dopantinduced threshold voltage fluctuations in nanoscale metal-oxide-semiconductor structures," in *Proc. IEEE Nanotechnology Conf.*, 2005, pp. 527–530.

- [13] A. Asenov, G. Slavcheva, A. R. Brown, J. H. Davies, and S. Saini, "Increase in the random dopant induced threshold fluctuations and lowering in sub-100 nm MOSFETs due to quantum effects: A 3-D density-gradient simulation study," *IEEE Trans. Electron Devices*, vol. 48, no. 4, pp. 722–729, Apr. 2001.

- [14] K. A. Bowman, X. Tang, J. C. Eble, and J. D. Menldl, "Impact of extrinsic and intrinsic parameter fluctuations on CMOS circuit performance," *Solid-State Circuits*, vol. 35, no. 8, pp. 1186–1198, 2000.

- [15] X. Tang, V. K. De, and J. D. Meindl, "Intrinsic MOSFET parameter fluctuations due to random dopant placement," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 5, no. 4, pp. 369–376, Apr. 1996.

- [16] S. Selberherr, Analysis and Simulation of Semiconductor Devices. New York: Springer-Verlag, 1984.

- [17] T. Binder, C. Heitzinger, and S. Selberherr, "A study on global and local optimization techniques for TCAD analysis tasks," *IEEE Trans. Computer-Aided Design Integrated Circuits Syst.*, vol. 23, no. 6, pp. 814–822, Jun. 2004.

- [18] D. A. Van Veldhuizen, J. B. Zydallis, and G. B. Lamont, "Evolutionary computing and optimization: Issues in parallelizing multiobjective evolutionary algorithms for real world applications," in *Proc. ACM Symp. Appl. Computing*, 2002, p. 595.

- [19] Y. Li and Y.-Y. Cho, "Intelligent BSIM4 model parameter extraction for sub-100 nm MOSFET era," *Jpn. J. Appl. Phys.*, vol. 43, pp. 1717–1722, 2004.

- [20] Y. Li, "An automatic parameter extraction technique for advanced CMOS device modeling using genetic algorithm," *Microelectron*. *Eng.*, to appear.

- [21] Y. Li and S.-M. Yu, "Comparison of random dopant-induced threshold voltage fluctuations in nanoscale single-, double-, and surroundinggate field effect transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 9A, pp. 6860–6865, 2006.

- [22] Y. Li and S.-M. Yu, "Study of threshold voltage fluctuations of nanoscale double gate metal-oxide-semiconductor field effect transistors using quantum correction simulation," *J. Computational Electron.*, vol. 5, no. 2–3, pp. 125–129, 2006.

- [23] Y. Li and Y.-S. Chou, "A novel statistical methodology for sub-100 nm MOSFET fabrication optimization and sensitivity analysis," in *Extended Abstract 2005 Int. Conf. Solid State Devices Materials*, 2005, pp. 622–623.

- [24] Y. Li and S.-M. Yu, "A two-dimensional quantum transport simulation of nanoscale double-gate MOSFETS using parallel adaptive technique," *IEICE-Trans. Info Syst.*, vol. E87-D, pp. 1751–1758, 2004.

- [25] Y. Li and S.-M. Yu, "A parallel adaptive finite volume method for nanoscale double-gate MOSFETs simulation," *J. Computational Appl. Math.*, vol. 175, no. 1, pp. 87–99, 2005.

- [26] Y. Li and H.-M. Chou, "A comparative study of electrical characteristic on sub-10 nm double gate MOSFETs," *IEEE Trans. Nanotechnol.*, vol. 4, no. 5, pp. 645–647, Oct. 2005.

- [27] Y. Li, H.-M. Chou, and J.-W. Lee, "Investigation of electrical characteristics on surrounding-gate and omega-shaped-gate nanowire Fin-FETs," *IEEE Trans. Nanotechnol.*, vol. 4, no. 5, pp. 510–516, Oct. 2005.

- [28] T.-W. Tang, X. Lin, and Y. Li, "Discretization scheme for the density-gradient equations and effect of boundary conditions," *J. Computational Electron.*, vol. 1, no. 3, pp. 389–393, 2002.

- [29] C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, "A physically based mobility model for numerical, simulation of nonplanar devices," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 7, pp. 1164–1171, Jul. 1988.

- [30] M. N. Darwish, J. L. Lentz, M. R. Pinto, P. M. Zeitzoff, T. J. Krutsick, and H. H. Vuong, "An improved electron and hole mobility model for general purpose device simulation," *IEEE Trans. Electron Devices*, vol. 44, no. 9, pp. 1529–1537, Sep. 1997.

- [31] A. Schenk, "Rigorous theory and simplified model of the band-to-band tunneling in silicon," Solid-State Electron., vol. 36, pp. 19–34, 1993.

- [32] Y. Li, C.-K. Chen, and Y.-Y. Cho, "A unified optimization framework for microelectronics industry," in *Proc. 8th Annu. Conf. Genetic Evolutionary Computation*, 2006, pp. 1875–1876 [Online]. Available: http://140.113.87.143/ymlab, UOF project [Online]. Available:

- [33] Y. Li and S.-M. Yu, T. Simos, Ed. et al., "A unified optimization framework for real world problems," *Lecture Series Computer Computa*tional Sciences, vol. 7, pp. 816–819, 2006, Recent progress in computational sciences and engineering.

- [34] Y. Li, S.-M. Yu, and Y.-L. Li, "Application of a unified optimization framework to electronic design automation," *Math. Comput. Simulation*, to be published.

Yiming Li (M'02) received the B.S. degrees in applied mathematics and electronics engineering, the M.S. degree in applied mathematics, and the Ph.D. degree in electronics from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, R.O.C., in 1996, 1998, and 2001, respectively.

In 2001, he joined the National Nano Device Laboratories (NDL), Taiwan, as an Associate Researcher, and the Microelectronics and Information Systems Research Center (MISRC), National Chiao Tung University (NCTU), as an Assistant

Professor, where he has been engaged in the field of computational science and engineering, particularly in modeling, simulation, and optimization of nanoelectronics and very large scale integration (VLSI) circuits. In the fall of 2002, he was a Visiting Assistant Professor with the Department of Electrical and Computer Engineering, University of Massachusetts, Amherst. From 2003 to 2004, he was the Research Consultant of the System on a Chip (SOC) Technology Center, Industrial Technology Research Institute (ITRI), Hsinchu. From 2003 to 2005, he was the Director of the Departments of Nanodevice and Computational Nanoelectronics, NDL, and an Associate Professor with the MISRC, NCTU, since the fall of 2004. He is currently an Associate Professor with the Department of Communication Engineering, NCTU, and is an Adjunct Professor of the Institute of Management of Technology. He is the Deputy Director of the Modeling and Simulation Center of NCTU and conducts the

Parallel and Scientific Computing Laboratory at NCTU. His current research areas include computational electronics and physics, physics of semiconductor nanostructures, device modeling, parameter extraction, and VLSI circuit simulation, development of technology computer-aided design (TCAD) and electronic CAD (ECAD) tools and SOC applications, bioinformatics and computational biology, and advanced numerical methods, parallel and scientific computing, optimization techniques, and computational intelligence. He has authored or coauthored over 120 research papers appearing in international book chapters, journals, and conferences.

Dr. Li has served as a reviewer, Guest Associate Editor, and Guest Editor for many international journals. He has organized and served on several international conferences and was an Editor for proceedings of international conferences. He is a member of Phi Tau Phi, Sigma Xi, the American Physical Society, the American Chemical Society, the Association for Computing Machinery, the Institute of Electronics, Information and Communication Engineers (IEICE), Japan, the Society for Industrial and Applied Mathematics, and is included in Who's Who in the World. He has served as a Reviewer for the IEEE TRANSACTIONS ON NANOTECHNOLOGY, the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, the IEEE ELECTRON DEVICE LETTERS, and the IEEE TRANSACTIONS ON ELECTRON DEVICES. He was the recipient of the 2002 Research Fellowship Award presented by the Pan Wen-Yuan Foundation, Taiwan, and the 2006 Outstanding Young Electrical Engineer Award from Chinese Institute of Electrical Engineering, Taiwan.

**Shao-Ming Yu** (S'05) received the B.S. and M.S. degrees in computer and information science from the National Chiao Tung University, Taiwan, R.O.C., in 2002 and 2004. Currently, he is pursuing the Ph.D. degree at the Department of Computer Science, National Chiao Tung University, Taiwan.

His research interests focus on modeling and simulation of semiconductor nanodevices, parallel and scientific computation, evolutionary algorithms, and design optimization.